Изобретение относится к цифровой вычислительной технике и может быть использовано для построения цифровых вычислительных машин.

, Целью изобретения является сокращение оборудования.

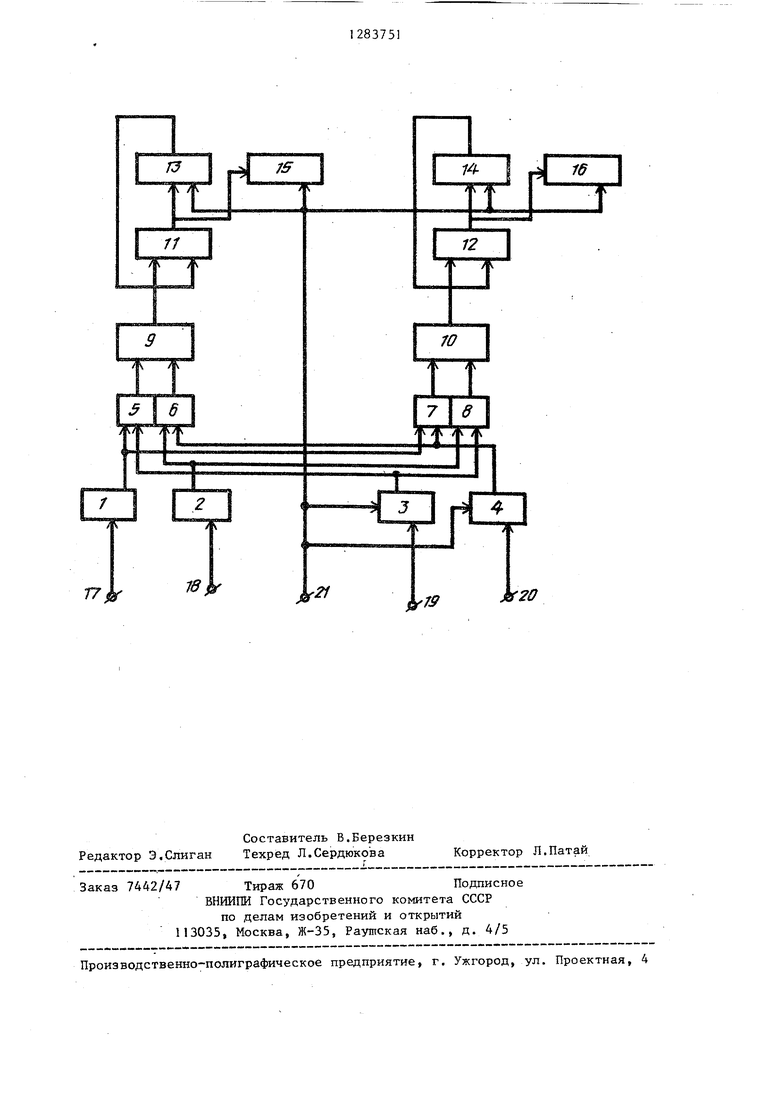

На чертеже представлена схема устройства для умножения комплексных чисел.

Устройство содержит регистры 1 и 2 множимого, регистры 3 и 4 множителя, группы элементов И 5-8, блок 9 вычитания кодов количества единиц, многовходовой одноразрядный сумматор 10, сумматоры И и 12, регистры 13 и 14 накопления, регистры 15 и 16 произведения, входы 17 и 18 множимого (действительной и мнимой частей); входы 19 и 20 множителя (действительной и мнимой частей), тактовый вход 21.

Устройство работает следующим образом,

В исходном состоянии в регистры 3, 4, 13-16 записаны нули, в- регистры 1 и 2 записано множимое. По входам 19 и 20 поступают последовательReIm

Множимое 0101ОНО

Множитель 0111ЮЮ

И6

0000

0000

001

И7 И8Be м-ля

0000 00000001

См 10 00000

Рг 15 Рг 14Рг 16

10000000 0000000000000

0001 0010ООН

опою

0000011000000 0000 00000000 III 0101 0010 0000 оно0111

0000100010

00000 1100000 0000110000000

10

283751 2

но разряды множителя, по входу 21 разряды множителя записываются в регистры 3 и 4 множителя, записывается сумма с сумматоров 11 и 12 в регистры 13 и 14 и производится сдвиг в регистрах 15 и 16. После записи очередного разряда множителя на выходах групп элементов И 5-8 образуются унитарные коды, которые преобразуются в двоичные коды в виде разности на выходе блока 9 и в виде суммы на выходе многовходового одноразрядного сумматора Ю. На сумматорах 1I и 12 суммируются коды с блока 9 и cyNjMaTopa 10 и регистров 13 и 14 соответственно. Результат со сдвигом записывается в регистры 13 и 14, а младший разряд суммы записывается в регистры 15 и 16, при этом в регистры множителя 3 и 4 записывается очередной разряд. После приема, всех разрядов множителя по входам 19 и 20 поступают нули в течение (n-l) тактов, где п - разрядность числа. Произведение получено в регистрах 15 и 16. Пример приведен ниже.

Блок 9 и сумматор 10 могут быть построены на ПЗУ

15

20

25

Im MHO-л я 0000

0001

0010

312837514

0100 0100 0101 Olio 11100101

0000000100

00000 0111000 00010 11000000

0100 -0010. 0000 0100 1100 1010

0000000001

00000 0011000 00001 11100000

0000 0100 0100 0000 1000 0100

00001

11111

11111 1001110

0000 0000 0000 0000

OOODO00000

inn n 00111 00000 1011100

0000 0000 0000 0000 0000

0000000000

11 11 I n iOOn 1 00000 0101 I 100

00001 on 1000 0000 1000

0000

Формула изобретени

Устройство для умножения комплек- сных чисел, содержащее два регистра множимогоj два регистра множителя, два сумматора и два регистра произведения, входы разрядов регистров множимого соединены с входами мно- жимого устройства, отличающееся тем что, с целью сокращения оборудования, в устройство введены четыре группы элементов И, два регистра накопления, многовходовой одноразрядный сумматор и блок вычитания кодов количества единиц, причем выходы разрядов первого и вто- рого регистров множимого соединены с первыми входами элементов И соот- ветственно первой и второй групп, вторые входы которых соединены с выходами разрядов соответственно первого и второго регистров множителя, первые входы элементов И третьей и четвертой групп соединены с выходами разрядов соответственно первого и второго разрядов множимого устройства, а вторые входы соединены с выходами разрядов соответственно вто- рого и первого регистров множителя устройства, выходы элементов И первой и второй групп соединены с вхо00001 on 1000 0000 1000

0000

дами блока вычитания кодов количества единиц, выходы которого соединены с первой группой входов первого сумматора, выходы элементов И третьей и четвертой групп соединены с входами мно го входов о го одноразрядного сумматора, выходы которого соединены, с первой группой входов второго сум- матора, выходы разрядов первого и второго сумматоров соединены со сдвигом на один разряд вправо с входами разрядов соответственно первого и второго регистров накопления, выходы младших разрядов первого и второго сумматоров соединены с вхоами старших разрядов соответственно первого и второго регистров про- йзведения, выходы первого и второго регистров накопления соединены с вторыми группами входов соответственно первого и второго сумматоров, выход знакового разряда первого сумматора соединен с входом знакового разряда первого регистра накопления, тактовый вход устройства подключен к входам управления сдвигом реги- стров множителя и произведения и входами записи регистров накопления, входы первых разрядов регистров множителя соединены с входами множителя устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1985 |

|

SU1260948A1 |

| Устройство для умножения | 1984 |

|

SU1254469A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1193667A1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для умножения | 1978 |

|

SU763897A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для построения цифровых вычислительных машин. Целью изобретения является сокращение оборудования. Устройство содержит регистры множимого, регистры множителя, четьфе группы элементов И, мно- говходовой одноразрядный сумматор, блок вычитания кодов количества единиц, сумматоры, регистры накопления, регистры произведения. 1 ил, 1 табл. (Л с:

Авторы

Даты

1987-01-15—Публикация

1985-07-23—Подача