Изобретение относится к вычислительной технике и предназначается в основном для использования в электроприводах постоянного и переменного тока с цифровым управлением.

Известен регистр, выполняющий функции приема, хранения и передачи информации. Информация хранится в регистре в виде слова, представленного комбинацией сигналов "0" и "1". Каждому разряду числа, записанному в регистр, соответствует свой разряд регистра, выполненный на основе триггеров RSt [1].

Данный регистр может быть использован для сигналов многофазного кода, но он обладает рядом недостатков, которые заключаются в возможности приема ошибочной информации, хранении ошибочной информации и возникновении ошибок во время ее хранения, низкой помехозащищенности и достоверности работы.

Наиболее близким к предлагаемому решению по технической сущности является регистр с блоком коррекции, выполненный на RSt-триггерах, элементах И и ИЛИ, где входные шины соединены с выходами RSt-триггеров ячеек памяти, выходы блока коррекции соединены с элементами И данной ячейки памяти и являются выходами регистра [2].

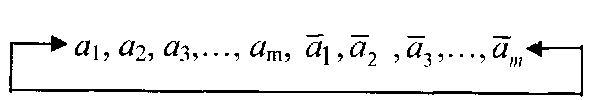

Особенностью многофазного кода является то, что для любой кодовой комбинации

кольцевой последовательной записи его сигналов  где

где

Регистр, приведенный в [2], при обнаружении и исправлении ошибки, не исправляет ошибки на границе нулей и единиц в последовательности сигналов многофазного кода. В процессе прохождения такой ошибки результирующая информация регистра искажается.

Цель изобретения - резервирование и повышение надежности регистра.

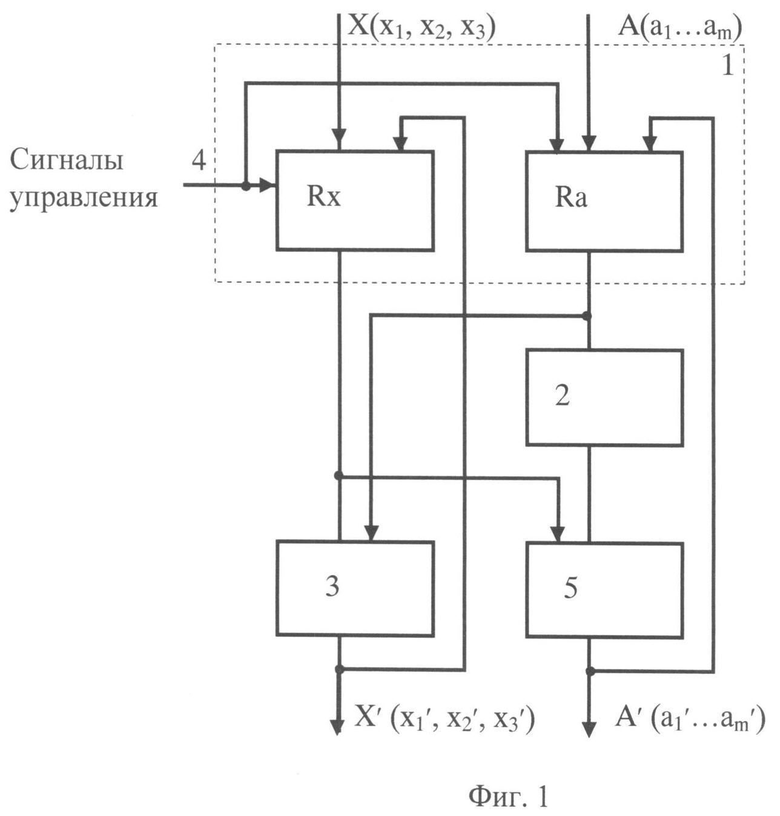

Поставленная цель достигается тем, что в регистр, содержащий ячейки памяти информационных сигналов Ra, блок коррекции, введены ячейки памяти контрольных сигналов Rx и блоки исправления ошибок, входы которых соединены с блоком коррекции и с элементами ячеек памяти Rx, Ra, при этом выходы блоков исправления ошибок контрольной части X'(x1', х2', х3') и информационной части A'(a1'…am') соединены с элементами ячеек памяти Rx, Ra соответственно и являются выходами регистра.

На фиг.1 изображена структурная схема резервирования регистра. Резервированный регистр в многофазном коде 1 содержит ячейки памяти информационных Ra, где a=1…m и контрольных сигналов Rx, где х=1…3, шину управления 4, блок коррекции 2 и блоки исправления ошибок контрольной части 3 и информационной 5.

Предлагаемый регистр работает следующим образом.

При подаче напряжением с уровнем логической единицы на шину 4 информация поступает в регистр и устанавливает его триггеры в ячейках памяти в соответствии с этими сигналами. Сигналы с выходов триггера после исправления ошибок в блоке 2 поступают на блоки исправления ошибок 3 и 5, с выходов которых поступают на выходные регистры. В режиме хранения информации снимается сигнал с шины 4. В этом случае исправленная от ошибок информация с выходов регистра снова подается на входы триггеров и устанавливает их в положения, соответствующие кодовой комбинации многофазного кода.

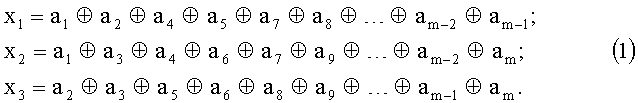

Методика обнаружения и исправления ошибок в блоках 3 и 5 основана на добавлении контрольных разрядов. Для исправления всех одиночных ошибок многофазного кода достаточно три контрольных сигнала, поскольку кодовое расстояние между любыми кодовыми комбинациями равно или более 3.

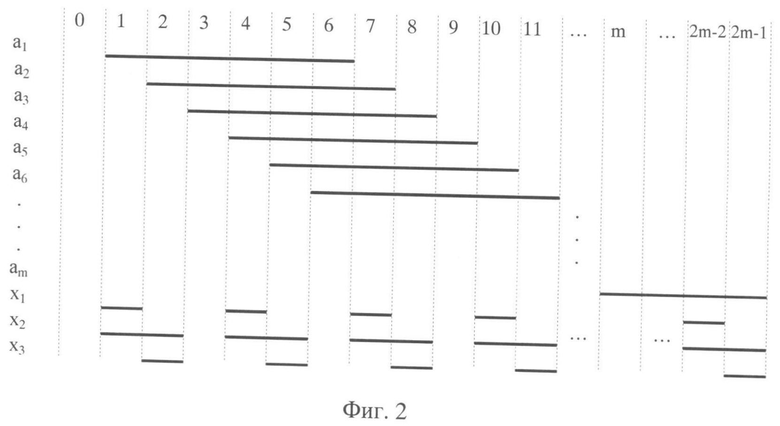

Зависимости многофазных сигналов (a1, a2, a3…am) с эквивалентными цифрами контрольной части (x1, х2, х3) представлены на фиг.2. Кодовая последовательность контрольных разрядов 0, 6, 3 циклически повторяется [3]. Аналогично образуются сигналы контрольных разрядов для любого числа фаз, кратных трем. Основание системы счисления многофазного кода Р=2m. Контрольные сигналы на входе блока исправления ошибок сформированы независимо в предыдущем устройстве - источнике m фазных сигналов и определяются зависимостями:

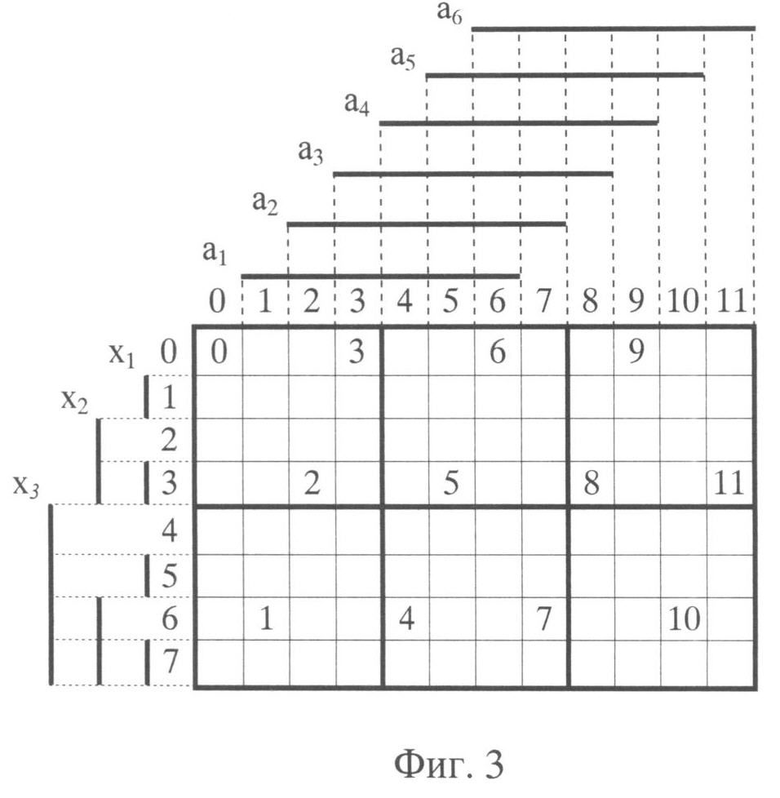

Работа по исправлению одиночной ошибки, возникающая в любом разряде кода, поясняется на фиг.3, где в ячейках n-мерного пространства проставлены разрешенные кодовые комбинации 0, 1, 2, …, 11 в соответствии с зависимостью сигналов многофазного кода a1-a6 от сигналов контрольных разрядов x1, x2, x3.

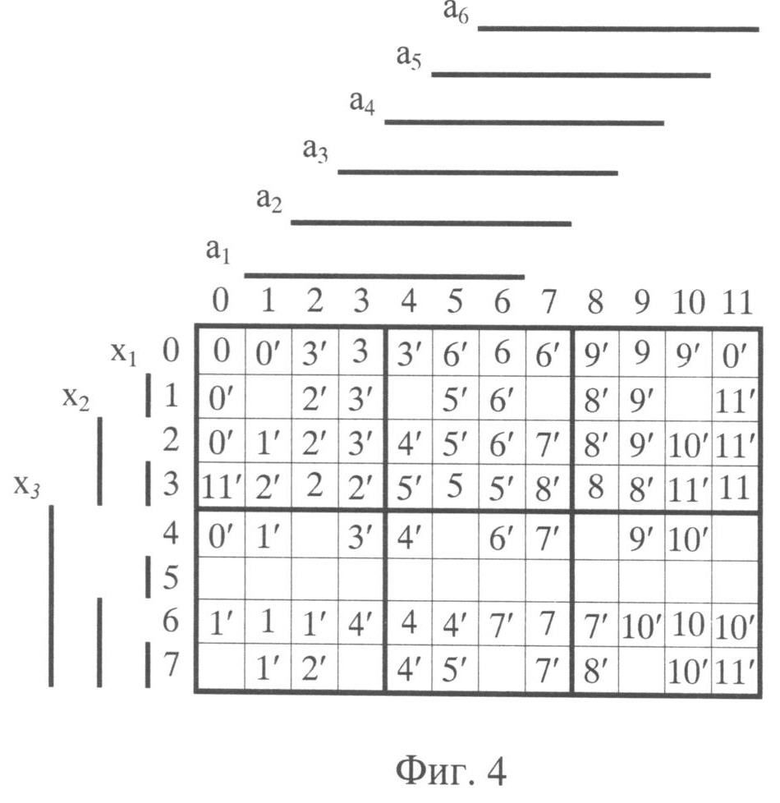

На фиг.4 кроме ячеек с разрешенными кодовыми комбинациями заполнены ячейки с кодовыми комбинациями одиночных ошибок.

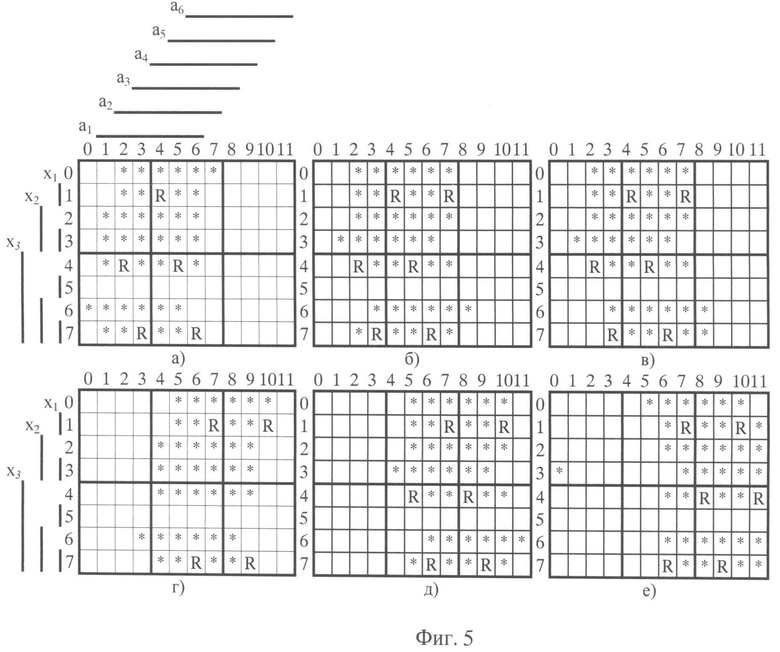

На фиг.5 (а, б, в, г, д, е), учитывая, что a1={1, 2, 3, 4, 5, 6}, а2={2, 3, 4, 5, 6, 7}, а3={3, 4, 5, 6, 7, 8}, а4={4, 5, 6, 7, 8, 9}, а5={5, 6, 7, 8, 9, 10}, а6={6, 7, 8, 9, 10, 11}, представлены геометрические образы сигналов a1'-a6' соответственно.

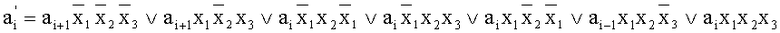

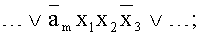

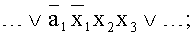

Для каждого геометрического образа сигналов a1'-am' выбираются те ячейки пространства, которые однозначно включаются в эти сигналы. Эта процедура позволяет получить в многомерном пространстве фигуры для сигналов многофазного кода a1'-am', оптимальное покрытие которых определяет функции блока исправления ошибок. При исправлении одиночных ошибок многофазного кода сигналы на выходе блока 3 для фаз i, i+1, m определяются зависимостями:

при этом для первой фазы шестое слагаемое в выражении для

если фаза последняя четвертое слагаемое в выражении для ai+2' запишется в виде:

где i=1, 4, 7…, m-2;

m - количество фаз многофазного кода.

ai, ai+1, ai+2, am - входные сигналы фаз i, i+1, i+2, m регистра;

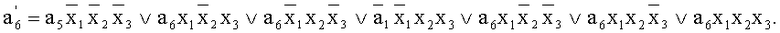

Например, для шестифазного кода логическая схема исправления ошибок во всех шести фазах в аналитической форме имеет следующий вид:

Аналогичным образом происходит исправление ошибок в сигналах многофазного кода для любой фазности, кратной трем.

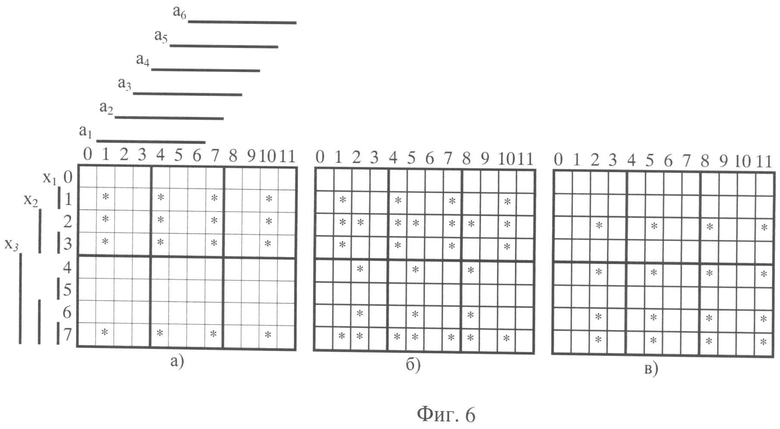

На фиг.6 (а, б, в), учитывая, что x1={2, 4, 7, 10}, х2={2, 3, 6, 7), х3={4, 5, 6, 7}, представлены геометрические образы контрольных сигналов х1'-х3' соответственно.

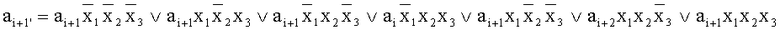

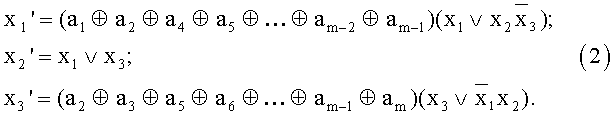

Схема исправления ошибок контрольных разрядов 5 для m-фазного кода в аналитической форме записи имеет вид:

Таким образом, предлагаемый многофазный регистр позволяет принимать информацию с одновременным исправлением всех одиночных ошибок, в том числе на границе нулей и единиц в последовательности многофазного кода, за счет введения контрольных сигналов и блока исправления ошибок. А обратные связи с выхода регистра на его вход позволяют сохранить информацию и не дают помехам установить триггер в нештатные состояния.

ЛИТЕРАТУРА

1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М.: Советское радио, 1975 г., с.104-111.

2. АС 987681. МПК7 G11C 19/00. Регистр / В.И.Кочергин // Открытия. Изобретения. 1983. №1.

3. Кочергин В.И. Теория многомерных цифро-векторных множеств. Томск: Изд-во ТГУ, 2007. стр.122-134.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр | 1980 |

|

SU987681A1 |

| СПОСОБ СИНДРОМНОГО ДЕКОДИРОВАНИЯ ДЛЯ СВЕРТОЧНЫХ КОДОВ | 2004 |

|

RU2282307C2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

| Способ обнаружения и исправленияОшибОК B зАпОМиНАющЕМ уСТРОйСТВЕ СпОМОщью КОРРЕКТиРующиХ КОдОВ | 1979 |

|

SU841062A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| Устройство коррекции ошибок в модулярном коде на основе расширения системы оснований | 2017 |

|

RU2652446C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении надежности и помехоустойчивости электроприводов с цифровым управлением за счет повышения достоверности функционирования устройств, содержащих ячейки памяти. Резервированный регистр, содержащий ячейки памяти информационных сигналов Ra, с которых по сигналам с шины управления данные поступают в блок коррекции, причем в регистр введены ячейки памяти контрольных сигналов Rx и блоки исправления ошибок, входы которых соединены с блоком коррекции и с элементами ячеек памяти Rx, Ra, при этом выходы блоков исправления ошибок контрольной части X'(x1', x2', x3') и информационной части A'(a1'…am') соединены с элементами ячеек памяти Rx, Ra соответственно и являются выходами регистра. 6 ил.

Резервированный регистр, содержащий ячейки памяти информационных сигналов Ra, с которых по сигналам с шины управления данные поступают в блок коррекции, отличающийся тем, что введены ячейки памяти контрольных сигналов Rx и блоки исправления ошибок, входы которых соединены с блоком коррекции и с элементами ячеек памяти Rx, Ra, при этом выходы блоков исправления ошибок контрольной части X'(x1', x2', x3') и информационной части A'(a1'…am') соединены с элементами ячеек памяти Rx, Ra соответственно и являются выходами регистра.

| БЕЛИЦКАЯ Л.А | |||

| Исправление одиночных ошибок в многофазных кодах | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| РЕЗЕРВИРОВАННЫЙ RS-ТРИГГЕР | 2006 |

|

RU2308147C1 |

Авторы

Даты

2013-06-27—Публикация

2011-11-11—Подача