: . Изобретение относится к вычислительной технике и, в частности, к запоминающим устройствам и может Gatb использовано в электроприводах с цифровым управлением и в системах управления этими приводами. .

Известен регистр, выполняющий функции приема, хранения и передачи информации. Информация хранится в регистре в виде слова, представленно-. го ксмбинацией сигналов О и 1,, Каждому разряду числа, записанному врегистр, соответствует свой разряд регистра, выполненный, как правило, на основе триггеров RS, RS, D, Di или 1К типов 1,

Данный регистр может быть использован для сигнгшов многофазного кода,, но он обладает рядом недостатков, которые заключгиотся в возможности Г приёма ошибочной информации, хранении Ошибочной информации и возникновении ошибок во ее хранения.

Наиболее близким к предлагаемому по технической суамости является регистр с паразшельиым при&лом информации, выполненный иа RS -триггерах, где входные овшы соединены с R- и 8-входами Й34- 1Жггеров через элемеиты связи (йапр1в4ер, элементы И).

Этот регистр при получении ошибочной информации также не производит ее исправления. В процессе хранения информации в результате случайного сбоя триггеров регистра информация

; регистра искажается.

Цель изобретения - повышение помехозащищенности регистра. Поставле1;ная цель достигается тем г.

10

что В регистр, содержащий ячейки пимяти, каждая из которых состоит из RS.-триггера и элементов И, выходы первого и второго элементов И соединены соответственно с одними R-. и

15 S-входами RS| -триггера, выходы третьего и четвертого элементов И соеди йены соруве.тственно с другими R- и S-входами RS -триггера, первые входы четвертых элементов И ячеек памяти

20 являк1тся входгили регистра,и шины управления, введен блок коррекции, входы которого соединены с выходами RS: -TpHrrepoB ячеек памяти, выходы блокакоррекции соединень с первыми

25 входами третьих элементов И ячеек памяти, первый вход второго элемента И каждой ячейки памяти соединен с выходом третьего элемента И данной ячейки памяти, ьторые входы второго

30 и третьего элементов И ячеек памяти

соединены с первой шиной уЬравлани.я, первый вход первого элемента И каждо ячейки памяти соединен с выходом четвертого элемента И данной ячейки памяти, вторые входы первого и четвертого элементов И соединены с второй шиной управления, а выходы блока коррекции являются выходами регистра.

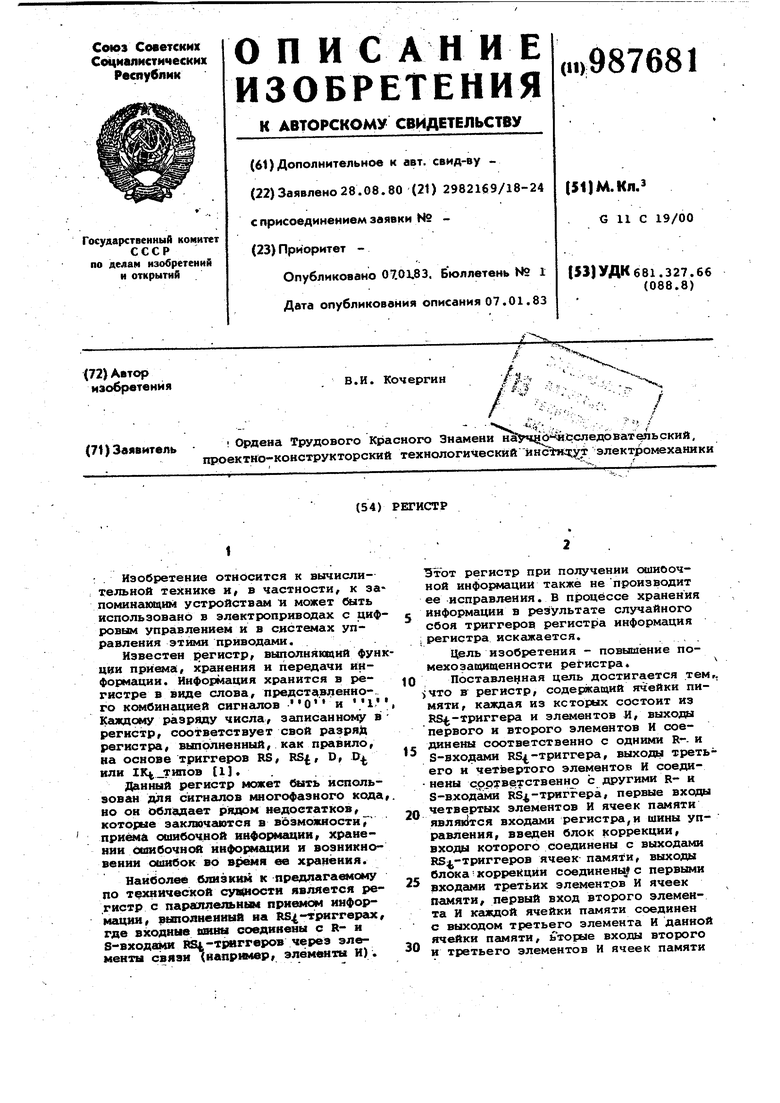

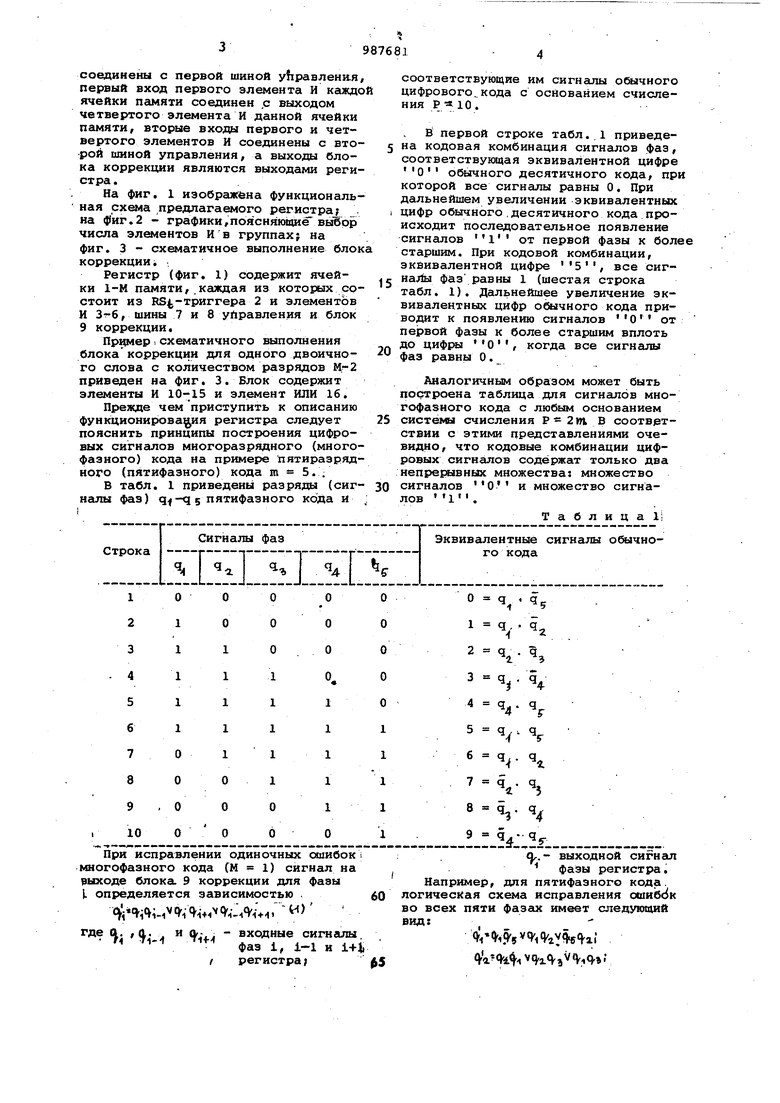

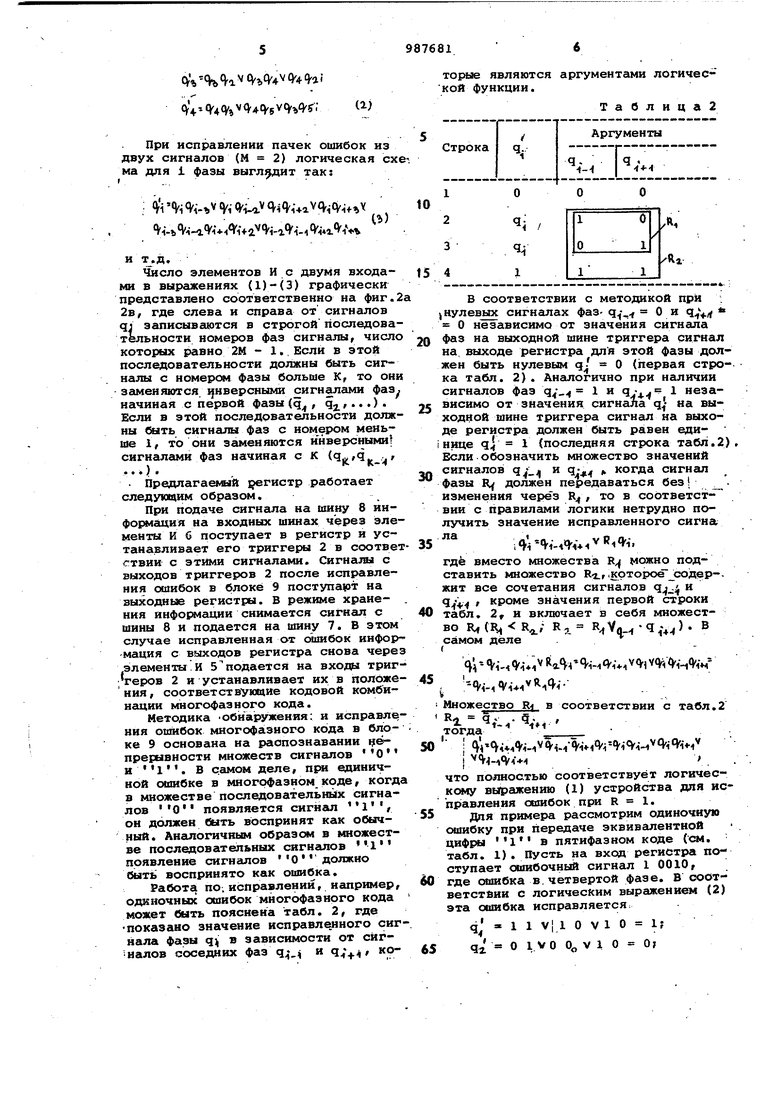

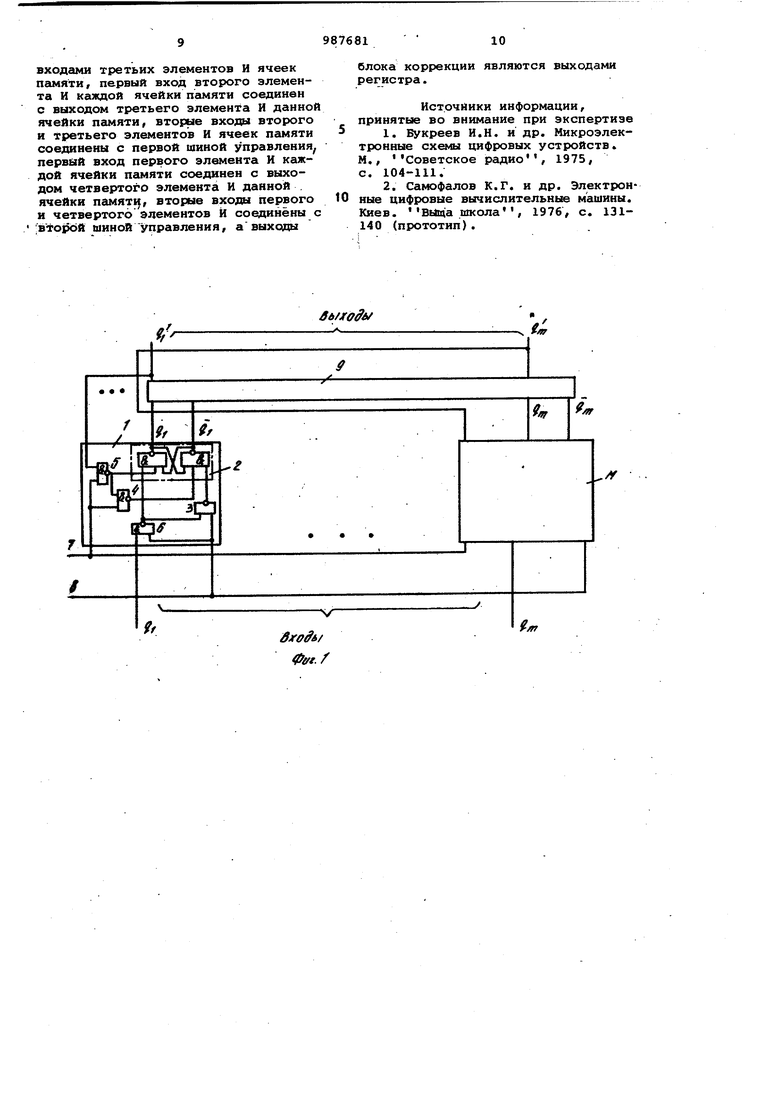

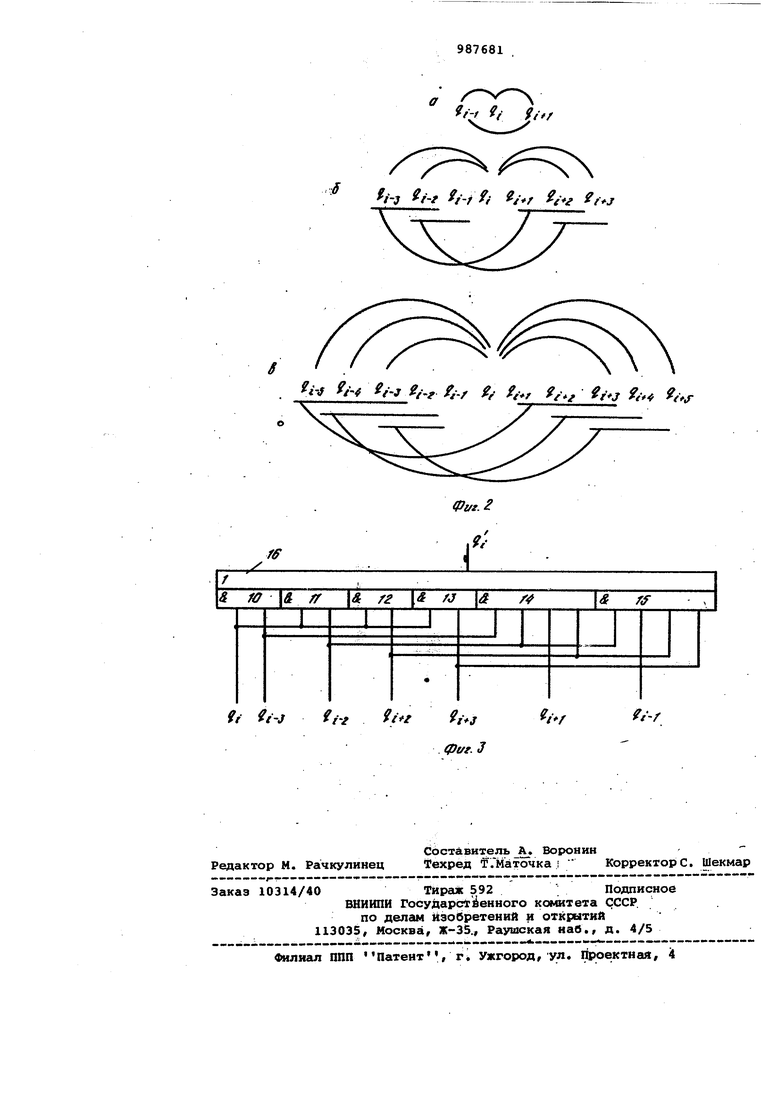

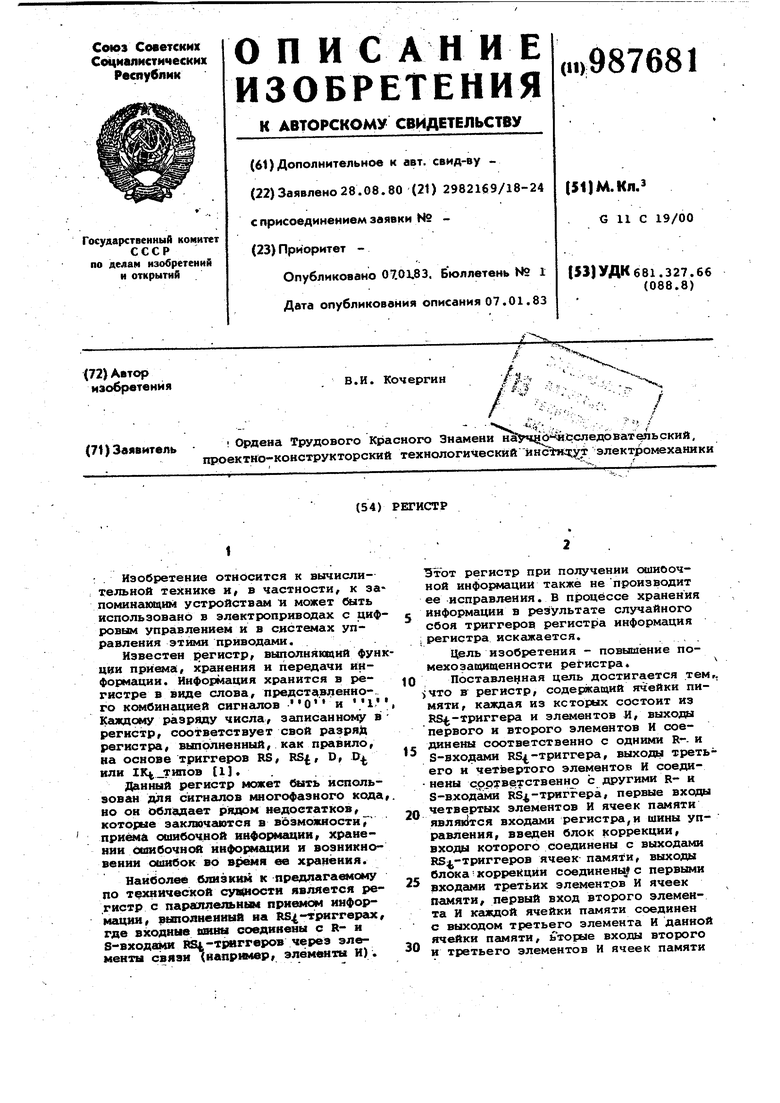

На фиг. 1 изображена функциональная схема предлагаемого регистра на фиг.2 - графики,поясняющиёвыёрр числа элементов Ив группах; на фиг. 3 - схематичное выполнение блок коррекции

Регистр (фиг. 1) содержит ячейки 1-м памяти, каждая из которых состоит из RS -триггера 2 и элементов И , шины 7 и 8 управления и блок 9 коррекции.

Пр |мер: схематичного шлполнения блокакоррекции для одного двоичного слова с количеством разрядов приведен на фиг. 3. Блок содержит элементы И 10-15 и элемент ИЛИ 16.

Прежде чем приступить к описанию функционирования регистра следует пояснить принципы построения цифровых сигналов многоразрядного (многофазного) кода на примере пятиразрядного (пятифазного) кода m 5..

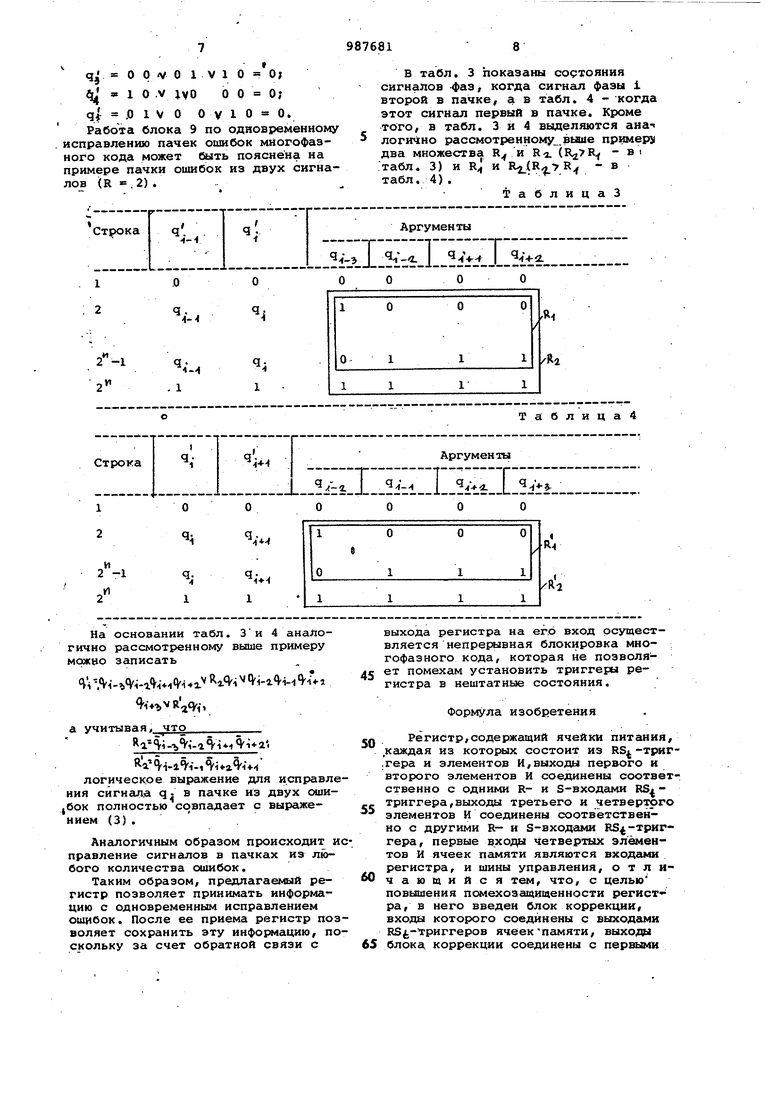

В табл. 1 приведены разряды (сигНсшы фаз) пятифазного кода и

соответствующие им сигнсшы обычного цифрового., кода с основанием счисления Р « 10.

В первой строке табл. 1 приведена кодовая комбинация сигналов фаз, соответствующая эквивалентной цифре О обычного десятичного кода, при которой все сигналы равны О. При дальнейшем увеличении эквивалентных цифр обычного.десятичного кода происходит последовательное появление

от первой фазы к более

сигналов

старшим. При кодовой комбинации, эквивалентной цифре 5, все сигHajfei фаз равны 1 (шестая строка табл. 1). Дальнейшее увеличение эквивалентных цифр обычного кода приводит к появлению сигнгипов О от фазы к более старшим вплоть

до цифЕял 0

, когда все сигналы фаз равны О.

Аналогичным образом может быть построена таблица для сигналов многофазного кода с любым основанием система счисления Р - 2И1 В соответствии с этими представлениями очевидно, что кодовые комбинации цифровых сигналов содержат только два непрерывных множества: множество сигналов О и множество сигналов

Таблица 1|

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Делитель-счетчик многофазного кода (его варианты) | 1982 |

|

SU1228269A1 |

| РЕЗЕРВИРОВАННЫЙ РЕГИСТР В МНОГОФАЗНОМ КОДЕ | 2011 |

|

RU2486611C1 |

| Устройство для управления многофазным инвертором | 1978 |

|

SU955837A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| АВТОНОМНЫЙ НАВИГАЦИОННЫЙ ПРИБОР | 1994 |

|

RU2098767C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1385294A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для исправления двухкратных ошибок в блоках передачи и хранения информации | 1983 |

|

SU1173417A1 |

При исправлении одиночных сшибок многофазного кода СМ 1) сигнал на выходе блока. 9 коррекции для фазы . определяется зависимостью . 0

C):.tv(V;.,vq|qr,-+,xq,-.i4i.

где t(L . и От- J - входные сигналы - фаз 1, 1-1 и i+i

/ регистра; 5

с. выходной сигнал

фазы регистра. Например, для пятифазного кода, логическая схема исправления сшибс к во всех пяти фазгис имеет следующий вид:

(V,q-.

CV4%4a V%«V4 Q4 i vV--V4% V4(V5V«V%4r.При исправлении пачек ошибок из двух сигналов (М 2) логическая сх ма для 1 фазы так: ; .vq.,-(,,-,,v(v,-cv.v%v «V4-bV-i-i4i Ai42 «Vi-a%-.i«V «xViV и т.д. Число элементов И с двумя входами в выражениях (1)-(3) графически представлено соответственно на фиг. 2в, где слева и справа от сигналов qj записываются в строгой последовательности номеров фаз сигналы, число которых равно 2М - 1,,Если в этой последовательности должны быть сигналы с номером фазы больше К, то они заменяются 1|нверсными сигналами фаз начиная с первой фазы (q , g,...). Если в этой последовательности должны ть сигналы фаз с номером меньше 1, то они заменяются инверсными сигналами фаз начиная с к (., . , )К К--1 V Предлагаемой гистр работает следующим образом. П{Я1 подаче сигнала на шину 8 информация на входных шинах через элементы И б поступает в регистр и устанавливает его триггеры 2 в соответ ствии с этими сигналами. Сигналь с выходов триггеров 2 после исправления ошибок в блоке 9 поступают на выходные регистры. В режиме хранения инфОЕ 1ации снимается сигнал с шины 8 и подается на шину 7. В этом случае исправленная от сиишбок информация с выходов регистра снова чере элементы.И 5 подается на входы триг /геров 2 и устанавливает их в положения , соответствующие кодовой комбингщии многофазного кода. Методика Обнаружения: и исправления ошибок многофазного кбда в блоке 9 основана на распознавании &пре1швности множеств сигналов 0 и 1. В рамом деле, при единичной ошибке в многофазном коде, когда в множестве последовательньгх сигналов О появляется сигнал 1, он должен быть воспринят как обычный. Ангшогичвым образом в множестве последовательных сигнгшов появление сигналов О должно быть воспринято как ошибка. Работа по. исправлении, иапример, одиночных ошибок многофазного кода может быть пояснена табл. 2, где показано значение исправле.нного сиг нала фазы q в зависимости от сигналов соседних фаз .:j и q;. крторые являются аргументами логичес кой функции.

Таблица2 В соответствии с методикой при : (Нулевых сигналах фаз- О и 0 независимо от значения сигнала фаз на выходной шине триггера сигнал на, выходе регистра для этой фазы должен быть нулевым О (первая строка табл. 2). Аналогично при наличии сигналов фаз q, 1 и : 1 независимо от значения сигнала q на выходной шине триггера сигнал на выходе регистра должен быть равен единице q 1 {последняя строка табл.2). Белиобозначить множество значений сигналов , и q- когда сигнал фазы R должен передаваться без . изменения через R, то в соОтветст- ВИИ с правилами логики нетрудно получить значение исправленного сигна ; iV,wqi4.vRi4i. где вместо множества R можно подставить множество Ri.,,KpTopoe coflep-жит все сочетания сигналов и кроме значения первой строки табл. 2, и включает в себя множество R (1 R,- R j R Vq q-v) В самом деле . -- Vi,, ( ,-.,(Vi, 44-,Vi i i iМножество R в соответствии с табл.2 R- q . . a. . X t- -Ifi тогда . I .)i V H 4iqi i 1 V(v.,v,., что полностью соответствует логическому выражению (1) устройства для испр авления сшибок при R 1. Для примера рассмотрим одиночную ошибку при передаче эквивалентной . цифры в пятифазном коде (см. табл. 1). Пусть на вхрд регистра поступает ошибочный сигнал 1 00X0, где ошибка в. четвертой фазе. В соответствии с логическим выражением (2) эта ошибка исправляется. q 1 1 V|1 О V 1 О If О 1 VO GO V 1 о 0;

q Opv01V10 0; 1 О .V lyo 00 0;

q| .0 1 V 0 0 V 1 0 0.

Работа блока 9 по одновременному исправлению пачек ошибок многофазного кода может быть пояснена на примере пачки ошибок из двух сигналов (R . 2) .

На основании табл. 3и 4 аналогично рассмотренному выше примеру можно записать

; Vi-%«V a, 41 qri-i Vi.i % Д J

Я-п+ъ л г У а учитывая, что

a3-i- i-a i 4

44i..,i a i4-i

логическое выражение для исправления сигнала Я: в пачке из двух оши,бок полностью совпадает с выражением (3) .

Аналогичным образом происходит исправление сигналов в пачках из любого количества ся1Шбок.

Таким образом, предлагаемый регистр позволяет принимать информацию с одновременным исправлением ошибок. После ее приема регистр позволяет сохранить эту информацию, поскольку за счет обратной связи с

В табл. 3 показаны состояния сигналов -фаз, когда сигнал фазы 1 второй в пачке, а в табл. 4 - когда этот сигнал первый в пачке. Кроме того, в табл. 3 и 4 выделяются ана- логично рассмотренному.выше примерл два множества R и R. ( - в i табл. 3) и и R2-(R. 7 R - в табл. 4) .

ТаблицаЗ

выхода регистра на его вход осуществляется непрерывная блокировка Многофазного кода, которая не позволяет помехам установить триггеры регистра в нештатные состояния.

Формула изобретения

Регистр,содержащий ячейки питания, каждая из которых состоит из RS -триг.гера и элементов И,выходы первого и второго элементов И соединены соответственно с одними R- и S-входами RS триггера,выходы третьего и четвертого элементов И соединены соответственно с другими R- и S-входами RS -триггера, первые входы четвертых элементов и ячеек памяти являются входами регистра, и шины управления, отличающийся тем, что, с целью повышения помехозащищенности регистра, в него введен блок коррекции, входы которого соединены с выходами RS -1rpиггepoв ячеекпамяти, выходы 5 блока коррекции соединены с первыми

входами третьих элементов И ячеек пгимяти, первый вход второго элемента И каждой ячейки памяти соединен с выходом третьего элемента И данной ячейки памяти, вторые входы второго и третьего элементов И ячеек памяти соединены с первой шиной управления, первый вход первого элемента И каждой ячейки памяти соединен с выходом четвертого элемента И данной . ячейки псшят ;, вторые входы первого и четвертого элементов И соединены с ;второй шинойуправления, авыходы

блока коррекции являются выходами регистра.

Источники информации, принятые во внимание при экспертизе

с. 104-111.

u/JTO A/

ff

г

v

фуг. /

f

J.

9,

a

ar

fm

/-j i-f f-t ft /«/ /v

ЛГ

X

f/ /-j /-/ /v/ //

./

.;

fi-r

. J

Авторы

Даты

1983-01-07—Публикация

1980-08-28—Подача