Изобретение относится к радиотехнике, а именно к синтезаторам частот (СЧ) с импульсной фазовой автоподстройкой (ИФАП) с зарядовой накачкой, делителем с переменным или дробно-переменным коэффициентом деления (ДПКД/ДДПКД) и дополнительным контуром управления в цепи обратной связи, формирующим дополнительное управляющее воздействие на основе информации о коэффициентах деления.

Известны СЧ, построенные на основе ИФАП с ДПКД или ДДПКД в цепи обратной связи (см. Синтезаторы частот: Учебное пособие / Б.И. Шахтарин и др. - М.: Горячая линия. - Телеком, 2007. - 128 с.). Указанные СЧ производятся в большом ассортименте в виде готовых микросхем ведущими производителями электроники: Analog Devices, Texas Instruments и др. Они позволяют формировать на выходе большое число дискретных частот при малых габаритах и малой потребляемой мощности.

Недостатком этих СЧ является вынужденный компромисс между возможностью получить высокую чистоту спектра выходного сигнала при широком диапазоне частот с малым шагом сетки частот и высоким быстродействием при переключении с одной частоты на другую.

Указанный недостаток устраняется применением многокольцевых схем, схем компенсации помех дробности, модификацией ЧФД и применением схем с изменяемой структурой.

Наиболее близким техническим решением к заявляемому изобретению является схема СЧ на базе контура импульсной фазовой автоподстройки частоты с компенсацией помех дробности, описанная в патенте РФ №2491713 от 01.10.2012, МПК H03L 7/00.

Схема имеет первый (Fref), второй (N) и третий (F) входы, выход Fvco и включает импульсный частотно-фазовый детектор (ИЧФД), имеющий первый вход Fref, второй вход Ffb, первый выход Up и второй выход Dn; управляемый источник тока (УИТ), имеющий первый вход Up, второй вход Dn и выход I0; емкостный элемент, имеющий вывод Vc; элемент коммутации, имеющий вход управления Sw и первый и второй выводы; фильтр нижних частот (ФНЧ), имеющий вход Vf и выход Vvco; управляемый генератор (УГ), имеющий вход Vvco и выход Fvco; делитель с дробно-переменным коэффициентом деления (ДДПКД), имеющий первый вход Fvco, второй вход N, третий вход OVER и выход Ffb; схему управления значением коэффициента деления (УКД), имеющую вход F, первый выход OVER и второй выход Fc; источник тока компенсации дробности (ИТКД), имеющий вход Fc и выход Iс.

На первый вход схемы ИЧФД подается сигнал опорной частоты с первого входа Fref устройства. Второй вход схемы ИЧФД подключен к выходу Ffb схемы ДДПКД. Выходы Up и Dn схемы ИЧФД соединены с соответствующими входами схемы УИТ. Выходы схем УИТ и ИТКД, вывод Vc емкостного элемента и первый вывод элемента коммутации соединены между собой. Второй вывод элемента коммутации соединен с входом схемы ФНЧ, выход которой соединен с входом Vvco схемы УГ. Выход схемы УГ, первый вход схемы ДДПКД и выход Fvco устройства соединены между собой. На второй вход схемы ДДПКД подается значение целой части коэффициента деления с второго входа N устройства. Третий вход схемы ДДПКД подключен к первому выходу схемы УКД. На вход схемы УКД подается значение дробной части коэффициента деления с третьего входа F устройства. Вход схемы ИТКД подключен к второму выходу Fc схемы УКД.

Устройство работает следующим образом. Схема ИЧФД сравнивает фазу сигнала Fref опорной частоты и фазу сигнала Ffb частоты обратной связи и вырабатывает сигналы Up и Dn в соответствии с фазовой разностью. По этим сигналам схема УИТ вырабатывает выходной ток I0, под действием которого, совместно с выходным током Ic схемы ИТКД, на емкостном элементе формируется потенциал напряжения сигнала Vc. Сигнал Sw управляет элементом коммутации так, что переводит его в разомкнутое состояние на время, когда выходные токи схем УИТ или ИТКД находятся в активном состоянии, и в замкнутое состояние, когда выходы схем УИТ и ИТКД выключены. На выходе схемы ФКУ формируется сигнал Vvco, являющийся управляющим для ГУН. Сигнал Fvco выходной частоты ГУН поступает на схему ДДПКД, осуществляющую деление на N или N+1 в зависимости от состояния сигнала управления OVER, и вырабатывающую сигнал Ffb частоты обратной связи. При каждом такте сравнения фаз в ИЧФД схема УКД накапливает значение фазовой ошибки Fc в пропорции к одному периоду выходной частоты ГУН и вырабатывает сигнал OVER для формирования дробности, заданной значением F. Схема ИТКД в соответствии со значением Fc накопленной фазовой ошибки вырабатывает ток Ic для компенсации импульсов тока I0 УИТ, вызванных дробным делением в ДДПКД.

Недостатком прототипа является большое время перестройки при переключении частоты СЧ.

Поставленной задачей предложенного решения является сокращение времени перестройки СЧ при смене рабочей частоты за счет исключения фазы поиска сигнала по частоте.

Технический результат изобретения - повышение быстродействия синтезатора частот при смене рабочей частоты.

Для достижения поставленной задачи в быстродействующий синтезатор частоты, содержащий опорный генератор, подключенный через первый вход импульсного частотно-фазового детектора к управляемому источнику тока, имеющий входы в соответствии с фазовой разностью опорного и сигнала частоты обратной связи, выход управляемого источника тока, подключенный к входу фильтра нижних частот, выход которого соединен через сумматор-формирователь сигнала управления с входом управляемого генератора, выходы управляемого генератора выведены на первый вход делителя с переменным или дробно-переменным коэффициентом деления и на потребителя, выход делителя с переменным или дробно-переменным коэффициентом деления подключен к второму входу импульсного частотно-фазового детектора, введен регистр управляющего кодового слова, соединенный с дешифратором управляющего кодового слова, при этом первый выход дешифратора управляющего кодового слова соединен с вторым входом сумматора-формирователя сигнала управления, а второй выход дешифратора управляющего кодового слова соединен с вторым входом делителя с переменным или дробно-переменным коэффициентом деления.

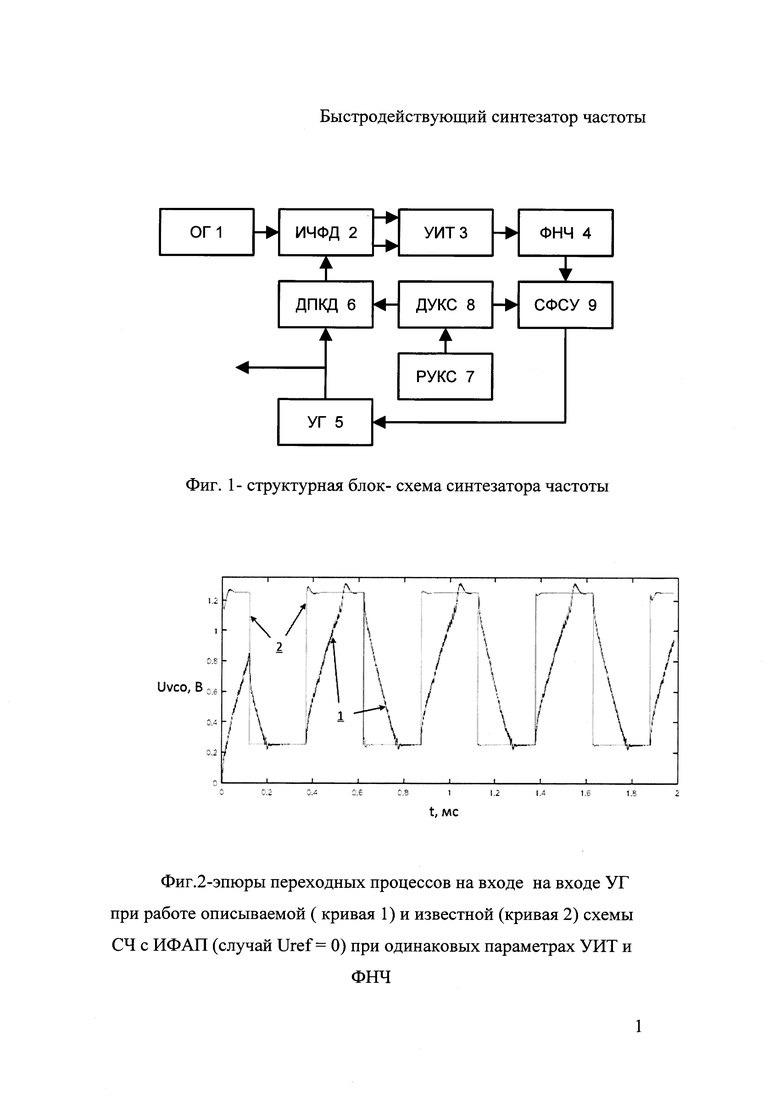

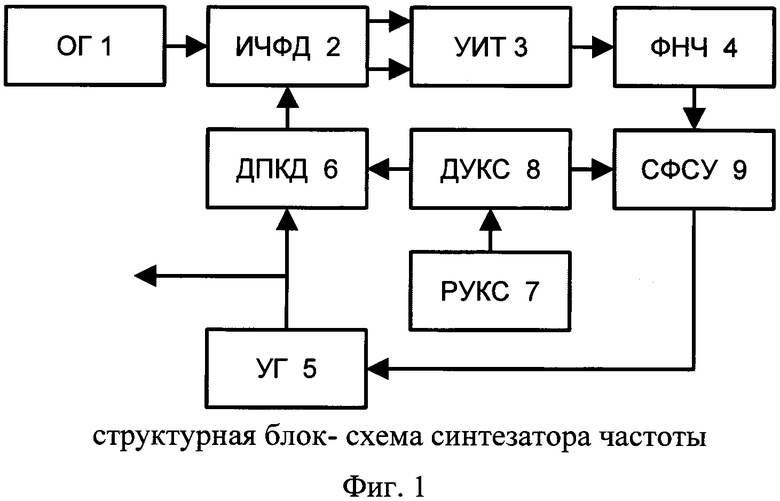

Изобретение поясняется чертежами, где на фиг. 1 представлена структурная блок-схема синтезатора частоты, на фиг. 2 приведены эпюры переходных процессов на входе УГ при работе описываемой и известной схем СЧ с ИФАП (случай Uref=0) при одинаковых параметрах УИТ и ФНЧ.

Синтезатор частоты в своем составе содержит опорный генератор 1 (ОГ 1), импульсный частотно-фазовый детектор 2 (ИЧФД 2), управляемый источник 3 тока (УИТ 3), фильтр 4 нижних частот (ФНЧ 4), управляемый генератор 5 (УГ 5), делитель 6 с переменным или дробно-переменным коэффициентом деления (ДПКД/ДДПКД 6), регистр 7 управляющего кодового слова (РУКС 7), дешифратор 8 управляющего кодового слова (ДУКС 8), сумматор-формирователь 9 сигнала управления (СФСУ 9).

Наряду с динамическим диапазоном, шагом сетки частот и спектральной чистотой генерируемого колебания, одним из главных показателей качества синтезатора частот является время переходного процесса при изменении генерируемой частоты. В традиционных синтезаторах косвенного синтеза время перестройки зависит от дискриминационной характеристики ИЧФД и динамических свойств петли ИФАП, изменение которых в пользу ускорения поиска и захвата частоты и фазы (расширение полосы ИФАП) неизбежно приводит к ухудшению спектральных характеристик генерируемого колебания. Имеется большое количество изобретений, улучшающих динамические характеристики ИФАП за счет оптимизации дискриминационной характеристики ИЧФД, коммутации дополнительных источников тока УИТ, а также изменения полосы пропускания ФНЧ, путем изменения его структуры в переходном режиме. Однако все эти решения, уменьшая время переходных процессов ИФАП, качественно не меняют алгоритм работы контура и не исключают процесс поиска и захвата.

Описываемая в настоящем изобретении структура синтезатора частот полностью устраняет частотное рассогласование в контуре ИФАП при переключении частоты синтезатора, исключает фазу поиска ИФАП по частоте, допуская лишь незначительное фазовое рассогласование в момент переключения.

Синтезатор частот работает следующим образом. При включении схемы ОГ 1 начинает вырабатывать опорное колебание с частотой Fref, которое подается на один из входов ИЧФД 2. ИЧФД 2 в зависимости от частотного и фазового рассогласования формирует на своих выходах Up и Dn сигнал управления УИТ 3 с широтно-импульсной модуляцией (ШИМ), знак рассогласования определяет выбор выхода "Up" или "Dn", а параметры ШИМ зависят от величины рассогласования. Сигналы, поступающие на входы УИТ 3, управляют коммутацией источников тока (зарядовой накачкой) для формирования выходного тока УИТ 3. Выходной ток УИТ3 поступает на вход ФНЧ 4, формирующего сигнал управления по частотно-фазовому рассогласованию Uerr. РУКС 7 содержит управляющее слово М, на основании которого ДУКС 8 формирует коэффициент деления N и опорный сигнал управления Uref. СФСУ 9 формирует сигнал управления путем сложения опорного сигнала управления Uref и сигнала управления по частотно-фазовому рассогласованию Uerr, Uvco=Uref+Uerr. На вход УГ 5 поступает сигнал Uvco=Uref+Uerr, УГ 5 вырабатывает колебание с частотой Fout=Fvco(Uvco). Контур управления замыкается через ДПКД/ДДПКД 6, на входы которого поступает колебание с частотой Fout и коэффициент деления N, частота выходного сигнала Fdiv=Fout / N. Для работы схемы обязательно выполнение следующих условий:

Fout(M)=Fref*N(M)

Fout(Uvco)=Fvco(Uvco)

Fout(M)=Fvco(Uref(M)), для Uerr=0

Uref(M)=F′vco(Fout(M))=F′vco(Fref*N(M)),

где F′vco - функция, обратная функции Fvco.

В этом случае, при задании кодового слова М1, соответствующего частоте Fout1, ДУКС 8 формирует Uref1, которое при малом Uref обеспечивает перестройку УГ 5 в окрестность частоты Fout1 за время, равное длительности переходного процесса УГ 5. При этом на вход ИЧФД 2 поступает сигнал, частота которого близка Fref, так как коэффициент деления N1=N(M1) также соответствует вышеприведенным уравнениям. Таким образом, на входе ИЧФД 2 оказываются сигналы близкой частоты со случайным фазовым рассогласованием. При дальнейшей работе небольшое фазовое рассогласование вызовет появление соответствующего сигнала Uerr, которое будет добавлено к Uref для компенсации фазового рассогласования. При переключении на частоту Fout2, соответствующую кодовому слову М2, ДУКС 8 скачкообразно изменит опорное напряжение на величину Uref2, что вызовет переключение УГ на частоту Fout2 и одновременное изменение коэффициента деления ДПКД/ДДПКД 6. Время переключения при этом не будет зависеть от разности частот dF=Fout1-Fout2 и будет существенно меньшее времени переходного процесса в контуре управления ИФАП, при сохранении режима синхронизма ИФАП.

Проиллюстрируем работу изобретения на следующем примере, пусть:

Fvco(U)=F0vco+Kvco*U, N(M)=M.

Fout=Fref*M

Uref(M)=F′vco(Fref*M)=(Fref*M-F0vco)/Kvco

На Фиг. 2 приведены эпюры переходных процессов на входе УГ 5 при работе описываемой и традиционной (известной) схем СЧ с ИФАП (случай Uref=0) при одинаковых параметрах УИТ 3 и ФНЧ 4. Из сравнения кривых видно, что использование предлагаемой схемы позволяет существенно сократить время переходных процессов.

Моделирование выполнялось для Fref=1 МГц, при периодическом скачкообразном изменении коэффициента деления N от 2 до 10. Видно, что для предложенного в изобретении СЧ с ИФАП при переключении удается полностью исключить режим поиска и захвата по частоте, характерный для СЧ ИФАП традиционной схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР СЕТКИ ЧАСТОТ НА БАЗЕ КОНТУРА ФАПЧ С КОМПЕНСАЦИЕЙ ПОМЕХ ДРОБНОСТИ | 2012 |

|

RU2491713C1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2013 |

|

RU2530248C1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2483434C1 |

| Устройство эквивалентного умножения емкости конденсатора петлевого фильтра контура ФАПЧ | 2015 |

|

RU2612573C1 |

| Устройство эквивалентного умножения емкости конденсатора петлевого фильтра контура ФАПЧ | 2022 |

|

RU2783664C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Синтезатор частот | 1988 |

|

SU1698989A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2440668C1 |

Изобретение относится к радиотехнике и может использоваться в синтезаторе частоты с импульсной фазовой автоподстройкой частоты. Достигаемый технический результат - повышение быстродействия при смене рабочей частоты. Быстродействующий синтезатор частоты содержит опорный генератор, частотно-фазовый детектор, управляемый источник тока, фильтр нижних частот, сумматор-формирователь сигнала управления, управляемый генератор, делитель с переменным или дробно-переменным коэффициентом деления, регистр управляющего кодового слова, дешифратор управляющего кодового слова. 2 ил.

Быстродействующий синтезатор частоты, содержащий опорный генератор, подключенный через первый вход импульсного частотно-фазового детектора к управляемому источнику тока, имеющему входы в соответствии с фазовой разностью опорного и сигнала частоты обратной связи, выход управляемого источника тока подключен к входу фильтра нижних частот, выход которого соединен через сумматор-формирователь сигнала управления с входом управляемого генератора, выходы управляемого генератора выведены на первый вход делителя с переменным или дробно-переменным коэффициентом деления и на потребителя, выход делителя с переменным или дробно-переменным коэффициентом деления подключен к второму входу импульсного частотно-фазового детектора, отличающийся тем, что в синтезатор частоты введен регистр управляющего кодового слова, соединенный с дешифратором управляющего кодового слова, при этом первый выход дешифратора управляющего кодового слова соединен с вторым входом сумматора-формирователя сигнала управления, а второй выход дешифратора управляющего кодового слова соединен с вторым входом делителя с переменным или дробно-переменным коэффициентом деления.

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| СХЕМА И СПОСОБ ФАЗОВОЙ СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1994 |

|

RU2127485C1 |

| СИНТЕЗАТОР ДРОБНЫХ КОГЕРЕНТНЫХ ЧАСТОТ С ФАЗОВОЙ СИНХРОНИЗАЦИЕЙ | 1998 |

|

RU2208904C2 |

| US 6366174 B1, 02.04.2002 | |||

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

Авторы

Даты

2016-11-20—Публикация

2015-10-14—Подача