Настоящее изобретение относится к вычислительной технике и дискретной автоматике и может быть использовано при проектировании высоконадежных процессоров, систем управления мехатроникой, специализированных средств обработки информации в особо ответственных технических системах и в системах управления опасными технологическими процессами в экстремальных условиях.

Известны микропрограммные автоматы управления (МПА) с самоконтролем, описанные как в учебно-научной литературе [1-4, 6-7, 9], так и в изобретениях [11] СССР 1365986, 2042189, 2042190 и патентах РФ №63588 БИ №15, 2007 г. и USA №3634665 System use of self-testing cheking circuits / Carter W.C.

В представленных аналогах производится проверка тем или иным способом правильности перехода автомата из предыдущего a(t) в последующее a(t+1) состояние, где t - настоящий, (t+1) - последующий моменты времени после импульса синхронизации.

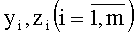

Известен патент РФ №63588 БИ №15, 2007, обеспечивающий контроль МПА на входе и выходе основной комбинационной схемы (F1), преобразующей конкатенацию переменных α1α2…αqx1x2…xm при состоянии a(t) в код y1y2…ym при состоянии a(t+1), где α1α2…αq множество {α} входных логических сигналов автомата, получаемых от операционного устройства (ОУ), являющегося объектом управления; {х} - x1x2…xm - двоично-позиционный (ДИК) или любой другой код a(t); y1y2…ym - код a(t+1).

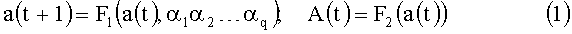

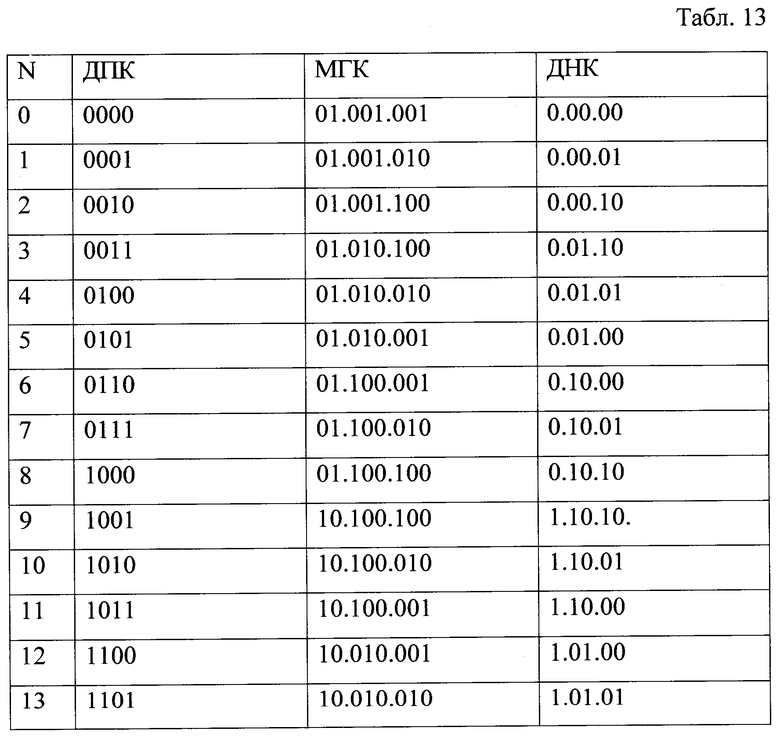

По патенту РФ №63588 -{y} - модифицированный геометрический код (МГК); {х} - двоичный непозиционный код (ДНК). Аналитическая запись работы имеет вид:

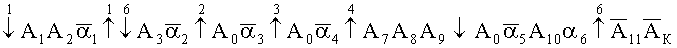

где A1, A2,…, Aк - множество {A} - выходных команд МПА для ОУ.

F2 - система булевых функций, которая определяет номера выходных команд только на основании кода x1x2…xm, тогда как код y1y2…ym состояния a(t+1) определяется системой булевых функций F1, зависящих как от x1x2…xm, так и от α1α2…αq. Главным объектом проверки правильности функционирования автомата является схема F1 ввиду ее наибольшей сложности в структуре МПА.

Устройство по патенту РФ №63588 может эффективно обнаруживать одиночные ошибки в каждой из трехразрядных групп выходного кода {y}, но не обнаруживает ошибки двух и большей кратности в одной группе. Другим недостатком самоконтролируемого автомата является высокая сложность схемы F1, так как используются коды с фиксированным числом единиц (МГК) и в качестве адреса схемы F1 используется полная конкатенация α1α2…αq совместно с x1x2…xm, при этом величина m для МГК в 1.5÷2 раза больше величины m, для ДНК в неконтролируемом автомате.

В учебной и научной литературе известен способ обеспечения самоконтролируемости автомата фактически за счет дублирования основной комбинационной схемы, преобразующей код a(t) в код a(t+1) при условиях α1α2…αq (см. работу [3] стр.242). В этом случае одна схема работает в прямом коде, а вторая в обратном. Сложность обеих схем одинакова и в оценках объема ПЗУ или ПЛМ в битах V=m2m+q. Например, при m=5 и q=12 (не очень сложный автомат) величина V=5·217=5·27·210≈650 кб=0,65 Мбит. При m=6, q=16 объем только одного ПЗУ составит V=6·222=6·22·210·210=24 Мбит. Именно это устройство [3] и является наиболее близким к предлагаемому изобретению, т.к. наличие двух схем позволяет фиксировать неисправность как тактовую, не классифицируя факта одиночной или многократной ошибки.

Целью настоящего изобретения является упрощение конструкции за счет снижения сложности комбинационных схем автомата при сохранении свойства самоконтролируемости. Далее для краткости самоконтролируемый автомат управления будет именоваться просто автоматом.

В структурной схеме прототипа используется операционное устройство ОУ(1), которое является объектом управления, регистр для запоминания логических условий, два регистра памяти для хранения кодов состояний a(t) и a(t+1) с парафазной связью между ними, комбинационные схемы (первая и вторая) принятия решений и блок синхронизации.

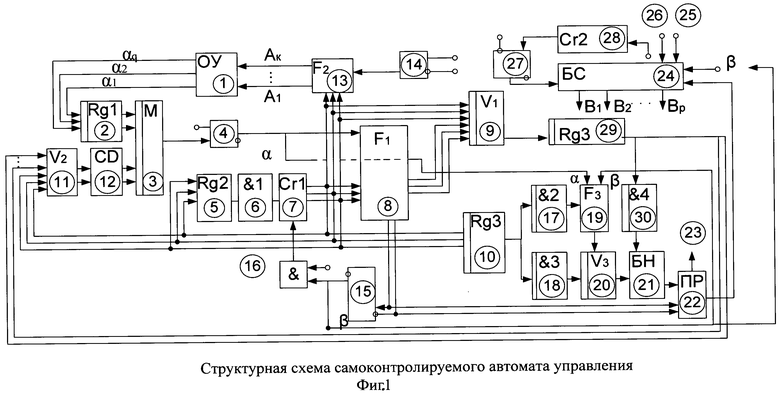

Предлагаемый самоконтролируемый автомат управления на фиг.1 состоит из операционного устройства ОУ (1), выходы которого через первый запоминающий регистр Rq1 (2) связаны с информационными входами мультиплексора М (3), выход которого связан с единичным входом первого триггера Tp1 (4); первая последовательная цепь блоков состоит из второго запоминающего регистра памяти Rq2 (5), блока схем И (6) для параллельной парафазной передачи результата на первый счетчик Сч1 (7), выходы которого связаны параллельно со входами первой комбинационной схемы F1 (8), первого блока схем ИЛИ1 (9), третьего регистра памяти Rq3 (10), второго блока схем ИЛИ2 (11), связанного через блок кодирования CD (12) с адресными входами мультиплексора М (3), выходы первого счетчика связаны со входами второй комбинационной схемы F2 (13), имеющей управляющий вход от второго триггера ТР2 (14), причем дополнительный вход первой комбинационной схемы F1 (8) связан с выходом первого триггера Tp1 (4), а выходы первой комбинационной схемы связаны со вторыми входами первого блока схем ИЛИ1 (9), причем первая комбинационная схема F1 (8) имеет дополнительный парафазный выход, связанный со входами третьего триггера Тр3 (15), единичный выход которого через элемент И (16) связан со счетным входом первого счетчика Сч1 (7); выходы третьего регистра памяти Rq3 (10) параллельно связаны со входами второго и третьего блоков схем И2 (17), И3 (18), выходы которых связаны соответственно со входами третьей комбинационной схемы F3 (19) и первыми входами третьего блока схем ИЛИ3 (20), имеющего связь с выходами третьей комбинационной схемы F3 (19), выходы третьего блока схем ИЛИ3 (20) через блок сравнения БН (21) и блок принятия решений ПР (22), имеющий внешнюю клемму (23), связаны с первым входом блока синхронизации БС (24), имеющего внешние клеммы ПУСК (25) и Останов (26), причем второй вход блока синхронизации БС (24) соединен с единичным выходом третьего триггера Тр3 (27), имеющего связь по единичному входу с выходом переполнения второго счетчика Сч2 (28); выходы первого блока схем ИЛИ1 (9) через четвертый запоминающий регистр Rq4 (29) связаны со входами четвертого блока схем И4 (30), входами второго регистра памяти Rq2 (5) и вторыми входами второго блока схем ИЛИ2 (11), при этом выходы четвертого блока схем ИЛИ4 (30) связаны со вторыми входами блока сравнения БН (21), а управляющие входы блока принятия решений ПР (22) связаны с дополнительным парафазным выходом первой комбинационной схемы F1 (8), единичный выход второго триггера Тр2 (15) связан с третьим входом блока синхронизации БС (24), причем блок синхронизации БС (24) имеет выходы микрокоманд синхронизации В1В2…Bp, связанные со всеми управляющими входами самоконтролируемого автомата, причем единичные выходы первого (α) и второго (β) триггеров Tp1 (4) и Тр2 (15) связаны с управляющими входами третьей комбинационной схемы F3 (19).

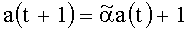

Функционирование самоконтролируемого автомата основано на последовательном переходе из состояния a(t) в состояние a(t+1), код которого y1y2…ym находится через первую комбинационную схему F1 (8) по адресу кода a(t) - x1x2…xm и значению αj(t), выбранному мультиплексором по коду a(t). Параллельно на основе конкатенации, т.е. «сводного» кода αja(t), находится код a(t+1) и αj(t+1) в третьей комбинационной схеме F3 (19) и эти два кода y1y2…ym (F1) и y1y2…ym (F3 (19)) сравниваются между собой в блоке БН (21). Для уменьшения объема схемы F1 (8) в графе алгоритма управления операционным устройством выделен самый длинный непрерывный путь от начальной до конечной вершины, которому сопоставлен счетчик с кодом Грея (Сч1 (7)). В коде Грея

Поскольку в предлагаемом изобретении имеются три варианта вычисления кода y1y2…ym, а перед этим идет выбор αj∈{α}, то синхронизация работы самоконтролируемого автомата невозможна только на основе двух тактов времени

Прежде чем детально описывать функционирование предлагаемого патентуемого автомата, следует рассмотреть структурную организацию нетиповых и некоторых типовых составляющих его схем.

Операционное устройство ОУ (1) не является неотъемлемой частью автомата, т.к. это объект управления, но оно включено в состав блоков с целью показа прямого и обратного взаимодействия самоконтролируемого автомата в системе управления.

На фиг.1 все типовые блоки (регистры памяти, блоки схем «И», «ИЛИ», мультиплексор) обозначены в виде прямоугольников с двойной линией по левой грани, а нетиповые блоки (F1 (8), F2 (13), F3 (19), CD (12), ПР (22), БН (21), БС (24)) обозначены в виде простых прямоугольников.

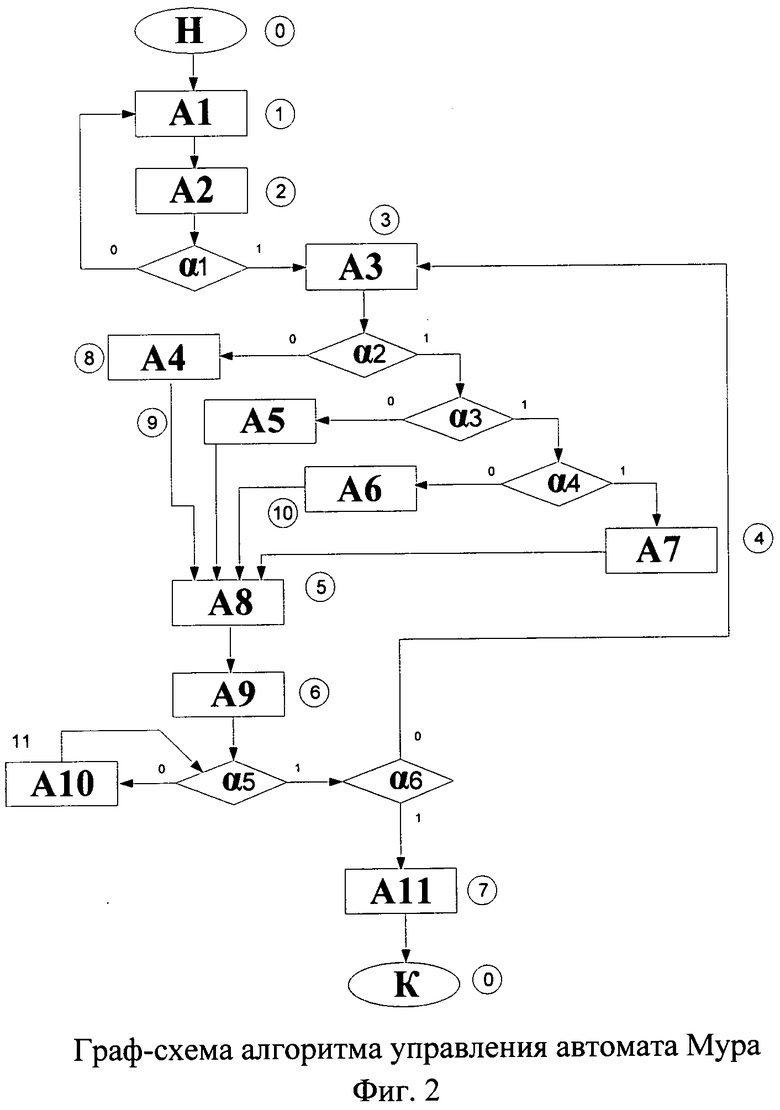

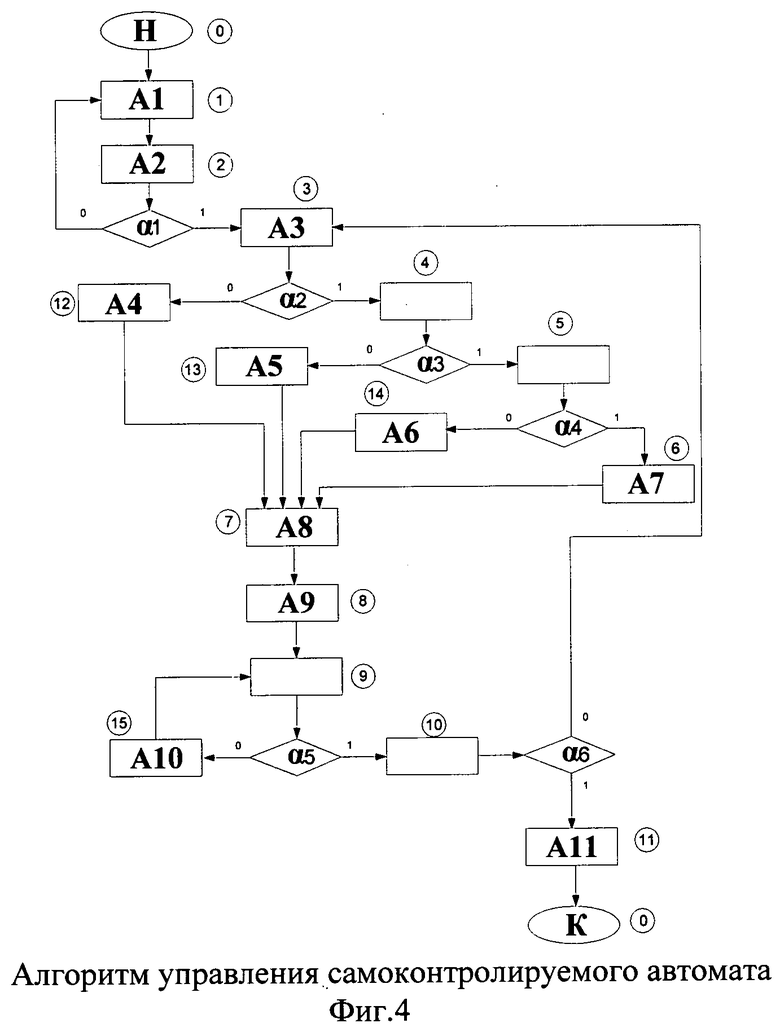

Для описания структурных схем нетиповых блоков (F1 (8), F3 (19), ПР (22), БС (24), БН (21)) потребуется детальное описание предлагаемого метода самоконтроля, основанного на способе уменьшения затрат оборудования, требуемого для реализации F1 (8) за счет введения мультиплексора М (3) после специального преобразования заданной граф-схемы алгоритма(ГСА), являющейся исходной для проектирования автомата. Пример заданного для реализации через МПА алгоритма (ГСА) приведен на фиг.2. В типовых структурах МПА система булевых функций для схемы F1 (8) определяется [1-4] на основе перехода от ГСА фиг.2 к графу переходов фиг.3.

В предлагаемом изобретении первая комбинационная схема F1 (8) реализуется как постоянное запоминающее устройство (ПЗУ) или программируемая логическая матрица (ПЛМ) с числом входов (m+1) и выходов (m+2). Причем m входов представлены кодом состояния автомата x1x2…xm, а (m+1)-й вход - это одно из αj∈(α1α2…αq), соответствующее состоянию a(t).

Некоторые αj будут соответствовать безусловному переходу, т.е. α0=0. Выходному коду y1y2…ym приписано также значение ym+1, соответствующее указанию необходимости выдачи сигнала β для увеличения содержимого кода счетчика на «1», и ym+2, соответствующего признаку (r) наличия противоречия в определении кодов y1y2…ym третьей комбинационной схемой F3 (19). Правило определения значения признака (r) определяется далее. Для того чтобы был возможен такой режим работы автомата и такая конструкция F1 (8), заданную граф-схему алгоритма (ГСА) для реализации автомата необходимо преобразовывать по следующим правилам.

1) Если в граф-схеме алгоритма управления операционным устройством ОУ (1) имеются прямые переходы от αi к αj без промежуточных операторов действия Aj∈{А1А2…Ak}, то между ними ставится пустой оператор А0, т.е. такой, которому не соответствует выдача команды управления Aj из множества {А}.

2) Пустой оператор ставится также перед любым αj∈{α}, если к нему идет передача управления от нескольких других операторов.

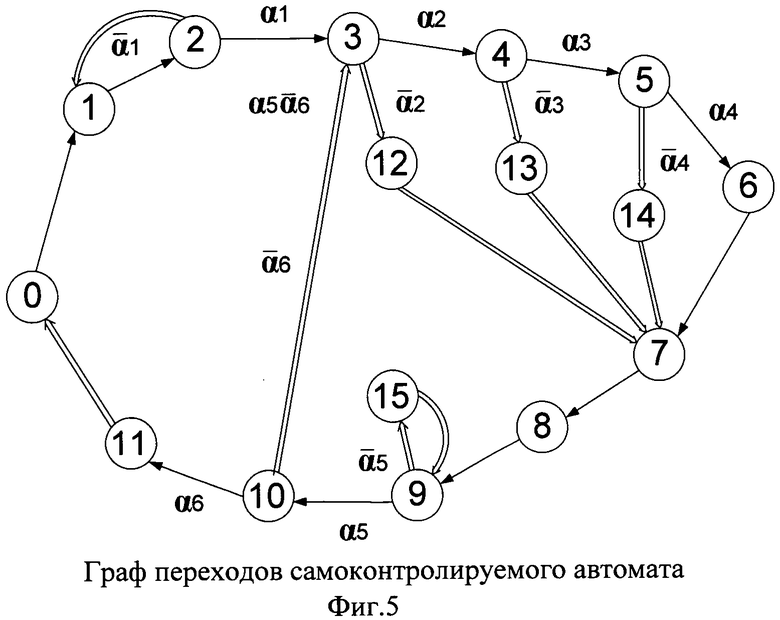

По граф-схеме фиг.4 получим граф переходов фиг 5, по которому и будет проектироваться автомат управления. Как видно из графа фиг.4, каждым номером a(t) может быть сопоставлен свой номер логического условия:

а(2) - α1

а(3) - α2

а(4) - α3

а(5) - α4

а(9) - α5

а(10) - α6

Тогда для определения номера j каждого αj потребуется преобразовать код a(t) в соответствующий j код.

Может быть использован вариант без использования специального преобразователя кодов (обозначен на фиг.1 как блок кодирования CD (12)), но тогда логические сигналы ОУ (1), соответствующие логическим условиям αj, соединяются со входами мультиплексора М (3) специальным образом т.е. для примера:

α0=0 ко входу 0,

α1 ко входу 2, α2→3, α3→4, α4→5, α5→9 и α6→10.

Но для этого требуется выполнить преобразования граф-схемы алгоритма по пункту 3.

Пункт 3) выполняется лишь при малом числе состояний в автомате (m<5). При m≥5 используется вариант с блоком кодирования.

3) В граф-схеме алгоритма после преобразования 1) и 2) для каждого αj∈{α} заменяется номер на тот, который соответствует номеру a(t), т.е номеру a(t), стоящему перед проверкой значения αj. На фиг.2 представлен пример заданной не сложной граф-схемы алгоритма управления. На фиг.3 представлен соответствующий граф-схеме алгоритма граф переходов автомата, полученный известным способом [1,3]. На фиг.4 представлена модифицированная по правилам 1), 2), 3) граф-схема алгоритма управления и соответствующий ей граф переходов (фиг.5). На графе фиг.5 отмечены двойными стрелками переходы, не относящиеся к самому длинному пути, которые и необходимо реализовать через схему F1 (8), а остальные через счетчик с кодом Грея.

Производится перенумерация логических условий так, чтобы номер совпадал с номером предыдущего оператора действия. На фиг.5 новые номера около αj не указаны, т.к. они совпадают с номерами предыдущего состояния.

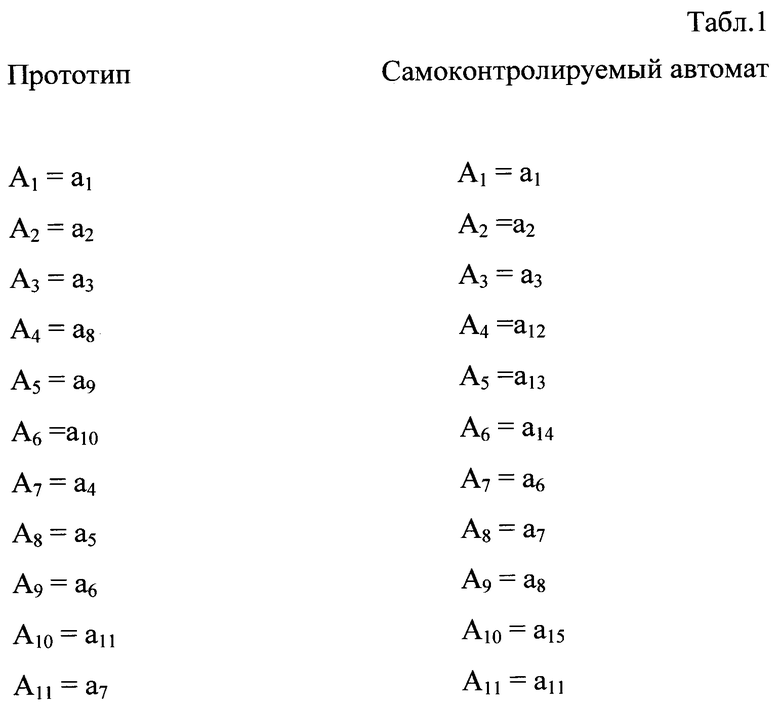

Сравнение фиг.2 и 4 позволяет убедиться в том, что в прототипе и предлагаемом автомате причинно-следственная последовательность выдачи операторов Aj∈{А} будет той же. Действительно, несмотря на некоторое изменение номеров состояний (число состояний в новом автомате увеличивается за счет введения пустых операторов) системы булевых функций для сигналов A(t) будут теми же, только Aj соответствуют состояниям с другими номерами (табл.1).

Следовательно, комбинационная схема F2 как в прототипе, так и в предлагаемом автомате будет состоять из дешифратора кода x1x2…xm и схем «ИЛИ» для « сборки» выходов дешифратора, соответствующих одной и той же команде. В примере необходим четырехвходовый дешифратор и нет необходимости в схемах «ИЛИ», т.к. в граф-схеме алгоритма нет повторяющихся команд.

Графы автоматов прототипа и предлагаемого изобретения отличаются двумя аспектами:

- логические переходы осуществляются по тем же логическим условиям, но с другими номерами,

- в новом графе переходов предлагаемого МПА переход из одной вершины, соответствующей состоянию автомата a(t), в другую, соответствующей состоянию a(t+1), возможен как безусловный, так и условный, но только по одному (единственному) логическому условию, номер которого совпадает с номером предыдущего состояния a(t). Тогда как в графе прототипа из одной вершины возможны переходы к одной вершине (безусловный переход); к двум или нескольким вершинам графа, соответствующим разным a(t+1). Такие переходы в графе помечены несколькими логическими условиями. В примере (фиг.3) из шести (α1α2α3α4α5α6) логических условий некоторые переходы из a(t) помечены тремя символами. А это значит, что в прототипе в качестве адреса для комбинационной схемы F1 (ПЗУ или ПЛМ) необходимо использовать всю комбинацию α1α2…αqx1x2…xm, где x1x2…xm двоичный код a(t).

В предлагаемом самоконтролируемом автомате адрес комбинационной схемы определяется значением единственного αj, номер (j) которого соответствует коду y1y2…ym.

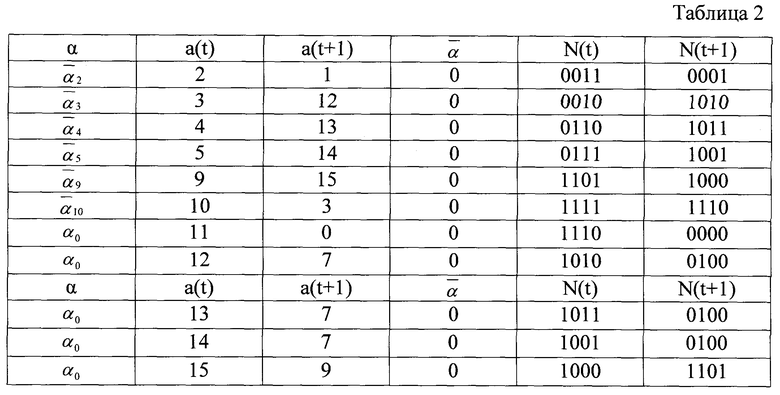

Правила переходов a(t)→a(t+1) для вершин, не расположенных на замкнутом цикле (кроме 1, 2, …, 11), представлены в виде табл.2, по которой могут быть выписаны булевы функции y1y2y3y4 на основании N(t+1) по значению α(t) и коду N(t). Эта таблица 2 является основной для записи содержимого реализации F1 (8) на ПЗУ, если будет использован метод прямого считывания {y} по конкатенации α(t){x}.

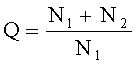

Представленные преобразования по правилам 1), 2), 3) позволяют получить новую граф-схему алгоритма, эквивалентную исходной по функциональным результатам, но быстродействие реализации алгоритма снизится в Q раз, где

N1 - число операторов действия (Aj,

N2 - число пустых операторов на этом же пути.

Для рассматриваемого примера N1=7, N2=4,

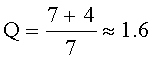

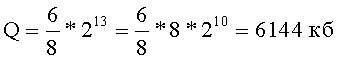

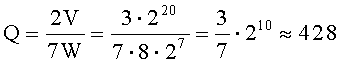

Последняя запись участка граф-схемы алгоритма от А1 до А11 представлена в виде ЛСА - логической схемы алгоритма. Правила перехода от граф-схемы (ГСА) к ЛСА даны в [4]. Однако снижение общего быстродействия выполнения всей программы автомата по заданной граф-схеме фиг.2 не является существенным для поставленной цели уменьшения общих затрат оборудования при обеспечении более полного самоконтроля автоматов. В принципе и быстродействие автомата может быть тем же, если ввести режим прерывания выдержки времени на реализацию Aj, если Aj - пустой оператор. Для рассматриваемого упрощенного примера граф-схемы алгоритма фиг.4 величины m=4, q=6. Тогда для прототипа V=m2m+q=4·210=212=4096 б. Для предлагаемого автомата Vm=(m+2)·2m+1=6·25=192 б. Выигрыш в объеме оборудования Q составит

Например, при числе состояний N≤64 для m=6 и q=14 получим

V=6*220=6 Мб

W=8*27=210=1 кб

Для такого варианта потребуется комбинационная схема F1 (8) в виде ПЗУ (ПЛМ) с объемом в шесть тысяч раз меньше, чем для прототипа.

Для m=6, q=16 величина Q=24576. Такое преимущество структурной организации предложенного автомата позволяет использовать новый способ самоконтроля, действующий только для предлагаемой структуры автомата, т.е. при организации автомата с выделенным мультиплексором и преобразованной граф-схемой алгоритма управления. Для классических структур МПА предлагаемый способ контроля в принципе нереализуем.

Третья комбинационная схема F3 (19) строится по следующему принципу:

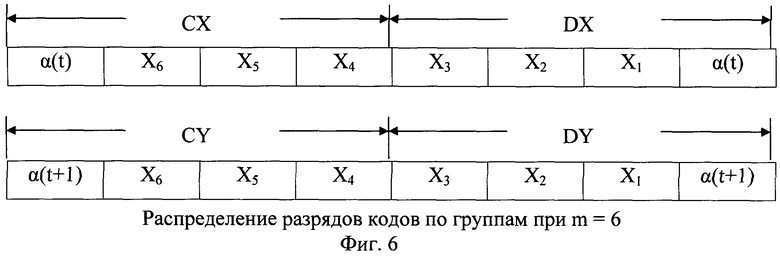

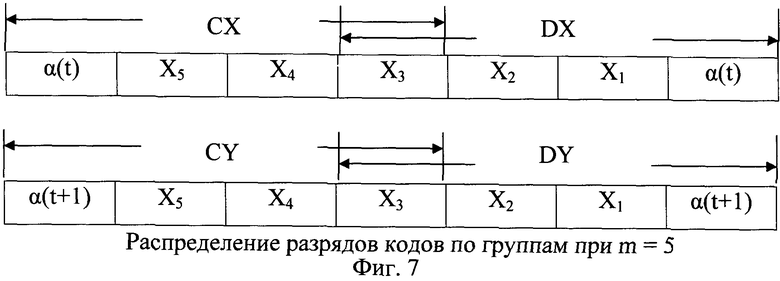

- рассматриваются совместно коды a(t) и a(t+1), т.е. x1x2…xm и y1y2…ym и значения αj для a(t) и для a(t+1), которые естественно могут быть разными (табл.2). Коды x1x2…xm и y1y2…ym делятся на две группы по три разряда в каждой и к каждой группе приписывается значение αj. Для группы {х} - αj, соответствующее a(t), а для {y} - значение αj(t+1).

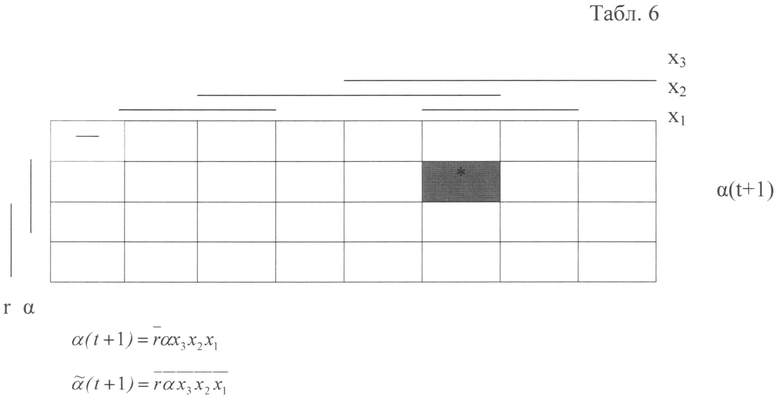

К коду x1x2…xm до младшего и после старшего разряда дописывается α(t), соответственно для y1y2…ym дописывается α(t+1) (фиг.6).

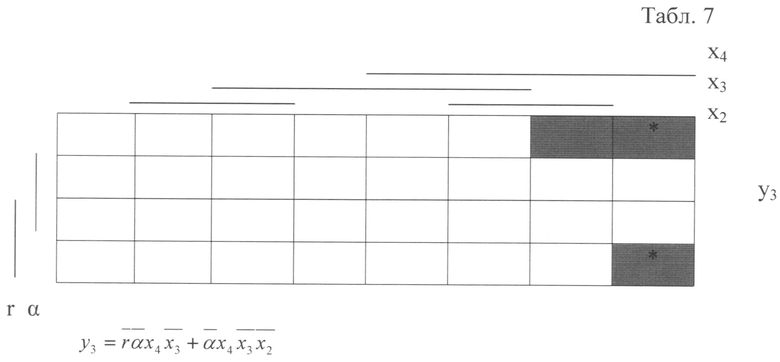

Получившаяся конкатенация разрядов делится на группы СХ, DX и CY, DY. Для m=6 в каждой группе по 3 разряда, для m=4 по 2 разряда. Для нечетного значения m группы формируются с «перекрытием» одного разряда, т.е. разряд х3(у3) входит как в одну, так и в другую группу (фиг.7). Случай m=3 не представляет интереса, т.к. в связи с простотой схемы F1 можно использовать другие известные решения для контроля, хотя в принципе предлагаемый метод и схемная реализация контроля применимы и для этого случая, т.к. при новой структуре МПА получаются две трехразрядные группы по два разряда с {х} и разряд α(t) с перекрытием разряда х2(у2).

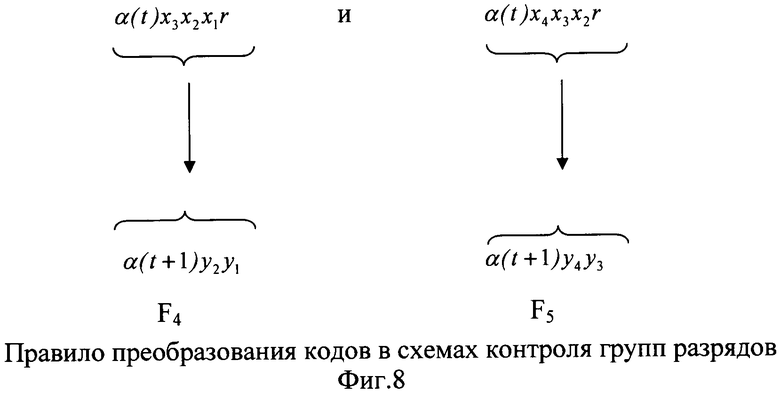

Для данного примера граф-схемы алгоритма фиг.4 необходимо образовать две группы зависимостей (фиг.8).

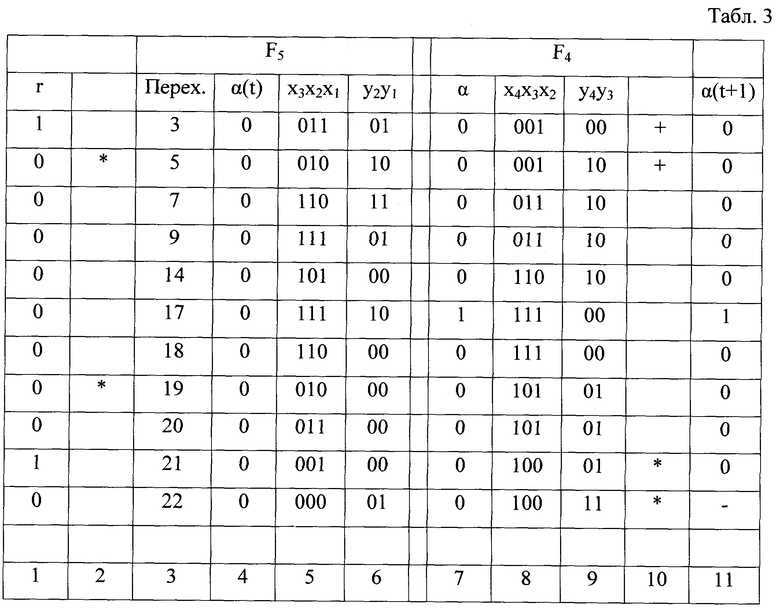

Функции F5, F4 блока F3 (19) выписываются по табл.3, полученной на основании табл.2. для переходов, соответствующих признаку β=0. Значение признака r определяется по таблице 3 и устанавливается таким (r=1 или r=0), чтобы различались те коды переходов a(t)→a(t+1) в соответствующей группе F5, F4 (F3 (19)), которым сопоставлены разные ответы для одних и тех же адресных групп α(t) xixi-1xi-2. Как видно из табл.3, в примере для переходов (3) и (5) функции F4 ответы по кодам 0001 и по кодам 0100 противоречивы, а для функции F3 такая ситуация имеет место для кода 0010.

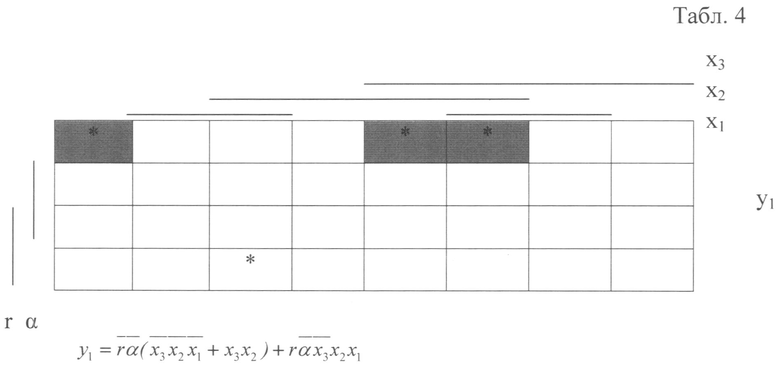

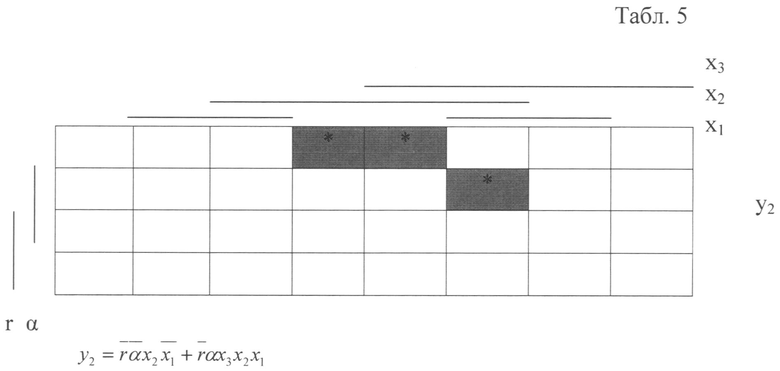

Противоречие заключается в том, что одним и тем же значениям переменных α(t) xixi-1x1 соответствуют разные значения функций. Такая ситуация возникает вследствие использования для контроля только части, а не полного кода a(t). Противоречивые ответы помечены символами * и + в столбцах (2) и (10) таблицы 3, а значения r для разрешения противоречий определены в столбце (1). Знаком прочерк (-) отмечено неопределенное значение α(t+1). В соответствии с табл.3 в таблицах 4-9 представлены значения y1, у2, α(t+1), у3, у4, α(t+1) в булевом пространстве [3, 4] переменных r, α, х3, х2, x1 и r, α, x4, х3, х2 с явно выраженными булевыми функциями F5(y1y2α(t+1)) и F4(у3у4α(t+1)) в виде подписей под таблицами.

Этот способ нахождения y1y2…ym через схему F3 (19) реализуется только для β=О. При β=1 работает счетчик Cr1 (7) с прибавлением (+1) в коде Грея, для которого коды a(t) и a(t+1) должны отличаться только на одну «1». В связи с тем, что третья комбинационная схема F3 (19) представляет из себя простую комбинационную схему, состоящую из двух схем F4 и F5, реализация которых по таблицам 4-9 не представляет каких-либо трудностей по методикам [1-4], ее детальная структура на элементах типового логического базиса не приводится.

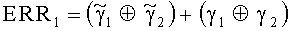

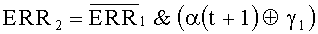

По предложенному способу проверка правильности вычисления y1y2…ym осуществляется сравнением кодов y1y2…ym, вычисленных схемой F1 (8) и схемами контроля как конкатенации выходов F5 и F4 (F3 (9)). Одновременно этот метод через вычисление α(t+1) дает возможность проверки верности выбранного значения α(t) для следующего такта. Несовпадение вычисленного α(t+1) и α(t) от мультиплексора будет свидетельствовать об ошибке либо схем контроля F5 и F4, либо мультиплексора. В третьей комбинационной схеме F3 (19) вычисляется α(t+1) независимо в схемах F5 (обозначается γ2) и в схеме F4 (обозначается γ1). А кроме того, определяется также тот факт, что значение для α(t+1) не может быть определенно, т.к. подается с Rg1 (2) на информационный вход мультиплексора М (3) и может быть равным как «0», так и «1».

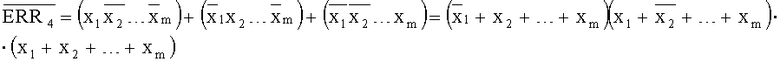

Эти неопределенные значения γ1γ2 обозначим

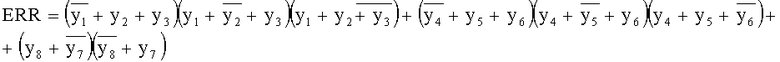

Ошибка также будет зафиксирована и в том случае, если не совпадут коды y1y2…ym (F3 (19)) и Rg3 (29), которые обозначим z1z2…zm, т.е.

Общая ошибка определяется в виде ERR=ERR1+ERR2+ERR3+ERR4, где символом (+) по-прежнему обозначена логическая операция «ИЛИ».

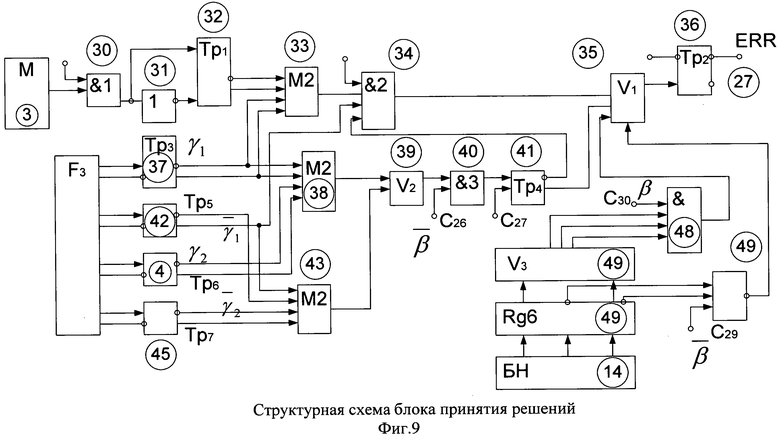

Блок принятия решений ПР (22) состоит (фиг.9) из последовательной цепи элементов первого элемента И (30), первый вход которого связан с выходом мультиплексора элемента НЕ (31), связанного с нулевым входом первого триггера Тр (32), единичный вход которого связан с выходом элемента И (30), оба выхода триггера поданы на первый элемент неравнозначности М2 (33), выход которого через второй элемент И (34) и первый элемент ИЛИ (35) связан с единичным входом второго триггера Тр2 (36), выход которого соединен с внешней клеммой ERR (23), входы третьего триггера Тр3 (37) связаны с входами первого М2 (33) и второго М2 (38) элемента неравнозначности, выходы которого через второй элемент ИЛИ (39), третий элемент И3 (40) связаны с единичным входом четвертого триггера Тр4 (41), единичный выход которого связан со вторым входом второй схемы И (34), а нулевой выход четвертого триггера Тр4 (41) связан со вторым входом первого элемента ИЛИ (35); пятый триггер Тр5 (42) связан своими выходами с третьим элементом неравнозначности М2 (43), а единичный выход пятого триггера Тр5 (42) связан с третьим входом второго элемента И2 (34). Выход третьего элемента неравнозначности М2 (43) связан со вторым входом второго элемента ИЛИ (39); шестой и седьмой триггеры Трб (44), Тр7 (45), входами связаны с выходами комбинационной схемы F3 (19), причем выходы шестого триггера Трб (44) связаны с третьим и четвертым входами второго элемента неравнозначности М2 (38), а выходы седьмого триггера Тр7 (45) связаны с третьим и четвертым входам третьего элемента неравнозначности М2 (43). При этом в блоке принятия решений ПР (22) имеется шестой регистр памяти Rq6 (46), связанный своими входами с блоком неравнозначности при этом выходы которого через БН (14), блок элементов ИЛИ3 (47), четвертый элемент И (48) связаны с третьим входом первого элемента ИЛИ 1 (35), а нулевые выходы шестого регистра памяти Rq6 (46) через элемент И-НЕ (49) связаны с четвертым входом первого элемента ИЛИ1 (35). Элементы (30), (40), (41), (34), (49), (48) и (36) имеют соответствующие синхровходы С25-С31 от блока синхронизации БС (24). Функционирование блока принятия решения описано ранее.

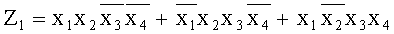

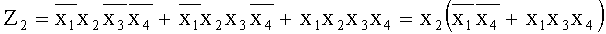

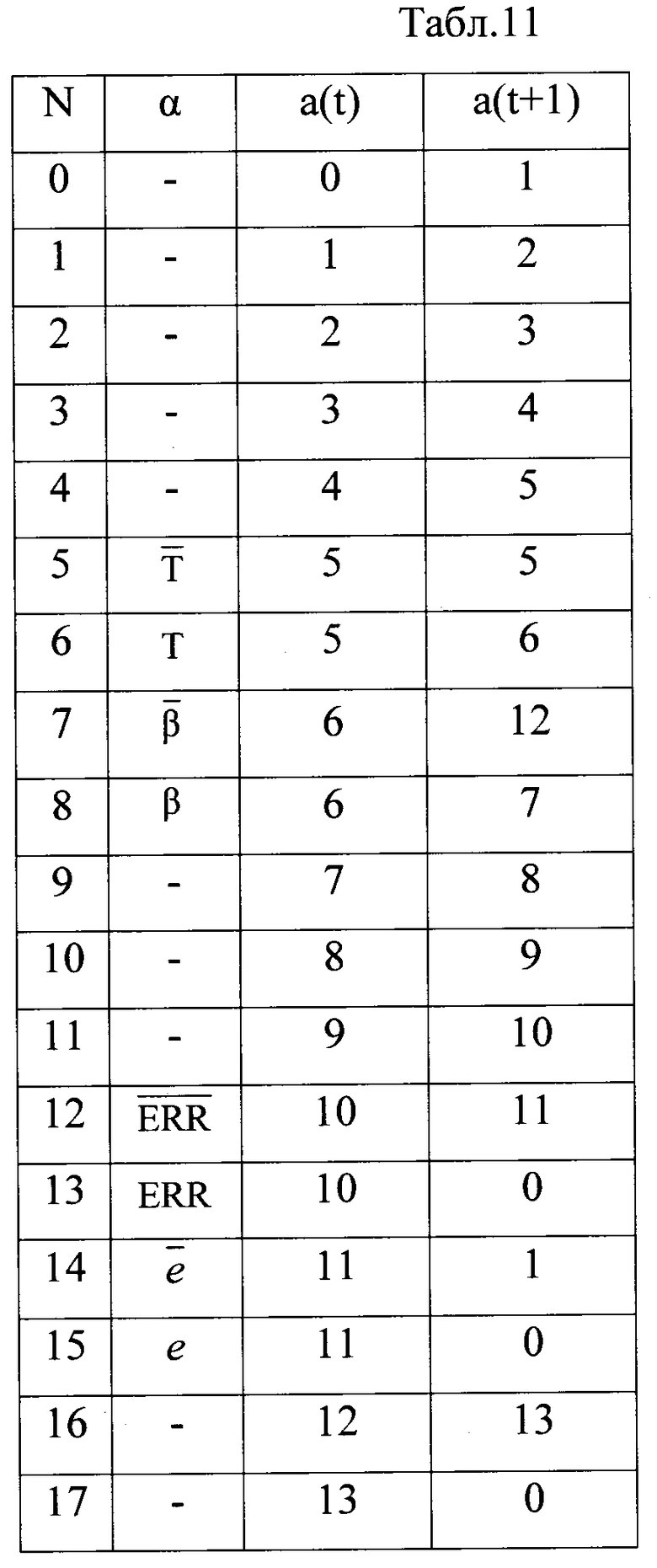

Блок кодирования CD (12) преобразует номера (коды) состояний a(t), при которых осуществляется проверка логических условий в номера (коды) адреса мультиплексора для выбора соответствующего αj∈{α}, по графу фиг.5 и табл.11 получим табл.12 N(t) в коде Грея, a R(t) в двоичном позиционном коде, т.к. это адрес мультиплексора.

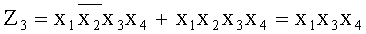

Из табл.12 для приведенного примера получим:

Реализация булевых функций для вычисления Z1, Z2, Z3 тривиальна.

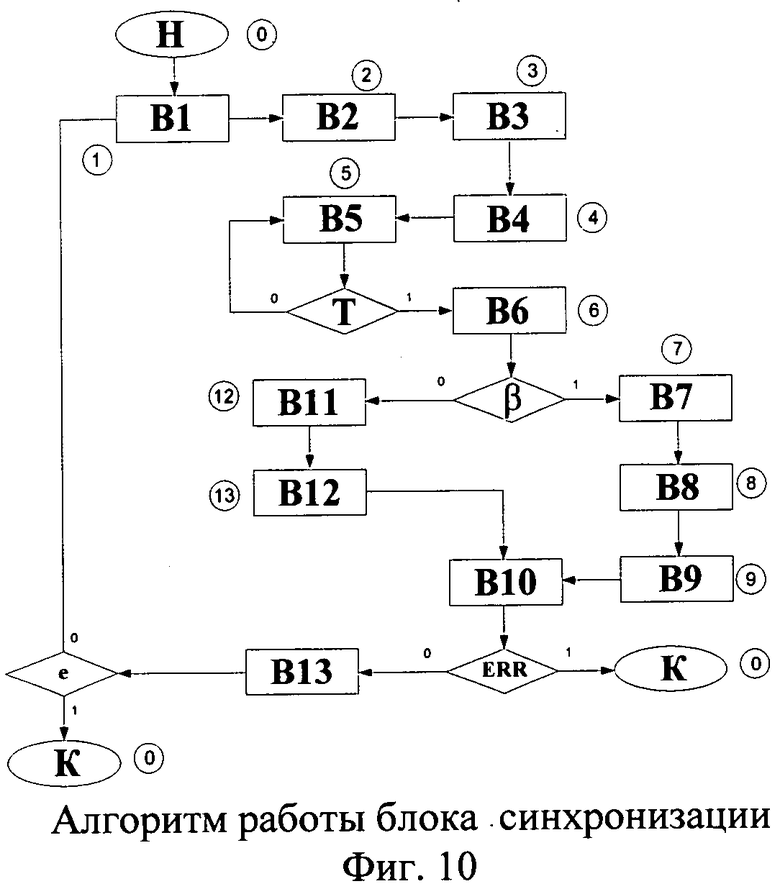

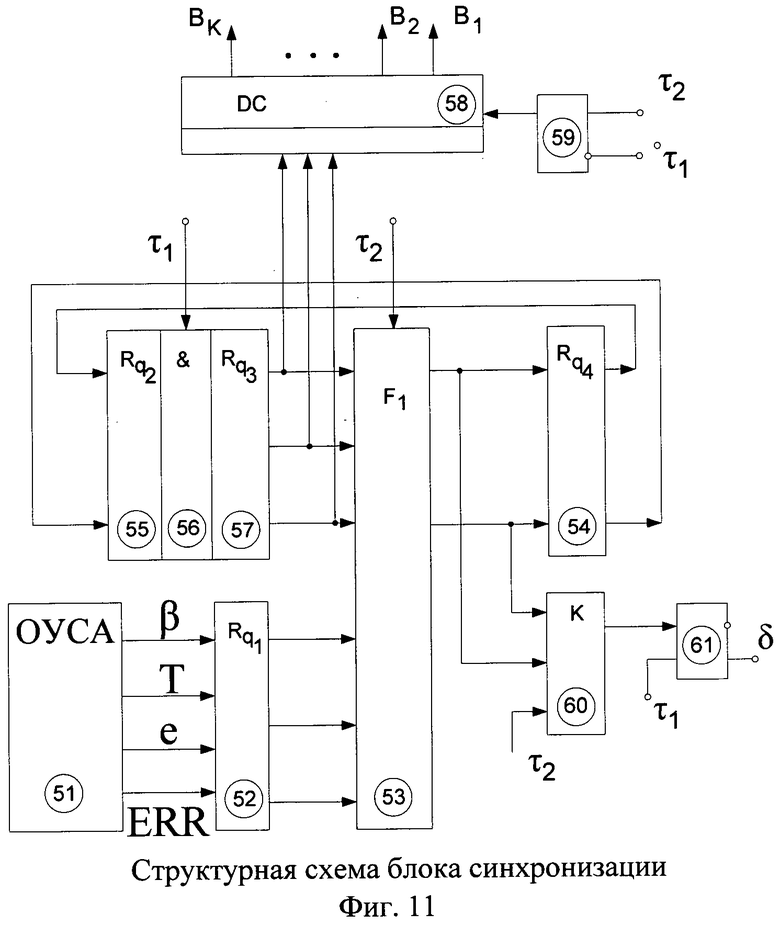

Формализованное описание последовательности функционирования самоконтролируемого автомата представлено в виде граф-схемы алгоритма работы блока синхронизации БС (24) на фиг.10. Расшифровка команд синхронизации приведена в табл.10. Структурная схема приведена на фиг.11 с тактирующим блоком (фиг.12). Блок синхронизации БС (24) может быть реализован по классической схеме [1, 4] с той лишь разницей, что в него введена схема контроля К (59) с триггером фиксации ошибки (δ) Тр (60). Тактирование осуществляется сигналами τ1, τ2 , причем τ1(t)&τ2=⌀. На схеме фиг.11 цифрой (51) обозначен комплекс блоков самого самоконтролируемого автомата фиг.1.

Согласно таблице переходов (табл.11) для блока синхронизации потребуется автомат Мура с числом разрядов m=4 и числом логических условий q=4. Такие автоматы относятся к классу простейших, поэтому комбинационная схема F1 (53) реализуется непосредственно по конкатенации от восьми переменных, включая (β, Т, е, ERR). В соответствии с патентом на полезную модель №63588 код a(t) представлен в виде двоичного непозиционного кода ДНК, а код y1y2y3…y8 в виде модифицированного геометрического кода (МГК). Соответствия двоичного позиционного кода (ДНК) кодам МГК и ДНК представлены в табл.13. Схема контроля К (59) тривиальна, т.к. ошибка ERR фиксируется в случае:

Структурная схема блока синхронизации БС (24) и ее функционирование как автомата Мура подробно описаны в работах [1, 4], поэтому схема фиг.11 не описывается, т.к. организация и взаимодействие элементов и блоков не имеют особенностей. Схема F2 для блока БС (24) представлена в виде дешифратора DC (58), т.к. все операторы действия (команды синхронизации Bj,

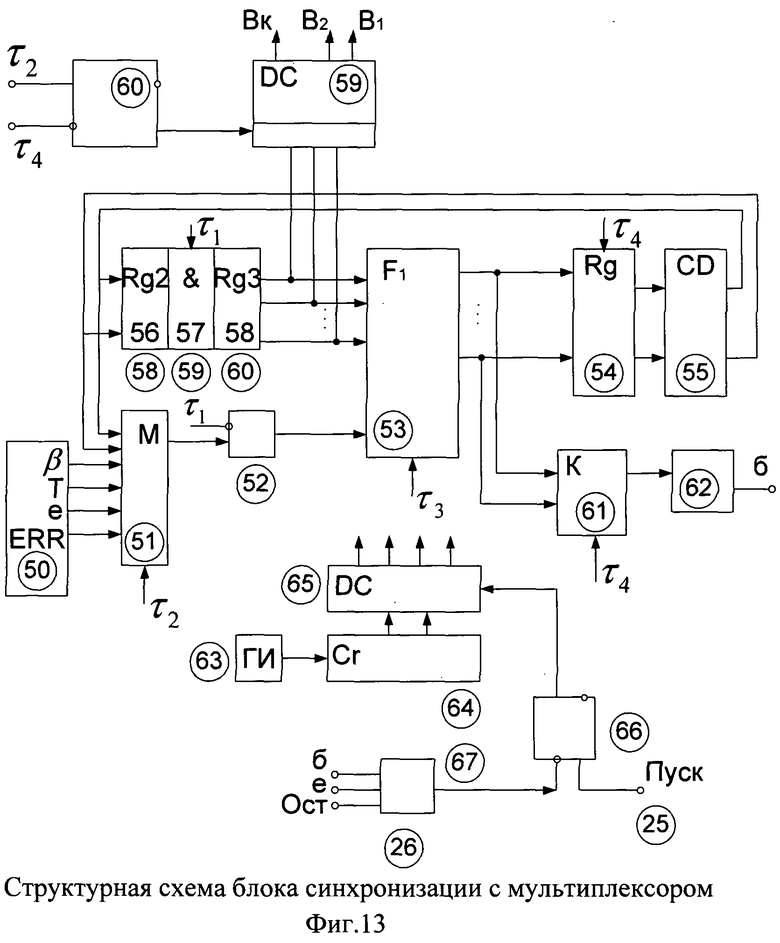

Структурная схема автомата фиг.11 не отличается от схемы по патенту №82888 (кроме схемы контроля) и описана в БИ №13, 2009, а также [2, 4]. Однако более целесообразно построить его также по схеме патента на полезную модель №82888 РФ БИ №13, 2009 с мультиплексором и прямым определением адреса мультиплексора М (51) по коду x1x2…xm. Граф переходов для такой схемы БС (24) приведен на фиг.14. В этом случае объем схемы F1 (53) на фиг.13 по сравнению со схемой F1 (53) на фиг.11 снизится в 2q-1=8 раз.

Для автомата по фиг.1 в блоке синхронизации БС (24) потребуется формировать четыре не пересекающихся во времени импульса τ1(t)& τ2(t)&τ3(t)&τ4(t)=⌀, что реализуется с помощью обычного генератора с одним выходом ГИ (63), двухразрядным счетчиком Cr (64) и дешифратором DC (65) на два адресных входа и четыре выхода (фиг.13).

δ=1 - ошибка в блоке синхронизации;

T=1 - окончание действия Aj(t);

β=1 - работа со счетчиком Грея;

е=1 - программа управления автоматом выполнена (end);

ERR - ошибка в самоконтролируемом автомате.

Таким образом, предложенное изобретение - самоконтролируемый автомат управления полностью реализуемо на современной интегральной базе, сохраняет свойства самоконтролируемости, присущие прототипу, но требует для своей реализации значительно меньших затрат оборудования. Кроме того, в предлагаемом решении кроме контроля правильности переходов a(t)→a(t+1) осуществляется также контроль по логическим условиям αj , чего нет ни в прототипе, ни в одном из изобретений известных авторам.

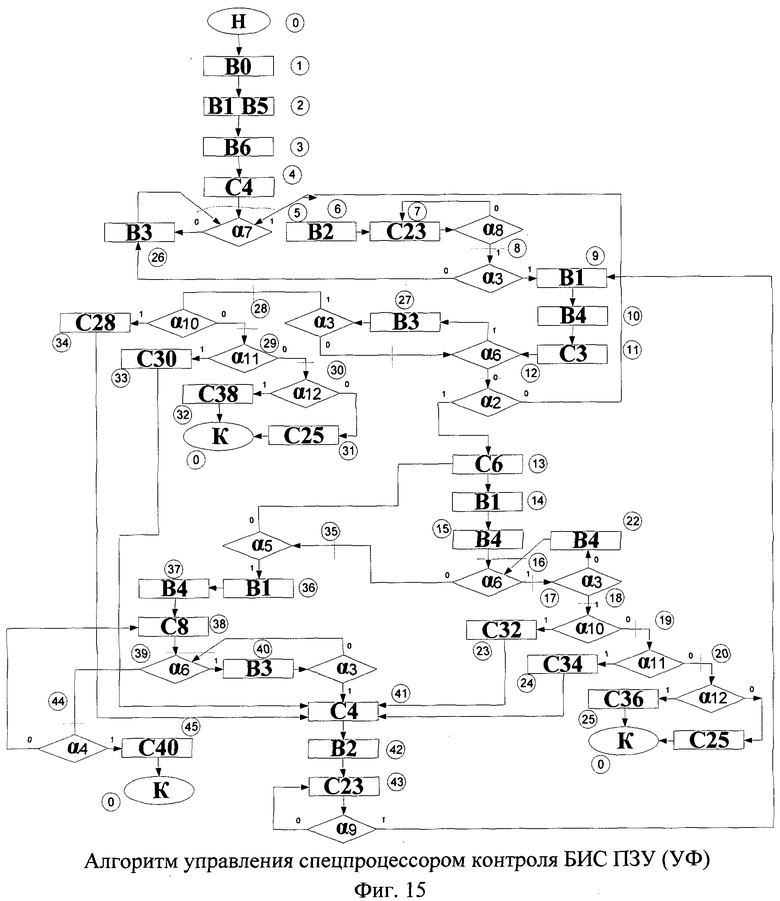

Наиболее сложной граф-схемой алгоритма в известной технической и научной литературе является алгоритм контроля ПЗУ с ультрафиолетовым стиранием информации [5], который представлен на фиг.15. В алгоритме фиг.15 из 45 операторов выделяется три последовательных действия 0-21; 27-31 и 35-44, составляющие в сумме 34 оператора. Следовательно, по новой методике синтеза самоконтролируемого автомата таблица переходов будет соответствовать оставшимся 45-34=11 операторам. При реализации самоконтролируемого автомата по схеме прототипа V=m2(m+q)=6·2(6+12)=1.5 Мб, где m=6 - разрядность a(t) в двоичном позиционном коде, q=12.

По предлагаемому решению W=m2m+1=6·27. Однако в предлагаемом изобретении m на выходе ПЗУ необходимо взять равным (m+2), т.к. добавляются признаки β и r.

Тогда W=(m+2)*2m+1=8*27=1024 б, т.е. для реализации F1 (8) потребуется 8-разрядное ПЗУ на 128 чисел вместо ПЗУ на 1,5 Мб. Затраты на все дополнительные блоки и элементы для обеспечения самоконтролируемости могут быть оценены как не более 7 F1 (8). Но в прототипе две комбинационные схемы с объемом V, тогда выигрыш в затратах оборудования (Q) составит

Оценка является верхней, т.е. выигрыш будет не менее Q раз, однако для точной оценки потребуется полная конструктивная реализация обоих вариантов (прототипа и предлагаемого решения) на конкретной элементной базе с использованием реальных БИС.

Поставленная цель изобретения достигнута, т.к. на уровне функционального проектирования показана возможность создания самоконтролируемого автомата, способного прекращать работу с фиксацией наличия ошибки независимо от того, является ли она одиночной или более высокой кратности, причем реализация предлагаемого решения осуществляется при существенно меньших затратах элементов по сравнению с прототипом.

Литература

1. Угрюмов Е.П. Цифровая схемотехника. - СПб., 2010. - 797 с.

2. Мухопад Ю.Ф. Микроэлектронные системы управления. - Братск, БрГУ. 2009. - 285 с.

3. Сапожников В.В. Кравцов Ю.А. Сапожников Вл.В. Теория дискретных устройств ж.д. автоматики, телемеханики и связи. - М.: Транспорт, 1995. - 320 с.

4. Мухопад Ю.Ф. Теория дискретных устройств. - Иркутск: ИрГУПС, 2010, - 172 с.

5. Мухопад Ю.Ф., Скосырский Г.С. Устройство контроля перепрограммируемых ПЗУ. - Авт. свид. СССР №1547034, БИ №8, 1990.

6. Щербаков Н.С.Структурная теория контроля автоматов. - М.: Машиностроение, 1982. - 191 с.

7. Сагунов В.Г. Алгоритм технического диагностирования дискретных устройств. - М.: Радио и связь, - 1990. - 111 с.

8. Патент РФ №63588, БИ №15, 2007

9. Тоценко В.Г. Алгоритмы технического диагностирования дискретных устройств. - М.: Радио и связь, 1985. - 238 с.

10. Патент РФ №82888, БИ №13, 2009.

11. Патенты РФ №2058041, №20449347, №2071112, №20446396, №2046395, №2042190, №2042189, №2042188, №2018967.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНЫЙ АВТОМАТ | 2013 |

|

RU2527190C1 |

| Метод динамического контроля автоматов и устройство, его реализующее | 2015 |

|

RU2651214C2 |

| УПРАВЛЯЮЩИЙ АВТОМАТ | 2011 |

|

RU2475816C1 |

| Самоконтролируемый автомат | 2020 |

|

RU2775173C1 |

| УПРАВЛЯЮЩИЙ АВТОМАТ С КОНТРОЛЕМ СОСТОЯНИЙ | 2022 |

|

RU2793301C1 |

| УСТРОЙСТВО КРИПТОГРАФИЧЕСКОЙ ЗАЩИТЫ ИНФОРМАЦИИ | 2011 |

|

RU2475838C1 |

| Устройство для вычерчивания циклоидных кривых | 1985 |

|

SU1418071A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Устройство поиска неисправных блоков и элементов | 1989 |

|

SU1709351A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении точности самоконтролируемости. Устройство содержит операционное устройство, четыре запоминающих регистра, три комбинационных схемы, блок схем ИЛИ, блок принятия решений, блок синхронизации, первый, второй и третий триггеры, блок схем для параллельной парафазной передачи результата, первый и второй счетчики, блок кодирования, элемент И, второй, третий и четвертый блоки схем И, блок сравнения, причем блок синхронизации имеет выходы микрокоманд синхронизации B1B2…Bp, связанные со всеми управляющими входами самоконтролируемого автомата, причем единичные выходы первого (α) и второго (β) триггеров связаны с управляющими входами третьей комбинационной схемы.15 ил., 13 табл.

Самоконтролируемый автомат управления, содержащий операционное устройство, три запоминающих регистра, три комбинационных схемы, блок схем ИЛИ, блок принятия решений и блок синхронизации, отличающийся тем, что выходы операционного устройства через первый запоминающий регистр связаны с информационными входами мультиплексора, выход которого связан с единичным входом первого триггера; первая последовательная цепь блоков состоит из второго запоминающего регистра памяти, блока схем для параллельной парафазной передачи результата на первый счетчик, выходы которого связаны параллельно с входами первой комбинационной схемы, первого блока схем ИЛИ, третьего регистра памяти, второго блока схем ИЛИ, связанного через блок кодирования с адресными входами мультиплексора, выходы первого счетчика связаны со входами второй комбинационной схемы, имеющей управляющий вход от второго триггера, причем дополнительный вход первой комбинационной схемы связан с выходом первого триггера, а выходы первой комбинационной схемы связаны со вторыми входами первого блока схем ИЛИ, причем первая комбинационная схема имеет дополнительный парафазный выход, связанный со входами третьего триггера, единичный выход которого через элемент И связан со счетным входом первого счетчика, причем выходы третьего регистра памяти параллельно связаны со входами второго и третьего блоков схем И, выходы которых связаны соответственно с входами третьей комбинационной схемы и первыми входами третьего блока схем ИЛИ, имеющего связь с выходами третьей комбинационной схемы, выходы третьего блока схем ИЛИ через блок сравнения и блок принятия решений, имеющего внешнюю клемму, связаны с первым входом блока синхронизации, имеющего внешние клеммы «ПУСК» и «Останов», причем второй вход блока синхронизации соединен с единичным выходом третьего триггера, имеющего связь по единичному входу с выходом переполнения второго счетчика; выходы первого блока схем ИЛИ через четвертый запоминающий регистр связаны со входами четвертого блока схем И, входами второго регистра памяти и вторыми входами второго блока схем ИЛИ, при этом выходы четвертого блока схем ИЛИ связаны со вторыми входами блока сравнения, а управляющие входы блока принятия решений связаны с дополнительным парафазным выходом первой комбинационной схемы, единичный выход второго триггера связан с третьим входом блока синхронизации, причем блок синхронизации имеет выходы микрокоманд синхронизации B1B2…Bp, связанные со всеми управляющими входами самоконтролируемого автомата, причем единичные выходы первого (α) и второго (β) триггеров связаны с управляющими входами третьей комбинационной схемы.

| Способ точной расточки коренных подшипников автомобильных, тракторных и т.п. двигателей | 1942 |

|

SU63588A1 |

| Система для автоматического контроля параметров радиоприемников | 1980 |

|

SU955092A1 |

| RU 2071112 C1, 27.12.1996 | |||

| US 3634665 A, 11.01.1972 | |||

| US 7716542 B2, 11.05.2010. | |||

Авторы

Даты

2013-12-20—Публикация

2011-11-30—Подача