Настоящее изобретение относится к вычислительной технике и дискретной автоматике и может быть применено в информационно-измерительных системах, в мехатронике и робототехнике, для управления токсичными, пожаро- и взрывоопасными производствами, транспортными системами различного назначения и другими средствами автоматизации технологических процессов.

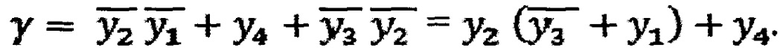

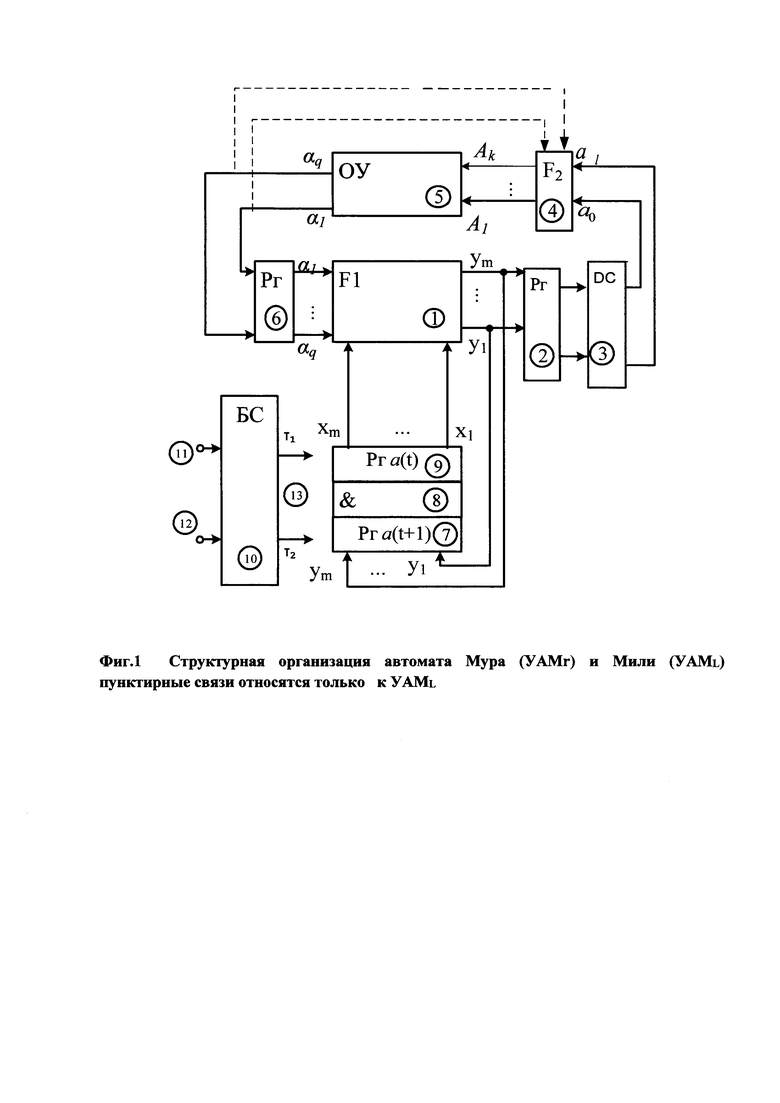

Известны управляющие автоматы (УА) со структурной организацией Мура и Мили [1-3]. Самоконтроль УА реализуется на основе кодов Хэмминга, Грея, Бергера, равновесных кодов kCn с k единицами в n разрядах и др. [4-7].

Аналогом самоконтролируемого УА является управляющий автомат Мура (УАМr) со встроенным блоком контроля (фиг. 1). Для УАМr требуются большие затраты оборудования на реализацию комбинационных схем переходов от предыдущего a(t) в последующее состояние a(t+1). Объем постоянного запоминающего устройства (ПЗУ), реализующего схему F1(1) равен V=mp2m+q, где m - разрядность кода состояния a(t), mp - реальная разрядность ПЗУ, равная 4, 8; q - количество логических условий α1…αq.

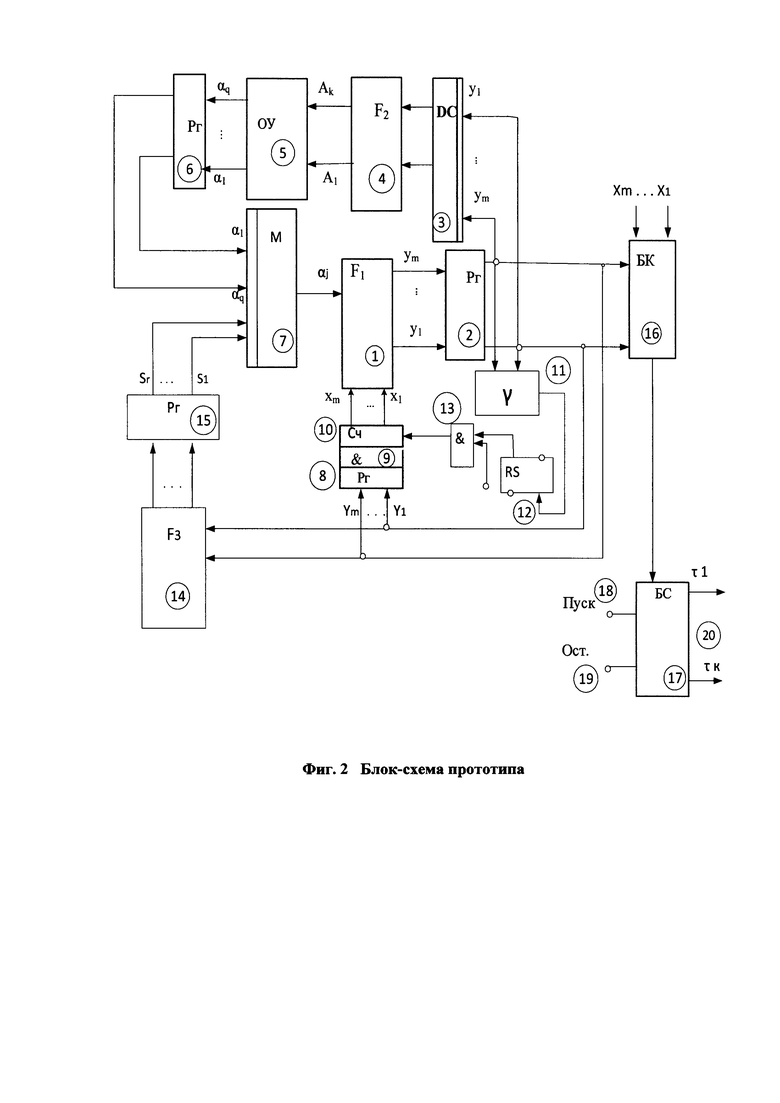

Поэтому в качестве прототипа используются автоматы (фиг. 2) нового типа (УАМх) с оригинальной структурной организацией [7, 8].

Примечание:

Управляющие автоматы разделяются на сверхпростые (СП), простые (ПА), средней сложности (СА), сложные (АС), высокой сложности (ВС), особо сложные (ОС) и ультрасложные (УС). В таблице 1 приведен сравнительный анализ УАМr и УАМx. Аббревиатура УАМx соответствует новому УА Мухопада, названного так по аналогии с УА Глушкова, Маркова, Майхилла, Мили, Мура, Рабина-Скотта, Уилкса и др. Снижение объема ПЗУ в прототипе по сравнению с аналогом определяется величиной Q=V/W=2q-1.

В столбце 10 проставлен коэффициент К снижения числа входов программируемой логической матрицы, если на ней реализуется комбинационная схема переходов F1(1). К=(m+q)/(m+1).

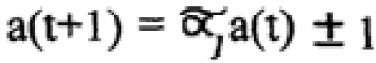

В новом автомате (фиг. 2) введен мультиплексор М(7) с блоком адресации F3(14) и регистром адреса Рг(15) для выбора одного αj∈{α} и подключения к одноразрядному входу F1(1). Тогда объем ПЗУ для реализации схемы переходов F1(1) составит W=mp2m+1, а выигрыш в объеме по сравнению с аналогом (УАМr) определится как Q=V/W=2q-1 (таблица 1).

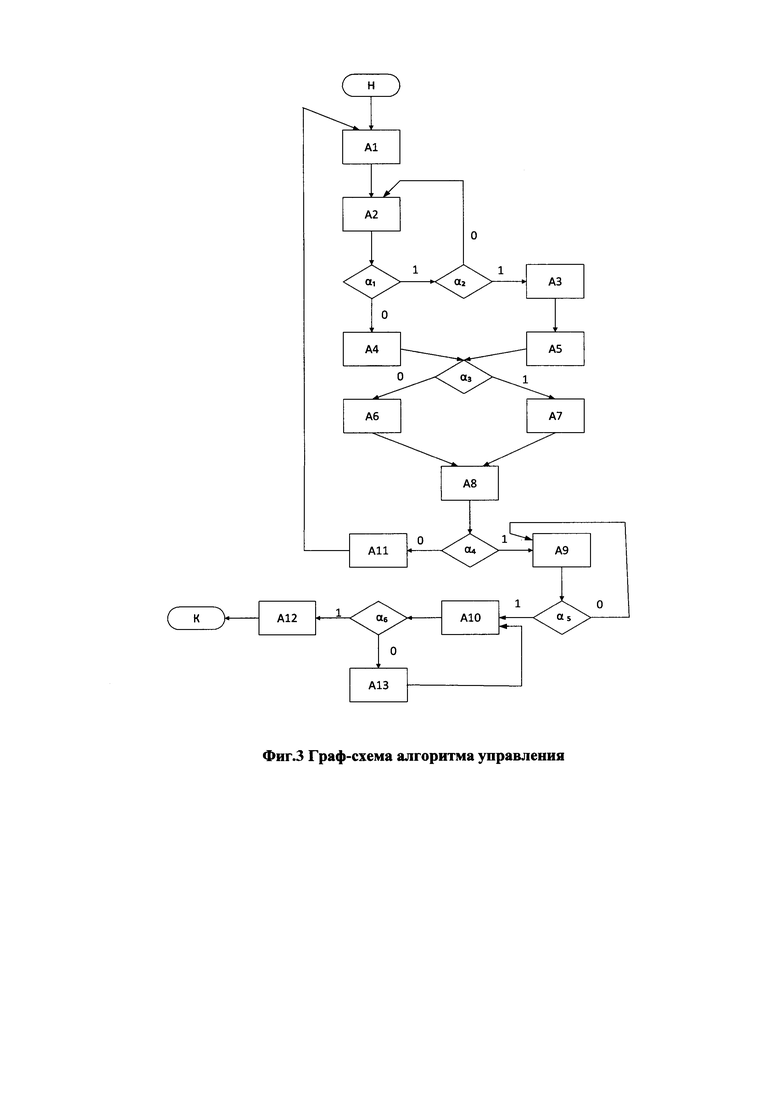

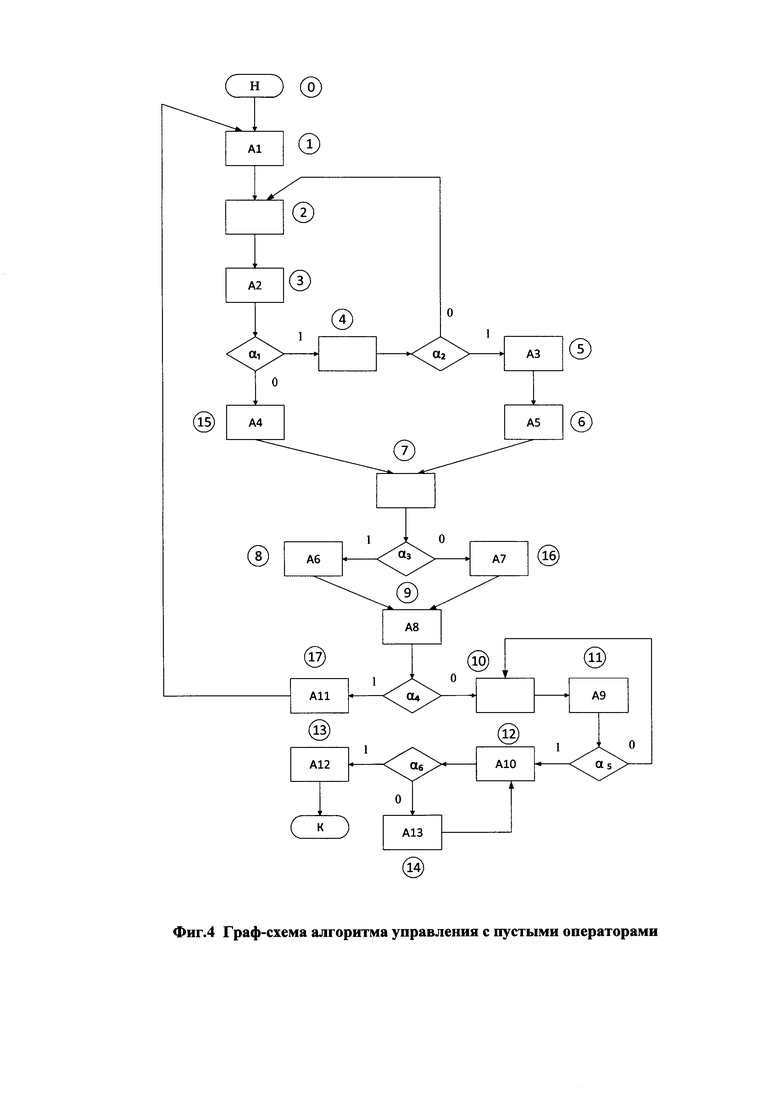

Структурная организация прототипа (фиг 2) стала возможной после преобразования заданной граф-схемы алгоритма (ГСА) управления (фиг. 3) за счет введения пустых операторов [7]:

- перед оператором действия Aj∈{A}, если  т.е. ликвидируются петли, которые недопустимы в самоконтролируемых УА;

т.е. ликвидируются петли, которые недопустимы в самоконтролируемых УА;

- если между αi и αj нет операторов действия А1…Ak;

- если к αj∈{α} передается управление от нескольких других операторов.

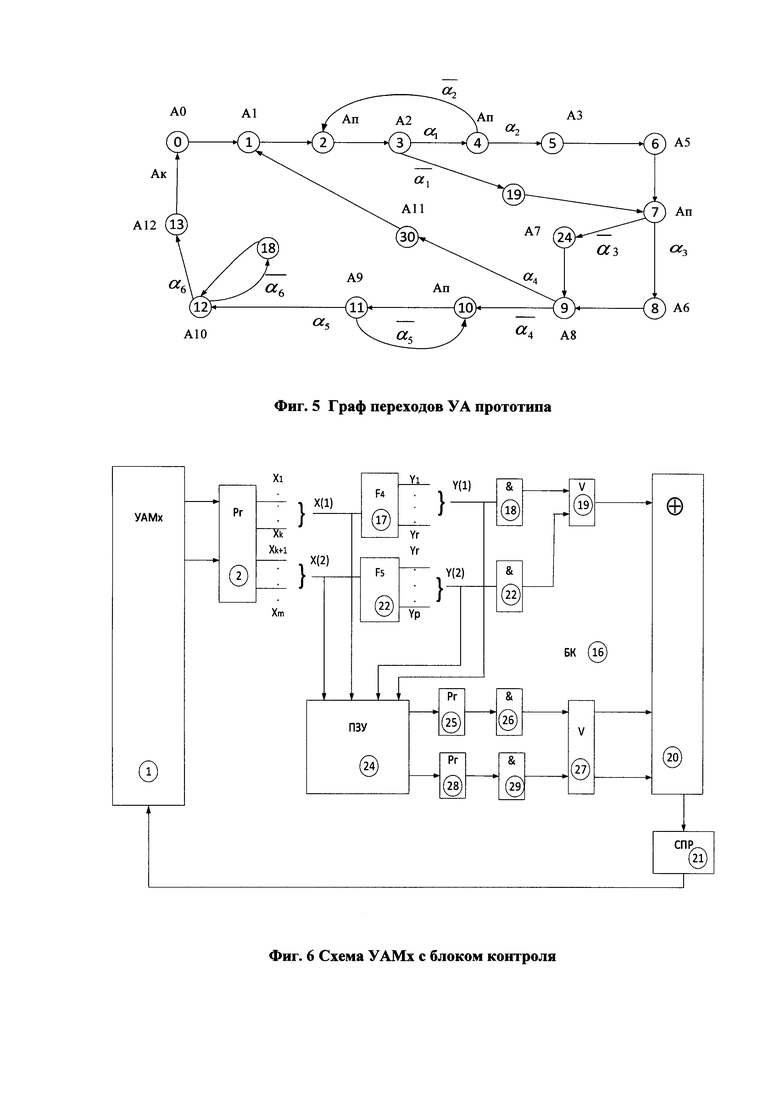

Преобразованная ГСА представлена на фиг. 4, а граф переходов УАМх на фиг. 5. Контроль УА реализуется на основе кодов Грея (таблица 2).

Все блоки в прототипе известны и их функциональная организация не зависит от заданной ГСА или применяемого способа контроля. Исключение составляют блоки F1(1), F3(14) и БК(16). Набор элементов составляющих блок F3(14) по ГСА фиг. 4 определяется по таблице 3, по которой можно записать булевы функции для разрядов адреса s1, s2, s3:

s1=а3+а7+a11; s2=а4+a7+а12; s3=а9+a11+a12.

В таблице 3 значения N(t) представлены в кодах Грея.

Для реализации уравнений адресации требуется дополнительный дешифратор и всего три трехвходовые схемы «ИЛИ», объединяющие выходы дешифратора (3, 7, 11), (4, 7, 12), 9, 11, 12).

Структура схем F1(1) и БС (16) не приводится, т.к. эта информация о прототипе не используется далее в тексте описания предлагаемого изобретения.

В работе [9] в блоке контроля БК(10) прототипа предложено коды состояний разделять приблизительно пополам. Каждая половина, в зависимости от конкретного значения разрядности (m) кода состояний, дополняется одним, двумя или тремя разрядами, значения которых определяются так, чтобы переход от предыдущего к последующему состоянию каждой половины подчинялся правилу Грея. Сравнение кодов состояний производится через многоразрядную схему одноразрядного сложения по mod2, после чего определяется действительно ли в логической сумме только одна «1» и нет кода из всех нулей. Кроме того между a(t) и a(t+1) вставляется промежуточный код, значение которого находится из ПЗУ по адресу каждой из половин кодов.

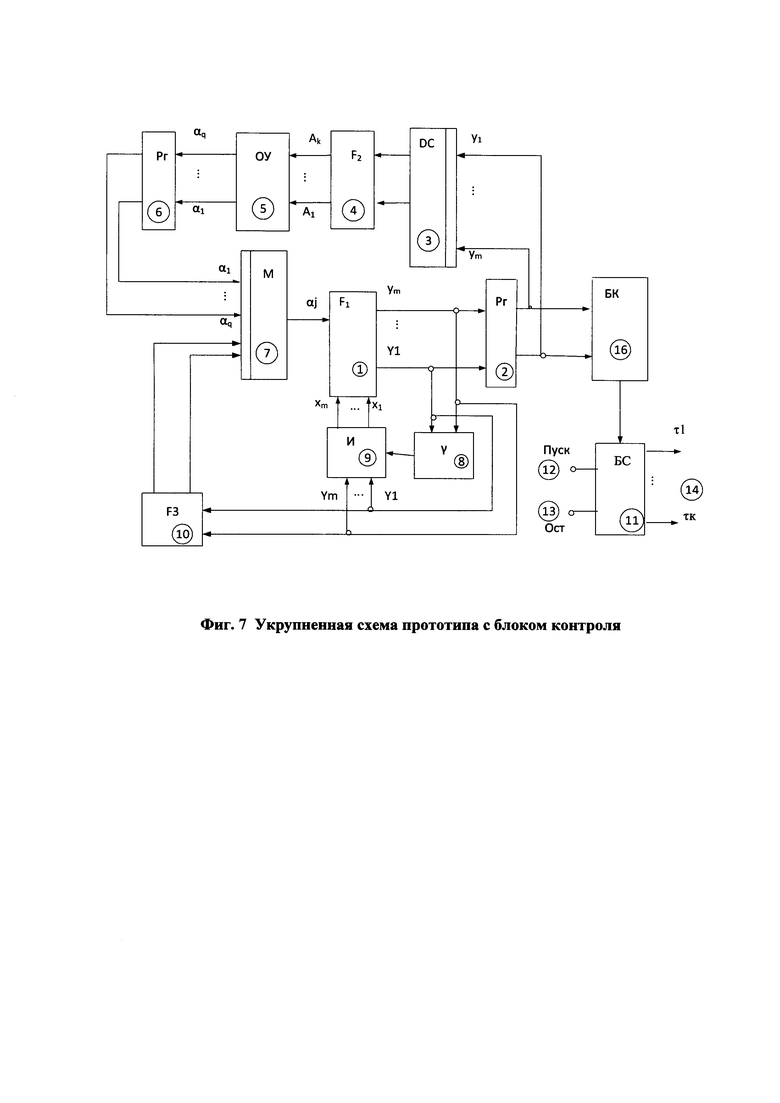

Блок контроля прототипа представлен на фиг. 6, где обозначено: F3(17) и F4(22) - функциональные преобразователи половинных кодов.

Как видно из фиг. 6 блок контроля сложен, т.к. содержит 13 многоразрядных блоков, RS - триггер и внутренний УА самого блока контроля. На фиг. 6 функциональные преобразователи F3(17) и F4(22) служат для представления двоичных позиционных кодов половинной разрядности в коды с дополнительными разрядами. Блок ⊕(20) - это схема определения логической суммы по mod2, СПР(21) - это схема определения наличия только одной единицы в коде логической суммы, которая обычно реализуется с применением регистра сдвига и счетчика.

Для сокращения текстовой части описания изобретения на фиг. 7 приведена укрупненная схема прототипа без детализации функциональной структуры отдельных блоков и элементов. Функциональная последовательность элементов в укрупненных блоках представлена в табл. 4.

Целью настоящего изобретения является создание самоконтролируемого управляющего автомата с существенно более простым блоком контроля, а также с самоконтролем блока синхронизации.

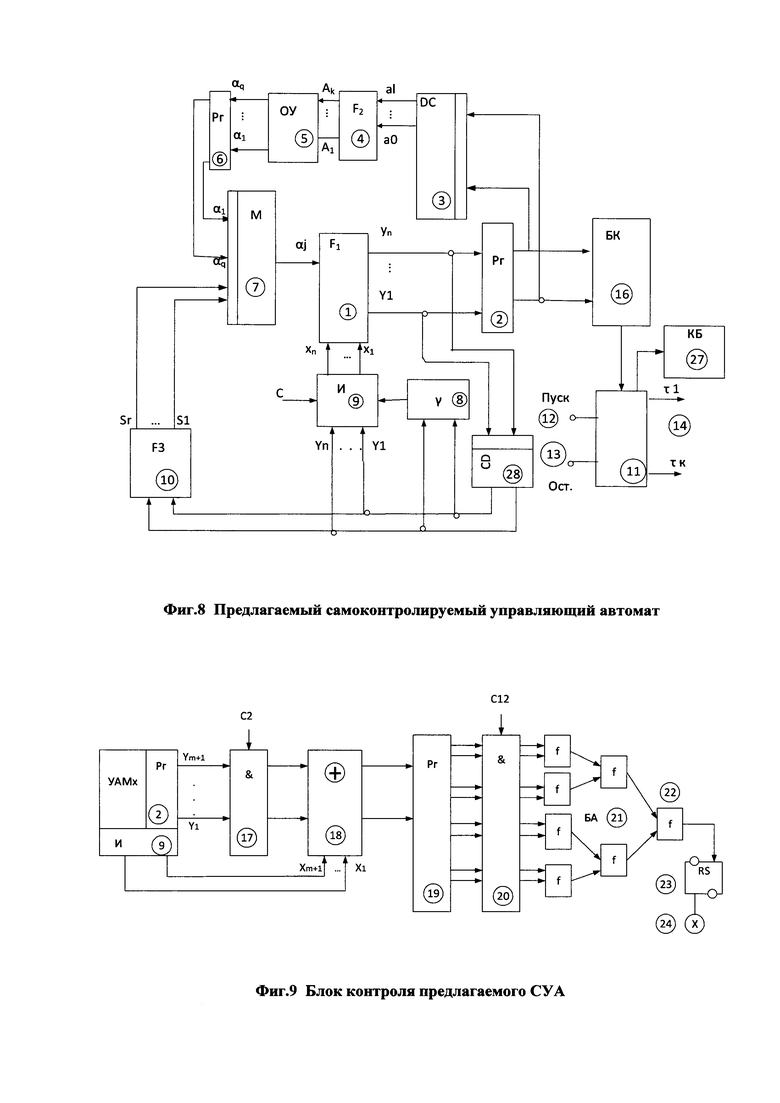

Структурная схема предлагаемого СУА с укрупненными блоками представлена на фиг. 8. В предлагаемом изобретении для контроля правильности переходов, как по счетчику, так и вне счетчика также используется код Грея, но без половинного разделения кодов состояний. Каждый переход представляется последовательностью вида: a(t)→П(t)→a(t+1), где П(t) есть непрерывная цепь вершин р(1)→р(2)→…→р(к), переходы между которыми соответствуют правилу Грея. Величина (к)≤4.

В последовательности П(t) нет необходимости, если  . Кроме того, при подборе кодов промежуточных вершин p(i), чтобы не было повторения номеров, необходимо приписать перед старшими разрядами комбинации 1, 10 или 100.

. Кроме того, при подборе кодов промежуточных вершин p(i), чтобы не было повторения номеров, необходимо приписать перед старшими разрядами комбинации 1, 10 или 100.

По графу переходов (фиг. 5) в переходах вне счетчика от a(t) №3, 7, 9, 12 к a(t+1) можно использовать любые номера от 14 до 31, но с целью уменьшения количества промежуточных вершин выбраны номера 19, 24, 30, 18.

Примечание: Возможно, что при расширении диапазона номеров от 31 до 63 удастся дополнительно уменьшить число промежуточных вершин.

Более того в столбце 6 указаны последовательности р(1)…р(к) в двоичном коде, который можно получить, если каждому разряду кода Грея приписать порядковый вес разрядов в ДПК. Такой код не используется в изобретении, но применен здесь для удобства восприятия и для того, чтобы не использовать таблицы Грея от 0 до 150-й позиции.

При введении промежуточных вершин все существовавшие и вновь введенные переходы подчиняются правилу Грея как будто предлагаемый СУА представляет собой единый счетчик без логических условий.

В структурную схему предлагаемого СУА (фиг. 8) по сравнению с прототипом введен контролирующий блок КБ(15) со светоиндикатором СИ(24), увеличено число выходов первой схемы переходов F1(1) Изменена функциональная организация блока контроля.

Функциональная организация блока контроля представлена на фиг. 9.

Блок контроля БК(16) состоит из последовательно соединенных пяти блоков в виде первого блока элементов «И»(17), блока сложения кодов по mod2 ⊕(18), третьего регистра памяти Рг(19), второго блока элементов «И»(20) и блока анализа БА(21) наличия только одной «1» в логической сумме кодов, представляющей собой трехъярусную однонаправленную сеть двухразрядных схем неравнозначности f(22), причем выход последней схемы f(22) через триггер RS(23) соединен со светоиндикатором СИ(24).

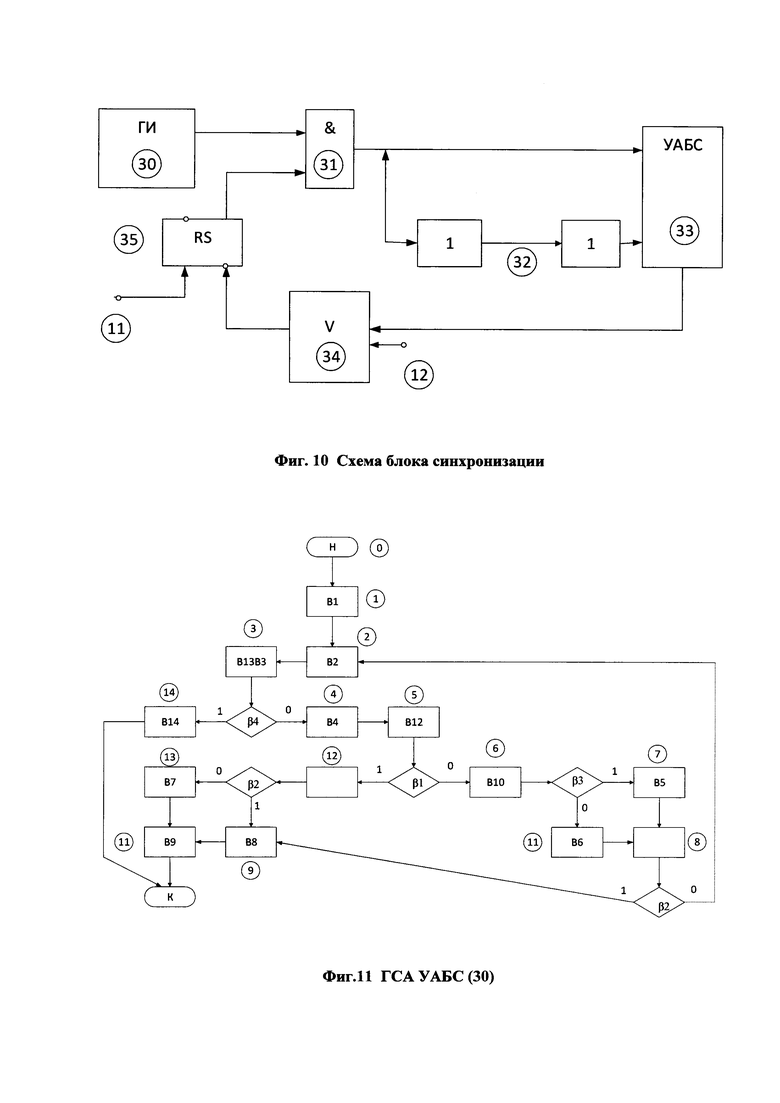

Функциональная схема блока синхронизации БС(11) представлена на фиг. 10. БС(11) представляет собой генератор импульсов ГИ(30) длительностью Т>>τ, элементы алгебры логики (31, 32, 34, 35) и управляющий автомат самого блока синхронизации УАБС(23).

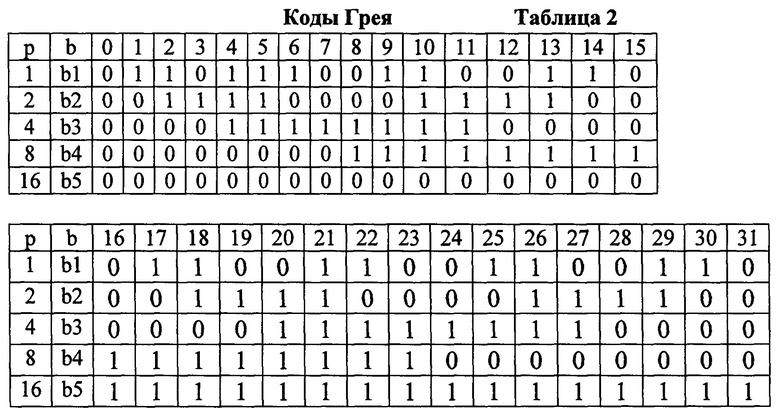

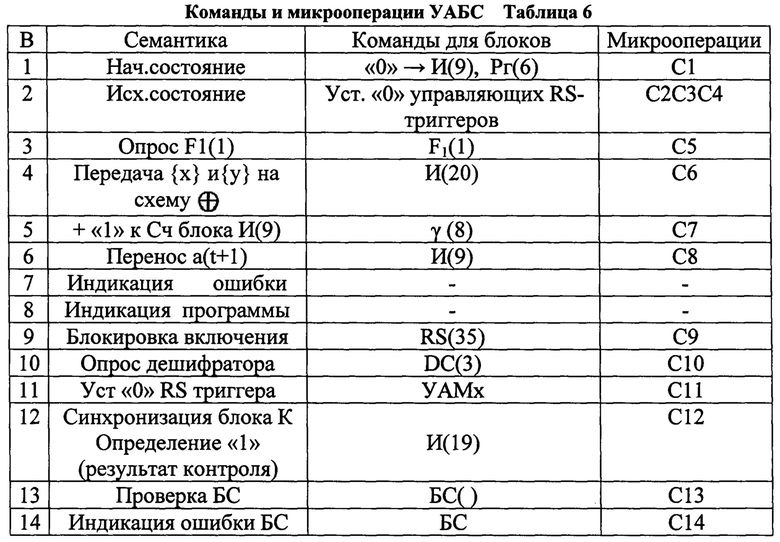

Граф-схема алгоритма управления УАБС(33) представлена на фиг. 11 с расшифровкой микроопераций В1…В14 и логических условий β1…β4 в таблицах 6, 7. Граф переходов УАБС представлен на фиг. 12, по которой можно сделать заключение, что УАБС относится к типу простых автоматов (ПА), который реализуется также по структуре УАМх, но с введением контрольного блока КБ(27) и шифратора (кодера) CD(28) фиг. 8.

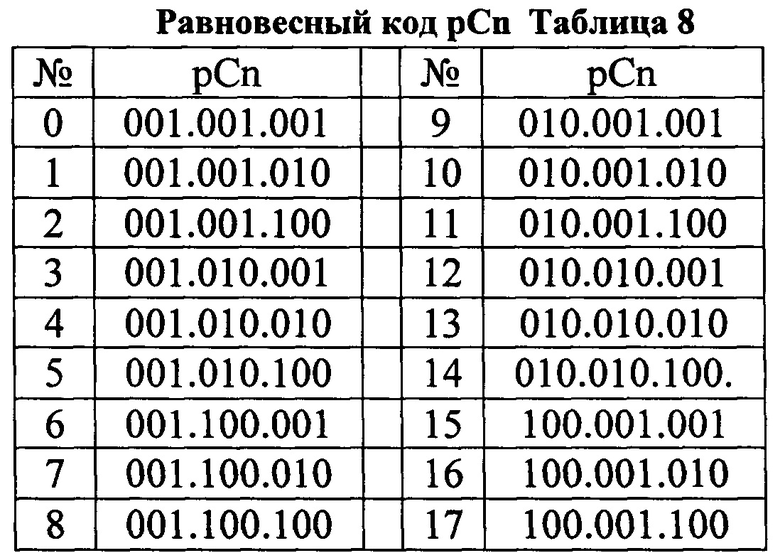

Контроль УАБС (33) осуществляется на основе применения равновесных кодов pCn (табл. 8), состоящего из р трехразрядных (abc) групп с одной единицей в группе. Тогда контроль правильности кода a(t+1) реализуется через параллельную работу p схем (z), выходы которых объединяются схемой «ИЛИ», причем

В схему УАБС(33) введен шифратор CD(25) для перевода кода pCn в ДНК. Функциональная схема шифратора CD(25) не приводится в виду ее тривиальности.

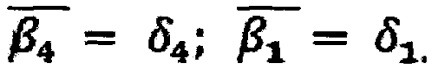

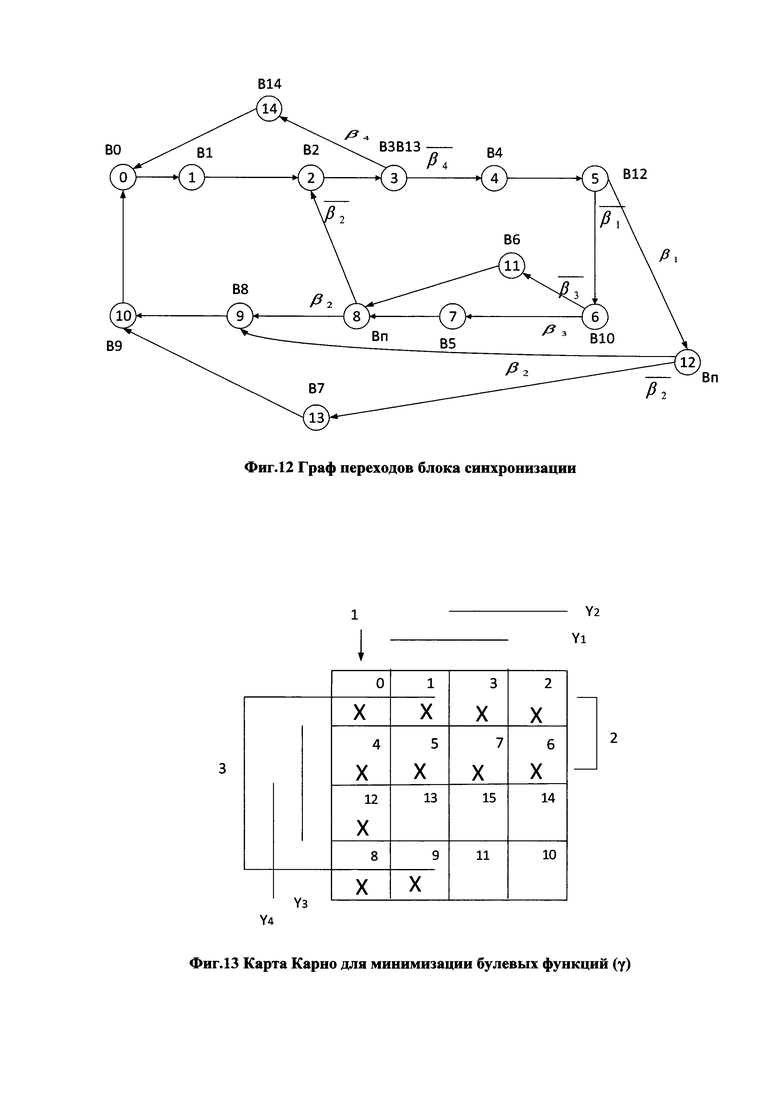

Переходы вне счетчика УАБС(33) приведены в табл. 9, по которой можно записать  По карте Карно (фиг. 13) уравнение для γ примет вид:

По карте Карно (фиг. 13) уравнение для γ примет вид:  Для представления γ в виде формулы в графе переходов произведена замена

Для представления γ в виде формулы в графе переходов произведена замена

Для рассматриваемого примера ГСА при реализации на ПЗУ первой комбинационной схемы переходов F1(1) потребуется объем W=mp2m+1=8*28+1=4 кб.

ОПИСАНИЕ РАБОТЫ СУА В СТАТИКЕ

Самоконтролируемый управляющий автомат (СУА), содержащий последовательную цепь блоков в виде первой комбинационной схемы переходов F1(1), первого регистра памяти Рг(2), дешифратора DC(3), вторую комбинационную схему F2(4) формирования управляющих команд A1…Ak, второй регистр памяти Рг(6) логических условий α1…αq, выходы которого соединены с информационными входами мультиплексора М(7), одноразрядный выход αj∈{α} мультиплексора М(7) соединен с первым входом первой комбинационной схемы переходов F1(1), а выходы у1у2…уm первой комбинационной схемы переходов F1(l) соединены параллельно со входами схемы изменения состояний γ(8) и многоразрядными входами информационного блока И(9), а также с входами третьей схемы F3(10) определения адреса мультиплексора М(7), выходы третьей схемы F3(10) соединены с адресными входами мультиплексора М(7), при этом одноразрядный выход схемы изменения состояний γ(8) связан с одноразрядным дополнительным входом информационного блока И(9); причем СУА имеет блок синхронизации БС(11) со входами «Пуск» (12) и «Останов» (13), на выходах которого τ1…τк(14) формируются сигналы синхронизации C1…Cn для управления всеми блоками СУА; при этом выходы первого регистра памяти Рг(2) соединены со входами блока контроля БК(16), выход которого связан с дополнительным входом блока синхронизации БС(11);

При этом информационный блок И(9) состоит из m-разрядного регистра состояний a(t+1) парафазно связанного через параллельные входы со счетчиком состояний Сч (a(t)), счетный вход которого подсоединен к выходу блока γ(8); схема γ(8) состоит из схемы определения необходимости изменения состояния на (+1) RS-триггера и элемента «И»; схема F3(10) определения адреса мультиплексора М(7), включающая регистр памяти с разрядами S1…Sr.

СУА, отличающийся тем, что с целью упрощения блока контроля БК(16) в него включены дополнительные выходы первой комбинационной схемы переходов F1(1), контролирующий блок КБ(27), блок контроля состоит из последовательности схем в виде первого блока элементов «И»(17), блока сложения кодов по модулю два (18), третьего регистра памяти Рг(19), второго блока элементов «И»(20), блока анализа для определения наличия только одной единицы в логической сумме по mod2 БА(21) в виде трехъярусной однонаправленной сети двухразрядных схем неравнозначности f(22), выход схемы БА(21) через RS-триггер (23) соединен с дополнительным входом блока синхронизации БС(11).

Динамика функционирования СУА полностью задана в виде граф-схемы алгоритма управления УАБС (фиг. 15) с расшифровкой операторов В1…В14 и логических условий β1…β4 в таблицах 6, 7.

Таким образом, в предлагаемом СУА за счет увеличения числа выходов первой комбинационной схемы переходов F1(1), введения промежуточных вершин в переходы вне счетчика, позволяющих осуществлять все переходы СУА с правилом Грея, а также применения оригинальной схемы определения наличия только одной единицы в логической сумме кодов в виде трехъярусной однонаправленной сети двухразрядных схем неравнозначности f(22), блок контроля реализован всего на пяти простых блоках вместо 13 блоков(включая ПЗУ) в прототипе.

Предлагаемый СУА отличается также тем, что за счет введения контролирующего блока КБ(15) с использованием оригинальных равновесных кодов из нескольких трехразрядных групп с одной единицей самоконтроль реализуется также и для блока синхронизации СУА.

Предлагаемый СУА отвечает требованиям, предъявляемым к изобретениям и по нашему мнению заслуживает положительного решения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Баркалов А.А. Прикладная теория цифровых автоматов / А.А. Баркалов, Л.А. Титаренко. - Донецк: ДонНТУ, 2013. - 320 с.

2. Соловьев В.В. Логическое проектирование цифровых систем на основе ПЛИС / В.В. Соловьев, А. Климович. - М.: Телеком, 2008. - 374 с.

3. Кудрявцев В.Б. Теория автоматов / В.Б. Кудрявцев, Ф.Б. Алешин, А.С. Подколзин // МГУ им. М. Ломоносова.- М.: Юрайт, 2018. - 320 с.

4. Труды по теории синтеза и диагноза конечных автоматов и релейных устройств / под ред. В.В. Сапожникова и Вл. В. Сапожникова. - СПб.: Элмор, 2009. - 894 с.

5. В.В. Сапожников Коды Хэмминга в системах функционального контроля логических устройств / В.В. Сапожников, Вл.В Сапожников, Д.В. Ефанов. - Спб.: изд-во Наука, 2018. - 151 с.

6. Багхдади А.А.А. Методы анализа и диагностирования цифровых устройств (аналитический обзор) / А.А.А. Багхдади, В.И. Хаханов, Е.И. Литвинова // Автоматизированные системы управления и приборы автоматики, 2014. - №166. С. 59-74.

7. Мухопад Ю.Ф. Алгоритмические системы управления / Ю.Ф. Мухопад, А.Ю. Мухопад. - Иркутск: ИрГУПС, 2018. - 96 с.

8. Мухопад А.Ю. Теория управляющих автоматов / А.Ю. Мухопад. - Иркутск: ИрГУПС, 2018. - 72 с.

9. Mukhopad Yu. F Majority redundancy of control automata FJMS Тома 103 №2, 2018 Far East Journal of Mathematical Sciences (FJMS) © 2018 Pushpa Publishing House, Allahabad, India, Volume 103, Number 2, 2018, Pages 311-320. Yu. F. Mukhopad, V.N. Sizykh, S.K. Kargapol'cev, O.N. Skrypnik and A.Yu. Mukhopad.

| название | год | авторы | номер документа |

|---|---|---|---|

| Метод динамического контроля автоматов и устройство, его реализующее | 2015 |

|

RU2651214C2 |

| САМОКОНТРОЛИРУЕМЫЙ АВТОМАТ | 2011 |

|

RU2502121C2 |

| УПРАВЛЯЮЩИЙ АВТОМАТ С КОНТРОЛЕМ СОСТОЯНИЙ | 2022 |

|

RU2793301C1 |

| МИКРОПРОГРАММНЫЙ АВТОМАТ | 2013 |

|

RU2527190C1 |

| УСТРОЙСТВО КРИПТОГРАФИЧЕСКОЙ ЗАЩИТЫ ИНФОРМАЦИИ | 2011 |

|

RU2475838C1 |

| УПРАВЛЯЮЩИЙ АВТОМАТ | 2011 |

|

RU2475816C1 |

| Логический анализатор для регистрации результатов контроля | 1988 |

|

SU1608668A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

Изобретение относится к вычислительной технике и дискретной автоматике и может быть применено в информационно-измерительных системах, в мехатронике и робототехнике, для управления токсичными, пожаро- и взрывоопасными производствами, транспортными системами и другими средствами автоматизации технологических процессов. Сущность: самоконтролируемый управляющий автомат (СУА) содержит комбинационные схемы переходов, регистры памяти, дешифратор, мультиплексор, шифратор, схему изменения состояний, информационный блок, блок синхронизации, блок контроля. Блок контроля состоит из последовательности схем в виде первого блока элементов «И», блока сложения кодов по модулю два, третьего регистра памяти, второго блока элементов «И», блока определения наличия только одной единицы в логической сумме по mod2 в виде трехъярусной однонаправленной сети двухразрядных схем неравнозначности, выход которых через RS-триггер соединен с дополнительным входом блока синхронизации, а дополнительный выход блока синхронизации связан со входом контролирующего блока. Причем информационный блок представляет собой регистр памяти последующего состояния автомата, парафазно связанный с параллельными входами суммирующего счетчика. Технический результат: упрощение блока контроля. 9 табл., 13 ил.

Самоконтролируемый управляющий автомат (СУА), содержащий последовательную цепь блоков в виде первой комбинационной схемы переходов, первого регистра памяти, дешифратора, второй комбинационной схемы формирования управляющих команд А1…Ak, объекта управления (ОУ), второго регистра памяти логических условий α1…αq, выходы которого соединены с информационными входами мультиплексора; одноразрядный выход αj∈{α} мультиплексора соединен с первым входом первой комбинационной схемы переходов, а выходы у1у2…уm первой комбинационной схемы переходов через шифратор соединены со входами схемы изменения состояний и многоразрядными входами информационного блока, а также со входами третьей комбинационной схемы определения адреса мультиплексора, выходы третьей комбинационной схемы соединены с адресными входами мультиплексора, при этом одноразрядный выход схемы изменения состояний связан с одноразрядным дополнительным входом информационного блока для прибавления «1» к коду состояния a(t+1); причем СУА имеет блок синхронизации со входами «Пуск» и «Ост.», на выходах которого τ1…τк формируются сигналы синхронизации С1…Cn для управления всеми блоками СУА; при этом выходы первого регистра памяти соединены со входами блока контроля, выход которого связан с дополнительным входом блока синхронизации, отличающийся тем, что блок контроля состоит из последовательности схем в виде первого блока элементов «И», блока сложения кодов по модулю два, третьего регистра памяти, второго блока элементов «И», блока определения наличия только одной единицы в логической сумме по mod2 в виде трехъярусной однонаправленной сети двухразрядных схем неравнозначности, выход которых через RS-триггер соединен с дополнительным входом блока синхронизации, а дополнительный выход блока синхронизации связан со входом контролирующего блока КБ, причем информационный блок представляет собой регистр памяти последующего состояния автомата, парафазно связанный с параллельными входами суммирующего счетчика.

| САМОКОНТРОЛИРУЕМЫЙ АВТОМАТ | 2011 |

|

RU2502121C2 |

| МИКРОПРОГРАММНЫЙ АВТОМАТ | 2013 |

|

RU2527190C1 |

| Способ точной расточки коренных подшипников автомобильных, тракторных и т.п. двигателей | 1942 |

|

SU63588A1 |

| УПРАВЛЯЮЩИЙ АВТОМАТ | 2011 |

|

RU2475816C1 |

| US 5668817 A1, 16.09.1997 | |||

| CN 100437507 C, 26.11.2008. | |||

Авторы

Даты

2022-06-28—Публикация

2020-04-03—Подача