Уровень техники

Изобретение относится к схеме синхронизации, способу синхронизации и системе приема. Прежде всего, данное изобретение относится к схеме синхронизации, способу синхронизации и системе приема, выполненным с возможностью поиска оптимальных коэффициентов передачи цепи обратной связи в соответствии с отдельными отличиями приемников и дрожанием сигнала во времени в каналах передачи, даже в случаях, когда в кадре передачи используют множество способов модуляции.

Последние годы свидетельствуют о феноменальном прогрессе в беспроводных цифровых технологиях передачи, включая мобильные телефоны, системы цифрового вещания (спутниковые и наземные) и беспроводные ЛВС.

Что касается приемника, используемого для беспроводной цифровой передачи, например, эффективность каждой схемы синхронизации, составляющей структуру приемника, важна для осуществления расширенной работы приема. В частности, эффективность синхронизации схемы синхронизации несущей частоты/фазы напрямую влияет на ошибки в разряде и таким образом является критически важной для эффективности приема приемником.

Типичной схемой частотной/фазовой синхронизации может быть цифровая ФАПЧ (фазовая автоподстройка частоты).

Схема частотной/фазовой синхронизации, которая использует цифровую ФАПЧ, обычно состоит из детектора ошибки фазы, фильтра в цепи обратной связи и генератора с числовым программным управлением (NCO).

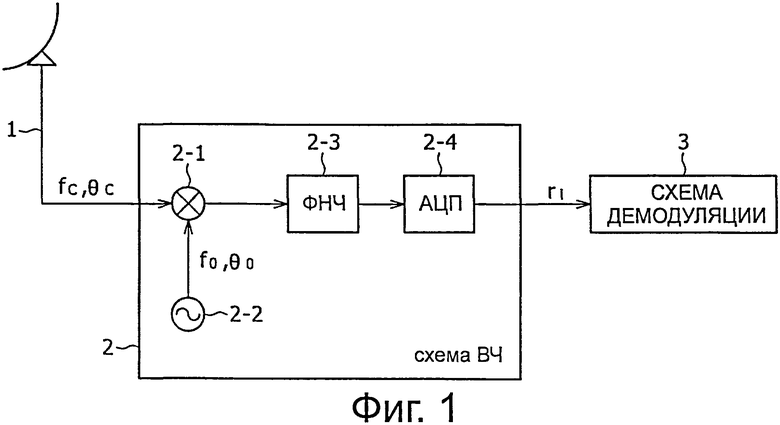

Фиг.1 представляет собой схематичный вид, показывающий неполную структуру обычного приемника, который включает в себя схему частотной/фазовой синхронизации, использующую цифровую ФАПЧ.

Как показано на фиг.1, приемник включает в себя схему 2 высокой частоты (ВЧ) и схему 3 демодуляции. Сигнал приема, полученный антенной 1, принимающей радиоволны, подают на вход умножителя 2-1 схемы 2 ВЧ.

Умножитель 2-1 умножает сигнал локальной генерации, поступающий от локального генератора 2-2, на сигнал приема, переданный от антенны 1. Сигнал, полученный посредством умножения, пересылают в фильтр 2-3 нижних частот (ФНЧ).

Локальный генератор 2-2 генерирует сигнал локальной генерации и передает его в умножитель 2-1.

ФНЧ 2-3 принимает сигнал умножения, поступающий от умножителя 2-1, и позволяет только низкочастотному компоненту сигнала проходить через процесс фильтрации. Сигнал, который подвергался процессу фильтрации, передают в аналого-цифровой преобразователь (АЦП) 2-4.

Предполагается здесь, что ссылочный символ fc означает частоту сигнала приема, который подвергался модуляции, такой как PSK (фазовая манипуляция), θc - фазу сигнала приема, f0 - частоту сигнала локальной генерации, сгенерированного локальным генератором 2-2, а θ0 - фазу частоты локальной генерации. При этом допущении сигнал, поступающий от ФНЧ, включает в себя разность частот Δf, соответствующую fc-f0, и разность фаз θ, соответствующую θc-θ0.

АЦП 2-4 выполняет аналого-цифровое преобразование для сигнала, поступающего от ФНЧ 2-3. Сигнал приема ri, который представляет собой цифровой сигнал приема, полученный посредством аналого-цифрового преобразования, передают в схему 3 демодуляции. Ссылочный символ i обозначает порядковую позицию сигнала приема, о котором идет речь, в последовательности символов.

Сигнал приема ri содержит ошибку фазы, которую можно задать в виде 2πΔft+θ.

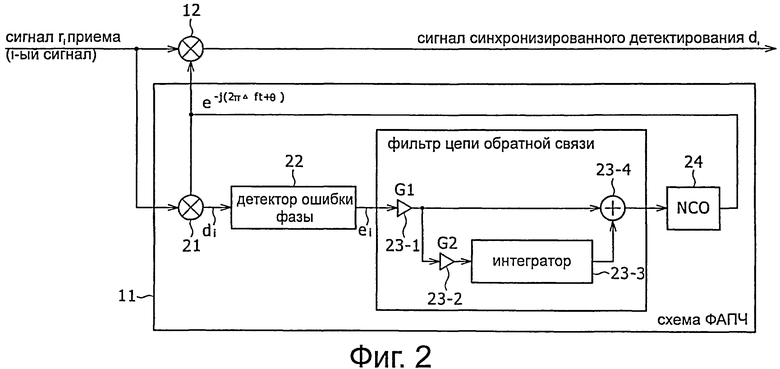

Фиг.2 представляет собой схематичный вид, показывающий типовую структуру схемы частотной/фазовой синхронизации, которая использует цифровую ФАПЧ и которая предоставлена в схеме 3 демодуляции на фиг.1.

Как показано на фиг.2, схема частотной/фазовой синхронизации образована схемой 11 ФАПЧ и умножителем 12. Схема 11 ФАПЧ состоит из умножителя 21, детектора 22 ошибки фазы, фильтра 23 цепи обратной связи и генератора 24 с числовым программным управлением (NCO).

Сигнал приема ri, который подвергался модуляции PSK, передают в умножитель 21 схемы 11 ФАПЧ и умножитель 12.

Умножитель 21 схемы 11 ФАПЧ умножает сигнал приема ri на величину регулирования фазы е-j(2пΔft+θ), поступающую от генератора 24 с числовым управлением. Сигнал, полученный посредством умножения, передают в детектор 22 ошибки фазы.

Детектор 22 ошибки фазы детектирует ошибку фазы, которая может сохраниться в сигнале, поступающем от умножителя 21, и передает детектированную ошибку фазы в фильтр 23 цепи обратной связи.

Например, если сигнал приема ri представляет собой сигнал известного символа, детектор 22 ошибки фазы детектирует в качестве ошибки фазы разницу между фазой символа, представленного сигналом, поступающим от умножителя 21, и фазой известного символа. Если сигнал приема ri не является сигналом любого известного сигнала, детектор 22 ошибки фазы детектирует в качестве ошибки фазы разницу между фазой актуального символа, представленного сигналом, переданным от умножителя 21, и фазой символа, полученного в результате жесткого решения.

Фильтр 23 цепи обратной связи представляет собой пропорциональный интегральный фильтр цепи обратной связи, который фильтрует величину детектированной ошибки фазы, поступающей от детектора 22 ошибки фазы. Отфильтрованную величину передают в генератор 24 с числовым программным управлением.

В частности, умножитель 23-1 фильтра 23 цепи обратной связи умножает величину детектированной ошибки фазы, поступающей от детектора 22 ошибки фазы, на заданный коэффициент передачи цепи обратной связи G1. Результат умножения передают в умножитель 23-2 и сумматор 23-4.

Умножитель 23-2 умножает G1-кратную величину детектированной ошибки фазы, поступающую от умножителя 23-1, на заданный коэффициент передачи цепи G1. Результат умножения передают в интегратор 23-3. Умножители 23-1 и 23-2 служат в качестве блока умножения, который прибавляет вес коэффициента передачи цепи G1 или G2 по входному сигналу.

Интегратор 23-3 интегрирует выход от умножителя 23-2 и передает результат интегрирования в сумматор 23-4.

Сумматор 23-4 складывает выход из умножителя 23-1 и выход из умножителя 23-3. Сумму передают в виде результата процесса фильтрации в генератор 24 с числовым программным управлением.

Генератор 24 с числовым программным управлением генерирует величину регулирования фазы е-j(2пΔft+θ) на основе результата фильтрации из фильтра 23 цепи обратной связи и передает сгенерированную величину в умножители 21 и 12.

Умножитель 12 умножает сигнал приема ri на величину регулирования фазы е-j(2пΔft+θ), поступающую от генератора 24 с числовым программным управлением. Сигнал, полученный посредством умножения, передают в виде синхронизированного сигнала детектирования di.

При этом коэффициенты передачи цепи обратной связи G1 и G2 фильтра 23 цепи обратной связи определяют полосу пропускания фильтрации, которая характеризует фильтр 23 цепи обратной связи. Полоса пропускания фильтра 23 цепи обратной связи и работа схемы 11 ФАПЧ, как известно, имеют взаимосвязь, описанную ниже.

А именно, когда фильтр цепи обратной связи имеет широкую (т.е. большую) полосу пропускания, улучшается способность следить за колебанием ошибки фазы, но повышается величина фазового дрожания синхронизированного сигнала детектирования, передаваемого из схемы ФАПЧ. И, наоборот, в случае, когда фильтр нижних частот имеет узкую (т.е. маленькую) полосу пропускания, ухудшается способность следить за колебанием ошибки фазы, но уменьшается величина фазового дрожания выходного синхронизированного сигнала детектирования. В связи с этим можно сослаться на выложенный патент Японии №2009-26426.

Раскрытие изобретения

Однако в приемнике, используемом для действующей беспроводной цифровой передачи, могут иметь место шум в фазе и частоте сигнала приема, обусловленный зависящими от температуры характеристиками локального генератора или непреднамеренной генерации внутри схемы ВЧ. С целью реализации оптимальной работы синхронизации схемы частотной/фазовой синхронизации, использующей цифровую ФАПЧ, может таким образом необходимо задать оптимальные коэффициенты передачи цепи в соответствии с отдельными отличиями характеристик приемника и дрожанием сигнала во времени в каналах передачи.

Обычная цифровая схема ФАПЧ выполнена с возможностью установки только фиксированного коэффициента передачи цепи. Достижение оптимальной работы приема включает в себя установку коэффициента передачи цепи, оптимальным образом адаптированного под среду приема для каждого отдельного приемника. В случае, когда каналы передачи динамически изменяют вследствие температуры и других факторов так, что оптимальный коэффициент передачи цепи соответственно динамически изменяется, используемый в настоящий момент коэффициент передачи цепи не останется оптимальным.

Более того, оптимальный коэффициент передачи цепи для фильтра цепи обратной связи в схеме ФАПЧ может изменяться в зависимости от способов модуляции, используемых в сигнале приема. Например, спутниковая цифровая схема вещания, принятая в Японии, позволяет множеству способов модуляции сосуществовать в одном кадре. В таком случае, если задают только один коэффициент передачи цепи, этот коэффициент передачи цепи может быть оптимальным для данного способа модуляции, но неоптимальным для других способов модуляции. Это может привести к ухудшению работы приема.

Настоящее изобретение было разработано с учетом вышеописанных обстоятельств и предоставляет схему синхронизации, способ синхронизации и систему приема, выполненные с возможностью поиска оптимальных коэффициентов передачи цепи в соответствии с отдельными отличиями приемников и дрожанием сигнала во времени в каналах передачи, даже в случаях, когда в кадре передачи используют множество способов модуляции.

Согласно одному варианту осуществления настоящего изобретения предоставлена схема синхронизации, включающая в себя: первую схему ФАПЧ, выполненную с возможностью вывода, на основе входного сигнала приема, первого сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; вторую схему ФАПЧ, выполненную с возможностью получения того же сигнала, что и сигнал приема, подаваемый на первую схему ФАПЧ, для вывода второго сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; первую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе первого сигнала регулирования фазы для вывода сигнала с регулированной фазой; вторую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе второго сигнала регулирования фазы для вывода сигнала с регулированной фазы; первую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы в первой схеме ФАПЧ на основе сигнала с регулированной фазы, выводимого из первой выходной схемы; вторую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы во второй схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из второй выходной схемы; схему регулирования, выполненную так, что если ошибка регулирования фазы, детектируемая в первой схеме ФАПЧ первой схемой детектирования, больше ошибки регулирования фазы, детектируемой во второй схеме ФАПЧ второй схемой детектирования, схема регулирования выполнена с возможностью устанавливать величину коэффициенту передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ, в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ; и участок хранения, выполненный с возможностью хранения параметра настройки коэффициента передачи цепи обратной связи, устанавливаемого в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ. Сигнал приема имеет структуру блоков кадра, составленных из множества слотов, передаваемых во множестве режимов передачи, соответствующих различным способам модуляции, и участок хранения хранит параметр настройки коэффициента передачи цепи для каждого режима передачи.

Предпочтительно схема синхронизации по настоящему изобретению может дополнительно включать в себя: участок сравнения, выполненный с возможностью сравнения по абсолютному значению ошибки регулирования фазы, детектируемой в первой схеме ФАПЧ первой схемой детектирования с ошибкой регулирования фазы, детектируемой во второй схеме ФАПЧ второй схемой детектирования; и участок поиска коэффициента передачи цепи обратной связи, выполненный так, что всякий раз, когда сравнение выполняется участком сравнения при поступлении сигнала приема, соответствующего слотам заданного режима передачи, участок поиска коэффициента передачи цепи выполнен с возможностью поиска параметра настройки оптимального коэффициента передачи цепи обратной связи для этого режима передачи путем изменения на заданную величину значения коэффициента передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ. Если величину коэффициента передачи цепи обратной связи второго фильтра цепи обратной связи изменяют заданное число раз участком поиска коэффициента передачи цепи обратной связи, то участок хранения может хранить значение, установленное в качестве коэффициента передачи цепи первого фильтра нижних частот, в качестве параметра настройки оптимального коэффициента передачи цепи обратной связи для этого режима передачи.

Предпочтительно схема синхронизации настоящего изобретения может дополнительно включать в себя участок идентификации номера режима передачи, выполненный с возможностью идентификации номера режима передачи, представляющего собой информацию для идентификации режима передачи каждого слота в сигнале приема, на основе сигнала управления, получаемого путем декодирования сигнала приема. Если идентифицированный номер режима передачи соответствует заданному режиму передачи, тогда участок поиска коэффициента передачи цепи обратной связи может выполнять поиск оптимального параметра настройки коэффициента передачи цепи обратной связи; и участок хранения может хранить оптимальный параметр настройки коэффициента передачи цепи обратной связи в соответствии с номером режима передачи, идентифицированным участком определения номера режима передачи.

Предпочтительно первая схема ФАПЧ может включать в себя: первую схему детектирования, выполненную с возможностью детектирования ошибки фазы, остающейся в сигнале с регулированной фазой; первый фильтр цепи обратной связи, выполненный с возможностью выполнения процесса фильтрации на ошибке фазы, детектированной первой схемой детектирования; первую схему генерации, выполненную с возможностью вывода первого сигнала регулирования фазы в зависимости от результата процесса фильтрации, выполненного первым фильтром цепи обратной связи; и первую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе первого сигнала регулирования фазы, выводимого из первой схемы генерации, при этом первая выходная схема дополнительно выполнена с возможностью вывода сигнала с регулированной фазой в первую схему детектирования в качестве сигнала, предназначенного для детектирования ошибки фазы; а вторая схема ФАПЧ может включать в себя: вторую схему детектирования, выполненную с возможностью детектирования ошибки фазы, остающейся в сигнале с регулированной фазой; второй фильтр нижних частот, выполненный с возможностью выполнения процесса фильтрации на ошибке фазы, детектированной второй схемой детектирования; вторую схему генерации, выполненную с возможностью вывода второго сигнала регулирования фазы в зависимости от результата процесса фильтрации, выполненного вторым фильтром нижних частот; и вторую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе второго сигнала регулирования фазы, выводимого из второй схемы генерации, при этом вторая выходная схема дополнительно выполнена с возможностью вывода сигнала с регулированием фазы во вторую схему детектирования в качестве сигнала, предназначенного для детектирования ошибки фазы.

Предпочтительно первый фильтр цепи обратной связи может включать в себя: первую схему умножения, выполненную с возможностью умножения ошибки фазы, детектированной первой схемой детектирования, на первый коэффициент передачи цепи обратной связи; вторую схему умножения, выполненную с возможностью умножения ошибки фазы, умноженной первой схемой умножения, на второй коэффициент передачи цепи обратной связи; и первую схему сложения, выполненную с возможностью сложения ошибки фазы, умноженной первой схемой умножения, и результата интегрирования ошибки фазы, умноженной второй схемой умножения, при этом первая схема сложения дополнительно выполнена с возможностью вывода суммы сложения в первую схему генерации; а второй фильтр цепи обратной связи может включать в себя: третью схему умножения, выполненную с возможностью умножения ошибки фазы, детектированной второй схемой детектирования, на третий коэффициент передачи цепи обратной связи; четвертую схему умножения, выполненную с возможностью умножения ошибки фазы, умноженной третьей схемой умножения, на четвертый коэффициент передачи цепи обратной связи; и вторую схему сложения, выполненную с возможностью сложения ошибки фазы, умноженной третьей схемой умножения, и результата интегрирования ошибки фазы, умноженной четвертой схемой умножения, при этом вторая схема сложения дополнительно выполнена с возможностью передачи суммы сложения во вторую схему генерации.

Предпочтительно схема регулирования может задать другую величину и для первого коэффициента передачи цепи, и для третьего коэффициента передачи цепи.

Согласно другому варианту осуществления настоящего изобретения предложен способ синхронизации, включающий в себя этапы, на которых: обеспечивают вывод первой схемой ФАПЧ, на основе входного сигнала приема, первого сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; обеспечивают прием второй схемой ФАПЧ того же сигнала, что и сигнал приема, вводимый в первую схему ФАПЧ, для вывода второго сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; обеспечивают при помощи первой выходной схемы регулирование фазы сигнала приема на основе первого сигнала регулирования фазы для вывода сигнала с регулированной фазы; обеспечивают при помощи второй выходной схемы регулирование фазы сигнала приема на основе второго сигнала регулирования фазы для вывода сигнала с регулированной фазой; обеспечивают при помощи первой схемы детектирования детектирование ошибки регулирования фазы в первой схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из первой выходной схемы; обеспечивают при помощи второй схемы детектирования детектирование ошибки регулирования фазы во второй схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из второй выходной схемы; при этом, если ошибка регулирования фазы, детектированная в первой схеме ФАПЧ первой схемой детектирования, больше ошибки регулирования фазы, детектированной во второй схеме ФАПЧ второй схемой детектирования, то устанавливают значение, равное коэффициенту передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ, в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ; и сохраняют параметр настройки коэффициента передачи цепи обратной связи, установленный в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ. Сигнал приема имеет структуру блоков кадра, составленных из множества слотов, передаваемых во множестве режимов передачи, соответствующих различным способам модуляции; и параметр настройки коэффициента передачи цепи сохраняют для каждого режима передачи.

Согласно дополнительному варианту осуществления настоящего изобретения предложена система приема, включающая в себя: участок получения, выполненный с возможностью получения сигнала, передаваемом по каналу передачи; участок процесса декодирования канала передачи, выполненный с возможностью выполнения обработки, включающей в себя процесс синхронизированного детектирования в отношении сигнала, полученного участком получения. Участок процесса декодирования канала передачи включает в себя: первую схему ФАПЧ, выполненную с возможностью вывода, на основе входного сигнала приема, первого сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; вторую схему ФАПЧ, выполненную с возможностью приема того же сигнала, что и сигнал приема, вводимый в первую схему ФАПЧ, для вывода второго сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; первую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе первого сигнала регулирования фазы для вывода сигнала с регулированной фазой; вторую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе второго сигнала регулирования фазы для вывода сигнала с регулированной фазой; первую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы в первой схеме ФАПЧ на основе сигнала с регулированием фазы, выводимого из первой выходной схемы; вторую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы во второй схеме ФАПЧ на основе сигнала с регулированием фазы, выводимого из второй выходной схемы; схему регулирования, выполненную так, что если ошибка регулирования фазы, детектированная в первой схеме ФАПЧ первой схемой детектирования, больше ошибки регулирования фазы, детектированной во второй схеме ФАПЧ второй схемой детектирования, то схема регулирования выполнена с возможностью устанавливать значение, равное коэффициенту передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ; и участок хранения, выполненный с возможностью хранения параметра настройки коэффициента передачи цепи обратной связи, установленного в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ. Сигнал приема имеет структуру блоков кадра, составленных из множества слотов, передаваемых во множестве режимов передачи, соответствующих различным способам модуляции, и участок хранения хранит параметр настройки коэффициента передачи цепи обратной связи для каждого режима передачи.

Согласно еще одному варианту осуществления настоящего изобретения предложена система приема, включающая в себя: участок процесса декодирования канала передачи, выполненный с возможностью выполнения обработки, включающей в себя процесс синхронизированного детектирования в отношении сигнала, полученного по каналу передачи; и участок процесса декодирования источника информации, выполненный с возможностью декодирования сигнала, подвергнутого обработке, выполненной участком процесса декодирования канала передачи, в данные, предназначенные для передачи. Участок процесса декодирования канала передачи включает в себя: первую схему ФАПЧ, выполненную с возможностью вывода, на основе входного сигнала приема, первого сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; вторую схему ФАПЧ, выполненную с возможностью приема того же сигнала, что и сигнал приема, поступающий на вход первой схемы ФАПЧ, для вывода второго сигнала регулирования фазы, представляющий величину регулирования фазы сигнала приема; первую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе первого сигнала регулирования фазы для вывода сигнала с регулированной фазой; вторую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе второго сигнала регулирования фазы для вывода сигнала с регулированной фазой; первую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы в первой схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из первой выходной схемы; вторую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы во второй схеме ФАПЧ на основе сигнала с регулированием фазы, выводимого из второй выходной схемы; схему регулирования, выполненную так, что если ошибка регулирования фазы, детектированная в первой схеме ФАПЧ первой схемой детектирования, больше ошибки регулирования фазы, детектированной во второй схеме ФАПЧ второй схемой детектирования, то схема регулирования устанавливает значение, равное коэффициенту передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ, в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ; и участок хранения, выполненный с возможностью хранения параметра настройки коэффициента передачи цепи обратной связи, установленного в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ. Сигнал приема имеет структуру блоков кадра, составленного из множества слотов, передаваемых во множестве режимов передачи, соответствующих различным способам модуляции, и участок хранения хранит параметр настройки коэффициента передачи цепи обратной связи для каждого режима передачи.

Согласно еще одному варианту осуществления настоящего изобретения предложена система приема, включающая в себя: участок процесса декодирования канала передачи, выполненный с возможностью выполнения обработки, включающей в себя процесс синхронизированного детектирования сигнала, получаемого по каналу передачи; и участок вывода, выполненный с возможностью вывода изображения и/или звука на основе сигнала, подвергшегося обработке, выполняемой участком процесса декодирования канала передачи. Участок процесса декодирования канала передачи включает в себя: первую схему ФАПЧ, выполненную с возможностью вывода, на основе входного сигнала приема, первого сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; вторую схему ФАПЧ, выполненную с возможностью приема того же сигнала, что и сигнал приема, поступающий на вход первой схемы ФАПЧ, для вывода второго сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; первую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе первого сигнала регулирования фазы для вывода сигнала с регулированной фазой; вторую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе второго сигнала регулирования фазы для вывода сигнала с регулированной фазой; первую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы в первой схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из первой выходной схемы; вторую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы во второй схеме ФАПЧ на основе сигнала с регулированной фазой, выводимой из второй выходной схемы; схему регулирования, выполненную так, что если ошибка регулирования фазы, детектированная в первой схеме ФАПЧ первой схемой детектирования, больше ошибки регулирования фазы, детектированной во второй схеме ФАПЧ второй схемой детектирования, то схема регулирования выполнена с возможностью установки значения, равного коэффициенту передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ, в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ; и участок хранения, выполненный с возможностью хранения параметра настройки коэффициента передачи цепи обратной связи, установленного в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ. Сигнал приема имеет структуру блоков кадра, составленного из множества слотов, передаваемых во множестве режимов передачи, соответствующих различным способам модуляции, и участок хранения хранит параметр настройки коэффициента передачи цепи обратной связи для каждого режима передачи.

Согласно еще одному варианту осуществления настоящего изобретения предложена система приема, включающая в себя: участок процесса декодирования канала передачи, выполненный с возможностью выполнения обработки, включающей в себя процесс синхронизированного детектирования сигнала, получаемого по каналу передачи; и участок записи, выполненный с возможностью записи сигнала, подвергнутого обработке, выполняемой участком процесса декодирования канала передачи. Участок процесса декодирования канала передачи включает в себя: первую схему ФАПЧ, выполненную с возможностью вывода, на основе входного сигнала приема, первого сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; вторую схему ФАПЧ, выполненную с возможностью приема того же сигнала, что и сигнал приема, поступающий на первую схему ФАПЧ, для вывода второго сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; первую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе первого сигнала регулирования фазы для вывода сигнала с регулированной фазой; вторую выходную схему, выполненную с возможностью регулирования фазы сигнала приема на основе второго сигнала регулирования фазы для вывода сигнала с регулированной фазой; первую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы в первой схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из первой выходной схемы; вторую схему детектирования, выполненную с возможностью детектирования ошибки регулирования фазы во второй схеме ФАПЧ на основе сигнала с регулированной фазой, выводимой из второй выходной схемы; схему регулирования, выполненную так, что если ошибка регулирования фазы, детектированная в первой схеме ФАПЧ первой схемой детектирования, больше ошибки регулирования фазы, детектированной во второй схеме ФАПЧ второй схемой детектирования, то схема регулирования выполнена с возможностью установки значения, равного коэффициенту передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ, в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ; и участок хранения, выполненный с возможностью хранения параметра настройки коэффициента передачи цепи обратной связи, установленного в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ. Сигнал приема имеет структуру блоков кадра, составленного из множества слотов, передаваемых во множестве режимов передачи, соответствующих различным способам модуляции, и участок хранения хранит параметр настройки коэффициента передачи цепи обратной связи для каждого режима передачи.

В случае, когда настоящее изобретение выполнено, как указано выше, обеспечивают вывод первой схемой ФАПЧ на основе входного сигнала приема, первого сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; обеспечивают вывод второй схемой ФАПЧ того же сигнала, что и сигнал приема, поступающий на первую схему ФАПЧ, для вывода второго сигнала регулирования фазы, представляющего величину регулирования фазы сигнала приема; при помощи первой выходной схемы обеспечивают регулирование фазы сигнала приема на основе первого сигнала регулирования фазы для вывода сигнала с регулированной фазой; при помощи второй выходной схемы обеспечивают регулирование фазы сигнала приема на основе второго сигнала регулирования фазы для вывода сигнала с регулированной фазой; при помощи первой схемы детектирования обеспечивают детектирование ошибки регулирования фазы в первой схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из первой выходной схемы; при помощи второй схемы детектирования обеспечивают детектирование ошибки регулирования фазы во второй схеме ФАПЧ на основе сигнала с регулированной фазой, выводимого из второй выходной схемы; если ошибка регулирования фазы, детектированная в первой схеме ФАПЧ первой схемой детектирования, больше ошибки регулирования ФАПЧ, детектированной во второй схеме ФАПЧ второй схемой детектирования, то устанавливают значение, равное коэффициенту передачи цепи обратной связи второго фильтра цепи обратной связи, включенного в состав второй схемы ФАПЧ, в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ; и сохраняют параметр настройки коэффициента передачи цепи обратной связи, установленный в качестве коэффициента передачи цепи обратной связи первого фильтра цепи обратной связи, включенного в состав первой схемы ФАПЧ. Сигнал приема имеет структуру блоков кадра, составленного из множества слотов, передаваемых во множестве режимов передачи, соответствующих различным способам модуляции, и параметр настройки коэффициента передачи цепи обратной связи хранят для каждого режима передачи.

Таким образом, согласно настоящему изобретению можно провести поиск оптимальных коэффициентов передачи цепи обратной связи в соответствии с индивидуальными различиями приемников и фазовым дрожанием сигнала во времени в каналах передачи, даже в случаях, когда в кадре передачи используют множество способов модуляции.

Краткое описание чертежей

Фиг.1 представляет собой схематичный вид, показывающий частичную структуру обычного приемника, который включает в себя схему частотной/фазовой синхронизации, использующую цифровую ФАПЧ;

фиг.2 представляет собой схематичный вид, показывающий типичную структуру схемы частотной/фазовой синхронизации, которая использует цифровую ФАПЧ и которая предоставлена в схеме на фиг.1;

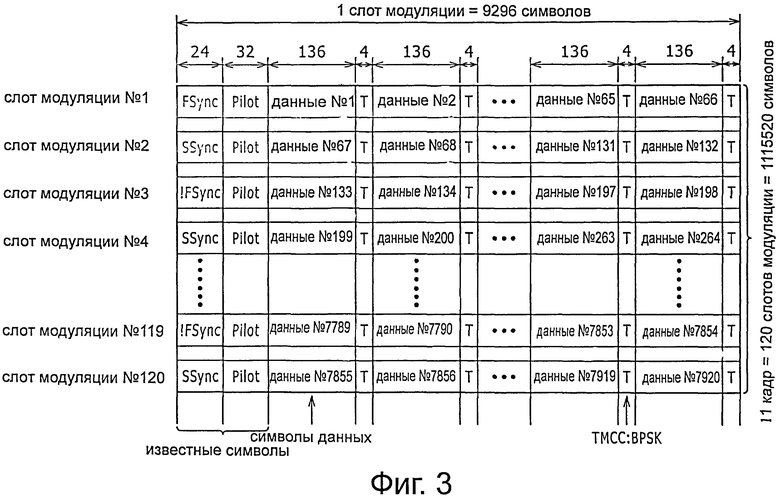

фиг.3 представляет собой схематичный вид, поясняющий структуру кадра Передовой системы цифрового спутникового вещания;

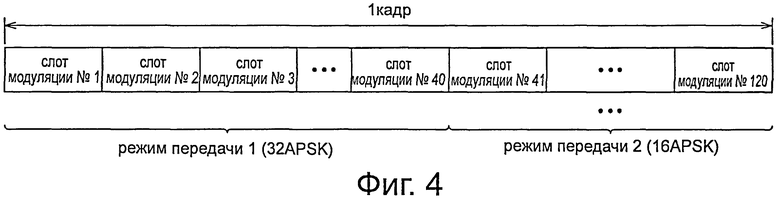

фиг.4 представляет собой схематичный вид, показывающий типовые режимы передачи в одном кадре Передовой системы цифрового спутникового вещания;

фиг.5 представляет собой блок-схему, показывающую типичную структуру схемы частотной/фазовой синхронизации, применяемую на практике в качестве одного варианта осуществления настоящего изобретения;

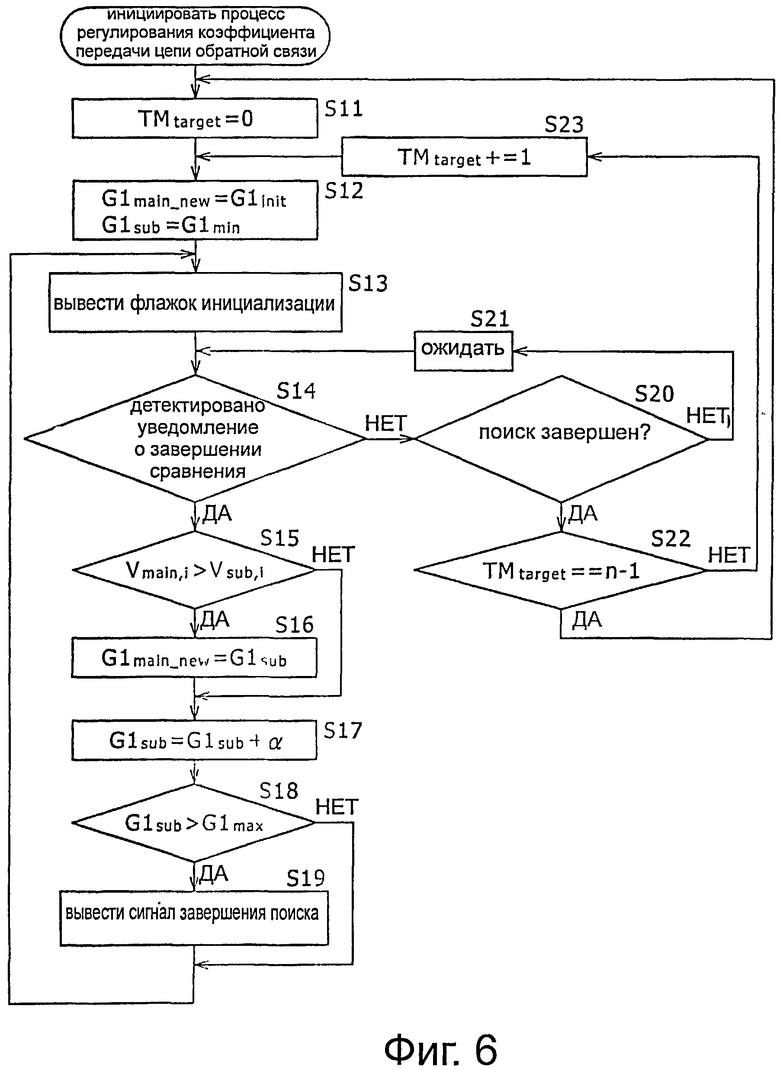

фиг.6 представляет собой блок-схему, поясняющую типичный процесс регулирования коэффициента передачи цепи обратной связи;

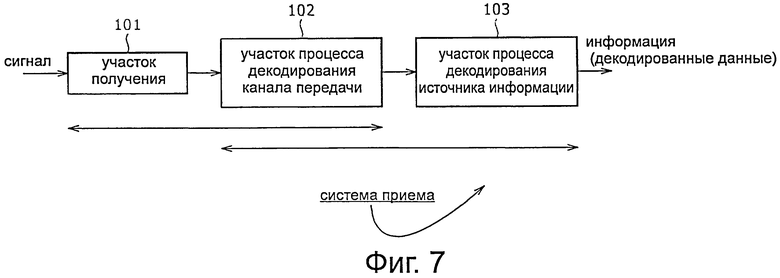

фиг.7 представляет собой блок-схему, показывающую типичную конфигурацию первого варианта осуществления системы приема, в которой используется схема частотной/фазовой синхронизации согласно вариантам осуществления настоящего изобретения;

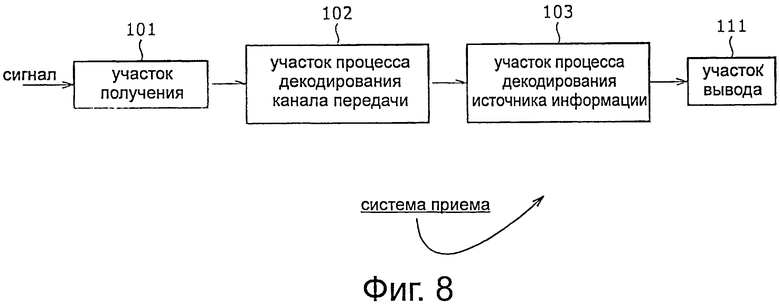

фиг.8 представляет собой блок-схему, показывающую типичную конфигурацию второго варианта осуществления системы приема, в которой используется схема частотной/фазовой синхронизации согласно вариантам осуществления настоящего изобретения;

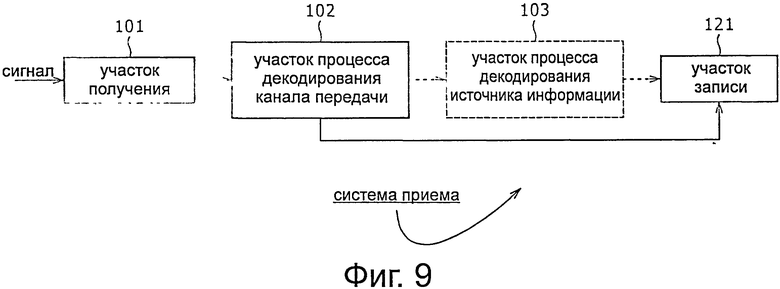

фиг.9 представляет собой блок-схему, показывающую типичную конфигурацию третьего варианта осуществления системы приема, в которой используется схема частотной/фазовой синхронизации согласно вариантам осуществления настоящего изобретения;

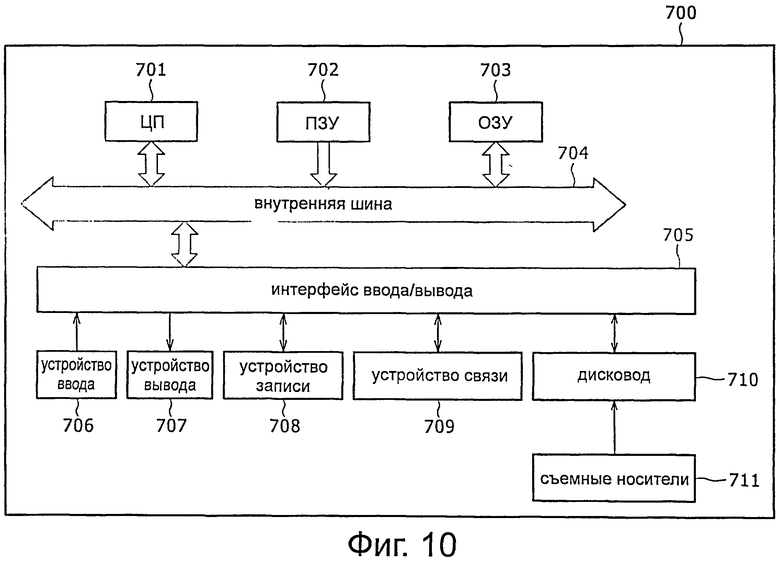

фиг.10 представляет собой блок-схему, показывающую типичную конфигурацию персонального компьютера.

Подробное описание предпочтительных вариантов осуществления

Некоторые предпочтительные варианты осуществления настоящего изобретения теперь будут детально описаны со ссылкой на прилагаемые чертежи.

Сначала изложена структура кадра Передовой системы цифрового спутникового вещания, предложенной в качестве системы цифрового спутникового вещания следующего поколения в Японии.

Фиг.3 представляет собой схематичный вид, поясняющий структуру кадра Передовой системы цифрового спутникового вещания. Как показано, один кадр скомпонован из 120 слотов модуляции. В данном примере слоты модуляции пронумерованы от №1 до №120.

Каждый слот модуляции включает в себя 24 символа для целей синхронизации (обозначены как «Fsync», «!Fsync» и «Ssync» на фиг.3) и 32 известных символа (каждый обозначен как «Pilot» на фиг.3), используемых для установки точек созвездий сигналов.

Также каждый слот модуляции включает в себя 66 элементов переданных данных, каждый из которых состоит из 136 символов. Например, элементы переданных данных в слоте модуляции №1 обозначены как «Данные №1» - «Данные №66», а элементы переданных данных в слоте модуляции №2 показаны как «Данные №67» - «Данные №132».

Более того, в каждом слоте модуляции сигнал ТМСС вставлен между каждыми двумя элементами переданных данных, при этом сигнал состоит из четырех символов, формирующих информацию управления о передаче и мультиплексировании. На фиг.3 ссылочный символ Т обозначает сигнал ТМСС.

Каждый кадр Передовой системы цифрового спутникового вещания, структура которого сформирована, как описано выше, составлен совокупно из 1115520 символов.

Передовая система цифрового спутникового вещания дает возможность множеству способов модуляции сосуществовать в каждом кадре. Например, в одном кадре можно определить до восьми режимов передачи, при этом каждый режим передачи позволяет принимать различные способы модуляции. В Передовой системе цифрового спутникового вещания можно использовать пять способов модуляции, состоящих из BPSK, QPSK, 8PSK, 16APSK и 32APSK.

Фиг.4 представляет собой схематичный вид, показывающий типовые режимы передачи в одном кадре Передовой системы цифрового спутникового вещания. В целях упрощения определены только два режима передачи. Как показано на фиг.4, режим передачи 1, заданный для способа передачи 32APSK, назначен слотам модуляции №1 - №40, а режим передачи 2 для способа передачи 16APSK назначен слотам модуляции №41 - №120.

Режим передачи каждого слота модуляции может быть определен анализом сигнала ТМСС, находящимся двумя кадрами ранее текущего кадра. Приемник, таким образом, выполнен с возможностью получения и сохранения всех сигналов ТМСС, вставленных в каждый слот модуляции кадра, принятый двумя кадрами ранее. Такое устройство позволяет приемнику определять способ модуляции для каждого слота модуляции в каждом принятом кадре. Независимо от режима передачи каждого слота модуляции следует отметить, что сигнал ТМСС, как правило, подвергается модуляции BPSK со сдвигом на π/2.

Настоящее изобретение ставит своей целью провести поиск оптимальных коэффициентов передачи цепи обратной связи, даже где используют множество способов модуляции в каждом кадре передачи, как, например, показано на фиг.4.

Фиг.5 представляет собой блок-схему, показывающую типовую структуру схемы частотной/фазовой синхронизации в качестве одного варианта осуществления настоящего изобретения.

Схема частотной/фазовой синхронизации, показанная на фиг.5, включена в состав схемы 3 демодуляции приемника, которая имеет ту же структуру, что и обозначенная на фиг.1.

Структура схемы частотной/фазовой синхронизации, показанная на фиг.5, в основном отличается от структуры стандартной схемы следующим: основная схема ФАПЧ дополнена подсхемой ФАПЧ, имеющей ту же структуру; коэффициенты передачи цепи обратной связи фильтров цепи обратной связи в основной схеме ФАПЧ и подсхеме ФАПЧ являются переменными; дополнительно предоставляется настройка регулирования коэффициента передачи цепи обратной связи.

Основная схема 31-1 ФАПЧ и подсхема 31-2 ФАПЧ сконструированы таким образом, чтобы использовать элементы, которые имеют одинаковые технические характеристики, и иметь одинаковую структуру схемы. Если в качестве коэффициента передачи цепи обратной связи фильтра цепи обратной связи и в основной схеме 31-1 ФАПЧ, и в подсхеме 31-2 ФАПЧ установлено одинаковое значение, и если один и тот же сигнал подают на вход двух схем, тогда сигнал, поступающий от основной схемы 31-1 ФАПЧ, совпадает с сигналом, переданным от подсхемы 31-2 ФАПЧ.

Как будет объяснено ниже, основная схема 31-1 ФАПЧ представляет собой схему, которая фактически выполняет синхронизированное детектирование. Подсхема 31-2 ФАПЧ может считаться схемой, которая выполняет «испытания» для установки коэффициента передачи цепи обратной связи, определяющего технические характеристики фильтра цепи обратной связи в основной схеме 31-1 ФАПЧ.

Сигнал приема ri, который представляет собой i-й сигнал (на i-м символе), подают на вход умножителя 41-1 основной схемы 31-1 ФАПЧ, умножителя 41-2 подсхемы 31-2 ФАПЧ и умножителя 32. Сигнал приема ri включает в себя ошибку фазы, которую можно записать в виде 2πΔft+θ.

Умножитель 41-1 основной схемы 31-1 ФАПЧ умножает сигнал приема ri на величину регулирования фазы е-j(2пΔft+θ), поступающую от генератора 44-1 с числовым программным управлением. Сигнал dmain,i, полученный посредством умножения, передают в детектор 42-1 ошибки фазы. Сигнал, поступающий от умножителя 41-1, совпадает с сигналом синхронизированного детектирования dmain,i, который представляет собой сигнал регулирования фазы, переданный от умножителя 32.

Детектор 42-1 ошибки фазы детектирует ошибку фазы, которая может сохраниться в сигнале, поступающем от умножителя 41-1, и выводит значение детектированной ошибки фазы основной схемы emain,i. Детектор 42-1 ошибки фазы выполняет детектирование ошибки фазы таким же способом, что и детектор 22 ошибки фазы, показанный на фиг.2. То же верно по отношению к детектору 42-2 ошибки фазы подсхемы 31-2 ФАПЧ, что будет обсуждаться позднее.

Значение детектированной ошибки фазы основной схемы emain,i, выводимое из детектора 42-1 ошибки фазы, передают в умножитель 51-1 фильтра 43-1 цепи обратной связи.

Фильтр 43-1 цепи обратной связи представляет собой пропорциональный интегральный фильтр нижних частот, который фильтрует значение детектированной ошибки фазы основной схемы emain,i, выводимое из детектора 42-1 ошибки фазы. Отфильтрованную величину передают в генератор 44-1 с числовым программным управлением.

В частности, умножитель 51-1 фильтра 43-1 цепи обратной связи умножает значение детектированной ошибки фазы основной схемы emain,i на G1main в соответствии с коэффициентом передачи цепи G1main цепи обратной связи, установленным участком 34 регулирования коэффициента передачи цепи обратной связи. Значение, полученное посредством умножения, выводят в умножитель 52-1 и сумматор 54-1.

Умножитель 52-1 далее умножает на G2 G1main-кратное значение детектированной ошибки фазы основной схемы emain,i, выводимое из умножителя 51-1. Величину, полученную посредством умножения, выводят в интегратор 53-1.

Интегратор 53-1 интегрирует выход от умножителя 52-1 и передает результат интегрирования в сумматор 54-1.

Сумматор 54-1 складывает выход из умножителя 51-1 и выход из интегратора 53-1 и выводит сумму сложения в виде результата фильтрации θmain,i в генератор 44-1 с числовым программным управлением.

Генератор 44-1 с числовым программным управлением генерирует величину регулирования фазы е-j(2пΔft+θ) на основе результата фильтрации из фильтра 43-1 цепи обратной связи и передает сгенерированную величину регулирования в умножители 41-1 и 32.

Умножитель 32 умножает сигнал приема ri на величину регулирования фазы е-j(2пΔft+θ), поступающую от генератора 44-1 с числовым программным управлением основной схемы 31-1 ФАПЧ. Сигнал, полученный посредством умножения, выводят в качестве сигнала синхронизированного детектирования dmain,i.

При этом сигнал, содержащий сигнал dmain,i, значение детектированной ошибки фазы основной схемы emain,i и результат фильтрации θmain,i, передают от основной схемы 31-1 ФАПЧ в качестве промежуточного сигнала основной схемы ФАПЧ в детектор 61 ошибки регулирования основной схемы ФАПЧ участка 33 сравнения ошибки регулирования ФАПЧ.

Подсхема 31-2 ФАПЧ также выполняет такую же обработку в отношении того же сигнала приема ri, в качестве сигнала, поступающего на вход основной схемы 31-1 ФАПЧ.

А именно умножитель 41-2 подсхемы 31-2 ФАПЧ умножает сигнал приема ri на величину регулирования фазы е-j(2пΔft+θ), поступающую от генератора 44-2 с числовым программным управлением. Сигнал dsub,i, полученный посредством умножения, выводят в детектор 42-2 ошибки фазы.

Детектор 42-2 ошибки фазы детектирует ошибку фазы, которая может сохраняться в сигнале, поступающем от умножителя 41-2, и соответственно выводит значение esub,i детектированной ошибки фазы подсхемы. Значение esub.i детектированной ошибки фазы подсхемы, выводимое из детектора 42-2 ошибки фазы, выводят в умножитель 51-2 фильтра 43-2 нижних частот.

Умножитель 51-2 фильтра 43-2 цепи обратной связи умножает значение esub,i детектированной ошибки фазы подсхемы на G1sub, заданную участком 34 регулирования коэффициента передачи цепи обратной связи. Значение, полученное посредством умножения, передают в умножитель 52-2 и сумматор 54-2.

Например, коэффициент передачи G1sub цепи обратной связи, заданный для умножителя 51-2, отличается от коэффициента передачи G1main цепи обратной связи, заданного для умножителя 51-1 основной схемы 31-1 ФАПЧ.

Умножитель 52-2 далее умножает на G2 G1sub-кратное значение esub,i детектированной ошибки фазы подсхемы, поступающую от умножителя 51-2. Значение, полученное посредством умножения, передают в интегратор 53-2. Умножитель 52-1 основной схемы 31-1 ФАПЧ и умножитель 52-2 подсхемы 31-2 ФАПЧ таким образом выполняют взвешивание с помощью одного и того же коэффициента передачи цепи обратной связи. Коэффициент передачи G2 обратной связи имеет заданную фиксированную величину.

Интегратор 53-2 интегрирует выход от умножителя 52-2 и передает результат интегрирования в сумматор 54-2.

Сумматор 54-2 складывает выход от умножителя 51-2 и выход от интегратора 53-2 и передает сумму сложения в качестве результата фильтрации θsub,i в генератор 44-2 с числовым программным управлением.

Генератор 44-2 с числовым программным управлением генерирует величину регулирования фазы е-j(2пΔft+θ) на основе результата фильтрации из фильтра 43-2 цепи обратной связи и выводит сгенерированную величину регулирования в умножитель 41-2.

При этом сигнал, содержащий сигнал dmain,i, значение esub,i детектированной ошибки фазы подсхемы и результат фильтрации θsub,i передают от подсхемы 31-2 ФАПЧ в качестве промежуточного сигнала подсхемы ФАПЧ в детектор 62 ошибки регулирования подсхемы ФАПЧ участка 33 сравнения ошибки регулирования ФАПЧ.

Детектор 61 ошибки регулирования основной схемы ФАПЧ участка 33 сравнения ошибки регулирования ФАПЧ получает промежуточный сигнал основной схемы ФАПЧ, поступающий от основной схемы 31-1 ФАПЧ, всякий раз, когда выводят сигнал приема ri. Например, детектор 61 ошибки регулирования основной схемы ФАПЧ вычисляет значение emain,i изменения детектированной ошибки фазы основной схемы, полученной из сигнала приема ri, имеющего заданное число символов. Величину изменения, полученную таким образом, передают в компаратор 63 в виде величины vmain ошибки регулирования.

Величину vmain ошибки регулирования вычисляют на основе результата умножения, выполняемого умножителем 41-1, т.е. на основе значения emain,i детектированной ошибки фазы основной схемы, представляющей детектированную ошибку фазы, сохраняющуюся в сигнале, который подвергался регулированию фазы основной схемой 31-1 ФАПЧ. По этой причине значение vmain ошибки регулирования обозначает ошибку регулирования фазы, выполняемую основной схемой 31-1 ФАПЧ.

Детектор 62 ошибки регулирования подсхемы ФАПЧ получает промежуточный сигнал подсхемы ФАПЧ, поступающий от подсхемы 31-2 ФАПЧ всякий раз, когда подают на вход сигнал приема ri. Например, детектор 62 ошибки регулирования подсхемы ФАПЧ вычисляет значение изменения значения esub,i детектированной ошибки фазы подсхемы, полученной из сигнала приема ri, имеющего заданное число символов. Значение изменения, полученное таким образом, передают в компаратор 63 в качестве значения vsub ошибки регулирования.

Значение vsub ошибки регулирования вычисляют на основе результата умножения, выполняемого умножителем 41-2, т.е. на основе значения esub,i детектированной ошибки фазы подсхемы, представляющей собой детектированную ошибку фазы, сохраняющуюся в сигнале, который подвергался регулированию фазы подсхемой 31-2 ФАПЧ. По этой причине значение vsub ошибки регулирования обозначает ошибку регулирования фазы, выполненную подсхемой 31-2 ФАПЧ.

Компаратор 63 сравнивает по абсолютному значению значение vmain ошибки регулирования, поступающей от детектора 61 ошибки регулирования основной схемы ФАПЧ, со значением vsub ошибки регулирования, поступающей от детектора 62 ошибки регулирования подсхемы ФАПЧ. Результат сравнения передают на участок 34 регулирования коэффициента передачи цепи обратной связи в ответ на уведомление о выводе результата сравнения, поступающего от таймера 64.

Как описано, фильтр 43-1 цепи обратной связи основной схемы 31-1 ФАПЧ и фильтр 43-2 нижних частот подсхемы 31-2 ФАПЧ используют различные коэффициенты G1main и G1sub обратной связи передачи цепи. Отсюда следует, что различие, отражающее несоответствие между коэффициентами передачи цепи G1main и G1sub цепи обратной связи, возникает в значении vmain ошибки регулирования, вычисленной детектором 61 ошибки регулирования основной схемы ФАПЧ, и в значении vsub ошибки регулирования, вычисленной детектором 62 ошибки регулирования подсхемы ФАПЧ.

В предшествующих абзацах рассмотрен пример, в котором значения vmain и vsub ошибки регулирования вычислены на основе значений emain,i и esub,i детектированной ошибки фазы основной схемы и подсхемы. И наоборот, значения vmain и vsub ошибки регулирования могут быть вычислены на основе сигнала dmain,i; на основе результата фильтрации θmain,i и сигнала dsub,I; или на основе результата фильтрации θsub,i.

Таймер 64 начинает отсчет времени после получения флажка инициализации, поступающего от участка 34 регулирования коэффициента передачи цепи обратной связи. По истечении заданного времени счета таймер 64 передает уведомление о завершении сравнения на участок 34 регулирования коэффициента передачи цепи обратной связи. Время, которое необходимо для вычисления значения ошибки регулирования, установлено на таймере 64, и это установленное время отсчитывается таймером 64. Таймер 64 также передает уведомление о выводе результата сравнения в компаратор 63 одновременно с выводом уведомления о завершении сравнения на участок 34 регулирования коэффициента передачи цепи обратной связи.

Участок 34 регулирования коэффициента передачи цепи обратной связи имеет расположенный в нем генератор 72 последовательности регулирования коэффициента передачи. Участок 34 регулирования коэффициента передачи цепи обратной связи проводит поиск оптимальных коэффициентов передачи цепи обратной связи при осуществлении контроля статуса работы основной схемы 31-1 ФАПЧ и подсхемы 31-2 ФАПЧ и задает детектированные оптимальные коэффициенты передачи цепи обратной связи для их соответствующих фильтров цепи обратной связи.

Например, если значение vmain ошибки регулирования, вычисленное детектором 61 ошибки регулирования основной схемы ФАПЧ, больше значения vsub ошибки регулирования, вычисленного детектором 62 ошибки регулирования подсхемы ФАПЧ, участок 34 регулирования коэффициента передачи цепи обратной связи устанавливает значение, равное коэффициенту передачи G1sub цепи обратной связи для фильтра 43-1 цепи обратной связи основной схемы 31-1 ФАПЧ, заменяя ранее установленный коэффициент передачи G1main цепи обратной связи.

То, что значение vmain ошибки регулирования больше значения vsub ошибки регулирования, означает, что синхронное получение может выполняться с меньшей ошибкой за счет установки коэффициента передачи G1sub цепи обратной связи, заданного для фильтра 43-2 цепи обратной связи подсхемы 31-2 ФАПЧ. Таким образом, в данном случае коэффициент передачи G1main обратной связи для фильтра 43-1 цепи обратной связи основной схемы 31-1 ФАПЧ заменяют коэффициентом передачи G1sub цепи обратной связи.

Если значение vsub ошибки регулирования, вычисленное детектором 62 ошибки регулирования подсхемы ФАПЧ, больше значения vmain ошибки регулирования, вычисленного детектором 61 ошибки регулирования основной схемы ФАПЧ, генератор 72 последовательности регулирования коэффициента передачи участка 34 регулирования коэффициента передачи цепи обратной связи оставляет коэффициент G1main передачи цепи обратной связи неизменным для фильтра 43-1 цепи обратной связи основной схемы 31-1 ФАПЧ.

То, что значение vsub ошибки регулирования больше, чем значение vmain ошибки регулирования, как описано выше, означает, что использование коэффициента передачи G1main цепи обратной связи неизменным позволяет выполнять синхронный сбор данных с меньшей ошибкой, чем если используется коэффициент передачи G1sub цепи обратной связи. Таким образом, в этом случае коэффициент передачи G1main цепи обратной связи для фильтра 43-1 цепи обратной связи основной схемы 31-1 ФАПЧ не будет замещен коэффициентом передачи G1sub цепи обратной связи.

Как описано, после того, как было определено, заменять ли коэффициент передачи G1main цепи обратной связи, изменяют коэффициент передачи G1sub цепи обратной связи для фильтра 43-2 цепи обратной связи. Затем проводят другое сравнение по абсолютному значению между значением vsub ошибки регулирования и значением vmain ошибки регулирования так, чтобы определить, заменять ли коэффициент передачи G1main цепи обратной связи. Таким образом, продолжаются поиски оптимальных коэффициентов передачи цепи.

Когда предстоит изменить коэффициент передачи G1sub цепи обратной связи, генератор 72 последовательности регулирования коэффициента передачи устанавливает коэффициент передачи G1sub цепи обратной связи, используя формулу G1sub=G1sub+α, где α означает самый маленький шаг квантования установленного G1. В данном случае, если установленное G1sub превышает максимальное допустимое значение G1max, участок 34 регулирования коэффициента передачи цепи обратной связи выводит сигнал о завершении поиска.

Участок 34 регулирования коэффициента передачи цепи обратной связи заставляет расположенный внутри участок 71 выбора регулирования коэффициента передачи для конкретного режима передачи хранить коэффициент передачи G1main цепи обратной связи для каждого из режимов передачи, предусмотренных для селективного вывода коэффициента передачи цепи обратной связи. По этой причине участок 71 выбора регулирования коэффициента передачи для конкретного режима передачи располагает количеством регистров, равным максимальному числу N задействованных режимов передачи (например, N=8), при этом каждый регистр используется для хранения оптимального коэффициента передачи цепи обратной связи для режима передачи, о котором идет речь. Предполагается, что эти регистры предоставляют выходные значения G1main0, G1main1, … G1mainN-1.

Режим передачи сигнала приема ri, способ модуляции, принятый для каждого режима передачи, и слоты модуляции, назначенные режиму передачи, о котором идет речь, устанавливаются ТМСС, который поступает от декодера 91 коррекции ошибки.

Генератор 92 номера режима передачи подсчитывает полученные символы, начиная от флажка старта входного кадра, и на основе величины отсчета полученного символа устанавливает, какому слоту модуляции принадлежит текущий полученный символ. Также на основе информации, полученной из сигнала ТМСС и представляющей слоты модуляции, назначенные каждому режиму передачи, генератор 92 номера режима передачи определяет номер ТМ, идентифицирующий режим передачи текущего полученного символа (ТМ именуют номером режима передачи) и передает номер режима передачи ТМ на участок 34 регулирования коэффициента передачи цепи.

Например, если текущая полученная схема передачи имеет «n» режимов передачи, которые мультиплексированы в ней, тогда номерами режимов передачи ТМ являются 0, 1, …, n-1.

Генератор 72 последовательности регулирования коэффициента передачи хранит номер режима передачи TMtarget, для которого предстоит провести поиск оптимального коэффициента передачи цепи обратной связи. Только в процессе приема символов, для которых TM=TMtarget, генератор 72 последовательности регулирования коэффициента передачи позволяет функционировать участку 33 сравнения ошибки регулирования ФАПЧ и участку 71 выбора регулирования коэффициента передачи для конкретного режима передачи. Генератор 72 последовательности регулирования коэффициента передачи передает обновленный сигнал EN (разрешения), уровень которого становится высоким в процессе приема символов, для которых TM=TMtarget, на участок 33 сравнения ошибки регулирования ФАПЧ и участок 71 выбора регулирования коэффициента передачи для конкретного режима передачи.

При высоком уровне обновленного сигнала EN участок 33 сравнения ошибки регулирования ФАПЧ выполняет процесс, описанный ниже. В случае, когда коэффициент передачи G1main цепи обратной связи предстоит заменить коэффициентом передачи G1sub цепи обратной связи при высоком уровне обновленного сигнала EN, участок генерации флажка обновления внутри участка 71 выбора регулирования коэффициента передачи для конкретного режима передачи передает флажок для записи в регистр коэффициента передачи цепи обратной связи, соответствующий номеру режима передачи ТМ, который действителен на данный момент.

Когда схему частотной/фазовой синхронизации, показанную на фиг.5, приводят в действие, номер режима передачи, для которого предстоит провести поиск оптимального коэффициента передачи цепи обратной связи, устанавливается в исходное состояние (TMtarget=0). Затем в исходное положение устанавливаются коэффициенты передачи цепи обратной связи для основной схемы 31-1 ФАПЧ и подсхемы 31-2 ФАПЧ.

После установления в исходное положение коэффициентов передачи цепи обратной связи основной схемы 31-1 ФАПЧ и подсхемы 31-2 ФАПЧ участок 34 регулирования коэффициента передачи цепи обратной связи передает флажок инициализации на участок 33 сравнения ошибки регулирования ФАПЧ.

После получения флажка инициализации от участка 34 регулирования коэффициента передачи цепи обратной связи участок 33 сравнения ошибки регулирования ФАПЧ сбрасывает результат сравнения значения ошибки регулирования, который действителен на данный момент, а также таймер 64. Затем участок 33 сравнения ошибки регулирования ФАПЧ вычисляет значение ошибки регулирования vmain,i и vsub,i, как описано выше. Компаратор 63 инициирует сравнение этих величин ошибки регулирования по абсолютному значению.

После сбрасывания таймер 64 участка 33 сравнения ошибки регулирования ФАПЧ запускает время отсчета. Когда время отсчета, необходимое для вычисления величины ошибки регулирования, истекает, таймер 64 передает уведомление о завершении сравнения на участок 34 регулирования коэффициента передачи цепи обратной связи. В то же время таймер 64 передает команду вывода результата сравнения в компаратор 63. Это, в свою очередь, заставляет компаратор 63 передавать результат сравнения ошибки регулирования на участок 34 регулирования коэффициента передачи цепи обратной связи.

Принимая во внимание результат сравнения ошибки регулирования, участок 34 регулирования коэффициента передачи цепи обратной связи соответственно регулирует коэффициенты передачи цепи обратной связи, которые поступают в фильтры 43-1 и 43-2 цепи обратной связи. На данном этапе, если коэффициент передачи G1main цепи обратной связи предстоит заменить коэффициентом передачи G1sub цепи обратной связи, генератор 72 последовательности регулирования коэффициента передачи передает коэффициент передачи G1sub цепи обратной связи на участок 71 выбора регулирования коэффициента передачи для конкретного режима передачи, как описано выше.

Участок 71 выбора регулирования коэффициента передачи для конкретного режима передачи обновляет величину, хранящуюся в регистре коэффициента передачи G1main[тм] цепи обратной связи, одном из множества внутренних регистров, который соответствует номеру режима передачи ТМ, с помощью значения, поступающего на вход от генератора 72 последовательности регулирования коэффициента передачи.

Также участок 71 выбора регулирования коэффициента передачи для конкретного режима передачи выбирает из G1main0, G1main1, … G1mainN-1 коэффициент передачи цепи обратной связи, соответствующий номеру режима передачи ТМ, поступающему от генератора 92 номера режима передачи, и передает выбранный коэффициент передачи цепи обратной связи в виде коэффициента передачи цепи в фильтр 43-1 цепи обратной связи.

Если сигнал завершения поиска передают от генератора 72 последовательности регулирования коэффициента передачи до получения уведомления о завершении сравнения от участка 33 сравнения ошибки регулирования ФАПЧ, тогда выполняют проверку для выяснения, равно ли значение TMtarget n-1 для того, чтобы определить, завершился ли поиск оптимальных коэффициентов передачи цепи обратной связи для всех режимов передачи. Если значение TMtarget не равно n-1, тогда величина TMtarget увеличивается на 1 с целью проведения поиска оптимального коэффициента передачи цепи обратной связи для следующего режима передачи. В то же время коэффициенты передачи цепи обратной связи для основной схемы 31-1 ФАПЧ и подсхемы 31-2 ФАПЧ снова устанавливаются в исходное положение.

В порядке, описанном выше, проводят поиск оптимального коэффициента передачи цепи обратной связи в отношении каждого значения TMtarget от 0 до n-1. Это позволяет задать оптимальный коэффициент передачи цепи обратной связи для каждого режима передачи, задействованного на основе разных способов модуляции.

И наоборот, если сигнал о завершении поиска передают от генератора 72 последовательности регулирования коэффициента передачи до получения уведомления о завершении сравнения от участка 33 сравнения ошибки регулирования ФАПЧ и если значение TMtarget равно n-1, тогда значение TMtarget можно сбрасывать до 0. Т.е. после выполнения поиска оптимального коэффициента передачи цепи обратной связи в отношении значений TMtarget от 0 до n-1, можно снова инициировать другой поиск оптимального коэффициента передачи цепи обратной связи в отношении каждой величины TMtarget от 0 до n-1.

Таким образом, даже в случае, когда имеет место дрожание сигнала во времени в характеристиках передачи задействованных каналов передачи, поиски оптимальных коэффициентов передачи цепи обратной связи могут выполняться постоянно, и детектированные коэффициенты передачи цепи обратной связи могут использоваться непрерывно.

Ниже со ссылкой на блок-схему на фиг.6 поясняется типичный процесс регулирования коэффициента передачи цепи обратной связи, выполняемый схемой частотной/фазовой синхронизации, показанной на фиг.5.

На этапе S11 генератор 72 последовательности регулирования коэффициента передачи устанавливает переменную TMtarget в исходное состояние 0.

На этапе S12 генератор 72 последовательности регулирования коэффициента передачи устанавливает в исходное состояние тот регистр коэффициента передачи цепи обратной связи внутри участка 71 выбора регулирования коэффициента передачи для конкретного режима передачи, который соответствует переменной TMtarget. В данном примере установка регистра коэффициента передачи цепи, о котором идет речь, представлена G1main_new, а его исходная величина - G1init. Установка G1main_new используется в виде коэффициента передачи цепи G1main для фильтра 43-1 цепи обратной связи.

Также на этапе S12 генератор 72 последовательности регулирования коэффициента передачи устанавливает в исходное положение коэффициент передачи G1sub цепи обратной связи для фильтра 43-2 цепи обратной связи. Исходное значение коэффициента передачи G1sub цепи обратной связи представляет собой наименьший коэффициент передачи цепи обратной связи, т.е. G1min. Параметр G1sub используется в качестве коэффициента передачи G1sub цепи обратной связи для фильтра 43-2 цепи обратной связи.

Переход на этап S13 осуществляют после установки коэффициента передачи цепи обратной связи в исходное положение. На этапе S13 участок 34 регулирования коэффициента передачи цепи обратной связи выводит флажок инициализации на участок 33 сравнения ошибки регулирования ФАПЧ.

После получения флажка инициализации участок 33 сравнения ошибки регулирования ФАПЧ сбрасывает уже выполненный результат сравнения ошибки регулирования, а также значение отсчета внутреннего таймера.

Также детектор 61 ошибки регулирования основной схемы ФАПЧ участка 33 сравнения ошибки регулирования ФАПЧ вычисляет значение vmain ошибки регулирования на основе промежуточного сигнала основной схемы ФАПЧ, поступающего от основной схемы 31-1 ФАПЧ. Детектор 62 ошибки регулирования подсхемы ФАПЧ вычисляет значение vsub ошибки регулирования на основе промежуточного сигнала подсхемы ФАПЧ, поступающего от подсхемы 31-2 ФАПЧ.

После сброса таймер 64 инициирует отсчет времени. После истечения заданного времени отсчета, необходимого для вычисления значений vmain и vsub ошибки регулирования, таймер 64 выводит уведомление о завершении сравнения на участок 34 регулирования коэффициента передачи цепи обратной связи. В то же время таймер 64 выводит команду вывода результата сравнения в компаратор 63. В ответ на команду вывода результата сравнения компаратор 63 выводит результат сравнения по абсолютному значению между значениями vmain и vsub ошибки регулирования на участок 34 регулирования коэффициента передачи цепи обратной связи.

На этапе S14 генератор 72 последовательности регулирования коэффициента передачи определяет, детектировано ли уведомление о завершении сравнения, выводимое из таймера 64. Если определяют, что уведомление о завершении сравнения еще не детектировано, управление передают на этап S20.

На этапе S20 определяют, выведен ли сигнал завершения поиска. Если определяют, что сигнал завершения поиска еще не выведен, управление передают на этап S21. На этапе S21 уведомление о завершении сравнения от таймера 64 запрашивают с интервалами заданного периода времени в состоянии ожидания. Затем управление возвращают на этап S14.

Если на этапе S14 определяют, что детектировано уведомление о завершении сравнения, управление передают на этап S15.

На этапе S15 генератор 72 последовательности регулирования коэффициента передачи определяет, имеет ли место vmain>vsub на основе результата сравнения, поступающего от компаратора 63.

Если на этапе S15 определяют, что vmain>vsub, осуществляется переход на этап S16. На этапе S16 генератор 72 последовательности регулирования коэффициента передачи заменяет коэффициент передачи цепи G1main_new на G1sub, заданный в настоящий момент в качестве коэффициента передачи цепи обратной связи для фильтра 43-2 цепи обратной связи. На данном этапе генератор 72 последовательности регулирования коэффициента передачи выводит заданный сигнал на участок генерации флажка обновления внутри участка 71 выбора регулирования коэффициента передачи для конкретного режима передачи. В свою очередь участок генерации флажка обновления передает флажок для записи в регистр коэффициента передачи цепи обратной связи, соответствующий номеру режима передачи ТМ, который действителен на данный момент.

Если на этапе S15 определяют, что vmain≤vsub вместо vmain>vsub, тогда этап S16 пропускают.

На этапе S17 генератор 72 последовательности регулирования коэффициента передачи устанавливает G1sub+α и вместе с тем обновляет коэффициент передачи G1sub цепи обратной связи, где α означает величину коэффициента передачи, соответствующую самому маленькому шагу квантования коэффициента передачи G1 (G1main и G1sub) цепи обратной связи.

На этапе S18 генератор 72 последовательности регулирования коэффициента передачи определяет, превышает ли коэффициент передачи цепи G1sub, обновленный на этапе S17, максимально допустимое значение G1max.

Если на этапе S18 определяют, что коэффициент передачи цепи G1sub превысил максимальное значение G1max, управление передают на этап S19. На этапе S19 генератор 72 последовательности регулирования коэффициента передачи выводит сигнал завершения поиска.

Если на этапе S18 определяют, что коэффициент передачи цепи G1sub не превысил максимальное значение G1max, тогда этап S19 пропускают.

Управление возвращают на этап S13, если на этапе S18 определяют, что коэффициент передачи G1sub цепи обратной связи не превысил максимальную величину G1max, или после завершения этапа S19.

После вывода на этапе S19 сигнала завершения поиска вывода сигнала подтверждают на этапе S20. Затем управление возвращают на этап S22.

На этапе S22 генератор 72 последовательности регулирования коэффициента передачи определяет, равна ли переменная TMtarget n-1. Если определяют, что переменная TMtarget не равна n-1, управление передают па этап S23. На этапе S23 генератор 72 последовательности регулирования коэффициента передачи увеличивает переменную TMtarget на 1. Управление затем возвращают на этап S12. Т.е. выполняют другой поиск оптимального коэффициента передачи цепи для следующего номера режима передачи.

Если на этапе S22 определяют, что переменная TMtarget равна n-1, управление возвращают на этап S11. Т.е. после выполнения поиска оптимальных коэффициентов передачи цепи обратной связи для всех номеров режима передачи инициируют второй поиск коэффициента передачи цепи обратной связи для каждой величины TMtarget от 0 до n-1. Во втором и последующем поисках нет необходимости устанавливать G1main_new в исходное состояние на этапе S12.

И, наоборот, если на этапе S22 определяют, что переменная TMtarget равна n-1, процесс регулирования коэффициента передачи цепи обратной связи можно завершить.

Процесс регулирования коэффициента передачи цепи выполняют в порядке, описанном выше. Таким образом, согласно настоящему изобретению можно провести поиск оптимальных коэффициентов передачи цепи обратной связи в соответствии с отдельными отличиями приемников и дрожанием сигнала во времени в каналах передачи, даже в случаях, когда в кадре передачи используют множество способов модуляции.

Предшествующие абзацы поясняют примеры, в которых выполняют поиск оптимального коэффициента передачи цепи обратной связи в качестве коэффициента передачи G1 цепи обратной связи для использования в прямых операциях умножения, выполняемых над детектированной ошибкой фазы в схеме частотной/фазовой синхронизации. И наоборот, можно выполнять поиск коэффициента передачи G2 цепи обратной связи для использования в операции умножения, которую предстоит выполнить над ошибкой фазы, возникающей в результате умножения с использованием коэффициента передачи G1 цепи обратной связи.

В качестве другой альтернативы можно выполнить поиски и коэффициента передачи G1 цепи обратной связи, и коэффициента передачи G2 цепи обратной связи.

Фиг.7 представляет собой блок-схему, показывающую типовую конфигурацию первого варианта осуществления системы приема, в которой используется схема частотной/фазовой синхронизации по вариантам осуществления настоящего изобретения.

Система приема на фиг.7 состоит из участка 101 получения, участка 102 процесса декодирования канала передачи и участка 103 процесса декодирования источника информации.

Участок 101 получения получает сигнал по каналам передачи, таким как наземные системы цифрового вещания, спутниковые системы цифрового вещания, сети CATV и Интернет (не показаны), и пересылает полученный сигнал на участок 102 процесса декодирования канала передачи.

Принимая во внимание сигнал, полученный участком 101 получения по каналам передачи, участок 102 процесса декодирования канала передачи выполняет процесс декодирования канала передачи, включающий в себя синхронизированное детектирование и коррекцию ошибок для полученного сигнала, и пересылает сигнал, полученный в результате процесса декодирования, на участок 103 процесса декодирования источника информации. Т.е. участок 102 процесса декодирования канала передачи включает в себя структуру схемы частотной/фазовой синхронизации, показанную на фиг.5, которая выполняет вышеупомянутое синхронизированное детектирование.

Участок 103 процесса декодирования источника информации выполняет процесс декодирования источника информации для сигнала, который подвергался процессу декодирования канала передачи, при этом процесс декодирования источника информации включает в себя процесс расширения сжатой информации обратно до исходной информации, посредством которой были собраны переданные данные.

Т.е. сигнал, данные о котором собраны участком 101 сбора данных по каналам передачи, мог подвергаться кодированию для сжатия, посредством которого исходная информация была сжата так, чтобы уменьшить величину данных, таких как видео- или аудиоданные. В таком случае участок 103 процесса декодирования источника информации выполняет процесс декодирования источника информации для сигнала, который подвергался процессу декодирования канала передачи, при этом процесс декодирования источника информации включает в себя процесс расширения сжатой информации обратно до исходной информации.

Если сигнал, полученный участком 101 получения по каналам передачи, не подвергался кодированию для сжатия, участок 103 обработки декодирования источника информации не выполняет процесс расширения сжатой информации обратно до исходной информации. Процесс расширения включает в себя декодирование MPEG, например. Процесс декодирования источника информации может включать в себя дескремблирование в дополнение к процессу расширения.

Система приема на фиг.7 может использоваться в ТВ-тюнерах, например, для приема цифровых ТВ-передач. Участок 101 получения, участок 102 обработки декодирования канала передачи и участок 103 обработки декодирования источника информации могут каждый быть выполнены в виде отдельного устройства (аппаратного средства, например, ИС (интегральной схемы) или программного модуля).

И, наоборот, участок 101 получения, участок 102 обработки декодирования канала передачи и участок 103 обработки декодирования источника информации могут быть выполнены все вместе в виде отдельного устройства. В качестве другой альтернативы участок 101 получения и участок 102 обработки декодирования канала передачи могут быть выполнены совместно в виде отдельного устройства.

Фиг.8 представляет собой блок-схему, показывающую типичную конфигурацию второго варианта осуществления системы приема, в которой используется схема частотной/фазовой синхронизации по вариантам осуществления настоящего изобретения.

Компоненты на фиг.8 с соответствующими их эквивалентами, показанными на фиг.7, обозначены аналогичными ссылочными позициями, и их объяснения могут быть опущены, когда это уместно.

Конфигурация системы приема на фиг.8 является общей с конфигурацией ее эквивалента на фиг.7, в котором предусмотрены участок 101 получения, участок 102 обработки декодирования канала передачи и участок 103 процесса декодирования источника информации. С другой стороны, конфигурация на фиг.8 отличается от конфигурации на фиг.7 тем, что в ней дополнительно предоставлен участок 111 вывода.

Участок 111 вывода может, как правило, состоять из устройства отображения для отображения изображений и из динамиков для вывода звуков. По существу участок 111 вывода выводит изображения и звуки, извлеченные из сигнала, поступающего от участка 103 процесса декодирования источника информации. Вкратце, участок 111 вывода представляет собой компонент, который выводит изображения и/или звуки.

Система приема на фиг.8 может использоваться, например, в телевизорах для приема цифровых ТВ-передач и радиоприемниках для приема радиопередач.

Если сигнал, данные о котором собирают на участке 101 сбора данных, не подвергался кодированию для сжатия, тогда сигнал, передаваемый от участка 102 процесса декодирования канала передачи, подают напрямую на участок 111 вывода.

Фиг.9 представляет собой блок-схему, показывающую типичную конфигурацию третьего варианта осуществления системы приема, в которой используется схема частотной/фазовой синхронизации вариантов осуществления настоящего изобретения.

Компоненты на фиг.9 с соответствующими их эквивалентами, показанными на фиг.7, обозначены аналогичными ссылочными позициями, и их объяснения могут быть опущены, когда это уместно.

Конфигурация системы приема на фиг.9 является общей с конфигурацией ее эквивалента на фиг.7, в котором предусмотрены участок 101 получения и участок 102 обработки декодирования канала передачи. С другой стороны, конфигурация на фиг.9 отличается от конфигурации на фиг.7 тем, что в ней не предусмотрен участок 103 процесса декодирования источника информации и дополнительно обеспечен участок 121 записи.

Участок 121 записи записывает(хранит) сигнал (например, пакеты TS в формате MPEG), передаваемый от участка 102 процесса декодирования канала передачи на носитель записи(информации), такой как оптические диски, жесткие диски (магнитные диски) и карты флеш-памяти.

Вышеописанная система приема на фиг.9 может использоваться, например, в устройствах записи для записи ТВ-передач.

В другом примере система приема на фиг.9 может быть снабжена участком 103 процесса декодирования источника информации. В данном случае участок 121 записи может записывать сигнал, который подвергался процессу декодирования источника информации участком 103 процесса декодирования источника информации, т.е. изображения и звуки, данные о которых собраны посредством процесса декодирования.

Ряд процессов, описанных выше, может выполняться или аппаратными, или программными средствами. В случае, когда предстоит выполнить обработку на основе программных средств, программы, составляющие эти программные средства, могут быть либо помещены заблаговременно в выделенные аппаратные средства используемого компьютера или установлены после использования через вычислительную сеть или с соответствующего носителя записи на универсальный персональный компьютер или аналогичное оборудование, такое как персональный компьютер 700, показанный на фиг.10, который исполнен с возможностью выполнения разнообразных функций на основе установленных программ.

На фиг.10 ЦП (центральный процессор) 701 выполняет различные процессы в соответствии с программами, хранящимися в ПЗУ (постоянном запоминающем устройстве) 702 или в соответствии с программами, загруженными из устройства 708 записи в ОЗУ (оперативное запоминающее устройство) 703. ОЗУ 703 может также размещать данные и другие ресурсы, необходимые ЦП 701 для выполнения разнообразной обработки.

ЦП 701, ПЗУ 702 и ОЗУ 703 соединены посредством шины 704. Интерфейс 705 ввода/вывода соединен с шиной 704.

Интерфейс 705 ввода/вывода соединен с устройством 706 ввода, устройством 707 вывода, устройством 708 записи и устройством 709 связи. Устройство 706 ввода, как правило, состоит из клавиатуры и мыши. Устройство 707 вывода обычно образовано блоком отображения, таким как ЖКД (жидкокристаллический дисплей) и динамиками. Устройство 708 записи, как правило, сформировано жестким диском. Устройство 709 связи обычно образовано модемом и интерфейсом вычислительной сети, таким как карта ЛВС. Устройство 709 связи осуществляет связь посредством вычислительных сетей, включая Интернет.

Дисковод 710 может быть далее соединен при необходимости с интерфейсом 705 ввода/вывода. Съемный носитель 711, такой как магнитные диски, оптические диски, магнитооптические диски или полупроводниковые блоки памяти, может быть загружен в дисковод 710. Компьютерные программы могут быть извлечены с загруженного съемного носителя и установлены при необходимости на устройство 708 записи.

В случае, когда вышеописанный ряд процессов предстоит выполнить программными средствами, программы, составляющие эти программные средства, могут быть установлены посредством вычислительных сетей, включая Интернет, или с носителей информации, таких как съемные носители 711.