Заявляемое изобретение относится к области цифровой обработки сигналов (ЦОС) различного назначения и может быть использовано при обработке видео- и аудиосигналов в реальном масштабе времени. Для решения задач ЦОС различного назначения применимы определенные подклассы дискретных полиномиальных преобразований (ДПП). Например, дискретных ортогональных (унитарных) преобразований - дискретного преобразования Фурье (ДПФ) и Хартли (ДПХ), как прямого, так и обратного [1, стр.21], а также цифровых фильтров с импульсной характеристикой конечной длительности (КИХ-фильтров) [2, стр.357].

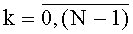

Существенной проблемой при проектировании устройств для выполнения ДПП является выбор такой его структуры, при которой обеспечивается как высокое быстродействие, так и универсальность данного устройства применительно к реализации заданного подкласса ДПП. Одним из способов повышения быстродействия указанного устройства является реализация конвейерной обработки данных с сохранением промежуточных результатов. Для устройств вычислительной техники (ВТ), реализованных указанным способом, максимальное быстродействие определено как сумма максимального времени задержки функционирования одной из ступеней конвейера и максимального времени задержки одного из регистров, сохраняющих промежуточные результаты. Универсальность устройства для вычисления ДПП достигается за счет возможности варьирования элементов системы функций φki(xk),

Согласно [2, стр.357], КИХ-фильтр (нерекурсивный цифровой фильтр) реализуем на основе (1) для системы функций φk(xk)=a

k·хk на конечном интервале длины N, N=2c, где xk - значение сигнала в k-й момент времени,

Известна реализация быстрого преобразования Хартли и Фурье при использовании конвейеризации процесса вычисления базовой операции («бабочки») алгоритма быстрого ДПФ и ДПХ [RU(11) 2190874(13) , C2 G06F 17/14, 20.07.1999]. Недостатком данной реализации является ограничение по количеству выполняемых дискретных преобразований.

Известна реализация ДПФ на конечном интервале N=2c при использовании процессоров, для которой обеспечивается максимальное быстродействие за счет оптимизации процесса извлечения коэффициентов ДПФ из памяти [RU(11) 2290687(13), C1 G06F 17/14 (2006.01), 31.05.2005]. Недостатком данной реализации является ограничение по количеству выполняемых дискретных преобразований.

Известна реализация универсального цифрового фильтра с программируемой структурой, которая, помимо КИХ-фильтра, позволяет реализовать и авторегрессионный фильтр [RU(11) 2399152(13), C2 H03H 17/04, H03H 17/06, H03H 21/00 (2006.01), 12.03.2008]. Недостатки данной реализации - ограничение по количеству выполняемых дискретных преобразований и низкое быстродействие.

Наиболее близким по технической сущности к заявляемому изобретению является устройство для формирования остатка по заданному модулю, содержащее Т блоков формирования частичных остатков с сохранением вычисленных результатов, два параллельных регистра, мультиплексор, компаратор и блок вычитания, причем t-й блок формирования частичных остатков,

К причинам, препятствующим достижению технического результата при использовании известного устройства, относится ограничение по количеству выполняемых ими дискретных преобразований, что существенно ограничивает область его применения.

Технический результат заключается в расширении функциональных возможностей устройства для вычисления ДПП, структура которого может быть настроена для выполнения различных подклассов ДПП (например, Фурье, Уолша, Хаара, Хартли, косинусного и т.п.), а также для реализации КИХ-фильтров. Настройка производится путем задания системы функций на конечном интервале длины N и заключается в занесении всевозможных значений функций φki(xk) при заданных значениях xk,

Технический результат достигается тем, что в устройство для вычисления дискретных полиномиальных преобразований, содержащее t-й комбинационный сумматор для N ƒ-разрядных двоичных чисел с одним выходом на (ƒ+log2N) разрядов каждый,

Каждый из Т блоков вычисления системы функций ДПП может быть настроен для реализации произвольной системы функций φki(xk) от заданных значений xk,

Схема устройства для вычисления дискретных полиномиальных преобразований представлена на фиг.1, а схемы системы из n N-разрядных регистров сдвига, t-го блока вычисления системы функций ДПП и t-го комбинационного сумматора для N ƒ-разрядных двоичных чисел,

Устройство для вычисления ДПП, содержит Т комбинационных сумматоров 11, …, 1T для N ƒ-разрядных двоичных чисел, систему 2 из n N-разрядных регистров сдвига, блоки 3t вычисления системы функций ДПП,

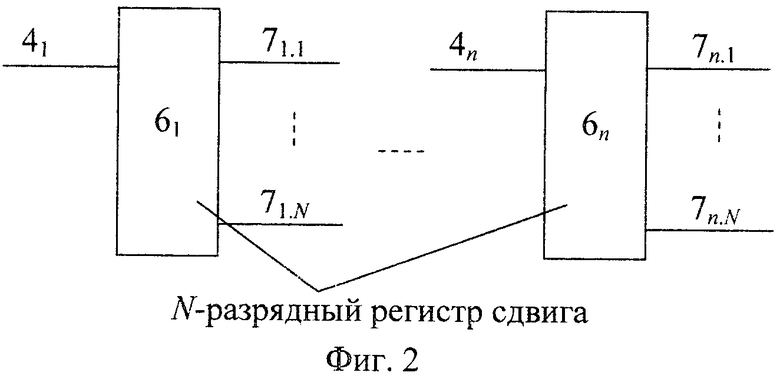

На фиг.2 представлена система 2 из n N-разрядных регистров сдвига, которая включает n N-разрядных регистров сдвига 6b,

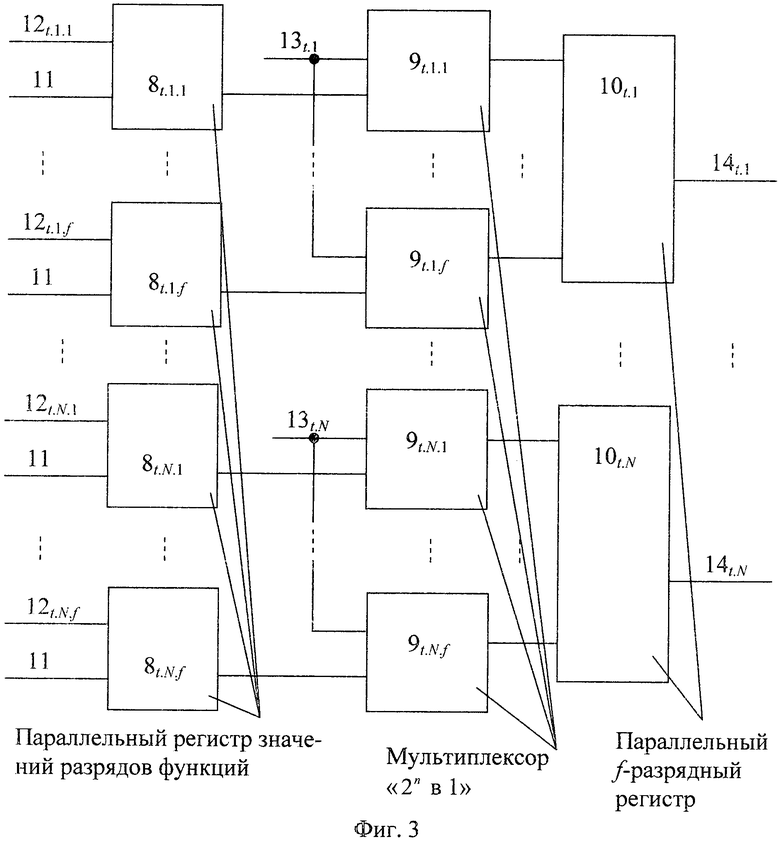

На фиг.3 представлен один из блоков 3t вычисления системы функций ДПП вида φk(t-1)(xk),

На фиг.4 изображен комбинационный сумматор 1t,

Рассмотрим устройство для вычисления дискретных полиномиальных преобразований в работе.

В предлагаемом устройстве на этапе инициализации в параллельные регистры 8t.(k+1).p значений разрядов функции разрядности 2n по сигналу 11 инициализации параллельно заносятся соответствующие значения p-x двоичных разрядов значения функций φk(t-1)(xk) системы (1),

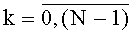

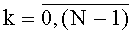

На этапе функционирования на каждом такте работы устройства для вычисления ДПП на вход 4 по синхросигналам, генерируемым через период времени ТУТПП, поступают n-разрядные двоичные числа xk,

Во время поступления следующего, (N·ТУТПП+1)-го, синхросигнала значения с выходов каждого из мультиплексоров 9t.(k+1).p «2n в 1» сохраняются в параллельных ƒ-разрядных регистрах 10t.(k+1),

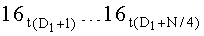

Во время поступления синхросигнала под номером (N·ТУТПП+2) значения частичных сумм, снимаемых с выходов сумматоров 15t.1, …, 15t.N/2, сохраняются в параллельных регистрах 16t.1, …, 16t.N/2 разрядности (ƒ+1), соответственно,

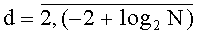

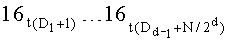

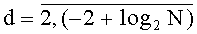

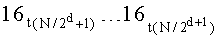

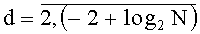

Во время поступления синхросигнала под номером (N·ТУТПП+d+2) значения частичных сумм, снимаемых с выходов сумматоров

Во время поступления синхросигнала под номером (N·ТУТПП+2+logN) значение, снимаемое с выхода сумматора 15t.(N-1), сохраняется в параллельном регистре 16t.(N-1) разрядности (ƒ+log2N) и поступает на выход 5t, который является одним из t выходов устройства для вычисления ДПП,

В результате, за (N·ТУТПП+2+logN) тактов работы устройства для вычисления ДПП возможно вычисление значений Т элементов образов для заданного подкласса дискретных полиномиальных преобразований. При этом минимальный интервал времени между поступлениями синхросигналов рассчитывается согласно формуле вида

ТУТПП=max(TMX, T(Σ))+TR,

где TMX, T(Σ) и TR - оценки максимального времени задержки мультиплексоров 9t.(k+1).p «2n в 1», двухвходового сумматора 15t.(k+1) для

При этом значения n-разрядных двоичных элементов обрабатываемых последовательностей, а также значения элементов образов заданного подкласса дискретных полиномиальных преобразований поступают на n-разрядный вход 4 и снимаются с Т(ƒ+log2N)-разрядных выходов 51, …, 5T устройства для вычисления ДПП, соответственно, по синхросигналам, поступающим через период времени не менее чем ТУТПП.

Таким образом, предлагаемое устройство для вычисления ДПП по сравнению с прототипом позволяет производить вычисление широкого класса дискретных полиномиальных преобразований, задаваемых системой полиномиальных функций вида (1), при использовании конвейерной обработки данных с сохранением промежуточных результатов, что позволяет обеспечивать высокое быстродействие предлагаемого устройства.

Источники информации

1. Крот A.M. Дискретные модели динамических систем на основе полиномиальной алгебры. Минск: Навука i тэхника, 1990. 311 с.

2. Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов: учебн. пособие для вузов. М.: Радио и связь, 1988. 312 с.

3. Блейхуд Р. Теория и практика кодов, контролирующих ошибки. Пер. с англ. под ред. Зигангирова К.Ш. М.: Мир, 1986. 576 с.

4. RU(11) 2190874(13), C2 G06F 17/14, 20.07.1999.

5. RU(11) 2290687(13), C1 G06F 17/14 (2006.01), 31.05.2005.

6. RU(11) 2399152(13), C2 H03H 17/04, H03H 17/06, H03H 21/00 (2006.01), 12.03.2008.

7. RU(11) 2421781(13), C1 G06F 7/72, H03M 7/18 (2006.01), 19.10.2009.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ЗАДАННОМУ МОДУЛЮ | 2009 |

|

RU2421781C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК И СОЧЕТАНИЙ | 2010 |

|

RU2427885C1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2010 |

|

RU2446444C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для сравнения чисел в системе остаточных классов | 2018 |

|

RU2698413C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| КОНВЕЙЕРНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2022 |

|

RU2791440C1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

Изобретение относится к области цифровой обработки сигналов и может быть использовано при обработке видео- и аудиосигналов в реальном масштабе времени. Техническим результатом является обеспечение выполнения различных подклассов дискретных полиномиальных преобразований (ДПП) и для реализации КИХ-фильтров с использованием заданной системы функций на конечном интервале длины N=2c. Устройство содержит систему из n N-разрядных регистров сдвига, Т блоков вычисления системы функций ДПП и Т блоков комбинационных сумматоров для N ƒ-разрядных двоичных чисел, где Т - количество элементов образа заданного подкласса ДПП, представленных (ƒ-1+log2N)-разрядными двоичными числами, ƒ=n+r, n - количество двоичных разрядов входа устройства, r - максимальное количество двоичных разрядов постоянных коэффициентов для заданного подкласса ДПП. 4 ил.

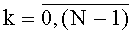

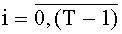

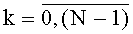

Устройство для вычисления дискретных полиномиальных преобразований, содержащее T комбинационных сумматоров для N f-разрядных двоичных чисел с одним выходом на (f+log2N) разрядов каждый, где T - количество элементов образа заданного подкласса дискретных полиномиальных преобразований (далее - ДПП), представленных (f+log2N)-разрядными двоичными числами, N=2c - длина интервала последовательности, над которой выполняется ДПП, c - целое положительное число, f=n+r, r - максимальное количество двоичных разрядов постоянных коэффициентов для заданного подкласса ДПП, n - количество двоичных разрядов входа устройства, отличающееся тем, что в него введены: система из n N-разрядных регистров сдвига с входом на n двоичных разрядов, с синхровходом и с N n-разрядными двоичными выходами, а также T блоков вычисления системы функций ДПП с N n-разрядными двоичными входами, с T входами значений разрядов функций ДПП на N·f·2n двоичных разрядов каждый, с синхровходом, с входом инициализации и с N выходами на f двоичных разрядов каждый, причем вход системы из n N-разрядных регистров сдвига является входом устройства на n двоичных разрядов, каждый из N выходов системы из n N-разрядных регистров сдвига соединен с N n-разрядными двоичными входами каждого из T блоков вычисления системы функций ДПП, при этом N f-разрядных выходов каждого из T блоков вычисления системы функций ДПП соединены с N входами соответствующего ему комбинационного сумматора для N f-разрядных двоичных чисел, (f+log2N)-разрядные выходы каждого из комбинационных сумматоров для N f-разрядных двоичных чисел являются выходами устройства для вычисления ДПП, синхровход системы из n N-разрядных регистров сдвига, синхровход каждого из T блоков вычисления системы функций ДПП и синхровход каждого из T комбинационных сумматоров для N f-разрядных двоичных чисел является синхровходом устройства для вычисления ДПП, каждый вход значений разрядов функций ДПП t-то блока вычисления системы функций ДПП соединен с t-м входом значений разрядов функций ДПП на N·f·2n двоичных разрядов устройства для вычисления ДПП,  , а вход инициализации каждого из Т блоков вычисления системы функций ДПП является входом инициализации устройства, система из n N-разрядных регистров сдвига содержит n N-разрядных регистров сдвига с последовательным входом, синхровходом и N двоичными выходами каждый, причем последовательный вход каждого N-разрядного регистра сдвига соединен с соответствующим двоичным разрядом n-разрядного входа устройства для вычисления ДПП, синхровход каждого из n N-разрядных регистров сдвига соединен с синхровходом устройства для вычисления ДПП, а i-e разряды N-разрядных регистров сдвига являются i-м выходом системы из n N-разрядных регистров сдвига на n двоичных разрядов каждый,

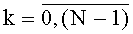

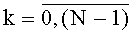

, а вход инициализации каждого из Т блоков вычисления системы функций ДПП является входом инициализации устройства, система из n N-разрядных регистров сдвига содержит n N-разрядных регистров сдвига с последовательным входом, синхровходом и N двоичными выходами каждый, причем последовательный вход каждого N-разрядного регистра сдвига соединен с соответствующим двоичным разрядом n-разрядного входа устройства для вычисления ДПП, синхровход каждого из n N-разрядных регистров сдвига соединен с синхровходом устройства для вычисления ДПП, а i-e разряды N-разрядных регистров сдвига являются i-м выходом системы из n N-разрядных регистров сдвига на n двоичных разрядов каждый,  , t-й блок вычисления системы функций ДПП,

, t-й блок вычисления системы функций ДПП,  , содержит N·f параллельных регистров значений разрядов функций разрядности 2n каждый с синхровходом, N·f мультиплексоров «2n в 1», N параллельных f-разрядных регистров с синхровходом, причем синхровход каждого из параллельных регистров значений разрядов функций соединен с входом инициализации устройства для вычисления ДПП, вход данных каждого из N·f параллельных регистров значений разрядов функций соединен с соответствующими входами значений разрядов функций ДПП на N·f·2n двоичных разрядов устройства для вычисления ДПП, а выходы данных каждого из N·f параллельных регистров значений разрядов функций соединены с входами данных соответствующих им мультиплексоров «2n в 1», управляющие входы каждого из f элементов i-й группы мультиплексоров «2n в 1» соединены с i-м входом n-разрядных двоичных чисел t-го блока вычисления системы функций ДПП, выходы данных i-й группы мультиплексоров «2n в 1» соединены с входом данных i-го параллельного f-разрядного регистра, синхровход каждого из которых соединен с синхровходом устройства для вычисления ДПП, а выход данных каждого из которых является i-м выходом f-разрядных двоичных чисел t-го блока вычисления системы функций ДПП,

, содержит N·f параллельных регистров значений разрядов функций разрядности 2n каждый с синхровходом, N·f мультиплексоров «2n в 1», N параллельных f-разрядных регистров с синхровходом, причем синхровход каждого из параллельных регистров значений разрядов функций соединен с входом инициализации устройства для вычисления ДПП, вход данных каждого из N·f параллельных регистров значений разрядов функций соединен с соответствующими входами значений разрядов функций ДПП на N·f·2n двоичных разрядов устройства для вычисления ДПП, а выходы данных каждого из N·f параллельных регистров значений разрядов функций соединены с входами данных соответствующих им мультиплексоров «2n в 1», управляющие входы каждого из f элементов i-й группы мультиплексоров «2n в 1» соединены с i-м входом n-разрядных двоичных чисел t-го блока вычисления системы функций ДПП, выходы данных i-й группы мультиплексоров «2n в 1» соединены с входом данных i-го параллельного f-разрядного регистра, синхровход каждого из которых соединен с синхровходом устройства для вычисления ДПП, а выход данных каждого из которых является i-м выходом f-разрядных двоичных чисел t-го блока вычисления системы функций ДПП,  ,

,  , t-й комбинационный сумматор для N f-разрядных двоичных чисел,

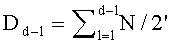

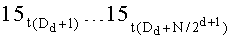

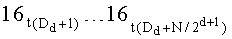

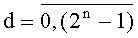

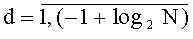

, t-й комбинационный сумматор для N f-разрядных двоичных чисел,  , содержит (N-1) двухвходовых сумматора, из которых 2u-2-j имеют разрядность (f+j),

, содержит (N-1) двухвходовых сумматора, из которых 2u-2-j имеют разрядность (f+j),  , u=1+logN, а также (N-1) параллельных регистра с синхровходом, из которых 2u-2-j имеют разрядность (f+j+1),

, u=1+logN, а также (N-1) параллельных регистра с синхровходом, из которых 2u-2-j имеют разрядность (f+j+1),  , u=1+logN, N входов на f двоичных разрядов каждый, причем каждый из N входов на f двоичных разрядов N/2 двухвходовых сумматоров соединен с N выходами t-го блока вычисления системы функций ДПП разрядности f,

, u=1+logN, N входов на f двоичных разрядов каждый, причем каждый из N входов на f двоичных разрядов N/2 двухвходовых сумматоров соединен с N выходами t-го блока вычисления системы функций ДПП разрядности f,  , выходы N/2 двухвходовых сумматоров соединены с входами N/2 (f+1)-разрядных параллельных регистров, выходы которых, в свою очередь, соединены с входами N/4 двухвходовых сумматоров, выходы которых соединены с входами N/4 (f+2)-разрядных параллельных регистров, выходы N/2d (f+d)-разрядных параллельных регистров соединены с входами N/2d+1 двухвходовых сумматоров, выходы которых соединены с входами N/2d+1 (f+d+1)-разрядных параллельных регистров,

, выходы N/2 двухвходовых сумматоров соединены с входами N/2 (f+1)-разрядных параллельных регистров, выходы которых, в свою очередь, соединены с входами N/4 двухвходовых сумматоров, выходы которых соединены с входами N/4 (f+2)-разрядных параллельных регистров, выходы N/2d (f+d)-разрядных параллельных регистров соединены с входами N/2d+1 двухвходовых сумматоров, выходы которых соединены с входами N/2d+1 (f+d+1)-разрядных параллельных регистров,  , выходы двух (f-1+log2N)-разрядных параллельных регистров соединен с входами двухвходового сумматора, выход которого соединен с входом параллельного регистра разрядности (f+log2N), выход которого является выходом t-го комбинационного сумматора для N f-разрядных двоичных чисел,

, выходы двух (f-1+log2N)-разрядных параллельных регистров соединен с входами двухвходового сумматора, выход которого соединен с входом параллельного регистра разрядности (f+log2N), выход которого является выходом t-го комбинационного сумматора для N f-разрядных двоичных чисел,  , синхровходы каждого из (N-1)-го параллельного регистра соединены с синхровходом устройства для вычисления ДПП.

, синхровходы каждого из (N-1)-го параллельного регистра соединены с синхровходом устройства для вычисления ДПП.

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ЗАДАННОМУ МОДУЛЮ | 2009 |

|

RU2421781C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ХАРТЛИ-ФУРЬЕ | 1999 |

|

RU2190874C2 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| US 6460061 B1, 01.10.2002 | |||

| US 6073154 A, 06.06.2000 | |||

| US 2007180010 A1, 02.08.2007 | |||

Авторы

Даты

2014-05-27—Публикация

2012-11-16—Подача