Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для формирования кодовых последовательностей.

Известны генераторы псевдослучайной последовательности (ПСП), например, в [1] на с.146, фиг.4.2.1 (генератор М-последовательностей), содержащий селектор двоичных импульсов, первый и второй регистры с обратными связями, формирователь синхроимпульсов и генератор тактовых импульсов.

Известен генератор псевдослучайных последовательностей, приведенный в книге [1] на с.147, фиг.4.2.3 (генератор М-последовательностей), выбранный в качестве прототипа, содержащий генератор тактовых импульсов, регистр сдвига с синхровходом, с последовательным входом и с выходом на n1 разряд, n1 умножителей и сумматор по модулю два на n1 вход.

Устройство-прототип имеет следующие функциональные связи.

Выход генератора тактовых импульсов соединен с синхровходом регистра сдвига, а n1 разряд с выхода регистра сдвига через n1 умножителей соединены с n1 входами сумматора по модулю два, выход которого соединен с последовательным входом регистр сдвига и, кроме того, является выходом устройства.

Работает устройство-прототип следующим образом. С генератора тактовых импульсов импульсы поступают на синхровход регистра сдвига. Разряды выхода регистра сдвига, сигналы поступают на выход устройства, а также через n1 умножителей поступают на соответствующие входы сумматора по модулю два, с выхода которого сигнал поступает на последовательный вход регистра сдвига, а также на выход устройства.

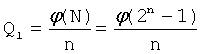

Недостатком данного устройства является небольшая сетка периодов. Например, для 10-разрядного регистра можно сформировать 60 шт. М-последовательностей. Данное обстоятельство ограничивает функциональные возможности данного генератора псевдослучайных последовательностей, что обусловлено следующей особенностью. При фиксированной разрядности сдвигового регистра устройство позволяет формировать возможное количество различающихся М-последовательностей с периодом N=2n-1 (под различающимися М-последовательностями понимаются последовательности, каждую из которых нельзя было бы представить в виде циклического сдвига любой другой), определяемое по формуле вида [2, с.33]

,

,

где φ(N) - функция Эйлера. Например, при n=13, Q1=60. Величина Q1 является сравнительно небольшой по отношению к возможному количеству 2n-1 двоичных последовательностей, различие которых определяется обратными связями n-разрядного регистра сдвига. Существенные различия объясняются применением линейных операций (сложения по модулю два) в цепи обратной связи. Эти недостатки устранены в предлагаемом устройстве.

Техническим результатом предлагаемого устройства является расширение функциональных возможностей - увеличение объема формируемых максимальных последовательностей путем подключения двух двоичных регистровых генераторов псевдослучайных последовательностей (ГПСП) с обратной связью (линейного генератора М-последовательности и нелинейного генератора с нелинейной обратной связью с максимальными взаимно простыми периодами) через функциональный цифровой преобразователь, формирующий систему классов вычетов по формуле

где хi - двоичные n2-разрядные числа, формируемые нелинейным ГПСП, yi - двоичные n1-разрядные числа, формируемые линейным генератором М-последовательности.

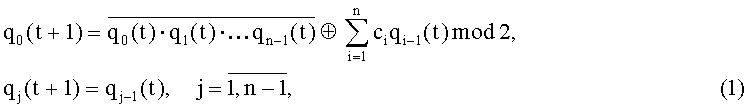

Нелинейный генератор описывается нелинейным рекуррентным уравнением вида [3, с.51-52]

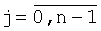

где qj(t) - двоичный символ на выходе j-го разряда регистра сдвига на t-м такте,  , ci - двоичные константы, определяющие вид обратной связи, ― - операция инверсии двоичного значения, вычисляемого схемой операции логического «И», ⊕ и

, ci - двоичные константы, определяющие вид обратной связи, ― - операция инверсии двоичного значения, вычисляемого схемой операции логического «И», ⊕ и  - операции поразрядного сложения по модулю два. Количество Q2 нелинейных последовательностей, формируемых нелинейным ГПСП при заданном n определяется по формуле [2, с.32-33]

- операции поразрядного сложения по модулю два. Количество Q2 нелинейных последовательностей, формируемых нелинейным ГПСП при заданном n определяется по формуле [2, с.32-33]

.

.

Например, при n=13, Q2=24083.

Предлагаемое устройство позволяет увеличить объем формируемых максимальных последовательностей до величины Q=Ql·Q2. При этом максимальный период получаемых последовательностей на выходе устройства равен величине 2n·(2n-1).

Технический результат в генераторе псевдослучайных последовательностей, содержащем генератор тактовых импульсов, n1 умножителей на два входа и выход каждый и сумматор по модулю два на n1 вход, достигается тем, что в него введены регистр сдвига с синхровходом, с последовательным входом, с параллельным входом на n1 разряд, входом асинхронной установки и с выходом на n1 разряд, параллельный регистр обратной связи генератора М-последовательности на n1 разряд с информационным входом, синхровходом и выходом на n1 разряд, нелинейный генератор с входом начального состояния на 2·n2 разрядов, входом инициализации, синхровходом и выходом на n2 разряда, параллельный (n1+n2)-разрядный регистр с информационным входом, синхровходом и выходом, (n1+n2) буферных элементов, каждый из которых имеет информационный вход, управляющий вход и выход, параллельный регистр коммутации с информационными входом на (n1+n2) разрядов, выходом на (n1+n2) разрядов и с синхровходом, причем синхровходы регистра сдвига, нелинейного генератора и параллельного (n1+n2)-разрядного регистра соединены с генератором тактовых импульсов, k-й разряд выхода регистра сдвига соединен с первым входом k-го умножителя соответственно, k-й разряд выхода параллельного регистра обратной связи генератора М-последовательности соединен со вторым входом k-го умножителя соответственно, выход которого соединен с k-м входом сумматора по модулю два соответственно,  , выход которого соединен с последовательным входом регистра сдвига, вход инициализации нелинейного генератора, вход асинхронной установки регистра сдвига, синхровход параллельного регистра обратной связи генератора М-последовательности и синхровход параллельного регистра коммутации соединены с входом инициализации генератора псевдослучайных последовательностей, параллельный вход регистра сдвига на n1 разряд и информационный вход параллельного регистра обратной связи генератора М-последовательности на n1 разряд соединены с первой группой разрядов входа начального состояния генератора псевдослучайных последовательностей (данная группа включает 2·n2 разрядов), вход начального состояния нелинейного генератора на 2·n2 разряда соединен с второй группой разрядов входа начального состояния генератора псевдослучайных последовательностей, информационный вход параллельного регистра коммутации на (n1+n2) разряда соединен с третьей группой разрядов входа начального состояния генератора псевдослучайных последовательностей (вход начального состояния генератора псевдослучайных последовательностей содержит 3·(n1+n2) двоичных разрядов), выходы нелинейного генератора и регистра сдвига соединены с младшими и старшими разрядами входа параллельного (n1+n2)-разрядного регистра соответственно, l-й разряд выхода параллельного (n1+n2)-разрядного регистра соединен с информационным входом l-го буферного элемента соответственно, управляющие входы которого соединены с l-м разрядом выхода параллельного регистра коммутации соответственно,

, выход которого соединен с последовательным входом регистра сдвига, вход инициализации нелинейного генератора, вход асинхронной установки регистра сдвига, синхровход параллельного регистра обратной связи генератора М-последовательности и синхровход параллельного регистра коммутации соединены с входом инициализации генератора псевдослучайных последовательностей, параллельный вход регистра сдвига на n1 разряд и информационный вход параллельного регистра обратной связи генератора М-последовательности на n1 разряд соединены с первой группой разрядов входа начального состояния генератора псевдослучайных последовательностей (данная группа включает 2·n2 разрядов), вход начального состояния нелинейного генератора на 2·n2 разряда соединен с второй группой разрядов входа начального состояния генератора псевдослучайных последовательностей, информационный вход параллельного регистра коммутации на (n1+n2) разряда соединен с третьей группой разрядов входа начального состояния генератора псевдослучайных последовательностей (вход начального состояния генератора псевдослучайных последовательностей содержит 3·(n1+n2) двоичных разрядов), выходы нелинейного генератора и регистра сдвига соединены с младшими и старшими разрядами входа параллельного (n1+n2)-разрядного регистра соответственно, l-й разряд выхода параллельного (n1+n2)-разрядного регистра соединен с информационным входом l-го буферного элемента соответственно, управляющие входы которого соединены с l-м разрядом выхода параллельного регистра коммутации соответственно,  , выходы (n1+n2) буферных элементов представляют собой разряды выхода генератора псевдослучайных последовательностей, нелинейный генератор содержит n2 мультиплексоров с двумя информационными входами, управляющим входом и выходом каждый, n2 одноразрядных регистра с информационным входом, синхровходом и выходом каждый, схему операции логического «И», имеющую n2 входов и выход с инверсией, схему операции логического «ИЛИ», имеющую два входа и выход, n2 буферных элемента с информационным входом, управляющим входом и выходом каждый, а также параллельный регистр обратной связи с n2-разрядным информационным входом, n2-разрядным выходом и с синхровходом, причем первый информационный вход первого мультиплексора соединен с выходом схемы операции логического «И», входы которой соединены с выходами n2 буферных элементов соответственно, при этом информационный вход i-го буферного элемента соединен с выходом i-го одноразрядного регистра соответственно,

, выходы (n1+n2) буферных элементов представляют собой разряды выхода генератора псевдослучайных последовательностей, нелинейный генератор содержит n2 мультиплексоров с двумя информационными входами, управляющим входом и выходом каждый, n2 одноразрядных регистра с информационным входом, синхровходом и выходом каждый, схему операции логического «И», имеющую n2 входов и выход с инверсией, схему операции логического «ИЛИ», имеющую два входа и выход, n2 буферных элемента с информационным входом, управляющим входом и выходом каждый, а также параллельный регистр обратной связи с n2-разрядным информационным входом, n2-разрядным выходом и с синхровходом, причем первый информационный вход первого мультиплексора соединен с выходом схемы операции логического «И», входы которой соединены с выходами n2 буферных элементов соответственно, при этом информационный вход i-го буферного элемента соединен с выходом i-го одноразрядного регистра соответственно,  , управляющие входы каждого из n2 мультиплексоров соединены в входом инициализации генератора псевдослучайных последовательностей, а первый информационный вход j-го мультиплексора соединен с выходом (j-1)-го одноразрядного регистра соответственно,

, управляющие входы каждого из n2 мультиплексоров соединены в входом инициализации генератора псевдослучайных последовательностей, а первый информационный вход j-го мультиплексора соединен с выходом (j-1)-го одноразрядного регистра соответственно,  , второй информационный вход i-го мультиплексора соединен с i-м разрядом первой подгруппы второй группы разрядов входа начального состояния генератора псевдослучайных последовательностей соответственно,

, второй информационный вход i-го мультиплексора соединен с i-м разрядом первой подгруппы второй группы разрядов входа начального состояния генератора псевдослучайных последовательностей соответственно,  , выход i-го мультиплексора соединен с входом i-го одноразрядного регистра соответственно,

, выход i-го мультиплексора соединен с входом i-го одноразрядного регистра соответственно,  , синхровходы каждого из n2 одноразрядных регистров соединены с выходом схемы операции логического «ИЛИ», первый вход которой соединен с входом инициализации генератора псевдослучайных последовательностей, а второй ее вход является входом подключения к генератору тактовых импульсов, соответственно, каждый управляющий вход i-го буферного элемента соединен с i-м разрядом параллельного регистра обратной связи соответственно,

, синхровходы каждого из n2 одноразрядных регистров соединены с выходом схемы операции логического «ИЛИ», первый вход которой соединен с входом инициализации генератора псевдослучайных последовательностей, а второй ее вход является входом подключения к генератору тактовых импульсов, соответственно, каждый управляющий вход i-го буферного элемента соединен с i-м разрядом параллельного регистра обратной связи соответственно,  , информационный вход которого соединен со второй подгруппой первой группы разрядов входа начального состояния генератора псевдослучайных последовательностей, а его синхровход соединен с входом инициализации генератора псевдослучайных последовательностей, каждый выход i-го одноразрядного регистра соединен с i-м разрядом выхода нелинейного генератора соответственно,

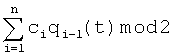

, информационный вход которого соединен со второй подгруппой первой группы разрядов входа начального состояния генератора псевдослучайных последовательностей, а его синхровход соединен с входом инициализации генератора псевдослучайных последовательностей, каждый выход i-го одноразрядного регистра соединен с i-м разрядом выхода нелинейного генератора соответственно,  , где n1 - количество двоичных разрядов чисел, снимаемых с выхода регистра сдвига, целое положительное число, n2 - количество двоичных разрядов чисел, снимаемых с выхода нелинейного генератора, целое положительное число, k, l, i, j - целые положительные числа.

, где n1 - количество двоичных разрядов чисел, снимаемых с выхода регистра сдвига, целое положительное число, n2 - количество двоичных разрядов чисел, снимаемых с выхода нелинейного генератора, целое положительное число, k, l, i, j - целые положительные числа.

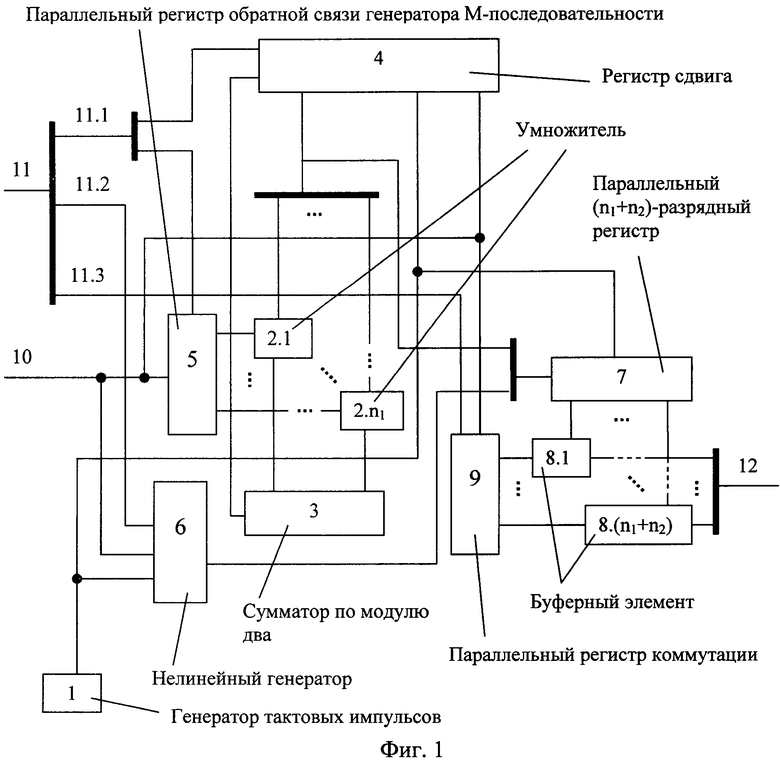

Схема генератора псевдослучайных последовательностей приведена на фиг.1, а схема блока нелинейного генератора - на фиг.2.

Генератор псевдослучайных последовательностей (фиг.1) содержит генератор 1 тактовых импульсов, умножители  , на два входа и выход каждый, сумматор 3 по модулю два на n1 вход, регистр 4 сдвига, параллельный регистр 5 обратной связи генератора М-последовательности, нелинейный генератор 6 с входом начального состояния на 2·n2 разряда, входом инициализации и синхровходом, параллельный (n1+n2)-разрядный регистр 7 с информационными входом на (n1+n2) разрядов, выходом на (n1+n2) разрядов и синхровходом, буферные элементы 8.l с информационным и управляющим входами, а также с выходом,

, на два входа и выход каждый, сумматор 3 по модулю два на n1 вход, регистр 4 сдвига, параллельный регистр 5 обратной связи генератора М-последовательности, нелинейный генератор 6 с входом начального состояния на 2·n2 разряда, входом инициализации и синхровходом, параллельный (n1+n2)-разрядный регистр 7 с информационными входом на (n1+n2) разрядов, выходом на (n1+n2) разрядов и синхровходом, буферные элементы 8.l с информационным и управляющим входами, а также с выходом,  , параллельный регистр 9 коммутации с (n1+n2)-разрядным информационным входом, с (n1+n2)-разрядным выходом, а также с синхровходом; вход 10 является входом инициализации генератора псевдослучайных последовательностей и соединен с входом асинхронной установки регистра 4 сдвига, с синхровходом параллельного регистра 5 обратной связи генератора М-последовательности, с входом инициализации нелинейного генератора 6 М-последовательности, с синхровходом параллельного (n1+n2)-разрядного регистра 7 коммутации и с управляющим входом для мультиплексоров 13.i (фиг.2),

, параллельный регистр 9 коммутации с (n1+n2)-разрядным информационным входом, с (n1+n2)-разрядным выходом, а также с синхровходом; вход 10 является входом инициализации генератора псевдослучайных последовательностей и соединен с входом асинхронной установки регистра 4 сдвига, с синхровходом параллельного регистра 5 обратной связи генератора М-последовательности, с входом инициализации нелинейного генератора 6 М-последовательности, с синхровходом параллельного (n1+n2)-разрядного регистра 7 коммутации и с управляющим входом для мультиплексоров 13.i (фиг.2),  , вход 11 является входом начального состояния генератора псевдослучайных последовательностей, при этом первая подгруппа первой группы разрядов данного входа, содержащая n1 разряд, поступает на параллельный вход регистра 4 сдвига, вторая подгруппа первой группы разрядов данного входа, содержащая n1 разряд, поступает на информационный вход параллельного регистра 5 обратной связи генератора М-последовательности, вторая группа разрядов данного входа, содержащая 2·n2 разряда, является входом начального состояния нелинейного генератора 6, а третья группа разрядов данного входа, содержащая (n1+n2) разрядов, является информационным входом параллельного регистра 9 коммутации, выход 12 является (n1+n2)-разрядным выходом генератора псевдослучайных последовательностей. Причем группа из n2 разрядов, соединенная с выходом нелинейного генератора 6, является группой младших разрядов, а группа из n1 разрядов, соединенная с выходом регистра 4 сдвига, является группой старших разрядов, при этом данные две группы разрядов соединены с информационным входом параллельного (n1+n2)-разрядного регистра 7, i-й разряд с выхода которого поступает на информационный вход буферного элемента 8.i соответственно,

, вход 11 является входом начального состояния генератора псевдослучайных последовательностей, при этом первая подгруппа первой группы разрядов данного входа, содержащая n1 разряд, поступает на параллельный вход регистра 4 сдвига, вторая подгруппа первой группы разрядов данного входа, содержащая n1 разряд, поступает на информационный вход параллельного регистра 5 обратной связи генератора М-последовательности, вторая группа разрядов данного входа, содержащая 2·n2 разряда, является входом начального состояния нелинейного генератора 6, а третья группа разрядов данного входа, содержащая (n1+n2) разрядов, является информационным входом параллельного регистра 9 коммутации, выход 12 является (n1+n2)-разрядным выходом генератора псевдослучайных последовательностей. Причем группа из n2 разрядов, соединенная с выходом нелинейного генератора 6, является группой младших разрядов, а группа из n1 разрядов, соединенная с выходом регистра 4 сдвига, является группой старших разрядов, при этом данные две группы разрядов соединены с информационным входом параллельного (n1+n2)-разрядного регистра 7, i-й разряд с выхода которого поступает на информационный вход буферного элемента 8.i соответственно,  i-й разряд с выхода параллельного регистра 9 коммутации поступает на управляющий вход буферного элемента 8.i соответственно,

i-й разряд с выхода параллельного регистра 9 коммутации поступает на управляющий вход буферного элемента 8.i соответственно,  , разряды, снимаемые с выходов буферных элементов 8.i,

, разряды, снимаемые с выходов буферных элементов 8.i,  , являются разрядами выхода 12 генератора псевдослучайных последовательностей.

, являются разрядами выхода 12 генератора псевдослучайных последовательностей.

На фиг.2 представлен нелинейный генератор 6, который включает n2 мультиплексоров  с двумя информационными входами, управляющим входом и выходом каждый, n2 одноразрядных регистра 14.i,

с двумя информационными входами, управляющим входом и выходом каждый, n2 одноразрядных регистра 14.i,  , с информационным входом, синхровходом и выходом, схему 15 операции логического «И» на n2 входов и один выход с инверсией, схему 16 операции логического «ИЛИ» на два входа и один выход, n2 буферных элемента 17.i,

, с информационным входом, синхровходом и выходом, схему 15 операции логического «И» на n2 входов и один выход с инверсией, схему 16 операции логического «ИЛИ» на два входа и один выход, n2 буферных элемента 17.i,  , с информационным входом, управляющим входом и с выходом каждый, параллельный регистр 18 обратной связи, с n2-разрядными входом, с n2-разрядными выходом, а также с синхровходом; нелинейный генератор 1 имеет выход 20 на n2 разряда, причем первый информационный вход мультиплексора 13.1 соединен с выходом схемы 15 операции логического «И», входы которой соединены с выходами буферных элементов 17.i,

, с информационным входом, управляющим входом и с выходом каждый, параллельный регистр 18 обратной связи, с n2-разрядными входом, с n2-разрядными выходом, а также с синхровходом; нелинейный генератор 1 имеет выход 20 на n2 разряда, причем первый информационный вход мультиплексора 13.1 соединен с выходом схемы 15 операции логического «И», входы которой соединены с выходами буферных элементов 17.i,  , при этом информационный вход каждого буферного элемента 17.i соединен с выходом одноразрядного регистра 14.i соответственно,

, при этом информационный вход каждого буферного элемента 17.i соединен с выходом одноразрядного регистра 14.i соответственно,  , а управляющий вход каждого буферного элемента 17.i - с i-ми разрядами параллельного регистра 18 обратной связи соответственно,

, а управляющий вход каждого буферного элемента 17.i - с i-ми разрядами параллельного регистра 18 обратной связи соответственно,  . Управляющие входы каждого из n2 мультиплексоров 13.i,

. Управляющие входы каждого из n2 мультиплексоров 13.i,  , соединены с входом 10 инициализации генератора псевдослучайных последовательностей, а первый вход мультиплексора 13.j соединен с выходом одноразрядного регистра 14. (j-1),

, соединены с входом 10 инициализации генератора псевдослучайных последовательностей, а первый вход мультиплексора 13.j соединен с выходом одноразрядного регистра 14. (j-1),  , соответственно. Второй вход каждого мультиплексора 13.i соединен с i-м разрядом первой подгруппы второй группы 11.2. разрядов входа 11 начального состояния генератора псевдослучайных последовательностей соответственно,

, соответственно. Второй вход каждого мультиплексора 13.i соединен с i-м разрядом первой подгруппы второй группы 11.2. разрядов входа 11 начального состояния генератора псевдослучайных последовательностей соответственно,  . Информационный вход параллельного регистра 18 обратной связи соединен со второй подгруппой второй группы 11.2. разрядов входа 11 начального состояния генератора псевдослучайных последовательностей, а синхровход параллельного регистра 18 обратной связи - с входом 10 инициализации генератора псевдослучайных последовательностей. Выход каждого мультиплексора 13.i соединен с входом информационным входом одноразрядного регистра 14.i соответственно,

. Информационный вход параллельного регистра 18 обратной связи соединен со второй подгруппой второй группы 11.2. разрядов входа 11 начального состояния генератора псевдослучайных последовательностей, а синхровход параллельного регистра 18 обратной связи - с входом 10 инициализации генератора псевдослучайных последовательностей. Выход каждого мультиплексора 13.i соединен с входом информационным входом одноразрядного регистра 14.i соответственно,  . Синхровходы одноразрядных регистров 14.i,

. Синхровходы одноразрядных регистров 14.i,  , соединены с выходом схемы 16 операции логического «ИЛИ», первый вход которой соединен с входом 10 инициализации генератора псевдослучайных последовательностей, а второй ее вход является входом 19 подключения к генератору тактовых импульсов, соответственно. Выход каждого одноразрядного регистра 14.i соединен с i-м разрядом выхода 20 нелинейного генератора 6 соответственно,

, соединены с выходом схемы 16 операции логического «ИЛИ», первый вход которой соединен с входом 10 инициализации генератора псевдослучайных последовательностей, а второй ее вход является входом 19 подключения к генератору тактовых импульсов, соответственно. Выход каждого одноразрядного регистра 14.i соединен с i-м разрядом выхода 20 нелинейного генератора 6 соответственно,  .

.

Все блоки, приведенные на фиг.1 и фиг.2, имеют стандартную и опубликованную в литературе реализацию, а также имеют входы электропитания, которые не изображены на фиг.1 и фиг.2.

Рассмотрим генератор псевдослучайных последовательностей в работе. В предлагаемом генераторе вычисление элементов псевдослучайных последовательностей производится на основе двух генераторов псевдослучайных последовательностей, один из которых, генератор М-последовательности, является линейным, а другой - нелинейным. По сравнению с прототипом ([1] на с.147, фиг.4.2.3), в устройство введены регистр 4 сдвига с синхровходом, с последовательным входом, с параллельным входом на n1 разряд, входом асинхронной установки и с выходом на n1 разряд, параллельный регистр 5 обратной связи генератора М-последовательности на n1 разряд с информационным входом, синхровходом и выходом на n1 разряд, нелинейный генератор 6 с входом начального состояния на 2·n2 разрядов, входом инициализации, синхровходом и выходом на n2 разряда, параллельный (n1+n2)-разрядный регистр 7 с информационным входом, синхровходом и выходом, (n1+n2) буферных элементов 8.1, ..., 8.(n1+n2), каждый из которых имеет информационный вход, управляющий вход и выход, параллельный регистр 9 коммутации с информационными входом на (n1+n2) разрядов, выходом на (n1+n2) разрядов и с синхровходом.

Сущность изобретения в том, что предлагаемый генератор реализует процедуру последовательного вычисления элементов псевдослучайных последовательностей согласно формуле

где хi - элементы периодической последовательности с периодом m1, образующие полную систему наименьших неотрицательных вычетов по модулю m1 [4, с.86], yi - элементы периодической последовательности с периодом, равным m2, где m1 и m2 - натуральные числа, m1>2, m2>2. При фиксированном хi при использовании элементов yi по формуле (2) формируется класс вычетов мощностью m2. При условии, что m1 и m2 - взаимно простые, последовательность, образованная согласно (2), имеет период, равный произведению m1·m2.

При этом блок нелинейного генератора позволяет получить периодическую последовательность согласно формуле вида (1).

Технический результат выражен в увеличении объема формируемых максимальных последовательностей путем применения нелинейного генератора, объединенного с генератором М-последовательности через функциональный цифровой преобразователь на основе параллельного регистра.

Значения элементов псевдослучайных периодических последовательностей, n1- и n2-разрядные числа хi и yi соответственно, формируемые по синхросигналу, подаваемому с генератора 1 тактовых импульсов на синхровход регистра 4 сдвига и синхровход нелинейного генератора 6, поступают с выходов регистра 4 сдвига (старшие разряды, yi) и нелинейного генератора 6 (младшие разряды, хi) на вход параллельного (n1+n2)-разрядного регистра 7. По синхросигналу, поступающему с генератора 1 тактовых импульсов, значения xi и уi заносятся в параллельный (n1+n2)-разрядный регистр 7. При этом каждый i-й разряд, снимаемый с выхода регистра 7, поступает на информационный вход буферного элемента 8.i соответственно,  , буферный элемент 8.i коммутируется путем подачи на его управляющий вход i-го разряда параллельного регистра 9 коммутации соответственно,

, буферный элемент 8.i коммутируется путем подачи на его управляющий вход i-го разряда параллельного регистра 9 коммутации соответственно,

выход буферного элемента 8.i является i-м разрядом выхода 12 генератора псевдослучайных последовательностей соответственно,  .

.

При подаче напряжения питания происходит инициализация генератора псевдослучайных последовательностей.

На этапе инициализации на вход асинхронной установки регистра 4 сдвига, на синхровход параллельного регистра 5 обратной связи генератора М-последовательности, на вход инициализации нелинейного генератора 6 и на синхровход параллельного регистра 9 коммутации с входа 10 инициализации генератора псевдослучайных последовательностей поступает сигнал (значение логической «1»), согласно которому в регистр сдвига заносится информация, поступающая с первой подгруппы первой группы разрядов входа 11 начального состояния генератора псевдослучайных последовательностей, в параллельный регистр 5 обратной связи генератора М-последовательности - информация со второй подгруппы первой группы разрядов входа 11, в нелинейный генератор 6 - информация со второй группы разрядов входа 11, а в параллельный регистр 9 коммутации - информация с третьей группы разрядов входа 11. На управляющий вход каждого мультиплексора 13.i поступает значение логической «1» с входа 10, тем самым обеспечивая прохождение на выход каждого мультиплексора 13.i значения, поступающего на его второй вход с i-го разряда первой подгруппы второй группы 11.2 разрядов входа 11 соответственно,  . Значение логической «1» с входа 10 поступает также на один из входов схемы 16 операции логического «ИЛИ», а затем через схему 16 поступает на синхровходы каждого из одноразрядных регистров 14.i соответственно,

. Значение логической «1» с входа 10 поступает также на один из входов схемы 16 операции логического «ИЛИ», а затем через схему 16 поступает на синхровходы каждого из одноразрядных регистров 14.i соответственно,  , тем самым обеспечивая сохранение значений с выхода каждого мультиплексора 13.i в одноразрядном регистре 14.i соответственно,

, тем самым обеспечивая сохранение значений с выхода каждого мультиплексора 13.i в одноразрядном регистре 14.i соответственно,  . Генерирование псевдослучайной последовательности нелинейным ГПСП с заданными свойствами согласно (1) осуществляется путем приведения соответствующих буферных элементов 15.i в открытое либо закрытое состояние в соответствии со значениями величин сi - двоичных констант, определяющих вид обратной связи и поступающими на управляющий вход соответствующего буферного элемента 15.i с i-го разряда параллельного регистра 18 обратной связи,

. Генерирование псевдослучайной последовательности нелинейным ГПСП с заданными свойствами согласно (1) осуществляется путем приведения соответствующих буферных элементов 15.i в открытое либо закрытое состояние в соответствии со значениями величин сi - двоичных констант, определяющих вид обратной связи и поступающими на управляющий вход соответствующего буферного элемента 15.i с i-го разряда параллельного регистра 18 обратной связи,  .

.

На этапе функционирования с генератора 1 тактовых импульсов поступает синхросигнал на синхровход регистра 4 сдвига, на синхровход нелинейного генератора 6 и на синхровход параллельного (n1+n2)-разрядного регистра 7. В данной связи, в регистре 4 сдвига производится логический сдвиг двоичных значений его разрядов, а значение, формируемое на его последовательном входе при использовании сумматора 3 по модулю два, заносится в младший разряд регистра 4 сдвига, в нелинейном генераторе 6 (фиг.2) синхросигнал с генератора 1 тактовых импульсов поступает через схему 16 операции логического «ИЛИ» на синхровходы каждого из одноразрядных регистров 14.i,  , а также в параллельный (n1+n2)-разрядный регистр 7 заносятся значения хi (младшие разряды) и yi (старшие разряды), снимаемые с выходов нелинейного генератора 6 и регистра 4 сдвига, соответственно. В соответствии с информацией, записанной в i-й разряд параллельного регистра 9 коммутации, который соединен с управляющим входом буферного элемента 8.i, значение с выхода i-го разряда регистра 7 поступает на информационный вход буферного элемента 8.i, а затем проходит (или не проходит) с выхода буферного элемента 8.i как i-й разряд выхода 12 генератора псевдослучайных последовательностей,

, а также в параллельный (n1+n2)-разрядный регистр 7 заносятся значения хi (младшие разряды) и yi (старшие разряды), снимаемые с выходов нелинейного генератора 6 и регистра 4 сдвига, соответственно. В соответствии с информацией, записанной в i-й разряд параллельного регистра 9 коммутации, который соединен с управляющим входом буферного элемента 8.i, значение с выхода i-го разряда регистра 7 поступает на информационный вход буферного элемента 8.i, а затем проходит (или не проходит) с выхода буферного элемента 8.i как i-й разряд выхода 12 генератора псевдослучайных последовательностей,  . На управляющий вход мультиплексора 13.i поступает значение логического «0» с входа 10, тем самым обеспечивая прохождение сигналов с первого информационного входа мультиплексора 13.i,

. На управляющий вход мультиплексора 13.i поступает значение логического «0» с входа 10, тем самым обеспечивая прохождение сигналов с первого информационного входа мультиплексора 13.i,  , на его выход. Значение с выхода мультиплексора 13.i поступает на вход одноразрядного регистра 14.i,

, на его выход. Значение с выхода мультиплексора 13.i поступает на вход одноразрядного регистра 14.i,  , и заносится в него по синхросигналу, поступающему с генератора 1 тактовых импульсов (через вход подключения 19 к генератору 1) на вход схемы 16, а затем с выхода схемы 16 на синхровходы каждого из одноразрядных регистров 14.i,

, и заносится в него по синхросигналу, поступающему с генератора 1 тактовых импульсов (через вход подключения 19 к генератору 1) на вход схемы 16, а затем с выхода схемы 16 на синхровходы каждого из одноразрядных регистров 14.i,  . Значения с выхода каждого одноразрядного регистра 14.i поступают на информационные входы буферных элементов 17.i соответственно,

. Значения с выхода каждого одноразрядного регистра 14.i поступают на информационные входы буферных элементов 17.i соответственно,  . В случае, если в i-м разряде параллельного регистра 18 обратной связи записана логическая «1», то она будет подана на управляющий вход буферного элемента 17.i и значение, поступившее на информационный вход буферного элемента 17.i, поступает на i-й вход схемы 15,

. В случае, если в i-м разряде параллельного регистра 18 обратной связи записана логическая «1», то она будет подана на управляющий вход буферного элемента 17.i и значение, поступившее на информационный вход буферного элемента 17.i, поступает на i-й вход схемы 15,  , а в случае, когда в i-м разряде регистра 18 записан логический «0», то на i-й вход схемы 15 поступает логический «0»,

, а в случае, когда в i-м разряде регистра 18 записан логический «0», то на i-й вход схемы 15 поступает логический «0»,  , тем самым обеспечивая запрет на прохождение информации, поступившей на информационный вход буферного элемента 17.i. Значение, снимаемое с выхода схемы 15, поступает на первый информационный вход мультиплексора 13.1, а на первый информационный вход каждого мультиплексора 13.i поступает значение, снимаемое с выхода одноразрядного регистра 14.(i-l) соответственно,

, тем самым обеспечивая запрет на прохождение информации, поступившей на информационный вход буферного элемента 17.i. Значение, снимаемое с выхода схемы 15, поступает на первый информационный вход мультиплексора 13.1, а на первый информационный вход каждого мультиплексора 13.i поступает значение, снимаемое с выхода одноразрядного регистра 14.(i-l) соответственно,  На i-й разряд выхода 20 нелинейного генератора поступают значения, снимаемые с выхода одноразрядного регистра 14.i соответственно,

На i-й разряд выхода 20 нелинейного генератора поступают значения, снимаемые с выхода одноразрядного регистра 14.i соответственно,  , вычисляемые согласно (1).

, вычисляемые согласно (1).

Источники информации

1. Шумоподобные сигналы в системах передачи информации/В.Б.Пестряков, В.П.Афанасьев, В.Л.Гурвич и др. М.: Сов. радио, 1973. 424 с.

2. Свердлик М.Б. Оптимальные системы и сигналы. М.: Сов. радио, 1975. 200 с.

3. Иванов М.А., Чугунков И.В. Теория применения и оценка качества генераторов псевдослучайных последовательностей. М.: «КУДИЦ-ОБРАЗ». 2003. 240 с.

4. Бухштаб А.А. Теория чисел. М.: Просвещение, 1966. 384 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР НЕЛИНЕЙНЫХ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2014 |

|

RU2549524C1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО | 2013 |

|

RU2536393C1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для формирования кодовых последовательностей. Техническим результатом является увеличение объема формируемых максимальных последовательностей. Устройство содержит генератор тактовых импульсов, n1 умножителей, сумматор по модулю два на n1 вход, регистр сдвига с синхровходом, с последовательным входом, с параллельным входом на n1 разряд, входом асинхронной установки и с выходом на n1 разряд, параллельный регистр обратной связи генератора М-последовательности на n1 разряд, нелинейный генератор с входом начального состояния на 2·n2 разрядов и выходом на n2 разряда, параллельный (n1+n2)-разрядный регистр, (n1+n2) буферных элементов, параллельный регистр коммутации с информационными входом на (n1+n2) разрядов и выходом на (n1+n2) разрядов, где n1 - количество двоичных разрядов чисел, снимаемых с выхода регистра сдвига, n2 - количество двоичных разрядов чисел, снимаемых с выхода нелинейного генератора. 2 ил.

Генератор псевдослучайных последовательностей, содержащий генератор тактовых импульсов, n1 умножителей на два входа и выход каждый и сумматор по модулю два на n1 вход, отличающийся тем, что в него введены регистр сдвига с синхровходом, с последовательным входом, с параллельным входом на n1 разряд, входом асинхронной установки и с выходом на n1 разряд, параллельный регистр обратной связи генератора М-последовательности на n1 разряд с информационным входом, синхровходом и выходом на n1 разряд, нелинейный генератор с входом начального состояния на 2·n2 разрядов, входом инициализации, синхровходом и выходом на n2 разряда, параллельный (n1+n2)-разрядный регистр с информационным входом, синхровходом и выходом, (n1+n2) буферных элементов, каждый из которых имеет информационный вход, управляющий вход и выход, параллельный регистр коммутации с информационными входом на (n1+n2) разрядов, выходом на (n1+n2) разрядов и с синхровходом, причем синхровходы регистра сдвига, нелинейного генератора и параллельного (n1+n2)-разрядного регистра соединены с генератором тактовых импульсов, k-й разряд выхода регистра сдвига соединен с первым входом k-то умножителя соответственно, k-й разряд выхода параллельного регистра обратной связи генератора М-последовательности соединен с вторым входом k-го умножителя соответственно, выход которого соединен с k-м входом сумматора по модулю два соответственно,  , выход которого соединен с последовательным входом регистра сдвига, вход инициализации нелинейного генератора, вход асинхронной установки регистра сдвига, синхровход параллельного регистра обратной связи генератора М-последовательности и синхровход параллельного регистра коммутации соединены с входом инициализации генератора псевдослучайных последовательностей, параллельный вход регистра сдвига на n1 разряд и информационный вход параллельного регистра обратной связи генератора М-последовательности на n1 разряд соединены с первой группой разрядов входа начального состояния генератора псевдослучайных последовательностей (данная группа включает 2·n2 разрядов), вход начального состояния нелинейного генератора на 2·n2 разряда соединен с второй группой разрядов входа начального состояния генератора псевдослучайных последовательностей, информационный вход параллельного регистра коммутации на (n1+n2) разряда соединен с третьей группой разрядов входа начального состояния генератора псевдослучайных последовательностей (вход начального состояния генератора псевдослучайных последовательностей содержит 3·(n1+n2) двоичных разрядов), выходы нелинейного генератора и регистра сдвига соединены с младшими и старшими разрядами входа параллельного (n1+n2)-разрядного регистра соответственно, 1-й разряд выхода параллельного (n1+n2)-разрядного регистра соединен с информационным входом 1-го буферного элемента соответственно, управляющие входы которого соединены с 1-м разрядом выхода параллельного регистра коммутации соответственно,

, выход которого соединен с последовательным входом регистра сдвига, вход инициализации нелинейного генератора, вход асинхронной установки регистра сдвига, синхровход параллельного регистра обратной связи генератора М-последовательности и синхровход параллельного регистра коммутации соединены с входом инициализации генератора псевдослучайных последовательностей, параллельный вход регистра сдвига на n1 разряд и информационный вход параллельного регистра обратной связи генератора М-последовательности на n1 разряд соединены с первой группой разрядов входа начального состояния генератора псевдослучайных последовательностей (данная группа включает 2·n2 разрядов), вход начального состояния нелинейного генератора на 2·n2 разряда соединен с второй группой разрядов входа начального состояния генератора псевдослучайных последовательностей, информационный вход параллельного регистра коммутации на (n1+n2) разряда соединен с третьей группой разрядов входа начального состояния генератора псевдослучайных последовательностей (вход начального состояния генератора псевдослучайных последовательностей содержит 3·(n1+n2) двоичных разрядов), выходы нелинейного генератора и регистра сдвига соединены с младшими и старшими разрядами входа параллельного (n1+n2)-разрядного регистра соответственно, 1-й разряд выхода параллельного (n1+n2)-разрядного регистра соединен с информационным входом 1-го буферного элемента соответственно, управляющие входы которого соединены с 1-м разрядом выхода параллельного регистра коммутации соответственно,  , выходы (n1+n2) буферных элементов представляют собой разряды выхода генератора псевдослучайных последовательностей, нелинейный генератор содержит n2 мультиплексоров с двумя информационными входами, управляющим входом и выходом каждый, n2 одноразрядных регистра с информационным входом, синхровходом и выходом каждый, схему операции логического «И», имеющую n2 входов и выход с инверсией, схему операции логического «ИЛИ», имеющую два входа и выход, n2 буферных элемента с информационным входом, управляющим входом и выходом каждый, а также параллельный регистр обратной связи с n2-разрядным информационным входом, n2-разрядным выходом и с синхровходом, причем первый информационный вход первого мультиплексора соединен с выходом схемы операции логического «И», входы которой соединены с выходами n2 буферных элементов соответственно, при этом информационный вход i-го буферного элемента соединен с выходом i-го одноразрядного регистра соответственно,

, выходы (n1+n2) буферных элементов представляют собой разряды выхода генератора псевдослучайных последовательностей, нелинейный генератор содержит n2 мультиплексоров с двумя информационными входами, управляющим входом и выходом каждый, n2 одноразрядных регистра с информационным входом, синхровходом и выходом каждый, схему операции логического «И», имеющую n2 входов и выход с инверсией, схему операции логического «ИЛИ», имеющую два входа и выход, n2 буферных элемента с информационным входом, управляющим входом и выходом каждый, а также параллельный регистр обратной связи с n2-разрядным информационным входом, n2-разрядным выходом и с синхровходом, причем первый информационный вход первого мультиплексора соединен с выходом схемы операции логического «И», входы которой соединены с выходами n2 буферных элементов соответственно, при этом информационный вход i-го буферного элемента соединен с выходом i-го одноразрядного регистра соответственно,  , управляющие входы каждого из n2 мультиплексоров соединены в входом инициализации генератора псевдослучайных последовательностей, а первый информационный вход j-го мультиплексора соединен с выходом (j-1)-го одноразрядного регистра соответственно,

, управляющие входы каждого из n2 мультиплексоров соединены в входом инициализации генератора псевдослучайных последовательностей, а первый информационный вход j-го мультиплексора соединен с выходом (j-1)-го одноразрядного регистра соответственно,  , второй информационный вход i-го мультиплексора соединен с i-м разрядом первой подгруппы второй группы разрядов входа начального состояния генератора псевдослучайных последовательностей соответственно,

, второй информационный вход i-го мультиплексора соединен с i-м разрядом первой подгруппы второй группы разрядов входа начального состояния генератора псевдослучайных последовательностей соответственно,  , выход i-го мультиплексора соединен с входом i-го одноразрядного регистра соответственно,

, выход i-го мультиплексора соединен с входом i-го одноразрядного регистра соответственно,  , синхровходы каждого из n2 одноразрядных регистров соединены с выходом схемы операции логического «ИЛИ», первый вход которой соединен с входом инициализации генератора псевдослучайных последовательностей, а второй ее вход является входом подключения к генератору тактовых импульсов соответственно, каждый управляющий вход i-го буферного элемента соединен с i-м разрядом параллельного регистра обратной связи соответственно,

, синхровходы каждого из n2 одноразрядных регистров соединены с выходом схемы операции логического «ИЛИ», первый вход которой соединен с входом инициализации генератора псевдослучайных последовательностей, а второй ее вход является входом подключения к генератору тактовых импульсов соответственно, каждый управляющий вход i-го буферного элемента соединен с i-м разрядом параллельного регистра обратной связи соответственно,  , информационный вход которого соединен с второй подгруппой первой группы разрядов входа начального состояния генератора псевдослучайных последовательностей, а его синхровход соединен с входом инициализации генератора псевдослучайных последовательностей, каждый выход i-го одноразрядного регистра соединен с i-м разрядом выхода нелинейного генератора соответственно,

, информационный вход которого соединен с второй подгруппой первой группы разрядов входа начального состояния генератора псевдослучайных последовательностей, а его синхровход соединен с входом инициализации генератора псевдослучайных последовательностей, каждый выход i-го одноразрядного регистра соединен с i-м разрядом выхода нелинейного генератора соответственно,  , где

, где

n1 - количество двоичных разрядов чисел, снимаемых с выхода регистра сдвига, целое положительное число,

n2 - количество двоичных разрядов чисел, снимаемых с выхода нелинейного генератора, целое положительное число,

k, 1, i, j - целые положительные числа.

| ПЕСТРЯКОВ В.Б | |||

| и др | |||

| Шумоподобные сигналы в системах передачи информации | |||

| - М.: Советское радио, 1973, с.147, рис.4.2.3 | |||

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2002 |

|

RU2223593C1 |

| ГЕНЕРАТОР N-ЗНАЧНОЙ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1994 |

|

RU2081450C1 |

| Устройство для погружения и извлечения ряда свай вдавливанием | 1979 |

|

SU887728A1 |

| US 2005097153 A1, 05.05.2005. | |||

Авторы

Даты

2012-03-27—Публикация

2010-11-12—Подача