Устройство для измерения частоты сетевого напряжения при несинусоидальных помехах относится к измерительной технике и может быть использовано для определения частоты питающего напряжения в условиях значительных несинусоидальных помех.

Известен способ с определением частоты электрической сети при несинусоидальных помехах [1] с применением итерационной процедуры измерения частоты сети, состоящей из операции предварительного подавления в сигнале высших гармоник той частоты, которая была измерена ранее, и очередного измерения частоты.

Недостатком измерителя является последовательное подавление несинусоидальных помех, что ведет к увеличению времени измерения, необходимого для получения более точного результата.

Наиболее близким техническим решением к предлагаемому является цифровой измеритель частоты [2], содержащий входное устройство, кварцевый генератор, формирующее устройство, делитель частоты, управляющее устройство, временной селектор, счетчик, дешифратор.

Недостатком измерителя является значительное время усреднения (счета), необходимое для получения требуемой точности измерений и низкая помехоустойчивость.

Предлагаемое изобретение направлено на повышение точности измерения при несинусоидальных помехах и на уменьшение времени измерения.

Это достигается тем, что в устройство для измерения частоты, содержащее входное устройство, кварцевый генератор, формирующее устройство, делитель частоты, управляющее устройство, временной селектор, счетчик, дешифратор, при этом выход формирующего устройства соединен с одним входом временного селектора, второй вход которого соединен с выходом управляющего устройства, выходы которого также соединены с входами счетчика импульсов, делителя частоты, дешифратора, вход управляющего устройства соединен с выходом делителя частоты, вход которого, через формирующее устройство, соединен с выходом кварцевого генератора опорной частоты, выход временного селектора соединен со входом счетчика импульсов, выход которого соединен со входом дешифратора, согласно предлагаемому изобретению после входного устройства дополнительно введены два интегратора, две линии задержки и два сумматора, при этом, выход входного устройства соединен с входом интегратора, выход которого в свою очередь соединен с входом сумматора и входом линии задержки , выход линии задержки соединен со входом сумматора, выход сумматора соединен со входом интегратора, выход которого в свою очередь соединен с входом сумматора и входом линии задержки, выход линии задержки соединен с входом сумматора, выход линии задержки соединен со входом формирующего устройства.

Введение новых элементов и связей между ними обеспечивает решение поставленной задачи.

На фиг. 1 представлена блок-схема предлагаемого устройства.

Устройство (фиг.1) содержит:

1 - входное устройство;

2 - первый интегратор;

3 - первая линия задержки;

4 - первый сумматор;

5 - второй интегратор;

6 - вторая линию задержки;

7 - второй сумматор;

8 - первое формирующее устройство;

9 - кварцевый генератор опорной частоты;

10 - второе формирующее устройство;

11 - временной селектор;

12 - делитель частоты;

13 - управляющее устройство;

14 - счетчик импульсов;

15 - дешифратор.

При этом, выход входного устройства 1 соединен с входом первого интегратора 2, выход которого в свою очередь соединен с входами первого сумматора 4 и первой линии задержки 3, выход первой линии задержки 3 соединен со входом первого сумматора 4, выход первого сумматора 4 соединен со входом второго интегратора 5, выход которого в свою очередь соединен с входами второго сумматора 7 и второй линии задержки 6, выход второй линии задержки 6 соединен с входом второго сумматора 7, выход второго сумматора 7 соединен со входом первого формирующего устройства 8, выход которого соединен с одним входом временного селектора 11, второй вход которого соединен с выходом управляющего устройства 13, выходы которого также соединены с входами счетчика импульсов 14, делителя частоты 12, дешифратора 15, вход управляющего устройства 13 соединен с выходом делителя частоты 12, вход которого, через второе формирующее устройство 10, соединен с выходом кварцевого генератора опорной частоты 9, выход временного селектора соединен со входом счетчика импульсов 14, выход которого соединен со входом дешифратора 15.

Работает предлагаемое устройство следующим образом.

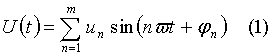

На вход входного устройства 1 сигнал сетевого напряжения с несинусоидальной помехой, описываемый выражением:

На входном устройстве сетевое напряжение в общем случае преобразуется к уровню, необходимому для нормальной работы формирующего устройства 8.

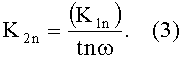

Сигнал с входного устройства 1 поступает на интегратор 2, где производится первая операция интегрирования. После этого производится задержка интегрированного сигнала на время td1 на линии задержки 3 и суммирование его с сигналом, получаемым на выходе интегратора 2, на сумматоре 4. При этом, у n-й гармоники ряда (1) появится амплитудный коэффициент:

где n - номер гармоники, ω = 2πf - угловая частота основной гармоники.

После этого сигнал, с выхода сумматора 4 поступает на интегратор 5, на котором производится вторая операция интегрирования. Далее на линии задержки 6 производится задержка интегрированного сигнала на время td2 и суммирование его с сигналом, получаемым на выходе интегратора 5, на сумматоре 7. При этом, у n-й гармоники ряда (1) появится амплитудный коэффициент:

Таким образом, из (3) и (2) следует, что амплитуда высших гармоник в выходном сигнале с сумматора 7 снижается пропорционально 3-ей степени номера гармоники. При этом, за счет операции сложения сигнала с выхода

линии задержки 6 с сигналом с выхода интегратора 5 удается избавиться от постоянной составляющей сигнала.

Следует отметить, что выбор времени td1 и td2 может быть произвольным в интервале равном от 0 до Т/2 основной гармоники.

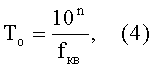

Далее сигнал поступает на формирующее устройство 8, где преобразуется в последовательность импульсов. На временной селектор 11 поступает сигнал Т0 с устройства управления 13. Сигнал Т0 формируется под действием сигнала кварцевого генератора 9 и его длительность будет определяться, как:

где fкв - частота кварцевого генератора, (5 или 10 МГц), 10n - ступени делителя частоты.

За время Т0 временной селектор 11 пропустит на счетчик импульсов 14 n отсчетов измеряемого сигнала. Таким образом, частота входного сигнала может быть получена по следующей формуле:

Пример.

С выхода формирующего устройства 1 на вход интегратора поступает сигнал u(t)=10sin(ωt)+5sin(9ωt)+5sin(15ωt), представленный на фиг.2а, с частотой первой гармоники 50 Гц. Как видно из фиг.2а, высшие гармоники будут вносить значительные трудности в определение частоты первой гармоники.

После двойной интегральной обработки на выходе сумматора 7 будет сформирован сигнал U(t), представленный на фиг.2б. На фиг.2б видно, что влияние высших гармоник на форму сигнала уменьшено в значительной степени, по сравнению с входным сигналом u(t).

Предлагаемое устройство позволяет снизить влияние высших гармоник на точность измерения частоты, при этом может быть уменьшено время необходимое для измерения частоты до одного периода первой гармоники.

Источники информации

1. Патент RU 2107302, МПК G01R, 23/02. Способ определения частоты электрической сети / Ю.Я. Лямец, А.П. Арсентьев, А.А. Салимон (РФ). - 1998.

2. Алешечкин А.М., Кокорин В.И. «Методы измерения частотно-временных параметров сигналов», - Уч.пособие. - Красноярск: ИПЦ КГТУ. - 2001. - 96с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения комплексного коэффициента передачи четырехполюсника СВЧ | 1988 |

|

SU1596275A1 |

| Калибратор сигналов, нормированных по коэффициенту гармоник | 1988 |

|

SU1555677A1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ГАРМОНИЧЕСКОГО СИГНАЛА | 2008 |

|

RU2368909C1 |

| Устройство для измерения симметричных составляющих напряжений трехфазной сети | 1990 |

|

SU1781642A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| МАЛОГАБАРИТНЫЙ РАДИОЛОКАТОР ТРАНСПОРТНОГО СРЕДСТВА | 1997 |

|

RU2117964C1 |

Изобретение относится к измерительной технике. Устройство содержит входное устройство, кварцевый генератор, формирующее устройство, делитель частоты, управляющее устройство, временной селектор, счетчик, дешифратор. При этом выход первого формирующего устройства соединен с одним входом временного селектора, второй вход которого соединен с выходом управляющего устройства, выходы которого также соединены с входами счетчика импульсов, делителя частоты, дешифратора, вход управляющего устройства соединен с выходом делителя частоты, вход которого, через второе формирующее устройство, соединен с выходом кварцевого генератора опорной частоты, выход временного селектора соединен со входом счетчика импульсов, выход которого соединен со входом дешифратора. Дополнительно устройство содержит после входного устройства два интегратора, две линии задержки и два сумматора. При этом выход входного устройства соединен с входом первого интегратора, выход которого в свою очередь соединен с входом первого сумматора и входом первой линии задержки, выход первой линии задержки соединен со входом первого сумматора, выход первого сумматора соединен со входом второго интегратора, выход которого в свою очередь соединен с входом второго сумматора и входом второй линии задержки, выход второй линии задержки соединен с входом второго сумматора, выход второго сумматора соединен со входом первого формирующего устройства. Технический результат заключается в повышении точности измерения. 2 ил.

Устройство для измерения частоты, содержащее входное устройство, кварцевый генератор, формирующее устройство, делитель частоты, управляющее устройство, временной селектор, счетчик, дешифратор, при этом выход первого формирующего устройства соединен с одним входом временного селектора, второй вход которого соединен с выходом управляющего устройства, выходы которого также соединены с входами счетчика импульсов, делителя частоты, дешифратора, вход управляющего устройства соединен с выходом делителя частоты, вход которого, через второе формирующее устройство, соединен с выходом кварцевого генератора опорной частоты, выход временного селектора соединен со входом счетчика импульсов, выход которого соединен со входом дешифратора, отличающееся тем, что дополнительно после входного устройства введены два интегратора, две линии задержки и два сумматора, при этом выход входного устройства соединен с входом первого интегратора, выход которого в свою очередь соединен с входом первого сумматора и входом первой линии задержки, выход первой линии задержки соединен со входом первого сумматора, выход первого сумматора соединен со входом второго интегратора, выход которого в свою очередь соединен с входом второго сумматора и входом второй линии задержки, выход второй линии задержки соединен с входом второго сумматора, выход второго сумматора соединен со входом первого формирующего устройства.

| Алешечкин A.M., Кокорин В.И | |||

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ЧАСТОТЫ ЭЛЕКТРИЧЕСКОЙ СЕТИ | 1993 |

|

RU2107302C1 |

| ЧАСТОТОМЕР ДЛЯ ПРОМЫШЛЕННЫХ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ | 2006 |

|

RU2326390C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ЧАСТОТЫ ЭЛЕКТРИЧЕСКОЙ СЕТИ | 1995 |

|

RU2110804C1 |

| RU 95100250 A1 27.11.1996 | |||

Авторы

Даты

2014-05-27—Публикация

2012-12-24—Подача