Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны двоичные сумматоры (см., например, рис.6.966 на стр.525 в книге Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для втузов. - СПб.: Политехника, 1996 г.), которые выполняют сложение одноразрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных двоичных сумматоров, относятся неоднородный аппаратурный состав, образованный логическими элементами трех типов, и ограниченные функциональные возможности, обусловленные тем, что не выполняется сложение четырехразрядных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип двоичный сумматор (рис.6.97 на стр.525 в книге Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для втузов. - СПб.: Политехника, 1996 г.), который содержит логические элементы и формирует двоичный код s4s3s2s1s0 суммы S двух четырехразрядных двоичных чисел X=x3x2x1x0, Y=y3y2y1y0, задаваемых двоичными сигналами х0,…,х3, y0,…,у3 ∈ {0,1} так, что х0, y0 и х3, y3 есть младшие и старшие разряды соответственно.

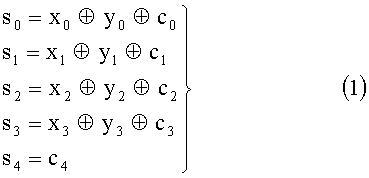

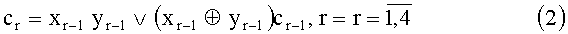

При этом

где c0=0;

Здесь символами ⊕, ·, ∨ обозначены операции ИСКЛЮЧАЮЩЕЕ ИЛИ, И, ИЛИ.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся неоднородный аппаратурный состав и низкое быстродействие, обусловленные соответственно тем, что прототип содержит логические элементы трех типов (элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И, элементы ИЛИ) и максимальное время задержки распространения сигнала в нем равно 9τЛЭ, где τЛЭ есть время задержки логического элемента.

Техническим результатом изобретения является увеличение быстродействия и повышение однородности аппаратурного состава при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в двоичном сумматоре, содержащем восемь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и восемь элементов И, у которых первый и второй входы i-го

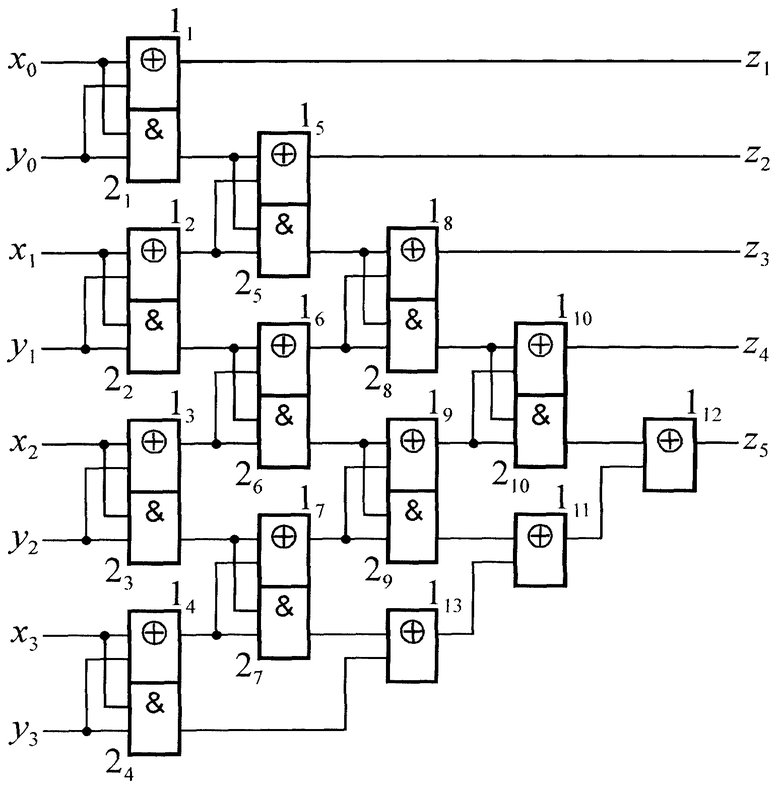

На чертеже представлена схема предлагаемого двоичного сумматора.

Двоичный сумматор содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11,…,113 и элементы И 21,…,210, причем первый и второй входы элемента 2i

Работа предлагаемого двоичного сумматора осуществляется следующим образом. На его первый,…,четвертый и пятый,…,восьмой входы подаются соответственно двоичные сигналы х0,…,х3 ∈ {0,1} и y0,…,y3 ∈ {0,1}. Тогда сигналы на выходах предлагаемого сумматора будут определяться выражениями

z1=x0⊕y0;

z2=x1⊕y1⊕x0y0;

z3=x2⊕y2⊕x1y1⊕(x1⊕y1)x0y0;

z4=x3⊕y3⊕x2y2⊕(x2⊕y2)x1y1⊕(x2⊕y2⊕x1y1)((x1⊕y1)x0y0)=

=x3⊕y3⊕x2y2⊕x1x2y1⊕x1y1y2⊕x0x1x2y0⊕

⊕x0x1y0y2⊕x0x2y0y1⊕x0y0y1y2;

z5=x3y3⊕(x3⊕y3)x2y2⊕(x3⊕y3⊕x2y2)((x2⊕y2)x1y1)⊕

⊕(x3⊕y3⊕x2y2⊕(x2⊕y2)x1y1)((x2⊕y2⊕x1y1)((x1⊕y1)x0y0))=

=x3y3⊕x2x3y2⊕x2y2y3⊕x1x2x3y1⊕x1x2y1y3⊕x1x3y1y2⊕

⊕x1y1y2y3⊕x0x1x2x3y0⊕x0x1x3y0y2⊕x0x2x3y0y1⊕

⊕x0x1y0y2y3⊕x0x2y0y1y3⊕x0x3y0y1y2⊕x0y0y1y2y3.

Рассмотрим таблицу

в которой значения cr вычислены согласно (2). Из анализа таблицы следует, что cr=xr-1yr-1⊕(xr-1⊕yr-1)c-1. Подставляя последнее равенство в выражения (1), получим

s0=x0⊕y0⊕0=x0⊕y0;

s1=x1⊕y1⊕c1=x1⊕y1⊕x0y0;

s2=x2⊕y2⊕c2=x2⊕y2⊕x1y1⊕(x1⊕y1)x0y0;

s3=x3⊕y3⊕c3=x3⊕y3⊕x2y2⊕(x2⊕y2)(x1y1⊕(x1⊕y1)x0y0)=

=x3⊕y3⊕x2y2⊕x1x2y1⊕x1y1y2⊕x0x1x2y0⊕

⊕x0x1y0y2⊕x0x2y0y1⊕x0y0y1y2;

s4=c4=x3y3⊕(x3⊕y3)(x2y2⊕(x2⊕y2)(x1y1⊕(x1⊕y1)x0y0))=

=x3y3⊕x2x3y2⊕x2y2y3⊕x1x2x3y1⊕x1x2y1y3⊕x1x3y1y2⊕

⊕x1y1y2y3⊕x0x1x2x3y0⊕x0x1x2y0y3⊕x0x1x3y0y2⊕x0x2x3y0y1⊕

⊕x0x1y0y2y3⊕x0x2y0y1y3⊕x0x3y0y1y2⊕x0y0y1y2y3.

Сравнив полученные соотношения с выражениями для z1,…,z5, имеем z1=s0, z2=s1, z3=s2, z4=s3, z5=s4. Таким образом, на выходах предлагаемого сумматора получим пятиразрядное двоичное число S=s4s3s2s1s0=X+Y, где Х=х3х2х1х0, Y=y3y2y1y0 - четырехразрядные двоичные числа, задаваемые входными двоичными сигналами х0,…,х3, y0,…,y3 так, что х0, y0 и х3, y3 есть младшие и старшие разряды соответственно.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый двоичный сумматор формирует двоичный код суммы двух четырехразрядных двоичных чисел, задаваемых двоичными сигналами, и имеет более однородный по сравнению с прототипом аппаратурный состав и более высокое быстродействие, поскольку содержит логические элементы двух типов (элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И) и максимальное время задержки распространения сигнала в нем равно 5 тτЛЭ, где τЛЭ есть время задержки логического элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2018931C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2012038C1 |

| СПУТНИКОВЫЙ РЕТРАНСЛЯТОР "АКСАЙ" | 1994 |

|

RU2097926C1 |

| СПОСОБ ИНТЕРФЕРЕНЦИОННОГО КОНТРОЛЯ КАЧЕСТВА ТЕЛЕСКОПИЧЕСКИХ ОПТИЧЕСКИХ СИСТЕМ | 1992 |

|

RU2031387C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2028660C1 |

| СУММАТОР ПО МОДУЛЮ СЕМЬ | 1992 |

|

RU2018924C1 |

| АДРЕСНЫЙ ИДЕНТИФИКАТОР | 2012 |

|

RU2491626C1 |

| СБОЕУСТОЙЧИВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2610264C1 |

| СУММАТОР ПО МОДУЛЮ q | 2018 |

|

RU2702970C1 |

| СПОСОБ АНАЛИЗА ВОЛНОВЫХ ФРОНТОВ СВЕТОВОГО ПОЛЯ | 1991 |

|

RU2031397C1 |

Изобретение предназначено для сложения двух четырехразрядных двоичных чисел, задаваемых двоичными сигналами и может быть использовано в системах цифровой вычислительной техники как средство арифметической обработки дискретной информации. Техническим результатом является повышение однородности аппаратурного состава и увеличение быстродействия. Устройство содержит тринадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (11,…,113) и десять элементов И (21,…,210). 1 ил., 1 табл.

Двоичный сумматор, содержащий восемь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и восемь элементов И, у которых первый и второй входы i-го

| ПУХАЛЬСКИЙ Г.И | |||

| и др | |||

| ЦИФРОВЫЕ УСТРОЙСТВА, САНКТ-ПЕТЕРБУРГ, ПОЛИТЕХНИКА, 1996, с | |||

| Телескоп | 1920 |

|

SU525A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СУММАТОР ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260836C1 |

| Комбинационный сумматор | 1988 |

|

SU1589269A1 |

| Четырехвходовый одноразрядный сумматор | 1988 |

|

SU1575172A1 |

| US 6711604 B1, 23.03.2004 | |||

| KR 20040091849 A, 02.11.2004 | |||

| JP 09282144 A, 31.10.1997 | |||

Авторы

Даты

2014-11-20—Публикация

2013-07-09—Подача