Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны сумматоры единичных сигналов (см., например, рис.1.36в на стр.58 в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. М.: Радио и связь, 1988), которые формируют младший разряд двоичного кода числа единичных сигналов входного кортежа (х1,..., х8), где хi∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных сумматоров единичных сигналов, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка кортежа (х1,..., xn) и не формируются остальные разряды двоичного кода числа единичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип сумматор единичных сигналов (см. рис.1.34б на стр.56 в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. М.: Радио и связь, 1988.), который содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И и формирует двоичный код числа единичных сигналов входного кортежа (х1, х2), где хi∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится ограниченные функциональные возможности, обусловленные тем, что не допускается обработка кортежа (x1,..., хn).

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения формирования двоичного кода числа единичных сигналов входного кортежа (х1,..., хn), хi∈{0,1}.

Указанный технический результат при осуществлении изобретения достигается тем, что в сумматоре единичных сигналов, содержащем вычислительную ячейку, которая содержит элемент И, подключенный первым, вторым входами и выходом соответственно к первому, второму входам и первому выходу вычислительной ячейки, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенный первым, вторым входами и выходом соответственно к первому, второму входам и второму выходу вычислительной ячейки, особенность заключается в том, что в него введены n элементов И, n D-триггеров и n-1 аналогичных упомянутой вычислительных ячеек, причем второй вход и выход i-го ( ) элемента И соединены соответственно с i-ым информационным входом сумматора единичных сигналов и первым входом i-ой вычислительной ячейки, подключенной первым выходом к входу данных i-го D-триггера, вход установки, тактовый вход и неинвертирующий выход которого соединены соответственно с первым, вторым управляющими входами сумматора единичных сигналов и первым входом i-го элемента И, второй выход каждой предыдущей вычислительной ячейки подключен к второму входу последующей вычислительной ячейки, а второй вход первой и второй выход n-ой вычислительных ячеек соединены соответственно с шиной нулевого потенциала и выходом сумматора единичных сигналов.

) элемента И соединены соответственно с i-ым информационным входом сумматора единичных сигналов и первым входом i-ой вычислительной ячейки, подключенной первым выходом к входу данных i-го D-триггера, вход установки, тактовый вход и неинвертирующий выход которого соединены соответственно с первым, вторым управляющими входами сумматора единичных сигналов и первым входом i-го элемента И, второй выход каждой предыдущей вычислительной ячейки подключен к второму входу последующей вычислительной ячейки, а второй вход первой и второй выход n-ой вычислительных ячеек соединены соответственно с шиной нулевого потенциала и выходом сумматора единичных сигналов.

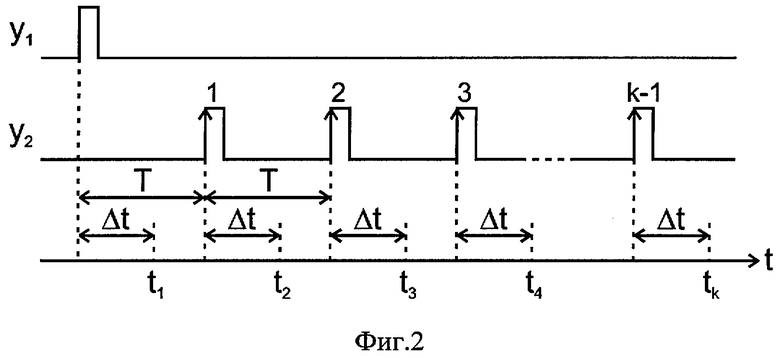

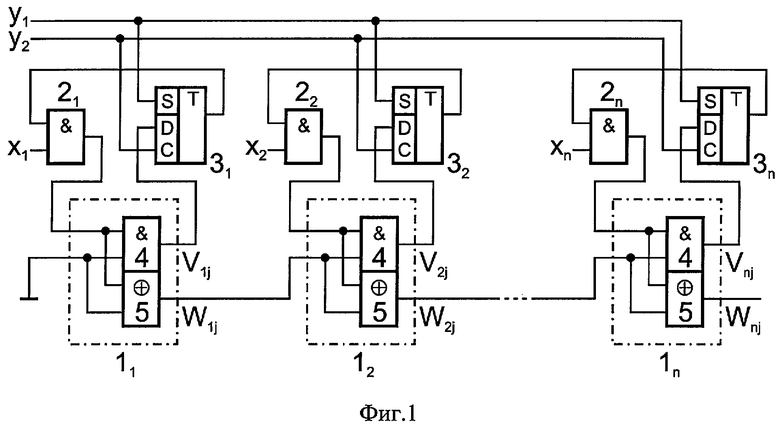

На фиг.1 и 2 представлены соответственно схема предлагаемого сумматора единичных сигналов и временные диаграммы сигналов настройки.

Сумматор единичных сигналов содержит вычислительные ячейки 11,..., 1n, элементы И 21,..., 2n, D-триггеры 31,..., 3n. Каждая вычислительная ячейка содержит элемент И 4, подключенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, подключенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу. Причем второй вход и выход элемента 2i( ) соединены соответственно с i-ым информационным входом сумматора единичных сигналов и первым входом ячейки 1i подключенной первым выходом к входу данных D-триггера 3i вход установки, тактовый вход и неинвертирующий выход которого соединены соответственно с первым, вторым управляющими входами сумматора единичных сигналов и первым входом элемента 2 второй выход каждой предыдущей ячейки подключен к второму входу последующей ячейки, а второй вход ячейки 11 и второй выход ячейки 1n соединены соответственно с шиной нулевого потенциала и выходом сумматора единичных сигналов.

) соединены соответственно с i-ым информационным входом сумматора единичных сигналов и первым входом ячейки 1i подключенной первым выходом к входу данных D-триггера 3i вход установки, тактовый вход и неинвертирующий выход которого соединены соответственно с первым, вторым управляющими входами сумматора единичных сигналов и первым входом элемента 2 второй выход каждой предыдущей ячейки подключен к второму входу последующей ячейки, а второй вход ячейки 11 и второй выход ячейки 1n соединены соответственно с шиной нулевого потенциала и выходом сумматора единичных сигналов.

Работа предлагаемого сумматора единичных сигналов осуществляется следующим образом.

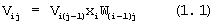

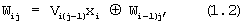

На его первый,...,n-ый информационные и первый, второй управляющие входы подаются соответственно двоичные сигналы x1,..., xn∈{0,1} и импульсные сигналы y1, y2∈{0,1} (фиг.2). Тогда сигналы на первом и втором выходах вычислительной ячейки 1i( ) будут определяться соответственно рекуррентными выражениями

) будут определяться соответственно рекуррентными выражениями

и

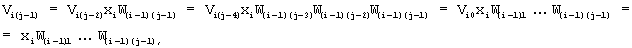

где  есть номер момента времени tj (фиг.2), k - разрядность двоичного кода числа n; Vi0=1; W0j=0. Период Т сигнала у2 должен удовлетворять условию Т>Δt, где Δt=nΔt1+Δt2+Δt3, а Δt1, Δt2 и Δt3 есть длительности задержек, вносимых соответственно ячейкой 1i элементом 2i и D-триггером 3i. Поскольку согласно (1.1) имеем

есть номер момента времени tj (фиг.2), k - разрядность двоичного кода числа n; Vi0=1; W0j=0. Период Т сигнала у2 должен удовлетворять условию Т>Δt, где Δt=nΔt1+Δt2+Δt3, а Δt1, Δt2 и Δt3 есть длительности задержек, вносимых соответственно ячейкой 1i элементом 2i и D-триггером 3i. Поскольку согласно (1.1) имеем

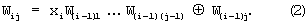

то с учетом (1.2) получим

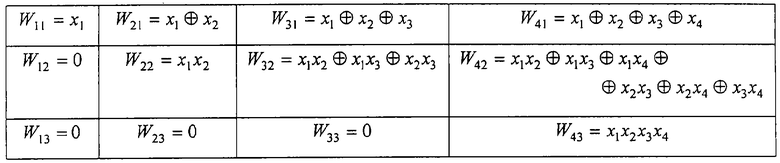

В представленной ниже таблице приведены значения выражения (2) при n=4.

Таким образом, предлагаемый сумматор единичных сигналов на своем выходе реализует операцию

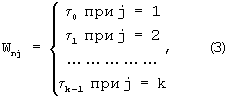

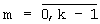

где τk-1...τ1τ0 есть k-разрядный двоичный код числа единичных сигналов в кортеже (x1,..., xn). Согласно (3) и фиг.2 настройка сумматора (фиг.1) на вычисление разряда τm( ) осуществляется соответствующим количеством m импульсов сигнала у2.

) осуществляется соответствующим количеством m импульсов сигнала у2.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый сумматор единичных сигналов обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает формирование двоичного кода числа единичных сигналов входного кортежа (x1,..., xn).

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2284655C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2277260C1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2003 |

|

RU2257608C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2256211C1 |

| Способ управления реакцией нейропроцессора на входные сигналы | 2018 |

|

RU2724784C2 |

| РЕЛЯТОРНЫЙ КОММУТАТОР АНАЛОГОВЫХ СИГНАЛОВ С АДРЕСНЫМ УПРАВЛЕНИЕМ | 2004 |

|

RU2256220C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2330322C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2335797C1 |

| Способ хранения и считывания аналоговых значений функций многих переменных | 2017 |

|

RU2656704C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения формирования двоичного кода числа единичных сигналов кортежа (x1,..., xn), хj∈{0,1}. Устройство содержит n вычислительных ячеек, каждая из которых состоит из элемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, n элементов И, n D-триггеров. 2 ил.

Сумматор единичных сигналов, содержащий вычислительную ячейку, которая содержит элемент "И", подключенный первым, вторым входами и выходом соответственно к первому, второму входам и первому выходу вычислительной ячейки, и элемент "исключающее ИЛИ", подключенный первым, вторым входами и выходом соответственно к первому, второму входам и второму выходу вычислительной ячейки, отличающийся тем, что в него введены n элементов "И", n D-триггеров и n-1 аналогичных упомянутой вычислительных ячеек, причем второй вход и выход i-го ( ) элемента "И" соединены соответственно с i-м информационным входом сумматора единичных сигналов и первым входом i-й вычислительной ячейки, подключенной первым выходом к входу данных i-го D-триггера, вход установки, тактовый вход и неинвертирующий выход которого соединены соответственно с первым, вторым управляющими входами сумматора единичных сигналов и первым входом i-го элемента "И", второй выход каждой предыдущей вычислительной ячейки подключен к второму входу последующей вычислительной ячейки, а второй вход первой и второй выход n-й вычислительных ячеек соединены соответственно с шиной нулевого потенциала и выходом сумматора единичных сигналов.

) элемента "И" соединены соответственно с i-м информационным входом сумматора единичных сигналов и первым входом i-й вычислительной ячейки, подключенной первым выходом к входу данных i-го D-триггера, вход установки, тактовый вход и неинвертирующий выход которого соединены соответственно с первым, вторым управляющими входами сумматора единичных сигналов и первым входом i-го элемента "И", второй выход каждой предыдущей вычислительной ячейки подключен к второму входу последующей вычислительной ячейки, а второй вход первой и второй выход n-й вычислительных ячеек соединены соответственно с шиной нулевого потенциала и выходом сумматора единичных сигналов.

| ШИЛО В.Л | |||

| Популярные цифровые микросхемы | |||

| Справочник, М.: | |||

| Радио и связь, 1988, с.56, рис.1.34б | |||

| СУММАТОР КОДОВ "1 ИЗ N" | 1997 |

|

RU2129730C1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1837280A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1797111A1 |

| Устройство для параллельного счета количества единиц (нулей) в двоичном числе | 1979 |

|

SU781811A2 |

| DE 3716551 А, 23.02.19. | |||

Авторы

Даты

2005-09-20—Публикация

2004-03-30—Подача