Изобретение относится к области обработки информации в радиотехнических системах и предназначено для определения времени задержки между двумя псевдослучайными последовательностями с известным знаком задержки.

Известно корреляционное устройство, служащее для определения времени задержки, содержащее два регистра сдвига, блок сравнения (группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и элемент И), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два триггера, два счетчика, одновибратор, четыре элемента И и элемент ИЛИ, причем информационный вход первого регистра сдвига является первым информационным входом дискриминатора, вторым информационным входом которого является первый вход первого элемента ИЛИ, тактовым входом дискриминатора служит тактовый вход второго регистра сдвига, разрядные выходы первого и второго регистров сдвига соединены соответственно с первыми и вторыми входами блока сравнения, выход которого соединен с входом одновибратора, выход которого соединен с обнуляющими входами регистров сдвига, первого счетчика и первого триггера, второй вход первого элемента И соединен с прямым выходом второго триггера и первым входом второго элемента И, второй вход которого соединен с тактовым входом второго регистра сдвига, а выход второго элемента И соединен с тактовым входом первого регистра сдвига и со счетным входом первого счетчика, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с информационным входом второго регистра сдвига, второй вход элемента ИЛИ соединен с выходом третьего элемента И, первый вход которого соединен с инверсным выходом второго триггера, установочный вход которого соединен с обнуляющим входом второго счетчика и является управляющим входом дискриминатора, счетный вход второго счетчика соединен с выходом четвертого элемента И, первый вход которого соединен с прямым выходом первого триггера, второй вход четвертого элемента И соединен с тактовым входом дискриминатора, выход переполнения первого счетчика соединен с обнуляющим входом второго триггера и установочным входом первого триггера, второй вход третьего элемента И соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого соединены с соответствующими выходами второго регистра сдвига, разрядные выходы второго счетчика являются выходом дискриминатора [А.с. СССР №1413643. Опубл. в БИ №28, 1988 г.].

Недостатком устройства является относительная сложность реализации и низкое быстродействие.

Наиболее близким по технической сущности является корреляционное устройство, выбранное в качестве прототипа и содержащее двухканальный одноразрядный мультиплексор, два регистра сдвига, блок сравнения, два триггера, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И, информационный вход первого регистра сдвига является первым информационным входом дискриминатора, тактовым входом которого служит тактовый вход второго регистра сдвига, разрядные выходы первого и второго регистров сдвига соединены соответственно с первыми и вторыми входами блока сравнения, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами второго регистра сдвига согласно правилу формирования псевдослучайной последовательности, тактовый вход первого регистра сдвига соединен с выходом первого элемента И, первый вход которого объединен с первым входом второго элемента И и подключен к тактовому входу дискриминатора, управляющим входом которого является установочный вход первого триггера, к управляющему входу дискриминатора подключен обнуляющий вход счетчика, суммирующий вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом второго триггера, разрядные выходы счетчика являются выходами дискриминатора, выход мультиплексора соединен с информационным входом второго регистра сдвига, первый информационный вход мультиплексора является вторым информационным входом дискриминатора, второй информационный вход мультиплексора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, адресный вход мультиплексора соединен с выходом второго триггера, D-вход которого соединен с выходом первого триггера, обнуляющий вход которого соединен с выходом блока сравнения, тактовый вход второго триггера соединен с тактовым входом дискриминатора, а инвертирующий выход второго триггера соединен со вторым входом первого элемента И [Пат. РФ №2246133. Опубл. в БИ №4, 2005 г.].

Недостатком прототипа является низкое быстродействие.

Технический результат, достигаемый при использовании настоящего изобретения, состоит в повышении быстродействия определения времени задержки.

Технический результат достигается тем, что в корреляционное устройство, содержащее два регистра сдвига, блок сравнения, два триггера, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, информационный вход первого регистра сдвига является первым информационным входом устройства, разрядные выходы первого и второго регистров сдвига соединены соответственно с первыми и вторыми входами блока сравнения, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами второго регистра сдвига согласно правилу формирования псевдослучайной последовательности, управляющим входом устройства является установочный вход первого триггера, выход которого соединен с D-входом второго триггера, синхровход которого подключен к синхровходу устройства, к управляющему входу устройства подключен обнуляющий вход счетчика, суммирующий вход которого соединен с выходом элемента И, первый вход которого соединен с выходом второго триггера, разрядные выходы счетчика являются выходами устройства, согласно изобретению, введен генератор тактовых импульсов и двухканальный трехразрядный мультиплексор, первый вход первого разряда которого объединен с первым входом второго разряда и подключен к синхровходу устройства, первый вход третьего разряда мультиплексора является вторым информационным входом устройства, второй вход первого разряда мультиплексора является входом логического нуля, второй вход второго разряда мультиплексора соединен с выходом генератора тактовых импульсов, второй вход третьего разряда мультиплексора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, адресный вход мультиплексора подключен к выходу второго триггера, второй вход элемента И соединен с выходом генератора тактовых импульсов, выход первого разряда мультиплексора соединен с тактовым входом первого регистра, выход второго разряда мультиплексора соединен с тактовым входом второго регистра, информационный вход которого соединен с выходом третьего разряда мультиплексора.

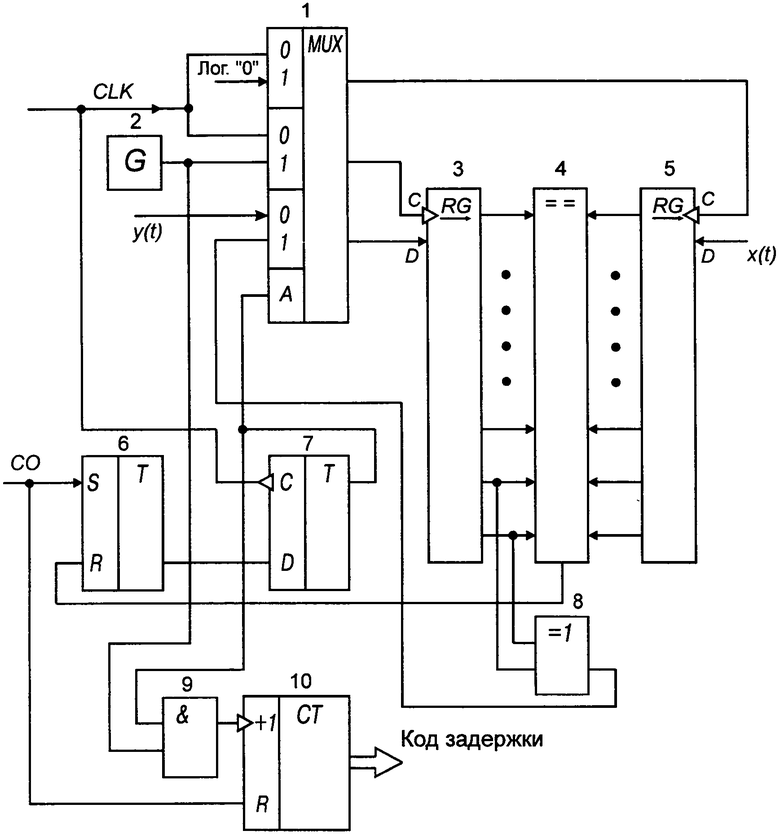

Сущность изобретения поясняется чертежом. На фигуре показана функциональная схема корреляционного устройства.

Функциональная схема содержит двухканальный трехразрядный мультиплексор 1, генератор 2 тактовых импульсов, регистры 3, 5 сдвига, блок 4 сравнения (компаратор двоичных чисел), триггеры 6, 7, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, элемент И 9 и счетчик 10. Информационный вход регистра 5 является первым информационным входом x(t) устройства, разрядные выходы регистров 3, 5 соединены соответственно с первыми и вторыми входами блока 4 сравнения, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 соединены с выходами регистра 3 согласно правилу формирования псевдослучайной последовательности, управляющим входом CO устройства является установочный вход триггера 6, выход которого соединен с D-входом триггера 7, синхровход которого подключен к синхровходу CLK устройства, к управляющему входу СО устройства подключен обнуляющий вход счетчика 10, суммирующий вход которого соединен с выходом элемента И 9, первый вход которого соединен с выходом триггера 7, разрядные выходы счетчика 10 являются выходами устройства, первый вход первого разряда мультиплексора 1 объединен с первым входом второго разряда и подключен к синхровходу CLK устройства, первый вход третьего разряда мультиплексора 1 является вторым информационным входом y(t) устройства, второй вход первого разряда мультиплексора 1 является входом логического нуля, второй вход второго разряда мультиплексора 1 соединен с выходом генератора 2 тактовых импульсов, второй вход третьего разряда мультиплексора 1 соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, адресный вход мультиплексора 1 подключен к выходу триггера 7, второй вход элемента И 9 соединен с выходом генератора 2 тактовых импульсов, выход первого разряда мультиплексора 1 соединен с тактовым входом регистра 5, выход второго разряда мультиплексора 1 соединен с тактовым входом регистра 3, информационный вход которого соединен с выходом третьего разряда мультиплексора 1.

Работает корреляционное устройство следующим образом.

На информационные входы x(t) и y(t) поступают соответственно опережающая и запаздывающая псевдослучайные последовательности с относительной задержкой τ. В исходном состоянии, до подачи на вход СО запускающего импульса, на адресном входе мультиплексора 1 присутствует низкий логический уровень, в результате чего на выходы мультиплексора коммутируются первые каналы разрядов (на схеме имеют обозначение «0»). При этом регистры 3, 5 непрерывно тактируются импульсами, поступающими с синхровхода CLK, и поступающие на их информационные входы символы псевдослучайных последовательностей непрерывно и последовательно заносятся в их ячейки. Таким образом, в любой тактовый момент на разрядных выходах регистров 3, 5 будут представлены сегменты псевдослучайных последовательностей, поступающие на входы x(t), y(t) устройства. Для начала измерений задержки τ на вход СО подают запускающий импульс, в ответ на что триггер 6 переходит в состояние высокого логического уровня, на D-входе триггера 7 также устанавливается высокий логический уровень и по отрицательному фронту тактового импульса со входа CLK триггер 7 меняет свое состояние. Переход триггера 7 в состояние высокого логического уровня приводит к переключению мультиплексора 1, в результате чего на его выходы коммутируются вторые каналы разрядов (на схеме имеют обозначение «1»). Это приводит к остановке тактирования регистра 5, и в результате в нем запоминается один из сегментов опережающей псевдослучайной последовательности, который далее будет выполнять роль опорного. Кроме того, переключение мультиплексора 1 приводит к коммутации на информационный вход регистра 3 выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, а тактирование регистра 3 начинает осуществляться от генератора 2. Регистр 3, охваченный обратной связью, следует рассматривать как генератор псевдослучайной последовательности. Организованный на время измерений генератор начинает потактно формировать сегменты псевдослучайной последовательности в соответствии с правилом, определенным для исследуемых псевдослучайных последовательностей. Исходным сегментом при этом является последний записанный в регистр 3 фрагмент. Через некоторое время на выходах регистра 3 сформируется сегмент, идентичный опорному, хранящемуся в регистре 5.

Искомое время τ* отсчитывается счетчиком 10 по количеству тактовых импульсов, необходимых для формирования сегмента псевдослучайной последовательности, идентичного опорному. При полном побитном равенстве сегментов, подаваемых на входы блока 4 сравнения, на выходе указанного блока сформируется перепад напряжений, приводящий к обнулению триггера 6. Далее по отрицательному фронту первого после обнуления триггера 6 тактового импульса триггер 7 также устанавливает на своем выходе низкий логический уровень, и подача тактовых импульсов на суммирующий вход счетчика 10 прекращается, а на его разрядных выходах фиксируется код задержки nτ. По известному периоду следования тактовых импульсов Т0, которые вырабатывает генератор 2, вычисляют время τ*=T0nτ.

По сравнению с прототипом время, затрачиваемое на нахождение значения τ*, определяется не частотой смены символов псевдослучайной последовательности, а частотой генератора 2 тактовых импульсов, который на время измерений используется для тактирования синтезированного генератора псевдослучайных последовательностей на основе регистра 3. Таким образом, отсутствие привязки к синхроимпульсам, сопровождающим псевдослучайные последовательности, и возможность произвольного выбора периода Т0 позволяют увеличить быстродействие устройства за счет увеличения частоты тактирования регистра 3, находящегося в режиме формирования псевдослучайной последовательности.

С подачей следующего запускающего импульса СО счетчик 10 обнуляется и цикл измерений повторяется.

Особенностью дискриминатора, также как и прототипа, является необходимость априорного знания правила формирования исследуемых псевдослучайных последовательностей, задаваемого для k-разрядных регистров 3, 5 характеристическим многочленом k-й степени

Ф(х)=a 0xk+a 1xk-1+…+a k-1x+a k,

где а 0, …, ak - коэффициенты многочлена, принимающие значения 0 или 1.

Значения коэффициентов многочлена определяют точки подключения обратных связей к разрядам регистра 3, также как и требуемое количество входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 [Аванесян Г.Р., Селезнев А.С. Генератор идентичных последовательностей, сдвинутых во времени. - Приборы и техника эксперимента, 1989, №1, стр.104-106]. Поэтому в общем случае элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8 может иметь не два входа, как показано на фигуре, а больше в зависимости от вида характеристического многочлена (количество входов равно количеству коэффициентов а, равных единице).

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ДИСКРИМИНАТОР ВРЕМЕНИ ЗАДЕРЖКИ | 2003 |

|

RU2246133C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2011 |

|

RU2445690C2 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для обмена информацией | 1985 |

|

SU1312586A1 |

| Устройство для контроля цифровых устройств | 1988 |

|

SU1509901A1 |

| Генератор псевдослучайных чисел | 1989 |

|

SU1691839A2 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

Изобретение относится к корреляционному устройству. Технический результат заключается в повышении быстродействия определения времени задержки. Корреляционное устройство содержит два регистра сдвига, блок сравнения, два триггера, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, генератор тактовых импульсов и двухканальный трехразрядный мультиплексор. 1 ил.

Корреляционное устройство, содержащий два регистра сдвига, блок сравнения, два триггера, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, информационный вход первого регистра сдвига является первым информационным входом устройства, разрядные выходы первого и второго регистров сдвига соединены соответственно с первыми и вторыми входами блока сравнения, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами второго регистра сдвига согласно правилу формирования псевдослучайной последовательности, управляющим входом устройства является установочный вход первого триггера, выход которого соединен с D-входом второго триггера, синхровход которого подключен к синхровходу устройства, к управляющему входу устройства подключен обнуляющий вход счетчика, суммирующий вход которого соединен с выходом элемента И, первый вход которого соединен с выходом второго триггера, разрядные выходы счетчика являются выходами устройства, отличающееся тем, что в него введен генератор тактовых импульсов и двухканальный трехразрядный мультиплексор, первый вход первого разряда которого объединен с первым входом второго разряда и подключен к синхровходу устройства, первый вход третьего разряда мультиплексора является вторым информационным входом устройства, второй вход первого разряда мультиплексора является входом логического нуля, второй вход второго разряда мультиплексора соединен с выходом генератора тактовых импульсов, второй вход третьего разряда мультиплексора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, адресный вход мультиплексора подключен к выходу второго триггера, второй вход элемента И соединен с выходом генератора тактовых импульсов, выход первого разряда мультиплексора соединен с тактовым входом первого регистра, выход второго разряда мультиплексора соединен с тактовым входом второго регистра, информационный вход которого соединен с выходом третьего разряда мультиплексора.

| Корреляционный дискриминатор времени задержки | 1987 |

|

SU1413643A1 |

| КОРРЕЛЯЦИОННЫЙ ДИСКРИМИНАТОР ВРЕМЕНИ ЗАДЕРЖКИ | 2003 |

|

RU2246133C2 |

| US 20020055830 A1, 09.05.2002 | |||

| US 7139785 B2, 21.11.2006 | |||

| Коррелятор | 1984 |

|

SU1224806A1 |

Авторы

Даты

2014-12-20—Публикация

2013-09-13—Подача