Изобретение относится к вычислительной технике и может быть использовано для имитации информационных сигналов на входах цифровых устройств при их автономной настройке, проверке работоспособности и диагностировании неиспрг:вностей.

Целью изобретения является сокращение аппаратурных затрат и расширение класса решаемых задач устройства путем обеспечения вьщачи имитируемой информации блоками произвольной длины.

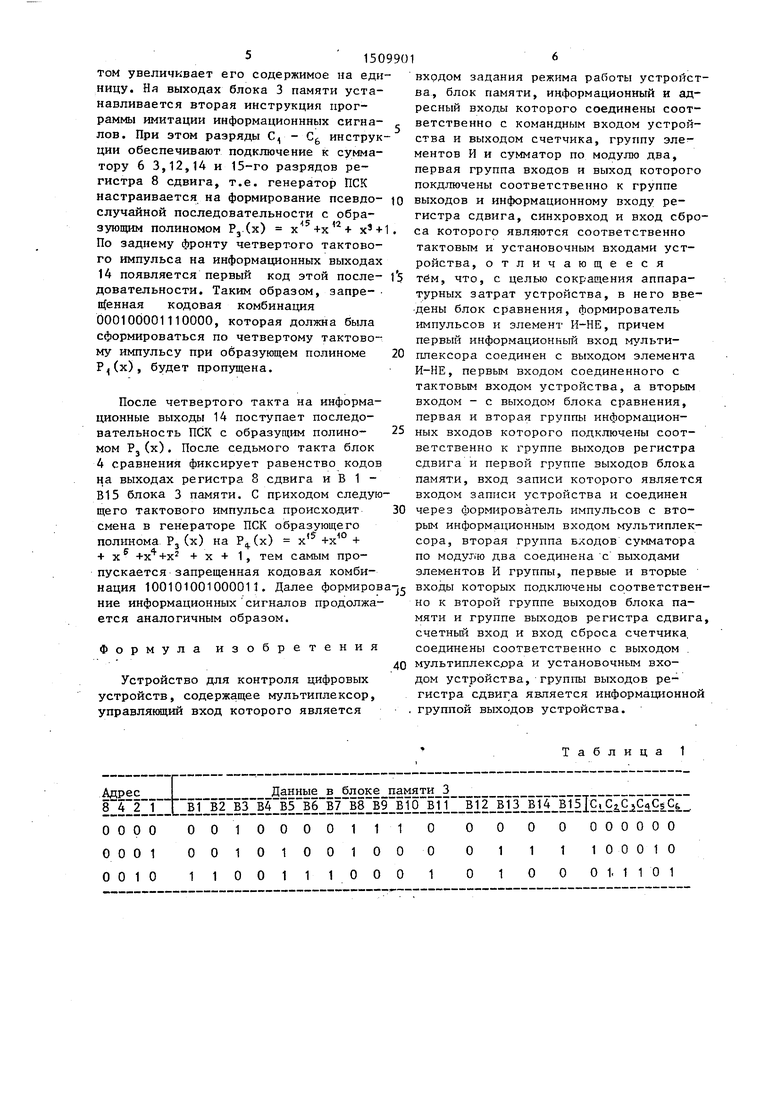

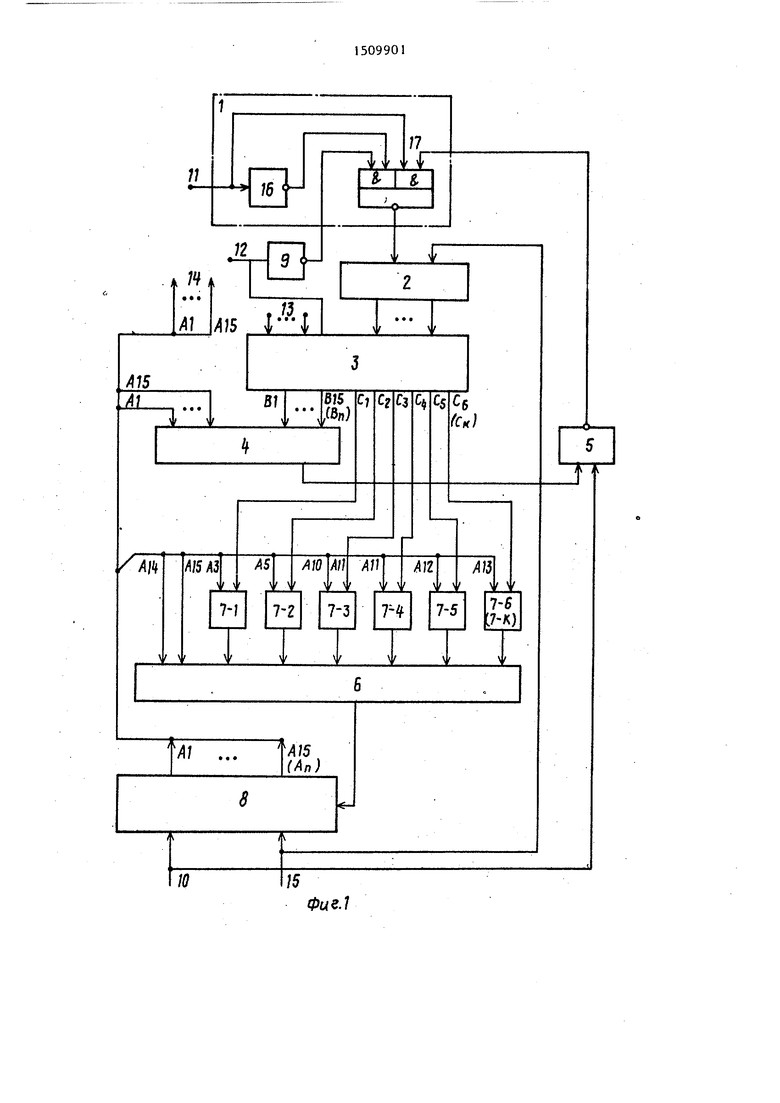

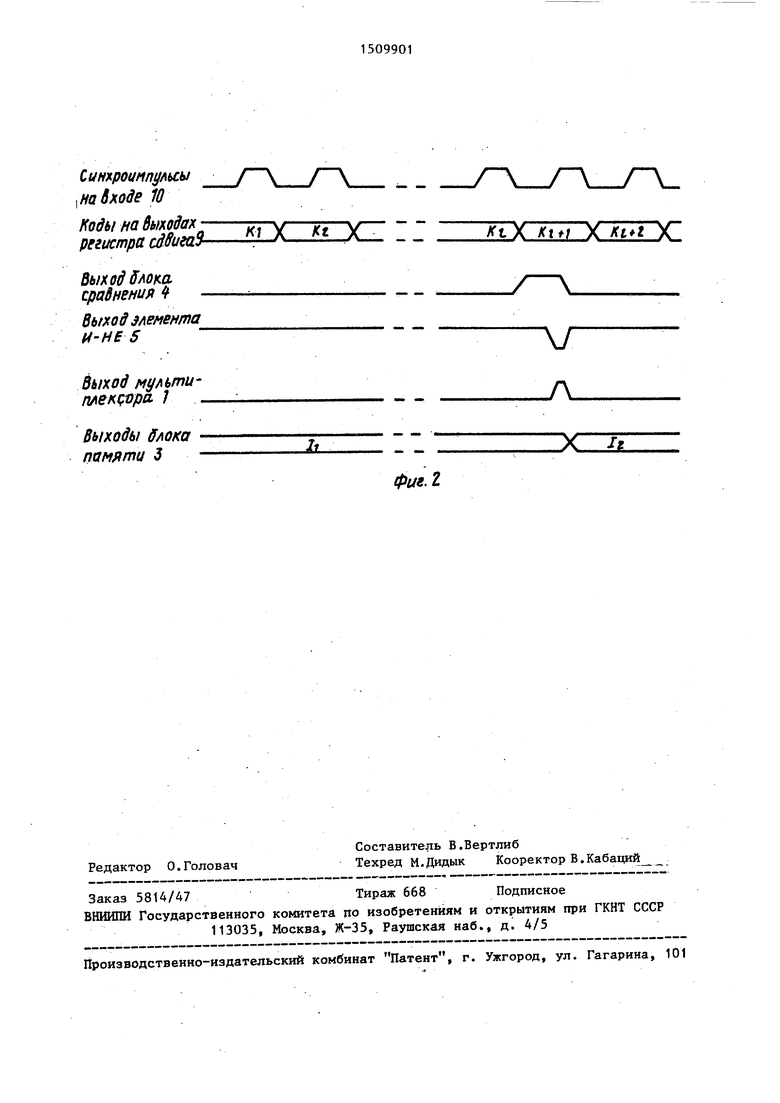

На фиг.1 представлена функциональная схема устройства для имитации информационных каналов; на фиг.2 временные диаграммы, поясняющие работу устройства,

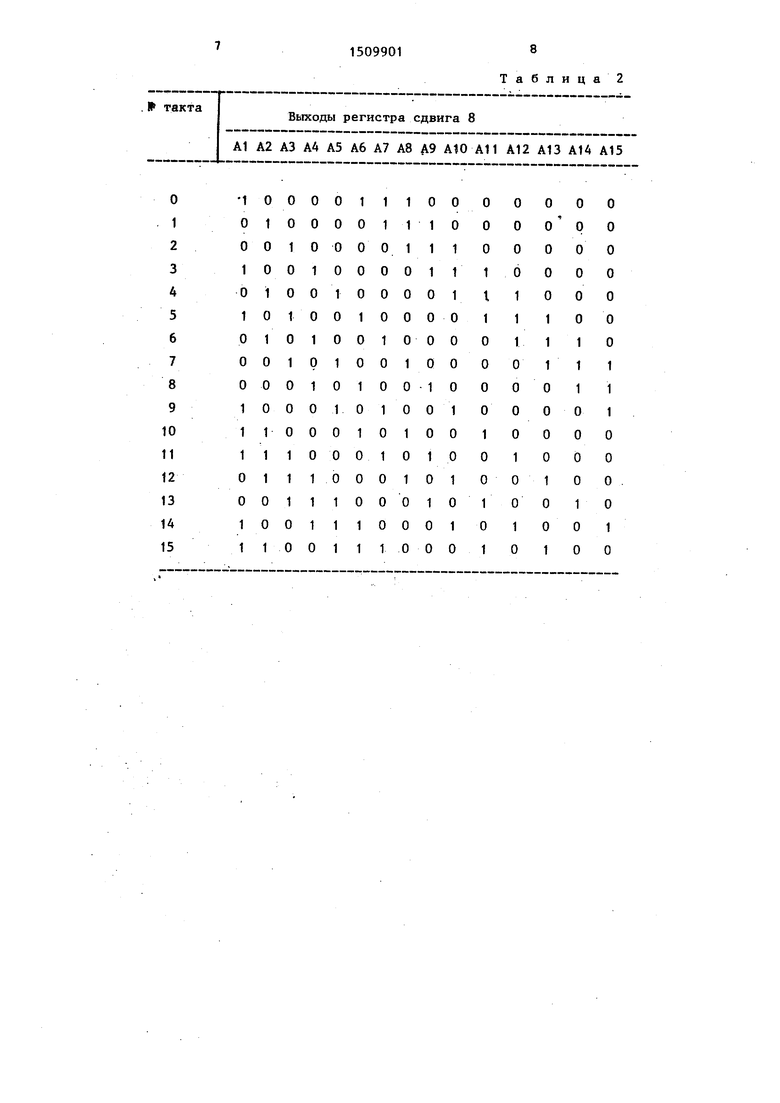

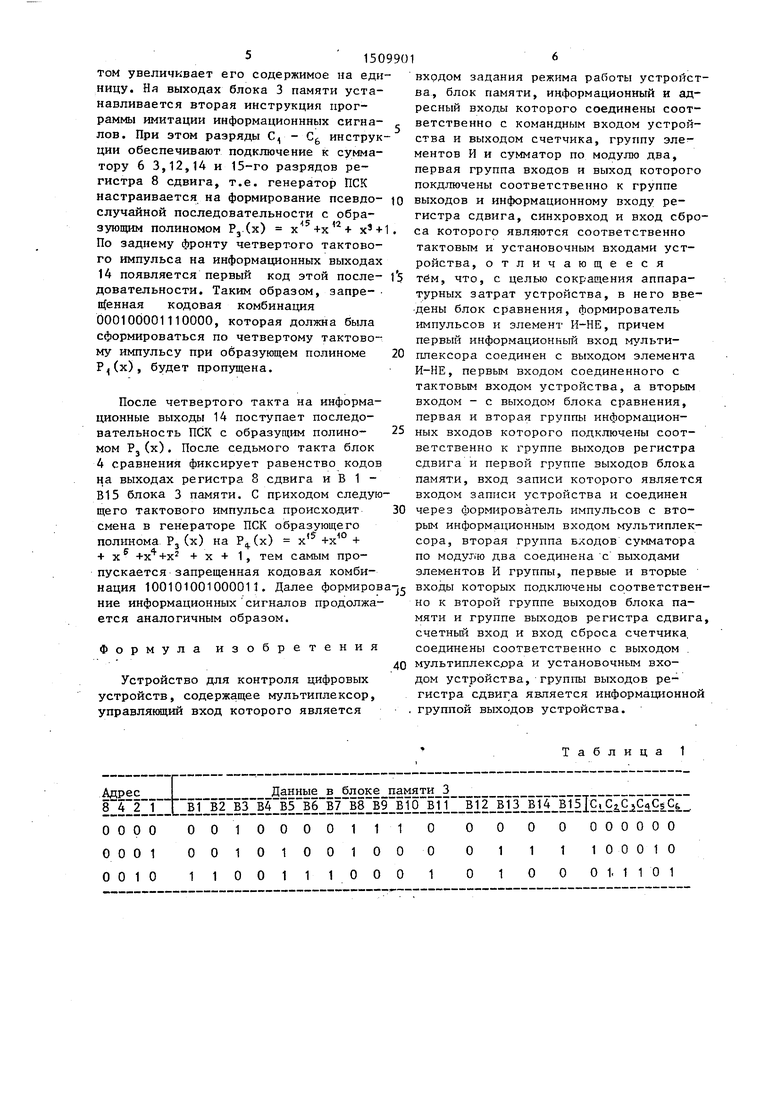

В табл. 1 и 2 приведены примеры имитируемой информационной последовательности.

Устройство содержит (фиг.1) мультиплексор 1, счетчик 2, блок 3 памяти, блок 4 сравнения, элемент И-НЕ 5, сумматор 6 по модулю два, группу элементов И 7-1 - 7-к, регистр 8 сдвига, формирователь 9 импульсов,. синхровход 10, управляющий вход 11, вход 12 записи, информационные входы 13, информационный выход 14 и установочный вход 15. Число к элементов И 7 в группе определяется числом разрядов регистСП

;о

(UD

31509

pa 8, необходимых для организации, кроме основной, дополнительных обратных связей в генераторе псевдослучайной последовательности (ПСК), пост роенном на базе регистра 8 сдвига с сумматором 6 по модулю два в обратной связи. На фиг.1 k 6, что позволяет формировать п-разрядные (фиг.1, ) последовательности с образующими по- липомами

Р. (х) х +1;

) х ° + х + 1;

РЗ (х) х + х + 1;

) х 5 + +1.

Мультиплексор 1 содержит злемент НЕ 16 и элемент И-ИЛИ-НЕ 17 (фиг.1).

Устройство работает слудеюущим образом.

В основу формирования информацион- ных сигналов для контролируемых объектов положено программируемое отсеивание запрещенных комбинаций из последователь ости кодов, получаемых с помощью генератора ПСК на ease регист ра 8 сдвига с сумматором 6 по модулю два в обратной связи.путем изменения структуры обратной связи генератора ПСК за один или несколько тактов до появления запрещенных кодовых ком- бинаций.

Перед началом работы для приведения устройства в исходное состояние подается импульс-на установочный вход 15. При этом в регистр 8 сдвига записывается начальная кодовая комбинация, а счетчик 2 обнуляется. Затем в блок 3 памяти загружается программа селекции, определяющая структуру выходной последовательности информацион ных сигналов, и, в частности, кодовые комбинации, которые будут отсеяны из формируемой последовательности кодов, программа селекции состоит из (п+1)- разрядных инструкций. Группа разрядов В1 - Вп каждой инструкции определяет п-разрядную кодовую.комбинацию,.формируемую на выходах регистра 8 сдвига за один или несколько тактов до появления запрещенного кода и при которой осуществляется изменение обратной связи в генератора ИСК. Разряды С, - С ц инструкции определяют структуру обратной связи генератора ПСК до достижения им кодовой комбинации, заданной в разрядах В1 - Вп той же инструкции. При загрузке программы селекции на управляющий вход 11 по- ,дается сигнал логического О, задаю

г

5

0 5 0

5 40 5 0

щий режим загрузки, на информационные входы 13 - код первой инструкции, а-на вход 12 записи - отрицательньй импульс сопровождения. Импульс записывает первую инструкцию программы в нулевую ячейку блока 3 памяти. По зад-ч нему фронту импульса записи формирователь 9 импульсов формирует отрицательный импульс, который поступает через мультиплексор 1 на счетный вход счетчика 2. По переднему фронту этого импульса содержимое счетчика

2увеличивается на единицу. Аналогично загружаются остальные инструкции программ в блок 3 памяти. По окончании загрузки программы селекции импульсов по установочному входу 15 счетчик 2 обнуляется. На вход 12 записи подается сигнал логической 1, определяющий режим чтения для блока

3памяти. На управляющем входе 11 устанавливается сигнал логической 1, задающий режим имитации информационных сигналов. На синхровход 10 подаются тактовые импульсы.

Рассмотрим работу на примере формирования фрагмента выходной последовательности кодов (фиг.З).

Предположим, что для контролируемого объекта запрещенными являются кодовые, комбинации 000100001110000 и 101001000011. В исходном сос тоянии в регистре 8 сдвига записана началь- ная комбинация 100001110000000, счетчик 2 обнулен и на выходах блока 3 памяти установлена первая инструкция программы селекции, К сумматору 6 подключены только 14-й и 15-й разряды регистра 8 сдвига,, т.е. в генераторе ПСК задана обратная связь, описываемая образующим полиномом Р(х) х + X 4- 1. По заднему фронту каждого тактового импульса на синхро- входе 10 генератор ПСК формирует очередной код, поступающий на информационные выходы 14. Блок 4 сравнения осуществляет сравнение кода а выходах регистра 8 сдвига с кодом, установленным на выходах В1 - В15 . блока 3 памяти. На третьем такте работы на выходе блока 4 сравнения формируется сигнал логической 1, свидетельствующий о совпадении сравниваемых кодов. На четвертом такте на выходе элемента И-НЕ 5 формируется отрицательный импульс, который через мультиплексор 1 поступает на счетный вход счетчика 2 и своим передним фронтом увеличивает его содержимое на единицу. Ня выходах блока 3 памяти устанавливается вторая инструкция программы имитации информациониных сигналов. При этом разряды С - С, инструкции обеспечивают подключение к сумматору 6 3,12,14 и 15-го разрядов регистра 8 сдвига, т.е. генератор ПСК

тактовым и установочным входами устройства, отличающе еся

20

настраивается на формирование псевдо- to выходов и информационному входу ре- случайной последовательности с обра- гистра сдвига, синхровход и вход сбро- зующим полиномом РЗ.(Х) х +1. са которого являются соответственно По заднему фронту четвертого тактового импульса на информационных выходах

14 появляется первый код этой после- тем, что, с целью сокращения аппара- довательности. Таким образом, эапре- пленная кодовая комбинация 000100001110000, которая должна была сформироваться по четвертому тактово му импульсу при образующем полиноме Р(х), будет пропущена.

После четвертого такта на информационные выходы 14 поступает последовательность ИСК с образущим полиномом PJ(х). После седьмого такта блок 4 сравнения фиксирует равенство кодов на выходах регистра 8 сдвига и В 1 - В15 блока 3 памяти. С приходом следующего тактового импульса происходит смена в генераторе ПСК образующего полинома РЗ (х) на Р,. (х) х + + х + X + 1, тем самым пропускается запрещенная кодовая комбитурных затрат устройства, в него вве- дены блок сравнения, формирователь импульсов и элемент Pi-HE, причем первый информационкьш вход мультиплексора соединен с выходом элемента И-НЕ, первым входом соединенного с тактовым входом устройства, а вторым входом - с выходом блока сравнения, первая и вторая группы информацион25 ных входов которого подключены соответственно к группе выходов регистра сдвига и первой группе выходов блока памяти, вход записи которого является входом записи устройства и соединен

30 через формирователь импульсов с вторым информационным входом fyльтиплeк- сора, вторая группа входов сумматора по модулю два соединена с выходами элементов И группы, первые и вторые

входом задания режима работы устройства, блок памяти, информационный и адресный входы которого соединены соответственно с командным входом устройства и выходом счетчика, группу элементов И и сумматор по модулю два, первая группа входов и выход которого покдлючены соответственно к группе

выходов и информационному входу ре- гистра сдвига, синхровход и вход сбро- са которого являются соответственно

тактовым и установочным входами устройства, отличающе еся

ыходов и информационному входу ре- гистра сдвига, синхровход и вход сбро а которого являются соответственно

тем, что, с целью сокращения аппара-

тем, что, с целью сокращения аппара-

турных затрат устройства, в него вве- дены блок сравнения, формирователь импульсов и элемент Pi-HE, причем первый информационкьш вход мультиплексора соединен с выходом элемента И-НЕ, первым входом соединенного с тактовым входом устройства, а вторым входом - с выходом блока сравнения, первая и вторая группы информационных входов которого подключены соответственно к группе выходов регистра сдвига и первой группе выходов блока памяти, вход записи которого является входом записи устройства и соединен

через формирователь импульсов с вторым информационным входом fyльтиплeк- сора, вторая группа входов сумматора по модулю два соединена с выходами элементов И группы, первые и вторые

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

Изобретение относится к вычислительной технике и может быть использовано для имитации информационных посылок в процессе настройки, контроля и диагностирования неисправностей цифровых устройств. Устройство содержит мультиплексор, счетчик, блок памяти, группу элементов И, сумматор по модулю два и регистр сдвига. Цель изобретения состоит в сокращении аппаратурных затрат устройства и достигается введением в него блока сравнения, элемента И-НЕ и формирователя импульсов. Имитируемая информация формируется из последовательности псевдослучайных кодов, генерируемых регистром сдвига с сумматором по модулю два в обратной связи, путем отсеивания запрещенных комбинаций. Отсеивание осуществляется по программе, хранящейся в блоке памяти, путем изменения с помощью группы элементов И структуры обратной связи генератора псевдослучайных кодов в моменты формирования им определенных кодов, заданных программой и обнаруживаемых блоком сравнения. 3 ил.

нация 100101001000011. Далее формирова- входы которых подключены соответствен- ние информационных сигналов продолжа- но к второй группе выходов блока памяти и группе выходов регистра сдвига, счетный вход и вход сброса счетчика, соединены соответственно с выходом . 40 мультиплексора и установочным входом устройства, группы выходов регистра сдвига является информационной . группой выходов устройства.

ется аналогичным образом. Формула изобретения

Устройство для контроля цифровых устройств, содержащее мультиплексор, управляющий вход которого является

Таблица 1

Таблица2

ФыеЛ

Син)1роимп1/Аьсы набмде 10

Коды на бымдах

JA..l

Коды на ВыходахjTpy-j T-у- - - FTV к, V V

регистра сдЗиш - -«-JL- tJULliLJULLtLje

Выход SAOt(.ii сравнения 4

Bbfxod элемента И-Н 5

Л/

Выход мульти- ПАек1 13ри 1 .

Выходы блока - памяти 3

Л/

yv

фиг.1

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-09-23—Публикация

1988-03-31—Подача