Изобретение относится к устройствам автоматики и вычислительной техники и позволяет повысить помехоустойчивость многоканальных счетных и интегрирующих устройств.

Известен многоканальный счетчик импульсов (см. авторское свидетельство СССР №1170610 от 30.09.1983, «Многоканальный счетчик импульсов», А.А. Сенюта, А.Г. Далингер и Н.И. Левашев, опубликовано 30.07.1985 г., БИ №28), содержащий сумматор, оперативное запоминающее устройство, блок начальной установки, устройство управления, буферное запоминающее устройство, RS-триггер, коммутирующий элемент и буферный регистр. Информационный вход сумматора соединен с входом оперативного запоминающего устройства. Один вход сумматора соединен с первым выходом блока начальной установки, второй выход которого соединен с другим информационным входом сумматора. Первый вход блока начальной установки соединен с шиной начальной установки, а второй вход через буферный регистр соединен с выходом оперативного запоминающего устройства. Управляющие выходы устройства управления соединены соответственно с управляющими входами буферного запоминающего устройства, блока начальной установки, оперативного запоминающего устройства, коммутирующего элемента, буферного регистра и входом сброса RS-триггера. Тактовый вход устройства управления соединен с тактовой шиной, а информационные шины подключены к информационным входам буферного запоминающего элемента, выход которого соединен с входом установки RS-триггера. Выход RS-триггера соединен с входом переноса сумматора и первым входом коммутирующего элемента, второй вход которого соединен с дополнительным выходом блока начальной установки. Выход коммутирующего элемента соединен с входом записи оперативного запоминающего устройства. Выход переполнения сумматора соединен с входом переполнения блока начальной установки и с выходной шиной переполнения. Адресный вход устройства управления соединен с адресным входом оперативного запоминающего устройства и выходной адресной шиной.

Недостатком данного устройства является низкая помехоустойчивость, что связано с большой ценой сбоя при совпадении помехи с моментом переключения счетчика.

Известен многоканальный счетчик импульсов (см. патент РФ №2152685 от 19.01.1999, «Многоканальный счетчик импульсов», Л.Б. Егоров, И.В. Цетлин, опубликовано 10.07.2000, БИ №19), содержащий блок оперативного запоминающего устройства (ОЗУ), блок начальной установки, устройство управления, триггер четности, триггер переноса, N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, N элементов ИЛИ, N элементов ИЛИ-НЕ, шину начальной установки и шину адреса. Блок ОЗУ выполнен в виде N ячеек ОЗУ, адресные входы которых соединены с шиной адреса, входы выборки соединены с управляющим входом блока начальной установки, а первые входы записи ячеек соединены со вторым входом блока начальной установки и шиной записи. Первые информационные входы ячеек ОЗУ соединены с соответствующими информационными выходами блока начальной установки, второй информационный вход и прямой выход каждой ячейки соединены соответственно с первым и вторым входами соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй вход записи ячеек - с выходом соответствующего элемента ИЛИ-НЕ. Инверсный выход каждой i-й ячейки, кроме последней, соединен с первым входом (i+1)-го элемента ИЛИ-НЕ. Первый вход каждого i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, кроме последнего, соединен с выходом (i+1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Первый вход последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым выходом устройства управления, а выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом устройства управления и информационным входом триггера четности, тактовый вход и выход которого соединены соответственно со вторым и третьим входами устройства управления. Шина признака старшей строки и тактовая шина соединены соответственно со вторым и четвертым входами устройства управления, второй и третий выходы которого соединены с первыми входами первых элементов ИЛИ и ИЛИ-НЕ соответственно. Вторые входы первых элементов ИЛИ и ИЛИ-НЕ соединены с четвертым входом устройства управления. Прямой выход каждой i-ой ячейки, кроме последней, соединен с первым входом (i+1)-го элемента ИЛИ, второй вход которого соединен с выходом i-го элемента ИЛИ и вторым входом (i+1)-го элемента ИЛИ-НЕ. Выход последнего элемента ИЛИ соединен с информационным входом триггера переноса, тактовый вход которого соединен с шиной признака младшей строки, а выход - с пятым входом устройства управления. Шина выборки и шина блокировки соединены соответственно с третьим и четвертым входами блока начальной установки.

Недостатком данного устройства является низкая помехоустойчивость в режиме ОЗУ (шина начальной установки используется в этом режиме в качестве шины данных), так как код Грея защищает информацию от помех только в счетных каналах и не защищает в других каналах ОЗУ.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбрано в качестве прототипа.

Достигаемым техническим результатом является повышение помехоустойчивости устройства во всех режимах его работы.

Указанный технический результат достигается тем, что в многоканальном счетчике импульсов, содержащем первое оперативное запоминающее устройство, устройство управления, подключенное к тактовой шине, первый триггер четности, первый, второй и третий элементы ИЛИ, первые входы которых объединены и подключены к шине блокировки, второй вход первого элемента ИЛИ соединен с первым выходом устройства управления, новым является то, что дополнительно введены второй и третий триггеры четности, автономный источник питания, второе оперативное запоминающее устройство, первый и второй выводы которого соединены с первым и вторым выводами первого оперативного запоминающего устройства и первым и вторым выводами автономного источника питания, соответственно, второй и третий выходы устройства управления соединены со вторыми входами второго и третьего элементов ИЛИ соответственно, выход последнего из которых соединен с первыми входами первого, второго и третьего триггеров четности, вторые входы которых объединены и подключены к первому выводу автономного источника питания, второй вывод которого соединен с третьими входами первого, второго и третьего триггеров четности, группы информационных выводов и адресных выходов устройства управления соединены с группами информационных выводов и адресных входов соответственно первого и второго оперативных запоминающих устройств, входы блокировки которых соединены с выходами первого и второго элементов ИЛИ соответственно, первый, второй и третий выводы из группы информационных выводов устройства управления подключены к информационным выводам первого, второго и третьего триггеров четности соответственно, выход записи и выход выборки устройства управления подключены соответственно к входам записи и входам выборки первого и второго оперативных запоминающих устройств и первого, второго и третьего триггеров четности, вход блокировки устройства управления соединен с шиной блокировки.

Указанная совокупность существенных признаков позволяет повысить помехоустойчивость многоканального счетчика импульсов во всех режимах его работы за счет дублирования ОЗУ с поочередным обращением к ним и защиты информации, хранящейся в ОЗУ, с помощью кода Хэмминга, а также за счет мажоритарного дублирования признака четности обращений к ОЗУ.

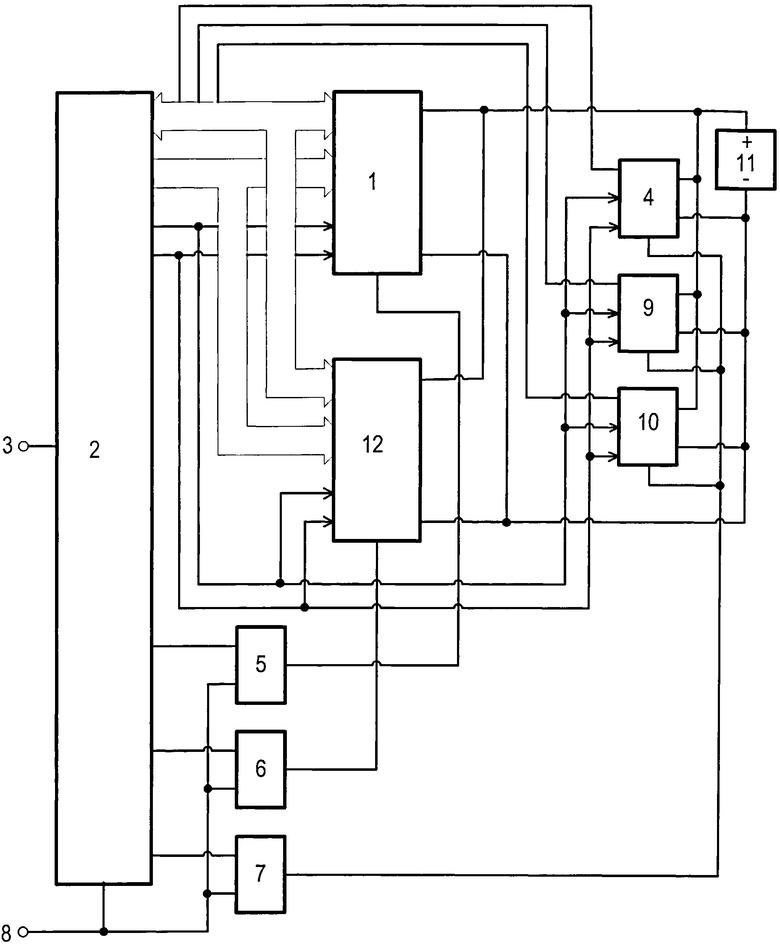

На фигуре приведена схема многоканального счетчика импульсов.

Многоканальный счетчик импульсов содержит первое оперативное запоминающее устройство (ОЗУ) 1, устройство управления 2, подключенное к тактовой шине 3, первый триггер четности 4, первый 5, второй 6 и третий 7 элементы ИЛИ, первые входы которых объединены и подключены к шине блокировки 8. Второй вход первого элемента ИЛИ 5 соединен с первым выходом устройства управления 2. Второй 9 и третий 10 триггеры четности, автономный источник питания 11, второе ОЗУ 12, первый и второй выводы которого соединены с первым и вторым выводами ОЗУ 1 и первым и вторым выводами автономного источника питания 11, соответственно. Второй и третий выходы устройства управления 2 соединены со вторыми входами соответственно второго 6 и третьего 7 элементов ИЛИ, выход последнего из которых соединен с первыми входами 4, 9 и 10 триггеров четности, вторые входы которых объединены и подключены к первому выводу автономного источника питания 11, второй вывод которого соединен с третьими входами 4, 9 и 10 триггеров четности. Группы информационных выводов и адресных выходов устройства управления 2 соединены с группами информационных выводов и адресных входов соответственно первого 1 и второго 12 ОЗУ, входы блокировки которых соединены с выходами соответственно 5 и 6 элементов ИЛИ. Первый, второй и третий выводы из группы информационных выводов устройства управления 2 подключены к информационным выводам соответственно 4, 9 и 10 триггеров четности. Выход записи и выход выборки устройства управления 2 подключены соответственно к входам записи и входам выборки первого 1 и второго 12 ОЗУ и 4, 9 и 10 триггеров четности. Вход блокировки устройства управления 2 соединен с шиной блокировки 8.

Многоканальный счетчик импульсов (см. Фигуру) работает следующим образом.

Ячейки ОЗУ 1 и 12, а также триггеры четности 4, 9 и 10 наиболее чувствительны к помехам в моменты переключения, более устойчивы к помехам в режиме хранения информации, а их наибольшая помехоустойчивость достигается в состоянии блокировки, когда триггерные структуры ОЗУ и триггеры четности отключены от выводов микросхем, в которых они расположены. Устройство 2 управления выполнено в виде микроконтроллера, который выполняет программу, реализующую функции многоканального счета импульсов, интегрирования и других вычислений с использованием результатов счета. Результаты счета и промежуточных вычислений запоминаются и в первом 1 и во втором 12 ОЗУ, но обращение к указанным ОЗУ производится поочередно в разные промежутки времени. Таким образом, в любой момент времени хотя бы одно ОЗУ находится в заблокированном состоянии, в котором оно обладает наивысшей помехоустойчивостью. Между обращениями к ОЗУ изменяется состояние триггеров четности 4, 9 и 10 свидетельствующее о том, к первому 1 или второму 12 ОЗУ будет производиться следующее обращение устройства управления 2.

Во время действия помехи на шину блокировки 8 поступает сигнал от датчиков помех по схеме ИЛИ. В качестве датчиков помех могут использоваться датчик провала напряжения питания (супервизор), датчик электромагнитной наводки (антенна) и т.п. Набор датчиков помех зависит от условий применения (помеховой обстановки) многоканального счетчика импульсов. Таким образом, во время действия помехи на выходах элементов ИЛИ 5, 6 и 7 формируются сигналы блокировки первого 1 и второго 12 ОЗУ и триггеров четности 4, 9 и 10. Сохранность информации в указанных устройствах в заблокированном состоянии обеспечивается питанием этих устройств от автономного источника питания 11, в качестве которого используется аккумулятор, обладающий высокой устойчивостью к помехам любого типа.

После окончания действия помехи, устройство управления 2 считывает информацию из триггеров четности 4, 9 и 10, обрабатывает ее по мажоритарному принципу и определяет, к какому ОЗУ должно производиться следующее обращение.

Схема заявляемого устройства позволяет также парировать не только одиночные сбои триггерных структур ОЗУ 1 и 12 и триггеров четности 4, 9 и 10, но и их одиночные отказы, происходящие с вероятностью q. Так как отказ триггерной структуры является событием независимым (не зависит от отказа других триггерных структур), то вероятность отказа двух и более триггерных структур равна соответствующей степенной функции qn (где n - число отказавших триггерных структур). Таким образом, наиболее вероятен отказ одиночной триггерной структуры. Вероятностью отказа двух и более триггерных структур можно пренебречь в силу ее пренебрежимо малого значения (например, если q=0.0001, то q2=0,00000001). Информация, хранящаяся в ОЗУ 1 и 12, защищается кодом Хэмминга, позволяющим обнаруживать и исправлять одиночные ошибки. Информация, хранящаяся в триггерах четности 4, 9 и 10, защищена мажоритарной функцией, которая тоже исправляет одиночную ошибку.

Проведено макетирование многоканального счетчика импульсов с использованием микросхем 1620РУ6У в качестве ОЗУ. Остальная часть устройства реализована на базе микросхемы БМК 5517ВЦ2У. Испытания макета в условиях действия различных помех подтвердили работоспособность заявляемого устройства и его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| Многоканальный счетчик импульсов | 1987 |

|

SU1508342A1 |

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2011 |

|

RU2455672C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1336239A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2010 |

|

RU2429515C1 |

| РЕГИСТРАТОР АВАРИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ЭНЕРГОСИСТЕМ | 2009 |

|

RU2402067C1 |

Изобретение относится к счетчикам импульсов. Техническим результатом является повышение помехоустойчивости в режиме ОЗУ. Счетчик включает ОЗУ 12 и ОЗУ 1. Группы информационных выводов и адресных выходов устройства управления 2 соединены с группами информационных выводов и адресных входов соответственно первого 1 и второго 12 ОЗУ, входы блокировки которых соединены с выходами соответственно первого 5 и второго 6 элементов ИЛИ. Причем выводы группы информационных выводов устройства управления 2 подключены к соответствующим информационным выводам соответствующих триггеров четности. Выход записи и выход выборки устройства управления 2 подключены соответственно к входам записи и входам выборки первого 1 и второго 12 ОЗУ и первого 4, второго 9 и третьего 10 триггеров четности. Вход блокировки устройства управления 2 соединен с шиной блокировки 2. 1 ил.

Многоканальный счетчик импульсов, содержащий первое оперативное запоминающее устройство, устройство управления, подключенное к тактовой шине, первый триггер четности, первый, второй и третий элементы ИЛИ, первые входы которых объединены и подключены к шине блокировки, второй вход первого элемента ИЛИ соединен с первым выходом устройства управления, отличающийся тем, что дополнительно введены второй и третий триггеры четности, автономный источник питания, второе оперативное запоминающее устройство, первый и второй выводы которого соединены с первым и вторым выводами первого оперативного запоминающего устройства и первым и вторым выводами автономного источника питания, соответственно, второй и третий выходы устройства управления соединены со вторыми входами соответственно второго и третьего элементов ИЛИ, выход последнего из которых соединен с первыми входами первого, второго и третьего триггеров четности, вторые входы которых объединены и подключены к первому выводу автономного источника питания, второй вывод которого соединен с третьими входами первого, второго и третьего триггеров четности, группы информационных выводов и адресных выходов устройства управления соединены с группами информационных выводов и адресных входов соответственно первого и второго оперативных запоминающих устройств, входы блокировки которых соединены с выходами соответственно первого и второго элементов ИЛИ, первый, второй и третий выводы из группы информационных выводов устройства управления подключены к информационным выводам соответственно первого, второго и третьего триггеров четности, выход записи и выход выборки устройства управления подключены соответственно к входам записи и входам выборки первого и второго оперативных запоминающих устройств и первого, второго и третьего триггеров четности, вход блокировки устройства управления соединен с шиной блокировки.

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| Счетчик импульсов | 1981 |

|

SU978358A1 |

| US 8253463 B1, 28.08.2012 | |||

| US 6504876 B1, 07.01.2003 | |||

Авторы

Даты

2015-01-10—Публикация

2014-01-30—Подача