Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах сопряжения цифровых вычислительных машин, обмена информацией, измерительных комплексах научных исследований и управления технологическими процессами.

Цель изобретения - повышение нановки в 1 триггера 12, заканчивается цикл обнуления ОЗУ 5 и начинается цикл ввода и преобразования входной информации, поступающей с шин 17 на информационные входы коммутатора 15. На выходах счетчиков 2-4 под воздействием импульсов генератора 1 возникает монотонно возрастающий код. На дежности за счет упрощения устройства Q выходах дешифратора 16 формируются и расширение области применения за распределенные во времени сигналы, счет возможности получения выходных поступающие на управляющие входы ком- сигналов в последовательном коде. мутатора 15.

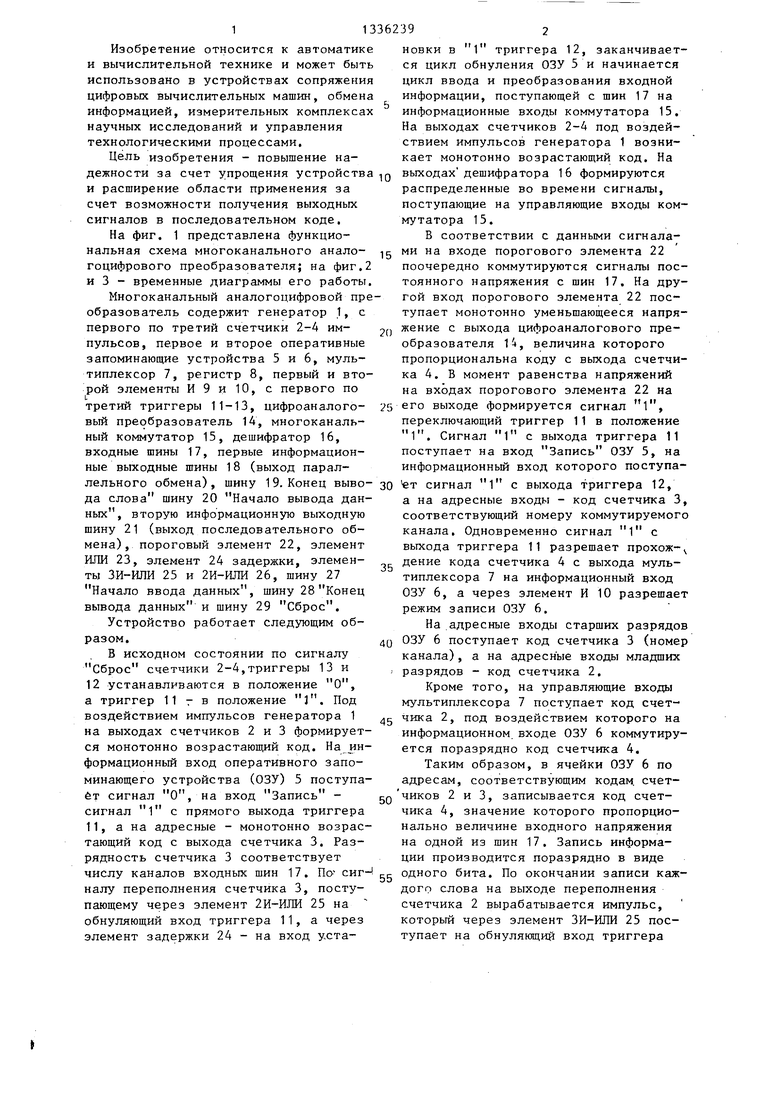

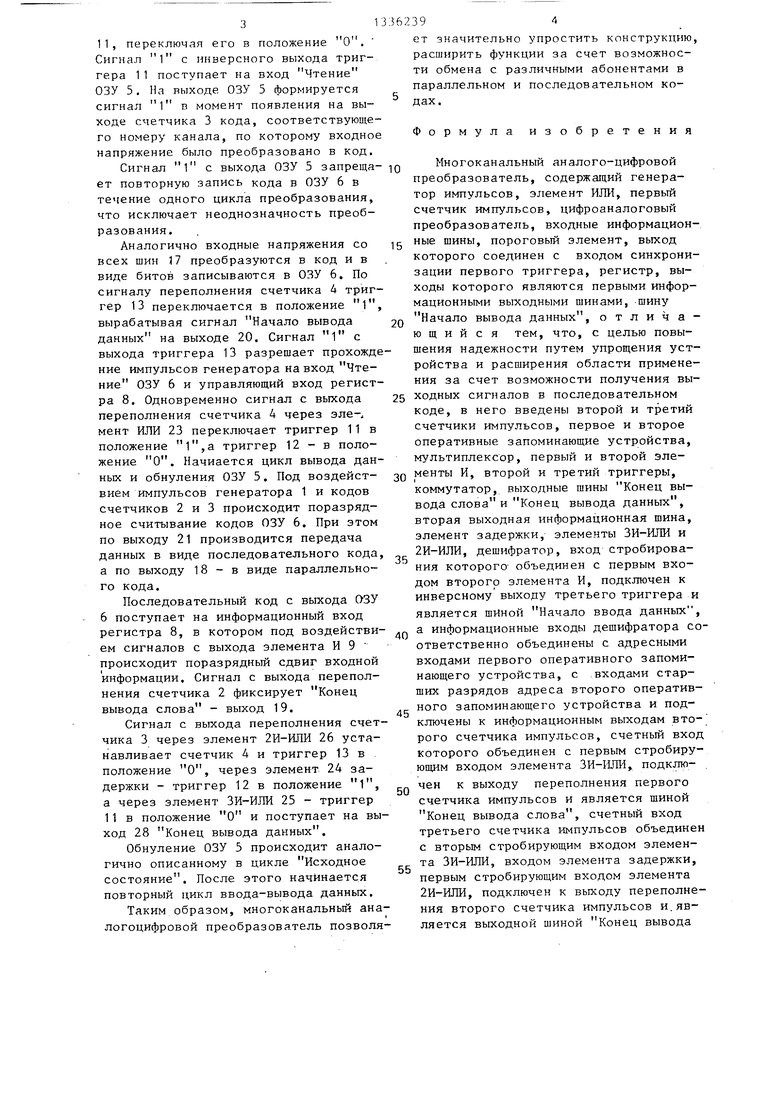

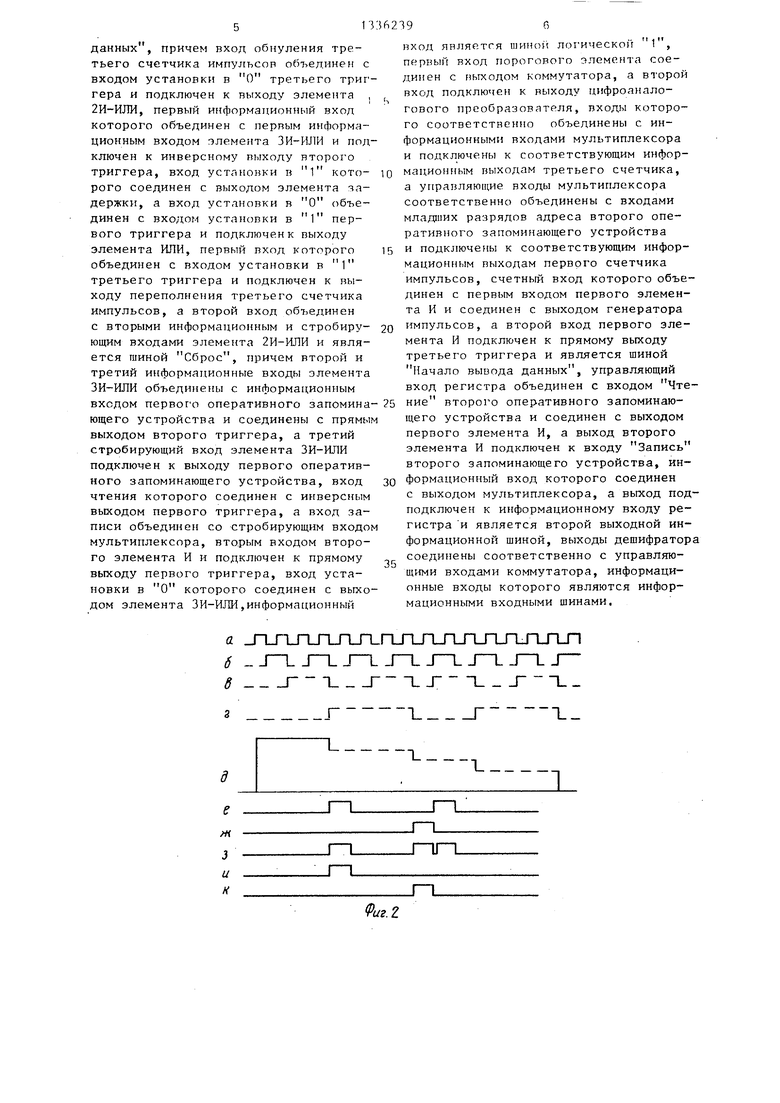

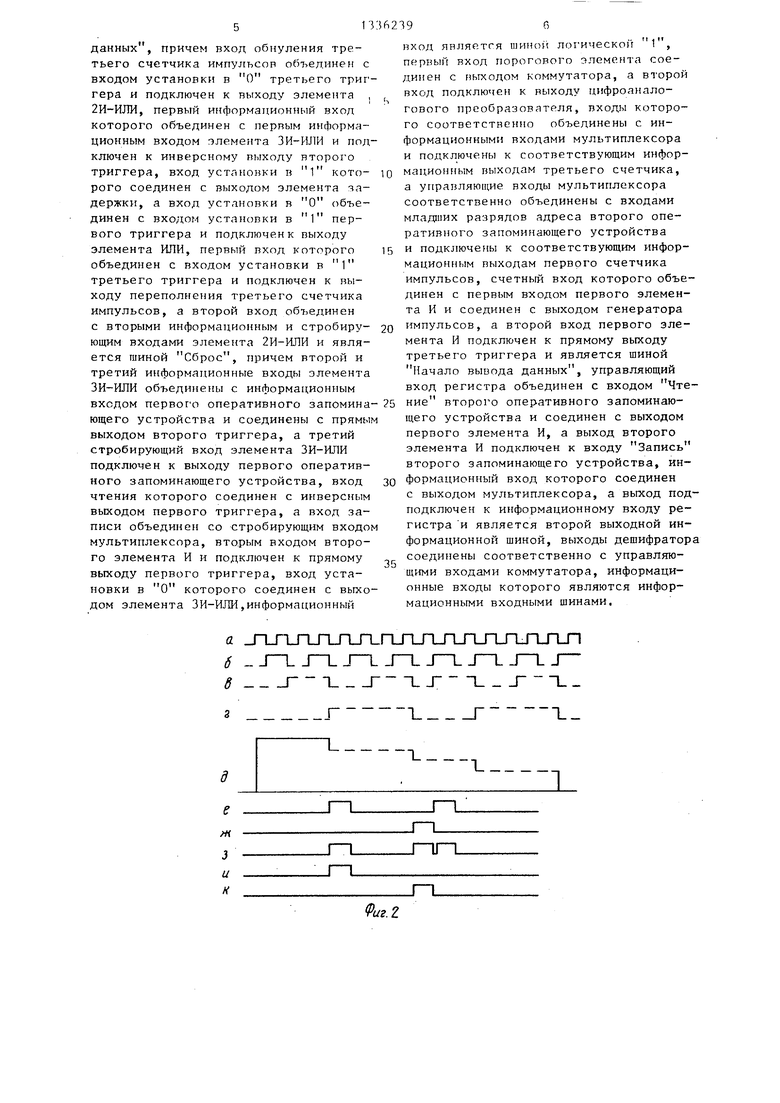

На фиг. 1 представлена функцио- В соответствии с данными сигнала- нальная схема многоканального анало- g ми на входе порогового элемента 22 гоцифрового преобразователя; на фиг.2 поочередно коммутируются сигналы пос- и 3 - временные диаграммы его работы.

Многоканальный аналогоцифровой преобразователь содержит генератор 1, с

тоянного напряжения с шин 17. На другой вход порогового элемента 22 поступает монотонно уменьшающееся напряжение с выхода цифроаналогового преобразователя 14, величина которого пропорциональна коду с выхода счетчика 4. В момент равенства напряжений на входах порогового элемента 22 на

первого по третий счетчики 2-4 импульсов, первое и второе оперативные запоминающие устройства 5 и 6, мультиплексор 7, регистр 8, первый и второй элементы И 9 и 10, с первого по

35

40

третий триггеры 11-13, цифроаналого- 25 его выходе формируется сигнал 1,

переключающий триггер 11 в положение 1. Сигнал 1 с выхода триггера 11 поступает на вход Запись ОЗУ 5, на информационньй вход которого поступа- лельного обмена), шину 19. Конец выво- зо ет сигнал 1 с выхода триггера 12, да слова шину 20 Начало вывода дан- а на адресные входы - код счетчика 3,

соответствующий номеру коммутируемого канала. Одновременно сигнал 1 с выхода триггера 11 разрешает прохож- дение кода счетчика 4 с выхода мультиплексора 7 на информационный вход ОЗУ 6, а через элемент И 10 разрешает режим записи ОЗУ 6.

На адресные входы старших разрядов ОЗУ 6 поступает код счетчика 3 (номер канала), а на адресные входы младших разрядов - код счетчика 2.

Кроме того, на управляющие входы мультиплексора 7 поступает код счет- 4g чика 2, под воздействием которого на информационном входе ОЗУ 6 коммутируется поразрядно код счетчика 4.

Таким образом, в ячейки ОЗУ 6 по адресам, соответствующим кодам, счетчиков 2 и 3, записывается код счетчика 4, значение которого пропорцио- 11, а на адресные - монотонно возрас- нально величине входного напряжения тающий код с выхода счетчика 3. Раз- на одной из шин 17. Запись информа- рядность счетчика 3 соответствует ции производится поразрядно в виде числу каналов входных шин 17. По- сиг-1 одного бита. По окончании записи каж- налу переполнения счетчика 3, посту- догп слова на выходе переполнения пающему через элемент 2И-ИЛИ 25 на счетчика 2 вырабатывается импульс, обнуляющий вход триггера 11, а через который через элемент ЗИ-ИЛИ 25 пос- элемент задержки 24 - на вход уста- тупает на обнуляющий вход триггера

вый преобразователь 14, многоканальный коммутатор 15, дешифратор 16, входные шины 17, первые информационные выходные шины 18 (выход паралных, вторую информационную выходную шину 21 (выход последовательного обмена), пороговый элемент 22, элемент ИЛИ 23, элемент 24 задержки, элементы ЗИ-ИЛИ 25 и 2И-ИЛИ 26, шину 27 Начало ввода данных, шину 28 Конец вывода данных и шину 29 Сброс.

Устройство работает следующим образом.

В исходном состоянии по сигналу Сброс счетчики 2-4,триггеры 13 и 12 устанавливаются в положение О, а триггер 11 г в положение 1. Под воздействием импульсов генератора 1 на выходах счетчиков 2 и 3 формируется монотонно возрастающий код. На JIH- формационный вход оперативного запоминающего устройства (ОЗУ) 5 поступает сигнал О, на вход Запись - сигнал 1 с прямого выхода триггера

50

новки в 1 триггера 12, заканчиваетВ соответствии с данными сигнала- ми на входе порогового элемента 22 поочередно коммутируются сигналы пос-

тоянного напряжения с шин 17. На другой вход порогового элемента 22 поступает монотонно уменьшающееся напряжение с выхода цифроаналогового преобразователя 14, величина которого пропорциональна коду с выхода счетчика 4. В момент равенства напряжений на входах порогового элемента 22 на

3

11, переключая его в положение О. Сигнал 1 с инверсного выхода триггера 11 поступает на вход Чтение ОЗУ 5, На выходе ОЗУ 5 формируется сигнал 1 в момент появления на выходе счетчика 3 кода, соответствующего номеру канала, по которому входно напряжение было преобразовано в код.

Сигнал 1 с выхода ОЗУ 5 запреща ет повторную запись кода в ОЗУ 6 в течение одного цикла преобразования, что исключает неоднозначность преобразования.

Аналогично входные напряжения со всех шин 17 преобразуются в код и в виде битов записываются в ОЗУ 6. По сигналу переполнения счетчика 4 триггер 13 переключается в положение 1 вырабатывая сигнал Начало вывода данных на выходе 20. Сигнал 1 с выхода триггера 13 разрешает прохождние импульсов генератора на вход Чтение ОЗУ 6 и управляющий вход регистра 8. Одновременно сигнал с выхода переполнения счетчика 4 через эле- мент ИЛИ 23 переключает триггер 11 в положение 1,а триггер 12 - в положение О. Начиается цикл вывода данных и обнуления ОЗУ 5. Под воздейст- вием импульсов генератора 1 и кодов счетчиков 2 и 3 происходит поразрядное считывание кодов ОЗУ 6. При этом по выходу 21 производится передача данных в виде последовательного кода

,

а по выходу 18 - в виде параллельного кода.

Последовательный код с выхода ОЗУ 6 поступает на информационный вход регистра 8, в котором под воздействи ем сигналов с выхода элемента И 9 происходит поразрядный сдвиг входной информации. Сигнал с выхода переполнения счетчика 2 фиксирует Конец вывода слова - выход 19.

Сигнал с выхода переполнения счетчика 3 через элемент 2И-ИЛИ 26 устанавливает счетчик 4 и триггер 13 в положение О, через элемент 24 задержки - триггер 12 в положение 1, а через элемент ЗИ-ИЖ 25 - триггер 11 в положение О и поступает на выход 28 Конец вывода данных.

Обнуление ОЗУ 5 происходит аналогично описанному в цикле Исходное состояние. После этого начинается повторный цикл ввода-вывода данных.

Таким образом, многоканальный ана логоцифровой преобразователь позволя

.394

ет значительно упростить конструкцию, расширить функции за счет возможности обмена с различными абонентами в параллельном и последовательном кодах.

Формула изобретения

Многоканальный аналого-цифровой преобразователь, содержащий генератор импульсов, элемент ИЛИ, первый счетчик импульсов, цифроаналоговый преобразователь, входные информационные шины, пороговый элемент, выход которого соединен с входом синхронизации первого триггера, регистр, выходы которого являются первыми информационными выходными шинами,-шину Начало вывода данных, отличающийся тем, что, с целью повышения надежности путем упрощения устройства и расширения области применения за счет возможности получения выходных сигналов в последовательном коде, в него введены второй и третий счетчики импульсов, первое и второе оперативные запоминающие устройства, мультиплексор, первый и второй элементы И, второй и третий триггеры, коммутатор, выходные шины Конец вывода слова и Конец вывода данных, вторая выходная информационная шина, элемент задержки, элементы ЗИ-ИЛИ и 2И-ИЛИ, дешифратор, вход стробирова- ния которого- объединен с первым входом второго элемента И, подключен к инверсному выходу третьего триггера и является шиной Начало ввода данных, а информационные входы дешифратора соответственно объединены с адресными входами первого оперативного запоминающего устройства, с входами старших разрядов адреса второго оперативного запоминающего устройства и подключены к информационным выходам вто- рого счетчика импульсов, счетный вход которого объединен с первым стробиру- ющим входом элемента ЗИ-ИШ1, подклто- ,

чей к выходу переполнения первого счетчика импульсов и является шиной Конец вывода слова, счетный вход третьего счетчика импульсов объединен с вторым стробирующим входом элемента ЗИ-ИЛИ, входом элемента задержки, первым стробирующим входом элемента 2И-ИЛИ, подключен к выходу переполнения второго счетчика импульсов и.является выходной шиной Конец вывода

данных , причем вход обнуления третьего счетчика импульсов объединен с входом установки в О третьего триггера и подключен к выходу элемента 2И-ИЛИ, первый информационный вход которого объединен с первым информационным входом элемента ЗИ-ИЛИ и подключен к инверсному выходу второго триггера, вход установки в 1 кото- рого соединен с выходом элемента задержки, а вход установки в О объединен с входом установки в 1 первого триггера и подключен к выходу элемента ИЛИ, первый вход которого объединен с входом установки в 1 третьего триггера и подключен к уш- ходу переполнения третьего счетчика импульсов, а второй вход об7,единен с вторыми информационным и стробиру- ющим входами элемента 2И-ИЛИ и является шиной Сброс, причем второй и третий информационные входы элемента ЗИ-ИЛИ объединены с информационным входом первого оперативного запоминающего устройства и соединены с прямы выходом второго триггера, а третий стробирующий вход элемента ЗИ-ИЛИ подключен к выходу первого оперативного запоминающего устройства, вход чтения которого соединен с инверсным вьсходом первого триггера, а вход записи объединен со стробирующим входо мультиплексора, вторым входом второго элемента И и подключен к прямому

выходу первого триггера, вход установки в О которого соединен с выхс дом элемента ЗИ-ИЛИ,информационный

вход является шиной логическоГг 1, первый вход порогового элемента соединен с гшгходом коммутатора, а второй вход подключе.н к выходу цифроанало- гового преобразователя, входы которого соответственно объединены с информационными входами мультиплексора и подключены к соответствующим информационным выходам третьего счетчика, а управляющие входы мультиплексора соответственно объединены с входами младших разрядов адреса второго оперативного запоминающего устройства и подключены к соответствующим информационным выходам первого счетчика импульсов, счетный вход которого объединен с первым входом первого элемента И и соединен с выходом генератора импульсов, а второй вход первого элемента И подключен к прямому выходу третьего триггера и является шиной Начало вывода данных, управляющий вход регистра объединен с входом Чтение второго оперативного запоминающего устройства и соединен с выходом первого элемента И, а выход второго элемента И подключен к входу Запись второго запоминающего устройства, ин- формационный вход которого соединен с выходом мультиплексора, а выход под- подключен к информационному входу регистра и является второй выходной информационной шиной, выходы дешифратора соединены соответственно с управляющими входами коммутатора, информационные входы которого являются инфор- мационньгми входными шинами.

fl jnj lJlJlJlJn nJlJlJlJlJTJ4J rLn 6 JLJLJLJLJLJLJL 6I1IL r--TT

Г

1

-}

Редактор А. Ворович

Заказ 4055/56Типяж Qniтт

Подписное

ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектн1я Т

Составитель Ю. Спиридонов

Техред И,Попович Корректоре. Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Многоканальный преобразователь код-частота | 1985 |

|

SU1267621A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство контроля качества часовых механизмов | 1986 |

|

SU1332257A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Интегрирующий частотомер | 1985 |

|

SU1308921A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1363467A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах сопряжения цифровых вычислительных машин, обмена информацией, измерительных комплексах научных исследований и управления технологическими процессами. Целью изобретения является повышение надежности за счет упрощения устройства и расширение области применения за счет возможности получения выходных сигналов в последовательном коде. В устройство, содержащее генератор 1, счетчик 2 импульсов, регистр 8, триггер 11, цифроаналоговый преобразователь 14, пороговый элемент 22, элемент ИЛИ 23, введены два счетчика 3 и 4 импульсов, оперативные запоминающие устройства 5 и 6, мультиплексор 7, элементы И 9 и 10, триггеры 12 и 13, коммутатор 15, дешифратор 16, элемент 24 задержки, элементы 3 И-ИЛИ 25 и 2 И-ИЛИ 26. 3 ил. S (Л со со О5 ю со со

| Микроэлектронные цифроаналоговые и аналого-цифровые преобразователи информации./Под ред | |||

| В.Б | |||

| Смолова, л.: Энергия, 1976, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-07—Публикация

1985-06-05—Подача