Изобретение относится к измерительной технике и автоматике и может быть использовано в системах автоматического измерения и контроля, а также в измерительно-вычислительных комплексах на базе микроЭВМ.

Известен многоканальный измеритель временных интервалов (см. авторское свидетельство СССР №1213465 от 15.05.84 «Многоканальный измеритель временных интервалов», В.В.Будашов, В.А.Новичихин и О.В.Лебедев, опубликовано 23.02.86, Бюл. №7), содержащий счетчик времени, запоминающее устройство, регистр, n элементов И, элемент ИЛИ, дешифратор, счетчик адресов, коммутатор, генератор импульсов и многовходовый элемент И. Выходы запоминающего устройства соединены с входами регистра, а информационные входы - с выходами счетчика времени. S-входы RS-триггеров подключены к шинам стоп-импульсов соответствующих измерительных каналов, а R-входы объединены и подключены к шине «Запуск», R-входам счетчика времени и счетчика адресов и входу запуска генератора импульсов. Прямые выходы RS-триггеров подключены к входам многовходового элемента И, выход которого подключен к шине окончания измерения, а инверсные выходы RS-триггеров соединены с первыми входами соответствующих элементов И, вторые входы которых подключены к соответствующим выходам дешифратора и входам коммутатора, а выходы через элемент ИЛИ подключены к входу записи запоминающего устройства, адресные входы которого соединены с входами дешифратора и выходами счетчика адресов, счетный вход которого подключен к первому выходу генератора импульсов, второй выход которого подключен к счетному входу счетчика времени. Выход коммутатора соединен с управляющим входом регистра.

Недостатками данного устройства являются отсутствие возможности измерения длительности входных импульсов, возможности непрерывного многократного измерения временных интервалов в течение длительного времени и чувствительность к помехам, действующим на входах.

Наиболее близким по технической сущности к заявляемому устройству является многоканальный измеритель временных интервалов (см. авторское свидетельство СССР №1257601 от 25.12.84 «Многоканальный измеритель временных интервалов в сериях импульсов», Ю.А.Марков, В.Н.Титов, опубликовано 15.09.86, Бюл. №34), который выбран в качестве прототипа. Устройство содержит счетчик времени, два счетчика, коммутатор, запоминающее устройство, два RS-триггера, n триггеров приема информации, два элемента И и элемент ИЛИ. Информационные входы запоминающего устройства соединены с выходами счетчика времени. R-входы триггеров приема информации соединены с соответствующими входными шинами измерителя. S-входы триггеров приема информации объединены, соединены с S-входом первого RS-триггера, входом сброса счетчика времени, первым входом элемента ИЛИ и подключены к шине опорных импульсов. Выходы триггеров приема информации подключены к информационным входам коммутатора, выход которого соединен с первым входом первого элемента И. Второй вход элемента ИЛИ соединен со счетным входом счетчика времени и с шиной временных импульсов. R-вход первого RS-триггера соединен со счетным входом первого счетчика и подключен к выходу переноса счетчика времени. Прямой выход первого RS-триггера соединен с управляющим входом счетчика времени и с первым входом второго элемента И, второй вход которого подключен к прямому выходу второго RS-триггера, а выход - к входу выбора запоминающего устройства и входу разрешения записи второго счетчика. Счетный вход второго счетчика соединен с шиной тактовых импульсов и вторым входом первого элемента И, выход которого соединен с входом записи запоминающего устройства, первая группа адресных входов которого соединена с выходами первого счетчика. Вторая группа адресных входов запоминающего устройства соединена с адресными входами коммутатора и выходами второго счетчика, выход переполнения которого подключен к R-входу второго RS-триггера, S-вход которого соединен с выходом элемента ИЛИ.

Недостатком прототипа является отсутствие возможности измерения длительности входных импульсов. Необходимость непрерывного многократного измерения в течение длительного времени требует использования в данном устройстве запоминающего устройства большой емкости, что затрудняет реализацию измерителя на базе одной микросхемы ПЛИС. Информацию, накопленную в запоминающем устройстве, можно переслать в микроЭВМ только после завершения процесса измерения. При длительных процессах измерения (часы, сутки) это представляет собой неудобство, так как не позволяет отображать на дисплее микроЭВМ оперативную информацию о ходе и промежуточных результатах измерения. Кроме того, данное устройство чувствительно к помехам, действующим на входах.

Решаемой технической задачей является создание многоканального измерителя временных интервалов с расширенными функциональными возможностями.

Достигаемым техническим результатом являются возможность измерения длительности входных импульсов, возможность оперативной передачи информации в микроЭВМ в процессе измерения, что позволяет увеличивать время измерения без увеличения схемных затрат, и повышение помехоустойчивости.

Для достижения технического результата в многоканальном измерителе временных интервалов, содержащем триггеры приема информации, счетчик времени, счетный вход и вход сброса которого подключены к шине временных импульсов и к шине опорных импульсов, соответственно, а выходы подключены к первой группе информационных входов первого запоминающего устройства, адресные входы которого подключены к выходам первого счетчика, второй счетчик, вход которого подключен к шине тактовых импульсов, а выходы соединены с адресными входами коммутатора, информационные входы которого соединены с выходами соответствующих триггеров приема информации, первые входы которых соединены с соответствующими входными шинами, триггер, вход которого соединен с шиной опорных импульсов, новым является то, что дополнительно введены второе запоминающее устройство, блоки анализа информации и второй коммутатор, информационные входы которого подключены к первым выходам соответствующих блоков анализа информации, вторые выходы которых подключены к тактовым входам соответствующих триггеров приема информации, первые входы блоков анализа информации подключены к соответствующим входным шинам, вторые входы - к шине тактовых импульсов, третьи входы - к выходам соответствующих триггеров приема информации, а четвертые входы - к шине опорных импульсов, к входу сброса первого счетчика и к тактовому входу регистра, информационные входы которого подключены к адресным входам первого и второго запоминающих устройств, первые группы информационных входов которых объединены, а вторые группы объединены и подключены к выходам второго счетчика, выходу первого коммутатора и адресным входам второго коммутатора, выход которого подключен к счетному входу первого счетчика и входам разрешения первого и второго запоминающих устройств, входы записи которых подключены к шине тактовых импульсов, а управляющие входы - к прямому и инверсному выходам триггера, соответственно, при этом первое и второе запоминающие устройства выполнены в виде двухпортовых ОЗУ, триггер выполнен в виде счетного триггера, а каждый триггер приема информации выполнен в виде D-триггера, первый вход которого является информационным входом.

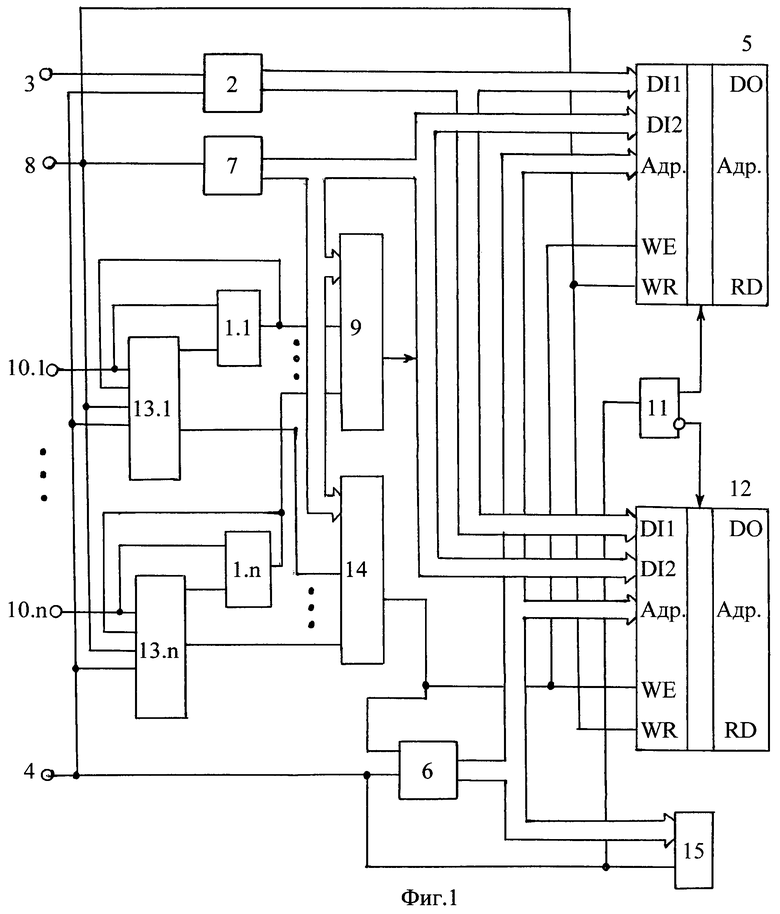

Блок анализа информации содержит реверсивный счетчик, счетчик событий, триггер, элемент ИЛИ-НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого является первым входом блока анализа информации и соединен с входом управления реверсом реверсивного счетчика, второй вход является третьим входом блока анализа информации, а выход соединен с управляющим входом реверсивного счетчика, первый вход элемента ИЛИ-НЕ является вторым входом блока анализа информации, второй вход соединен с выходом счетчика событий, а выход - со счетным входом реверсивного счетчика и входом сброса триггера, выход которого является первым выходом блока анализа информации и соединен со счетным входом счетчика событий, вход сброса которого является четвертым входом блока анализа информации и соединен с входом сброса реверсивного счетчика, выход переноса которого является вторым выходом блока анализа информации и соединен со счетным входом триггера.

Указанная совокупность признаков позволяет расширить функциональные возможности многоканального измерителя временных интервалов за счет введения блоков анализа информации, формирующих короткие импульсы, совпадающие с фронтом и срезом входного импульса, что позволило фиксировать не только время фронта, но и среза входных импульсов. При этом введение второго коммутатора позволило сохранить разрешающую способность измерителя на достигнутом в прототипе уровне. Введение второго запоминающего устройства и регистра и выполнение запоминающих устройств в виде двухпортовых ОЗУ позволило осуществлять оперативную передачу информации в микроЭВМ в процессе измерения и уменьшить объем памяти запоминающих устройств до уровня, необходимого для фиксации информации только в одном цикле измерения. Блок анализа информации обеспечивает помехоустойчивость измерителя путем стробирования триггеров приема информации только при превышении длительности входного импульса заданного порогового значения.

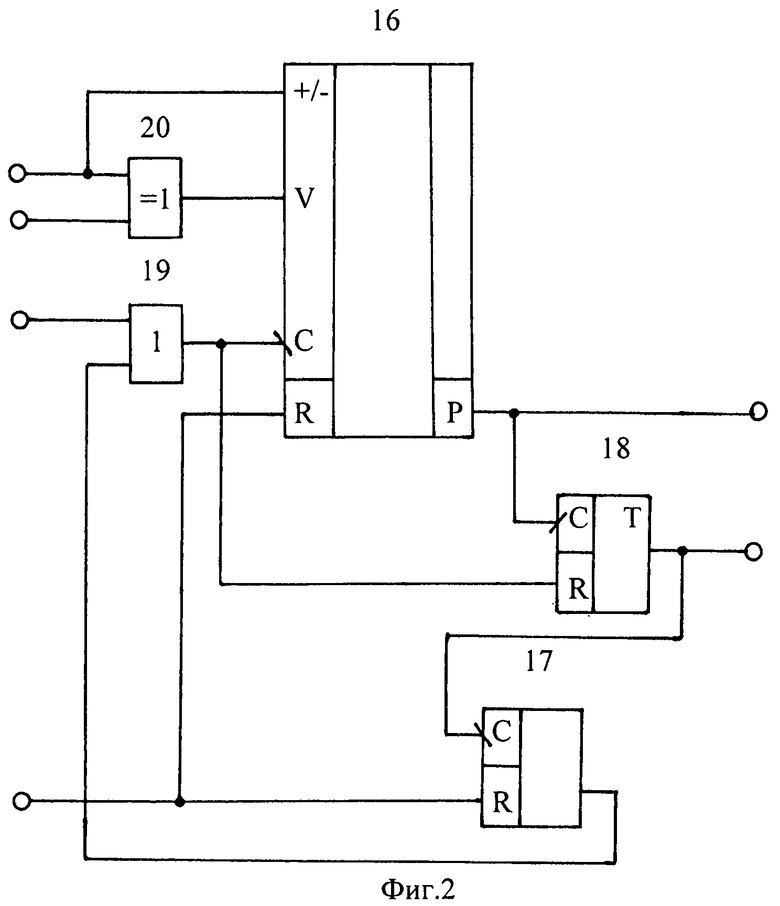

На Фиг.1 приведена схема многоканального измерителя временных интервалов. На Фиг.2 приведена схема блока анализа информации.

Многоканальный измеритель временных интервалов содержит триггеры 1.1…1.n приема информации, счетчик 2 времени, счетный вход и вход сброса которого подключены к шине 3 временных импульсов и к шине 4 опорных импульсов, соответственно, а выходы подключены к первой группе информационных входов первого запоминающего устройства 5, адресные входы которого подключены к выходам первого счетчика 6, второй счетчик 7, вход которого подключен к шине 8 тактовых импульсов, а выходы соединены с адресными входами первого коммутатора 9, информационные входы которого соединены с выходами соответствующих триггеров 1.1…1.n приема информации, первые входы которых соединены с соответствующими входными шинами 10.1…10.n, триггер 11, вход которого соединен с шиной 4 опорных импульсов. Введены второе запоминающее устройство 12, блоки 13.1…13.n анализа информации и второй коммутатор 14, информационные входы которого подключены к первым выходам соответствующих блоков 13.1…13.n анализа информации, вторые выходы которых подключены к тактовым входам соответствующих триггеров 1.1…1.n приема информации, первые входы блоков 13.1…13.n анализа информации подключены к соответствующим входным шинам 10.1…10.n, вторые входы - к шине 8 тактовых импульсов, третьи входы - к выходам соответствующих триггеров 1.1…1.n приема информации, а четвертые входы - к шине 4 опорных импульсов, к входу сброса первого счетчика 6 и к тактовому входу регистра 15, информационные входы которого подключены к адресным входам первого 5 и второго 12 запоминающих устройств, первые группы информационных входов которых объединены, а вторые группы объединены и подключены к выходам второго счетчика 7, выходу первого коммутатора 9 и адресным входам второго коммутатора 14, выход которого подключен к счетному входу первого счетчика 6 и входам разрешения первого 5 и второго 12 запоминающих устройств, входы записи которых подключены к шине 8 тактовых импульсов, а управляющие входы - к прямому и инверсному выходам триггера 11, соответственно. Первое 5 и второе 12 запоминающие устройства выполнены в виде двухпортовых ОЗУ. Порты, приведенные на Фиг.1 слева (DI1, DI2, Адр., WE, WR) являются портами записи, а порты чтения, приведенные справа (DO, Адр., RD), вместе с выходами регистра 15 и триггера 11 доступны для микроЭВМ. Триггер 11 выполнен в виде счетного триггера, вход которого является счетным входом, а каждый триггер 1.1…1.n приема информации выполнен в виде D-триггера, первый вход которого является информационным входом.

Каждый блок 13.1…13.n анализа информации содержит реверсивный счетчик 16 и счетчик 17 событий, триггер 18, элемент ИЛИ-НЕ 19 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, первый вход которого является первым входом блока анализа информации и соединен с входом управления реверсом реверсивного счетчика 16, второй вход является третьим входом блока анализа информации, а выход соединен с управляющим входом реверсивного счетчика 16, первый вход элемента ИЛИ-НЕ 19 является вторым входом блока анализа информации, второй вход соединен с выходом счетчика 17 событий, а выход - со счетным входом реверсивного счетчика 16 и входом сброса триггера 18, выход которого является первым выходом блока анализа информации и соединен со счетным входом счетчика 17 событий, вход сброса которого является четвертым входом блока анализа информации и соединен с входом сброса реверсивного счетчика 16, выход переноса которого является вторым выходом блока анализа информации и соединен со счетным входом триггера 18.

Многоканальный измеритель временных интервалов (Фиг.1, 2) работает следующим образом.

Так как запоминающие устройства 5 и 12 одинаковы, исходное состояние триггера 11 произвольное. Допустим, что исходным состоянием счетного триггера 11 является нулевое состояние. Первый опорный импульс сбрасывает в исходное состояние счетчик 2 времени, первый счетчик 6, все счетчики 16 и 17 блоков 13.1…13.n анализа информации и переключает в единичное состояние триггер 11. В этом состоянии триггер 11 устанавливает первое запоминающее устройство 5 в режим записи, а второе запоминающее устройство 12 - в режим чтения. Момент окончания первого опорного импульса является началом измерения временных интервалов и началом первого цикла измерения. Счетчик 2 времени начинает считать временные импульсы, а второй счетчик 7 - тактовые импульсы. Частота следования тактовых импульсов в n раз больше частоты временных импульсов. Таким образом, за интервал времени, расположенный между фронтами соседних временных импульсов, коммутатор 9 успевает опросить выходы всех триггеров 1.1…1.n приема информации, а коммутатор 14 - первые выходы всех блоков 13.1…13.n анализа информации. Если на любом из этих выходов в момент его опроса будет уровень логической «1», то на выходе коммутатора 14 сформируется импульс, который поступит на вход разрешения первого запоминающего устройства 5, и в него через первую группу информационных входов запишется код состояния счетчика 2 времени, а через вторую группу информационных входов - код состояния второго счетчика 7, который является номером информационного входа коммутатора 9, и информационный бит с выхода коммутатора 9. Данный бит несет в себе информацию о типе зарегистрированного события (логическая «1» - фронт входного импульса, логический «0» - срез входного импульса), а номер информационного входа коммутатора 9 - это номер входа 10.1…10.n измерителя, на который поступил данный входной импульс. Код состояния счетчика 2 времени несет в себе информацию о времени, прошедшем с начала цикла измерения до момента регистрации события. Информация о первом зарегистрированном событии будет записана по нулевому адресу запоминающего устройства 5, так как первый счетчик 6 находится в исходном (нулевом) состоянии. По срезу импульса на выходе коммутатора 14 первый счетчик 6 переключится в первое состояние, и информация о следующем зарегистрированном событии запишется в запоминающее устройство 5 по первому адресу и т.д. Таким образом, первый счетчик 6 является счетчиком событий, зарегистрированных за время текущего цикла измерения. В конце цикла измерения вторым опорным импульсом состояние этого счетчика записывается в регистр 15, сбрасываются в исходное состояние счетчик 2 времени, первый счетчик 6, все счетчики 16 и 17 блоков 13.1…13.n анализа информации и переключается в нулевое состояние триггер 11. В этом состоянии триггер 11 устанавливает первое запоминающее устройство 5 в режим чтения, а второе запоминающее устройство 12 - в режим записи.

Во втором цикле измерения устройство работает так же, как и в первом цикле, но информация записывается во второе запоминающее устройство 12. В это время микроЭВМ считывает состояние триггера 11 и определяет, что информацию нужно считывать с первого запоминающего устройства 5, считывает информацию с регистра 15 и определяет, сколько слов данных нужно считать начиная с нулевого адреса, и считывает эти данные, если состояние регистра 15 не нулевое. Если состояние регистра 15 нулевое, то это означает, что за время предыдущего цикла измерения не зарегистрировано ни одного события и считывать информацию с запоминающего устройства 5 нет необходимости. Таким образом, в канал общего пользования микроЭВМ с измерителя временных интервалов поступает необходимый минимум информации, что исключает засорение указанного канала лишней информацией и высвобождает для микроЭВМ время для работы с другими устройствами измерительного комплекса.

Емкость запоминающих устройств 5 и 12 выбирается исходя из ожидаемого максимального числа k событий, происходящих на каждом входе измерителя в течение одного цикла измерения, и разрядности счетчиков 2 и 7 с учетом бита на выходе коммутатора 9. Адресное пространство каждого запоминающего устройства простирается от 0 до k*n - 1, а емкость счетчиков 17 блоков 13.1…13.n выбирается равной k. При переполнении эти счетчики прекращают счет событий и блокируют дальнейшую работу блоков 13.1-13.n анализа информации. Это предотвращает забивание запоминающего устройства паразитной информацией при возникновении периодической помехи на одном из входов 10.1-10.n задолго до окончания цикла измерения и потерю полезной информации о событиях на остальных входах измерителя. Таким образом ресурс емкости запоминающего устройства распределяется между входами 10.1…10.n равномерно, что обеспечивает устойчивость измерителя к периодическим помехам на отдельных входах.

Помехи, длительность которых меньше заданного порогового значения, подавляются следующим образом. Так как входные каналы измерителя одинаковы, рассмотрим работу на примере первого канала. При отсутствии импульсов на первом входе блока анализа информации 13.1 присутствует уровень логического «0». Реверсивный счетчик 16 находится в режиме вычитания в нулевом состоянии, на его выходе переноса присутствует уровень логической «1». На выходе триггера 1.1 приема информации присутствует уровень логического «0», который по четвертому входу блока анализа информации 13.1 поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, с выхода которого уровень логического «0» поступает на управляющий вход счетчика 16, запрещая счет тактовых импульсов, присутствующих на его счетном входе. Счетчик 16 переходит в режим ожидания начала входного импульса. При появлении импульса на первом входе блока анализа информации 13.1 появятся уровни логической «1» на управляющем входе и входе управления реверсом счетчика 16, он перейдет в режим сложения и начнет подсчитывать тактовые импульсы, поступающие на счетный вход.

Если длительность входного импульса меньше заданного порогового значения, то к моменту окончания входного импульса счетчик 16 не успеет дойти до переполнения и импульс на его выходе переноса не появится. По окончании входного импульса счетчик 16 перейдет в режим вычитания и при отсутствии входных импульсов дойдет до режима ожидания начала входного импульса. Состояние триггера 1.1 приема информации не изменится и триггер 18 импульса на своем выходе не сформирует.

Если длительность входного импульса больше заданного порогового значения, то счетчик 16 дойдет до переполнения, по фронту импульса на выходе переноса счетчика 16 переключатся в единичное состояние триггер 1.1 приема информации и триггер 18. По окончании тактового импульса триггер 18 сбросится в нулевое состояние. Таким образом, данный триггер формирует импульс, свидетельствующий о появлении фронта входного импульса. При этом начало входного импульса, отфильтрованного от помех, появляется на выходе триггера 1.1 приема информации. С выхода триггера 1.1 приема информации уровень логической «1» поступает через третий вход блока анализа информации 13.1 на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19, с выхода которого уровень логического «0» поступает на вход управления счетчика 16, запрещая счет тактовых импульсов. Счетчик 16 переходит в режим ожидания конца входного импульса, то есть начала паузы между импульсами. При появлении паузы на первом входе блока анализа информации 13.1 появятся уровень логической «1» на управляющем входе и уровень логического «0» на входе управления реверсом счетчика 16, он перейдет в режим вычитания и начнет подсчитывать тактовые импульсы методом обратного отсчета.

Если длительность паузы меньше заданного порогового значения, то к моменту окончания паузы счетчик 16 не успеет дойти до нулевого состояния и импульс на его выходе переноса не появится. По окончании паузы счетчик 16 перейдет в режим сложения и при отсутствии последующих пауз дойдет до режима ожидания конца входного импульса (начала паузы). Состояние триггера 1.1 приема информации не изменится и триггер 18 импульса на своем выходе не сформирует.

Если длительность паузы больше заданного порогового значения, то счетчик 16 дойдет до нулевого состояния, по фронту импульса на выходе переноса счетчика 16 триггер 1.1 приема информации переключится в нулевое состояние, а триггер 18 - в единичное состояние. По окончании тактового импульса триггер 18 сбросится в нулевое состояние. Таким образом, данный триггер формирует импульс, свидетельствующий о появлении среза входного импульса. При этом на выходе триггера 1.1 приема информации появляется окончание входного импульса, отфильтрованного от помех.

Счет циклов измерения микроЭВМ осуществляет программно. Поэтому в отличие от прототипа время измерения не ограничено аппаратными возможностями. Также программно вычисляется длительность входных импульсов путем вычитания времени поступления фронта импульса из времени поступления его среза.

Проведено макетирование 32-канального измерителя временных интервалов на макетной плате с микросхемой АРА075 фирмы Actel. Испытания макета измерителя подтвердили работоспособность заявляемого устройства и его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2010 |

|

RU2429515C1 |

| Многоканальный измеритель интервалов времени | 1989 |

|

SU1651686A1 |

| Многоканальный измеритель временных интервалов в сериях импульсов | 1984 |

|

SU1257601A1 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Делитель частоты следования импульсов с регулируемым коэффициентом деления | 1987 |

|

SU1517130A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345204C2 |

Изобретение относится к измерительной технике и автоматике и направлено на обеспечение возможности измерения длительности входных импульсов, подавления помех, действующих на входах измерителя, и возможности оперативной передачи информации в микроЭВМ в процессе измерения, что позволяет увеличивать время измерения без увеличения схемных затрат. Этот результат обеспечивается за счет того, что многоканальный измеритель временных интервалов содержит триггеры приема информации, счетчик времени, счетный вход и вход сброса которого подключены к шине временных импульсов и к шине опорных импульсов, соответственно, а выходы подключены к первой группе информационных входов первого запоминающего устройства, адресные входы которого подключены к выходам первого счетчика, второй счетчик, вход которого подключен к шине тактовых импульсов, а выходы соединены с адресными входами первого коммутатора, информационные входы которого соединены с выходами соответствующих триггеров приема информации, первые входы которых соединены с соответствующими входными шинами, триггер, вход которого соединен с шиной опорных импульсов. При этом, согласно изобретению, дополнительно введены второе запоминающее устройство, блоки анализа информации и второй коммутатор, информационные входы которого подключены к первым выходам соответствующих блоков анализа информации, вторые выходы которых подключены к тактовым входам соответствующих триггеров приема информации, первые входы блоков анализа информации подключены к соответствующим входным шинам, соответствующих триггеров приема информации, первые входы блоков анализа информации подключены к соответствующим входным шинам, вторые входы - к шине тактовых импульсов, третьи входы - к выходам соответствующих триггеров приема информации, а четвертые входы - к шине опорных импульсов, к входу сброса первого счетчика и к тактовому входу регистра, информационные входы которого подключены к адресным входам первого и второго запоминающих устройств, первые группы информационных входов которых объединены, а вторые группы объединены и подключены к выходам второго счетчика, выходу первого коммутатора и адресным входам второго коммутатора, выход которого подключен к счетному входу первого счетчика и входам разрешения первого и второго запоминающих устройств, входы записи которых подключены к шине тактовых импульсов, а управляющие входы - к прямому и инверсному выходам триггера, соответственно, при этом первое и второе запоминающие устройства выполнены в виде двухпортовых ОЗУ, триггер выполнен в виде счетного триггера, а каждый триггер приема информации выполнен в виде D-триггера, первый вход которого является информационным входом. 2 ил.

Многоканальный измеритель временных интервалов, содержащий триггеры приема информации, счетчик времени, счетный вход и вход сброса которого подключены к шине временных импульсов и к шине опорных импульсов, соответственно, а выходы подключены к первой группе информационных входов первого запоминающего устройства, адресные входы которого подключены к выходам первого счетчика, второй счетчик, вход которого подключен к шине тактовых импульсов, а выходы соединены с адресными входами первого коммутатора, информационные входы которого соединены с выходами соответствующих триггеров приема информации, первые входы которых соединены с соответствующими входными шинами, триггер, вход которого соединен с шиной опорных импульсов, отличающийся тем, что дополнительно введены второе запоминающее устройство, блоки анализа информации и второй коммутатор, информационные входы которого подключены к первым выходам соответствующих блоков анализа информации, вторые выходы которых подключены к тактовым входам соответствующих триггеров приема информации, первые входы блоков анализа информации подключены к соответствующим входным шинам, вторые входы - к шине тактовых импульсов, третьи входы - к выходам соответствующих триггеров приема информации, а четвертые входы - к шине опорных импульсов, к входу сброса первого счетчика и к тактовому входу регистра, информационные входы которого подключены к адресным входам первого и второго запоминающих устройств, первые группы информационных входов которых объединены, а вторые группы объединены и подключены к выходам второго счетчика, выходу первого коммутатора и адресным входам второго коммутатора, выход которого подключен к счетному входу первого счетчика и входам разрешения первого и второго запоминающих устройств, входы записи которых подключены к шине тактовых импульсов, а управляющие входы - к прямому и инверсному выходам триггера, соответственно, при этом первое и второе запоминающие устройства выполнены в виде двухпортовых ОЗУ, триггер выполнен в виде счетного триггера, а каждый триггер приема информации выполнен в виде D-триггера, первый вход которого является информационным входом.

| Многоканальный измеритель временных интервалов в сериях импульсов | 1984 |

|

SU1257601A1 |

| Многоканальный измеритель временных интервалов | 1984 |

|

SU1213465A1 |

| ИЗМЕРИТЕЛЬ ИНТЕРВАЛОВ ВРЕМЕНИ | 2008 |

|

RU2379824C1 |

| Устройство и способ устранения колебаний оптического разряда | 2020 |

|

RU2738461C1 |

Авторы

Даты

2012-07-10—Публикация

2011-02-14—Подача