Предлагаемое изобретение относится к области электронной вычислительной техники, в частности к технике цифровой фильтрации, и может быть использовано при разработке цифровых фильтров в дискретных (релейных) системах.

Известен способ цифровой фильтрации сигналов [1], основанный на преобразовании входного сигнала X в цифровую форму, формировании разности ΔXi(I=1, 2, 3….) входного и выходного сигналов и формировании выходного сигнала

Недостаток этого способа состоит в низком быстродействии и низкой помехоустойчивости. В дискретных (релейных) системах входной сигнал X принимает значения «0» (низкий уровень) и «1» (высокий уровень). Так, при реализации известного способа установка начального значения выходного сигнала

Известен цифровой фильтр [1], содержащий аналого-цифровой преобразователь, генератор, цифровой компаратор, реверсивный счетчик, элементы И и ИЛИ.

Недостаток этого фильтра состоит в низком быстродействии и низкой помехоустойчивости.

Наиболее близким способом цифровой фильтрации дискретного сигнала к предлагаемому является способ [2], основанный на преобразовании входного сигнала X в дискретный сигнал, формировании начального значения выходного сигнала

Недостаток этого способа состоит в низком быстродействии и низкой помехоустойчивости. Несмотря на то что этот способ позволяет практически без запаздывания устанавливать начальное значение, быстродействие при формировании выходного сигнала при изменении входного сигнала остается низким, вследствие чего теряется помехозащищенность.

Наиболее близким техническим решением к предлагаемому цифровому фильтру является устройство [2], содержащее аналого-цифровой преобразователь, первый и второй генераторы, цифровой компаратор, первый и второй реверсивные счетчики, элементы И и ИЛИ.

Недостаток этого цифрового фильтра состоит в низком быстродействии и низкой помехоустойчивости.

Задача изобретения - повышение быстродействия и помехоустойчивости.

Эта задача достигается тем, что в способе цифровой фильтрации дискретного сигнала, включающем формирование дискретного сигнала Р, принимающего значения «0» или «1», дополнительно формируют цифровой сигнал В путем суммирования импульсов заданного периода при значении промежуточного дискретного сигнала Р=1 и путем вычитания этих же импульсов при значении промежуточного дискретного сигнала Р=0, и формируют выходной сигнал D в виде

D=1, при В=А1 и в течение времени при В≠A2,

D=0, при В=A2 и в течение времени при В≠A1,

где A1 и A2 - заданные значения, определяемые максимально возможным интервалом, в котором состояние входного сигнала однозначно не определено, и ограничивающие интервал изменения цифрового сигнала В.

В цифровой фильтр, содержащий шину входного сигнала, генератор, первый и второй элементы И, триггер, элемент ИЛИ, инвертор, реверсивный счетчик и первый цифровой компаратор, при этом выход генератора соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход элемента ИЛИ соединен с входом С реверсивного счетчика, выходная шина которого соединена с входной шиной В первого цифрового компаратора, дополнительно введены второй цифровой компаратор, задатчик сигналов ограничения A1 и A2, второй и третий инверторы, источник опорного напряжения и резистор, первый вывод которого соединен с нулевой шиной источника опорного напряжения, второй вывод резистора соединен с шиной входного сигнала, входом первого инвертора, первым входом второго элемента И и входом «+/-» реверсивного счетчика, выходная шина которого соединена с входной шиной В второго цифрового компаратора, выходные шины задатчика сигналов ограничения A1 и A2 соединены соответственно с шиной A1 первого цифрового компаратора и с шиной A2 второго цифрового компаратора, выход которого В=A2 соединен с входом третьего инвертора и входом S триггера, вход R которого соединен с выходом В = первого цифрового компаратора и входом второго инвертора, выходы второго и третьего инверторов соединены со вторыми входами первого и второго элементов И соответственно, третьи входы которых соединены соответственно с выходом первого инвертора и выходом генератора, при этом выход триггера подключен к шине выходного сигнала.

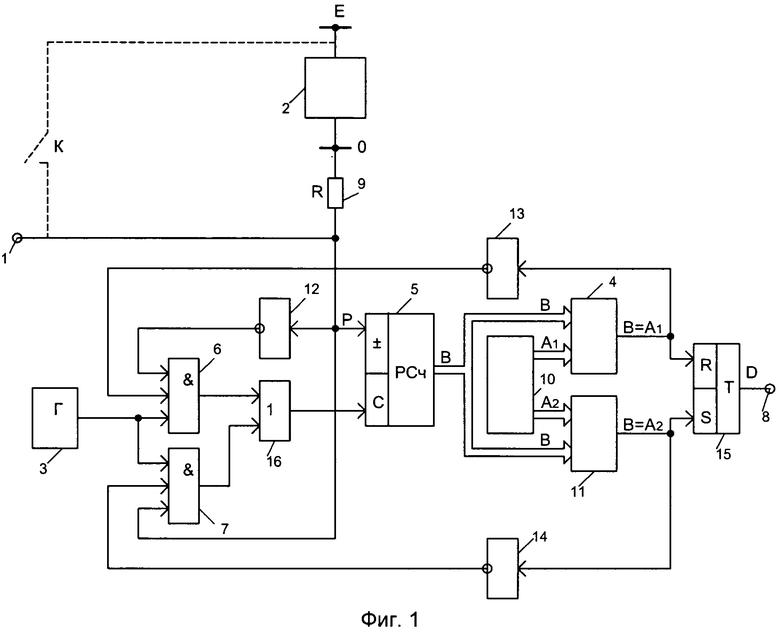

На фиг 1 представлена блок-схема цифрового фильтра, реализующего предлагаемый способ фильтрации дискретного сигнала. На этой схеме 1 - шина входного сигнала, 2 - источник опорного напряжения, 3 - генератор, 4 - первый цифровой компаратор, 5 - реверсивный счетчик, 6 - первый элемент И, 7 - второй элемент И, 8 - шина выходного сигнала, 9 - резистор, 10 - задатчик сигналов ограничения A1 и A2, 11 - второй компаратор, 12, 13 и 14 - соответственно первый, второй и третий инверторы, 15 - триггер, 16 - элемент ИЛИ.

В цифровом фильтре шина входного сигнала 1 соединена со вторым выводом резистора 9, первым входом второго элемента И 7, входом C «+/-» реверсивного счетчика 5 и входом первого инвертора 12. Первый вывод резистора 9 соединен с нулевой шиной источника опорного напряжения 2. Выход генератора 3 соединен с первым входом первого элемента И 6 и третьим входом второго элемента И 7. Вторые входы первого 6 и второго 7 элементов И соединены соответственно с выходом второго 13 и выходом третьего 14 инверторов. Выход первого инвертора 12 соединен с третьим входом первого элемента И 6. Выходы первого 6 и второго 7 элементов И соединены соответственно с первым и вторым входами элемента ИЛИ 16, выход которого соединен с входом С реверсивного счетчика 5, выходная шина которого соединена с входной шиной В первого 4 и второго 11 цифровых компараторов. Входная шина A1 первого цифрового компаратора 4 и входная шина A2 второго цифрового компаратора 11 соединены с соответствующими выходными шинами задатчика сигналов ограничения A1 и A2 10. Выход В=A1 первого цифрового компаратора 4 соединен с входом второго инвертора 13 и входом R триггера 15, выход В=A2 второго цифрового компаратора 11 соединен с входом третьего инвертора 14 и входом S триггера 15, выход которого соединен с шиной выходного сигнала 8.

Цифровой фильтр работает следующим образом. Пусть реверсивный счетчик 5 имеет пять разрядов, а сигналы ограничения A1 и A2 задатчика сигналов ограничения 10 выбраны следующими: A1=00000, A2=01111. Пусть также в начальный момент состояние реверсивного счетчика 5 В=00000 и входной сигнал на шине 1 Р=0 (предполагаем, что входной сигнал формируется в системе управления замыканием /размыканием контакта К, на фиг.1 показан условно пунктиром для простоты пояснения работы схемы). Предположим, что во время функционирования контакт К имеет неопределенное состояние (например, за счет «дребезга») в течение интервала ΔT=0,015 с. Если период следования импульсов с генератора 3 выбран равным τ=0,001 с, то сигналы ограничения A1 и A2 выбираются из условия А2-A1=ΔT/τ=15 (сигналы A1 и A2 задаются в двоичном коде). При Р=0 на выходе первого цифрового компаратора 4 формируется сигнал B=A1=1, который устанавливает триггер 15 по входу R в нулевое состояние и выходной сигнал триггера 15 D=0. Кроме того, сигнал B=A1=1 поступает на вход второго инвертора 13 и его выходной сигнал, равный «0», блокирует прохождение сигналов с выхода генератора 3 на первый вход элемента ИЛИ 16 через второй элемент И 7, в результате чего состояние реверсивного счетчика 5 не изменятся. На его выходной шине присутствует сигнал В=00000. В этом состоянии схема фиг.1 будет находиться до тех пор, пока не изменится состояние входного контакта К.

Пусть в некоторый момент времени происходит замыкание контакта К. В этом случае на входной шине 1 формируется сигнал Р=1 (образуется сигнал высокого уровня Е, например, 5В). Сигнал Р=1 поступает на вход первого инвертора 12 и его выходной сигнал, равный «0», блокирует работу первого элемента И 6. Сигнал Р=1 поступает также на первый вход второго элемента И 7, разрешая прохождение сигналов с выхода генератора 3 на вход С реверсивного счетчика 5, в результате чего его состояние В начинает изменяться. Так как B≠A2, то на выходе второго компаратора 11 сформирован сигнал, равный «0», и на выходе третьего инвертора 14 образован сигнал, равный «1», который также разрешает прохождение сигналов с выхода генератора 3 через второй элемент И 7 на вход С реверсивного счетчика 5. Считаем, что при Р=1 реверсивный счетчик 5 устанавливается в режим «сложение» импульсов, а при Р=0 реверсивный счетчик импульсов 5 устанавливается в режим «вычитание» импульсов.

При Р=1 реверсивный счетчик импульсов 5 начинает суммировать импульсы с генератора 3 до тех пор, пока на его выходе не установится состояние В=01111. В этом случае на выходе второго компаратора 11 формируется сигнал В=А2=1, который поступает на вход S триггера 15, устанавливая его в единичное состояние, в результате выходной сигнал триггера 15 D=1. Одновременно сигнал В=А2=1 поступает на вход третьего инвертора 14 и его выходной сигнал, равный «0», блокирует прохождение сигналов с генератора 3 через второй элемент И 7 на вход С реверсивного счетчика 5, который будет оставаться в состоянии В=А2=1 до тех пор, пока не изменится состояние контакта К. Если при переходе контакта К из состояния «разомкнут» в состояние «замкнут» дискретный сигнал Р=1 формируется в течение всего времени, не прерываясь, то время ΔT, по истечению которого появляется выходной сигнал D=1, будет определяться значением 15 τ, где число 15 определяет количество импульсов с генератора 3 для изменения состояния реверсивного счетчика 5 из состояния В=00000 в состояние В=01111.

Если, например, при замыкании контакта К возникает «дребезг», то формирование выходного сигнала D будет осуществляться следующим образом. Пусть при замыкании контакта К из-за «дребезга» дискретный сигнал Р представляет собой последовательность значений Pi(i=1, 2, 3…), принимающих значение 0 или 1. Пусть, например, P1=P3=P5=P7=P9=1, при этом длительность каждого сигнала для простоты равна τ1=0,75 мс, P2=P4=P6=P8=0, при этом длительность каждого сигнала τ0=1,25 мс. Пусть также время t1 первого поступления импульса с генератора 3 на интервале, когда P1=1, равно 0,5 мс (отсчитывается от начала импульса P1=1). Если период следования импульсов с генератора 3 τ=1 мс, то моменты поступления импульсов с генератора 3 ti=0,5+i τ. Значения сигнала Pti в эти моменты времени будут равны: Pt1=Pt3=Pt5=Pt7=Pt9=1, Pt2=Pt4=Pt6=Pt8=0.

В течение времени «дребезга» контакта К состояние реверсивного счетчика 5 будет изменяться следующим образом. В момент времени t1 при Pt1=1 реверсивный счетчик 5 произведет суммирование одного импульса, так как Р=1 и B≠A2, и его состояние станет равным В=00001. В момент времени t2 Pt2=0. Так как в этот момент времени B≠A1, Р=0, то реверсивный счетчик 5 осуществит вычитание одного импульса и его состояние В=00000. Выходной сигнал D не изменит своего состояния, так как B≠A2 и сигнал на входе S триггера 15 равен 0. Далее процесс будет повторяться. В момент времени t3 состояние реверсивного счетчика 5 станет В=00001 и далее оно будет изменяться, переходя из состояния В=00000 в состояние В=00001 в течение времени «дребезга». В момент времени t9 «дребезг» заканчивается, сигнал Р становится устойчиво равным 1 и состояние реверсивного счетчика 5 будет последовательно изменяться от состояния В=00001 до состояния В=01111. В этот момент времени выходной сигнал второго цифрового компаратора 11 В=А2=1 и этот сигнал переводит триггер 15 в единичное состояние, в результате выходной сигнал D=1.

Если предположить, что «дребезг» контакта К происходит таким образом, что во все моменты времени ti значения сигнала Pti в эти моменты времени будут равны 1, то выходной сигнал D=1 появляется по истечение времени ΔT=15 мс, т.е. по окончании «дребезга».

Рассмотренная схема производит фильтрацию входного сигнала, оставляя неизменным выходной сигнал D в течение всего времени действия «дребезга» (помехи) входного сигнала. Лишь после окончания «дребезга» по истечении времени ≤15 мс формируется полезный выходной сигнал D=1. С учетом времени действия сигнала помехи («дребезга») время переходного процесса ΔT=9 мс (время «дребезга») + 15 мс ≤ 24 мс.

В качестве элементов для реализации цифрового фильтра можно использовать, цифровой компаратор типа 564 ИП2, реверсивный счетчик, триггер, инверторы, элементы И и ИЛИ серии 564. В качестве задатчика сигналов ограничения может быть использован регистр заданного числа.

В процессе функционирования возможно многократное кратковременное замыкание или размыкание входного контакта К (например, при движении контакта по ламели). Длительность ложного замыкания или размыкания контакта К обычно не превышает 10 мс. Как следует из приведенного описания, цифровой фильтр не реагирует на ложные изменения дискретного сигнала Р. Таким образом, предлагаемый цифровой фильтр осуществляет фильтрацию дискретного сигнала и имеет время переходного процесса ΔT≤24 мс.

В известном цифровом фильтре [2] при появлении на входе сигнала помехи выходной сигнал начинает изменяться. В предлагаемом цифровом фильтре сигнал помехи не приводит к изменению выходного сигнала. При изменении входного полезного сигнала из одного состояния в другое в предлагаемом цифровом фильтре изменение выходного сигнала D происходит с некоторым запаздыванием, но мгновенно. В известном цифровом фильтре при изменении входного полезного сигнала из одного состояния в другое выходной сигнал начинает изменяться линейно, от минимального значения до максимального (или наоборот) в течение времени переходного процесса ΔT=0,5 с (предполагается, что минимальное значение выходного сигнала равно 0, максимальное значение равно 5 В, Δ=0,01В, τ=0,001 с). Если предположить, что дискретному выходному сигналу, равному 0, соответствует выходное напряжение UВЫХ<1,2В, дискретному сигналу, равному 1, соответствует выходное напряжение UВЫХ>3,5В, то в интервале 1,2В<UВЫХ<3,5В дискретный выходной сигнал, формируемый приемным устройством системы, использующей известный цифровой фильтр, принимает неопределенное значение «0» или «1». Неопределенное формирование полезного выходного сигнала в указанном интервале выходного напряжения известного цифрового фильтра указывает на его недостаточную помехозащищенность.

Таким образом, предлагаемый авторами цифровой фильтр снижает время переходного процесса (24 мс вместо 500 мс в известном цифровом фильтре), увеличивая быстродействие, и повышает помехозащищенность.

Предлагаемая совокупность признаков в рассмотренных авторами решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям «новизна» и «изобретательский уровень».

Литература

1. Патент Российской Федерации №2188499, МПК7 H03H 17/02, 2002 г.

2. Патент Российской Федерации №2187883, МПК7 H03H 17/02, 2002 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЦИФРОВОЙ ФИЛЬТРАЦИИ СИГНАЛОВ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2000 |

|

RU2187883C2 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2477887C1 |

| Следящий аналого-цифровой преобразователь | 1990 |

|

SU1757101A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ГАРМОНИЧЕСКИХ ИСКАЖЕНИЙ (ВАРИАНТЫ) | 2003 |

|

RU2247996C2 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2455682C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2451328C1 |

Изобретение относится к области вычислительной техники, к технике цифровой фильтрации и может быть использовано при разработке цифровых фильтров в дискретных системах. Достигаемый технический результат - повышение быстродействия и помехоустойчивости. Способ цифровой фильтрации основан на формировании дискретного сигнала Р, принимающего значения «0» или «1», формировании цифрового сигнала В путем суммирования импульсов заданного периода при значении дискретного сигнала P=1 и путем вычитания этих же импульсов при значении дискретного сигнала P=0, и формировании выходного сигнала D в виде D=1, при B=A1 и в течение времени при В≠А2, D=0, при B=А2 и в течение времени при B≠A1,

где А1 и А2 - заданные значения, определяемые максимально возможным интервалом, в котором состояние входного сигнала однозначно не определено, и ограничивающие интервал изменения цифрового сигнала В. Цифровой фильтр содержит генератор, реверсивный счетчик, два цифровых компаратора, задатчик сигналов ограничения A1 и A2, триггер, инверторы, элементы И и ИЛИ. 2 н.п. ф-лы, 1 ил.

1. Способ цифровой фильтрации дискретного сигнала, включающий формирование дискретного сигнала Р, принимающего значения «0» или «1», отличающийся тем, что дополнительно формируют цифровой сигнал В путем суммирования импульсов заданного периода при значении дискретного сигнала Р=1 и путем вычитания этих же импульсов при значении дискретного сигнала Р=0, и выходной сигнал D формируют в виде

D=1, при B=A1 и в течение времени при В≠А2,

D=0, при B=А2 и в течение времени при B≠A1,

где A1 и A2 - заданные значения, определяемые максимально возможным интервалом, в котором состояние входного сигнала однозначно не определено, и ограничивающие интервал изменения цифрового сигнала В.

2. Цифровой фильтр, содержащий шину входного сигнала, генератор, первый и второй элементы И, триггер, элемент ИЛИ, инвертор, реверсивный счетчик и первый цифровой компаратор, при этом выход генератора соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход элемента ИЛИ соединен с входом С реверсивного счетчика, выходная шина которого соединена с входной шиной В первого цифрового компаратора, отличающийся тем, что в него дополнительно введены второй цифровой компаратор, задатчик сигналов ограничения A1 и A2, второй и третий инверторы, источник опорного напряжения и резистор, первый вывод которого соединен с нулевой шиной источника опорного напряжения, второй вывод резистора соединен с шиной входного сигнала, входом первого инвертора, первым входом второго элемента И и входом «+/-» реверсивного счетчика, выходная шина которого соединена с входной шиной В второго цифрового компаратора, выходные шины задатчика сигналов ограничения A1 и A2 соединены соответственно с шиной A1 первого цифрового компаратора и с шиной A2 второго цифрового компаратора, выход которого B=A2 соединен с входом третьего инвертора и входом S триггера, вход R которого соединен с выходом B=A1 первого цифрового компаратора и входом второго инвертора, выходы второго и третьего инверторов соединены со вторыми входами первого и второго элементов И соответственно, третьи входы которых соединены соответственно с выходом первого инвертора и выходом генератора, при этом выход триггера подключен к шине выходного сигнала.

| СПОСОБ ЦИФРОВОЙ ФИЛЬТРАЦИИ СИГНАЛОВ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2000 |

|

RU2187883C2 |

| СПОСОБ ЦИФРОВОЙ ФИЛЬТРАЦИИ СИГНАЛОВ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2000 |

|

RU2188499C2 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1990 |

|

RU2022485C1 |

Авторы

Даты

2015-08-10—Публикация

2013-12-10—Подача