Настоящее изобретение относится к способу, с помощью которого обнаруживают попытку атаки на процессор безопасности с помощью непосредственно процессора безопасности. Задачей настоящего изобретения является также выполнение носителя записи информации, а также процессора безопасности для осуществления этого способа.

Процессоры безопасности представляют собой обычно компоненты аппаратных средств, содержащие конфиденциальную информацию, такую как криптографические ключи или права доступа, которые могут использовать только легальные пользователи. Для сохранения конфиденциальности этой информации, эти процессоры разрабатывают по возможности устойчивыми к попыткам атак компьютерных хакеров. Например, процессор безопасности представляет собой чип-карту, снабженную электронным процессором.

Процессоры безопасности подвергаются различным типам атаки. Некоторые из этих атак нацелены на извлечение или определение конфиденциальной информации, содержащейся в процессоре безопасности. С этой целью предпринимается большое количество атак. Например, некоторые из этих атак предпринимаются для достижения ненормального функционирования процессора безопасности, заставляя его обрабатывать сообщения, создаваемых компьютерными хакерами. В других более грубых способах пытаются нарушить функционирование процессора безопасности в ключевые моменты его работы путем использования его напряжения питания или посредством направления лазерного луча на процессор безопасности.

Другие типы атаки, в которых не пытаются извлечь или определить конфиденциальную информацию, которая содержится в процессоре безопасности, заключаются в том, чтобы избыточно загрузить процессор безопасности. Например, в области платного телевидения совместное использование контрольных слов или совместное использование карты подвергается этому типу атаки. Вкратце, совместное использование контрольных слов состоит из совместного использования контрольного слова, дешифрированного с помощью процессора безопасности, между несколькими приемниками. Эти приемники могут затем дешифрировать скремблированные мультимедийные контенты с помощью этого контрольного слова, тогда как подписка была оплачена только для одного приемника.

При совместном использовании карты один и тот же процессор безопасности производит дешифрирование нескольких зашифрованных контрольных слов, поступающих из различных приемников. Как упомянуто выше, все эти приемники могут затем дескремблировать скремблированные мультимедийные контенты, тогда как только один из этих приемников имеет доступ к контенту.

Для противодействия этим атакам известны способы обнаружения попыток атак, и, в ответ на это обнаружение, выполнения контрмер.

Один пример способа обнаружения попыток атак и выполнения ответных контрмер описан, например, в заявке на патент ЕР 1575293.

Контрмерой является действие, нацеленное на предотвращение атаки на процессор безопасности, которое является продолжительным или успешным. Существует большое количество контрмер, которые может выполнить процессор безопасности. Эти меры простираются от простого увеличения мер безопасности в процессоре безопасности, вплоть до окончательной и неустранимой блокировки процессора безопасности, который затем становится неиспользуемым.

Ранее были предложены способы обнаружения попытки атаки. Эти способы содержат этапы, на которых:

- измеряют несколько различных событий, происходящих независимо друг от друга в отсутствие попыток атак, затем

- сравнивают каждое измерение с заданным соответствующим порогом для обнаружения наличия или отсутствия попытки атаки.

Однако затруднение возникает из-за того факта, что события, представляющие попытку атаки, могут также происходить в случае, когда отсутствует попытка атаки. В настоящее время, необходимо предотвратить выработку ложных обнаружений попыток атак, так как они могут привести в результате к несвоевременному принятию контрмер, которые также причиняют неудобства легальному пользователю процессора безопасности. По этой причине, существуют известные способы выбора гораздо более высокого значения для заданного порога, чем значения всех измерений, которые можно получить при отсутствии атак. Однако выбор высокого заданного порога делает некоторые атаки необнаруживаемыми или замедляет обнаружение попытки атаки.

Для устранения этого недостатка в настоящем изобретении предложен способ обнаружения попытки атаки, который также содержит этапы, на которых:

- создают значение, по меньшей мере, одного показателя атаки в зависимости по меньшей мере от одного индекса отношения между по меньшей мере двумя различными измеренными событиями, причем индекс отношения между событиями представляет собой временную близость между двумя различными измеренными событиями; и

- обнаруживают попытку атаки, если значение показателя атаки превышает заданный порог.

Вышеупомянутый способ учитывает временную близость между различными событиями, происходящими в процессоре безопасности. Это позволяет выполнить более быстро обнаружение попытки атаки или обнаружение попытки атаки, которую нельзя было обнаружить путем наблюдения измерения одного события. В действительности может случиться, что измерение каждого из этих событий, взятых по отдельности, не создает быстрого представления о попытке атаки, поскольку эти события происходят во время нормальной работы процессора безопасности. Напротив, когда эти события происходят почти совместно, тогда как они должны происходить нормальным образом независимо друг от друга, можно принять во внимание с высокой степенью достоверности, что попытка атаки имела место. Поэтому вышеописанный способ позволяет процессору безопасности выполнить быстрое обнаружение с высокой степенью достоверности обнаружения того факта, что он стал жертвой от попытки атаки. Выполнение соответствующих контрмер можно затем активизировать с большей скоростью.

Варианты осуществления этого способа могут содержать один или более следующих характеристик:

- значение показателя атаки создается из множества индексов отношения между различными измеряемыми событиями и путем взвешивания значимости этих индексов отношения между событиями относительно друг друга посредством заданного набора коэффициентов взвешивания;

- способ содержит этап, на котором создают множество значений показателя атаки путем использования множества наборов коэффициентов взвешивания между одинаковыми индексами отношения между событиями, причем каждый набор коэффициентов взвешивания задается так, чтобы он был чувствительным к попытке атаки, которая отличается от попыток атак, к которым другие показатели являются более чувствительными;

- коэффициент взвешивания одинакового индекса отношения между событиями является одинаковым во всех наборах коэффициентов взвешивания, который используется для создания различных значений показателя атаки;

- измерение события ограничено скользящим интервалом времени для того, чтобы не учитывать события, которые произошли вне этого интервала времени, причем это делается для того, чтобы установить факт того, что эти события являются сопутствующими при измерении этого интервала времени;

- по меньшей мере одно из измеренных событий представляет собой обнаружение ошибки при функционировании процессора безопасности, причем каждый случай приводит к тому, что процессор безопасности останавливает операции обработки, выполняемые в текущий момент времени, и автоматически производит сброс для возобновления этих операций с начала;

- измерение события заключается в подсчете с помощью счетчика, сколько раз произошло это событие, причем значение счетчика составляет результат измерения;

- индекс отношения по меньше мере между двумя измерениями получается путем перемножения результатов измерений друг на друга.

Эти варианты осуществления этого способа дополнительно имеют следующие преимущества:

- использование коэффициентов взвешивания для индексов отношения между событиями просто модифицирует чувствительность показателя атаки, созданного для конкретного типа атаки путем модификации значения этих коэффициентов взвешивания,

- использование нескольких различных наборов коэффициентов взвешивания позволяет при использовании одинакового набора индексов отношения между событиями создать несколько индикаторов атак, каждый из которых выделен для обнаружения другой попытки атаки,

- систематическое использование одинакового коэффициента взвешивания для одинакового индекса отношения между событиями ограничивает размер памяти, который требуется для хранения различных коэффициентов взвешивания,

- ограничение измерения события скользящим интервалом времени ограничивает число ложных обнаружений попыток атак, вызванных накоплением во времени измеренных событий при отсутствии попыток атак,

- когда одно из измеренных событий представляет собой обнаружение ошибки процессора безопасности, которая приводит к сбросу этого процессора безопасности, то безопасность повышают путем предотвращения несвоевременной блокировки этого процессора безопасности.

Задачей настоящего изобретения является также выполнение носителя записи информации, содержащего команды для выполнения вышеописанного способа, когда эти инструкции исполняются электронным компьютером. И, наконец, задачей настоящего изобретения является также выполнение процессора безопасности, содержащего:

- регистры, в которых хранятся измерения нескольких событий, происходящих независимо друг от друга в отсутствие попыток атак, и

- компьютер с возможностью

- создания значения, по меньшей мере, одного показателя атаки в зависимости, по меньшей мере, от одного индекса отношения между по меньшей мере двумя различными измеренными событиями, измерения которых хранятся в регистрах, причем этот индекс отношения между событиями представляет собой временную близость между двумя измененными различными событиями, и

- обнаружения попытки атаки в случае, если значение показателя атаки превышает заданный порог.

Настоящее изобретение будет более понятно из следующего ниже описания, приведенного только посредством неограничивающего примера и выполненного со ссылкой на сопроводительные чертежи, на которых:

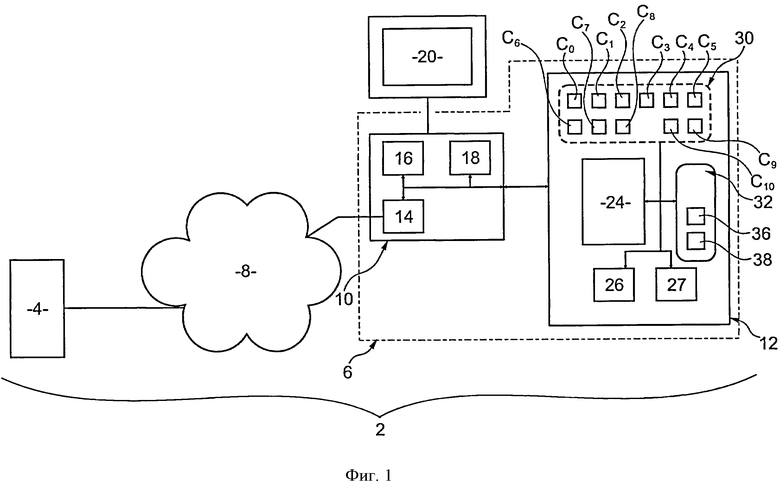

фиг.1 - схематичная иллюстрация системы передачи скремблированных мультимедийных контентов, которые содержит в себе процессор безопасности;

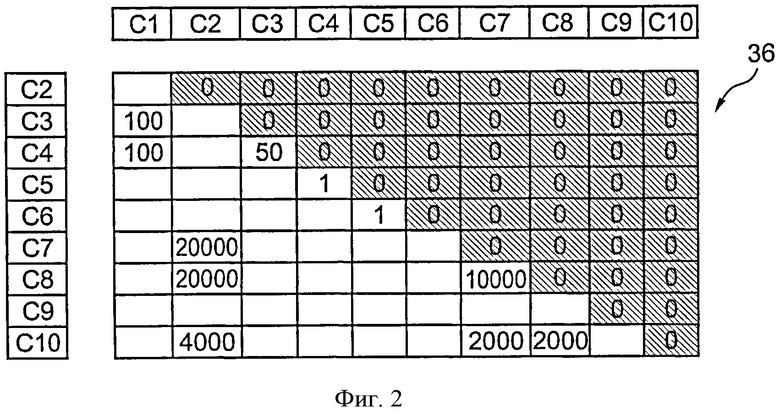

фиг.2 - схематичная иллюстрация матрицы взвешивания коэффициентов, используемых процессором безопасности системы (фиг. 1);

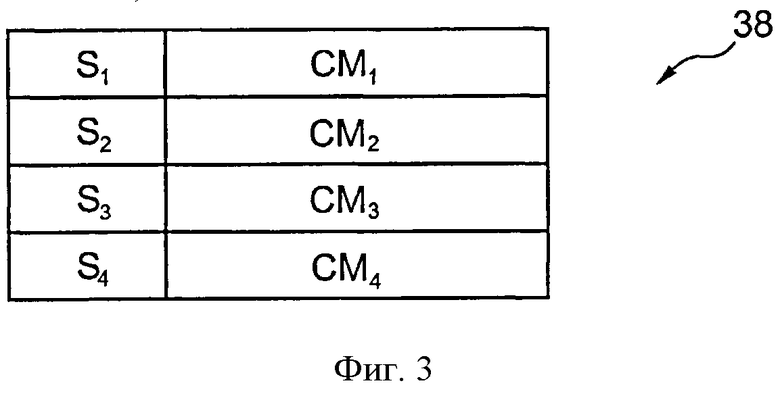

фиг.3 - схематичная иллюстрация таблицы предупреждения о порогах, которые используются процессором безопасности (фиг. 1); и

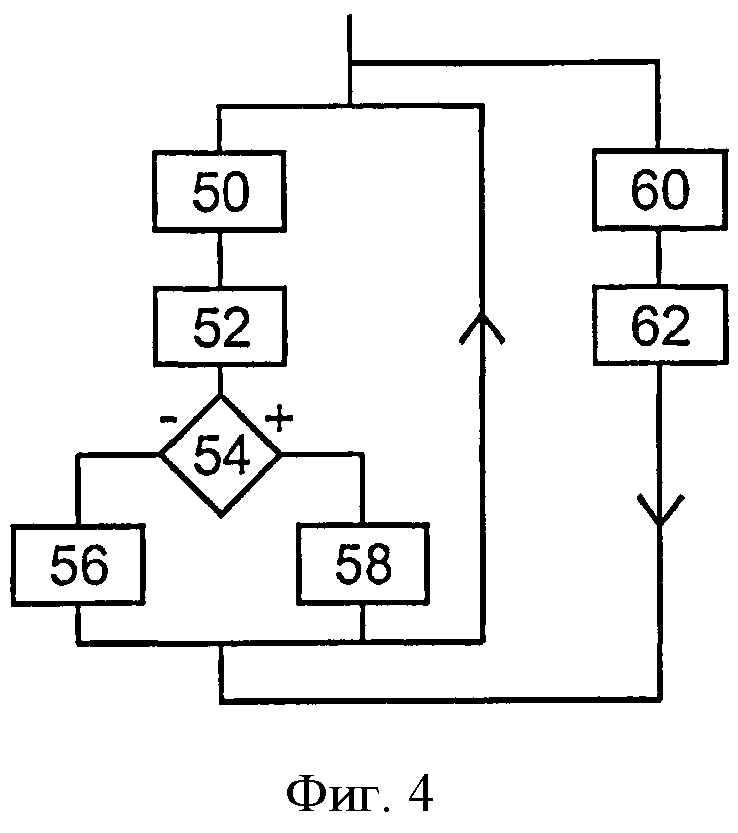

фиг.4 - алгоритм способа обнаружения попытки атаки на процессор безопасности системы (фиг. 1).

На этих чертежах одинаковые ссылки используются для обозначения одинаковых элементов.

Ниже, в этом описании, характеристики и функции, хорошо известные специалистам в данной области техники, не будут подробно описаны. Более того, используемая терминология относится к системам условного доступа к мультимедийным контентам. Для получения большей информации по этой терминологии можно использовать ссылку на работу: "Функциональная модель системы условного доступа". Обзор EBU. - Технический европейский вещательный союз, Брюссель, BE, №266, 21 декабря 1995 г. ("Functional model of a conditional access system" EBU Review - Technical European Broadcasting Union, Brussels, BE, No 266,21 December 1995).

На фиг.1 изображена система для абонентского широковещания мультимедийных контентов. Например, система 2 представляет собой систему для широковещания нескольких скремблированных телевизионных каналов. Дескремблирование каждого из этих телевизионных каналов или групп телевизионных каналов является условным после оплаты подписки абонентами. В этом описании, термин "скремблировать"/"шифровать" и "дескремблировать"/"дешифрировать" рассматриваются как синонимы.

Система 2 имеет, по меньшей мере, один передатчик 4, скремблированные мультимедийные контенты и многочисленные приемники с возможностью дешифрирования широковещания мультимедийного контента с помощью передатчика 4. Для упрощения на фиг.1 показан только один приемник 6. Например, другие приемники идентичны приемнику 6.

Приемник 6 подсоединен к передатчику 4 посредством сети 8 удаленной передачи информации. Сеть 8 может быть сетью беспроводной связи или проводной сетью, такой как Интернет.

Обычно передатчик 4 передает мультиплексированные скремблированные мультимедийные контенты с управляющими сообщениями ЕСМ (сообщение управления доступом) и EMM (сообщения условного доступа). Каждое сообщение ЕСМ содержит, по меньшей мере, одну криптограмму CW* управляющего слова CW, которое используется для дескремблирования скремблированного мультимедийного контента.

Приемник 6 имеет декодер 10 и процессор 12 безопасности, подсоединенный с возможностью разъединения к декодеру 10.

Декодер 10 имеет приемник 14 данных, передаваемых с помощью передатчика 4, подсоединенного к демультиплексору 16. Демультиплексор 16 демультиплексирует принятые данные и передает скремблированный мультимедийный контент в дескремблер 18 и сообщение ЕСМ или EMM в процессор 12 безопасности.

Процессор 12 безопасности принимает криптограмму CW* и дешифрирует эту криптограмму для того, чтобы послать управляющее слово CW в незашифрованном виде в дескремблер 18. Это дешифрирование разрешено только в случае, если права доступа, которые содержатся в ЕСМ, соответствуют правам доступа, которые хранятся в процессоре 12 безопасности. Например, процессор 12 является процессором чип-карты.

Дескремблер 18 дескремблирует дескремблированный мультимедийный контент посредством управляющего слова CW, дешифрированного с помощью процессора 12 безопасности. Затем дескремблированный мультимедийный контент отображается, например, в нешифрованном виде на экране 20 так, чтобы отображаемый мультимедийный контент был непосредственно заметен и понятен пользователю.

Функции и характеристики процессора 12 для выполнения различных операций, которые относятся к дешифрированию управляющего слова CW, известны и более подробно не будут описаны здесь.

Процессор 12 имеет электронный компьютер 24, подсоединенный к датчикам 26, 27, и набор 30 регистров.

Датчик 26 имеет преобразователь напряжения, который позволяет преобразовывать напряжение питания процессора 12 в часть цифровых данных, которые можно использовать с помощью компьютера 24.

Датчик 27 содержит оптический датчик, который позволяет преобразовывать фотоны лазерного луча, направленного на процессор 12, в цифровые данные, которые можно использовать с помощью компьютера 24.

В качестве иллюстрации, набор 30 содержит одиннадцать регистров, обозначенных С0-С10. Каждый из регистров С0-С10 предназначен для содержания в себе измерения события, которое может быть активизировано попыткой атаки на процессор 12. Измеренные события могут также происходить в отсутствие попыток атаки. Однако когда попытка атаки отсутствует, эти измеренные события происходят независимо друг от друга. Таким образом, маловероятно, что измеренные события будут происходить сопутствующим образом, когда отсутствует попытка атаки. Термин "сопутствующим образом" обозначает факт того, что эти события происходят во время одинакового интервала времени. Здесь один интервал времени связан с каждым измеренным событием. Этот интервал времени может иметь ограниченную продолжительность или, напротив, неограниченную продолжительность. В случае ограниченной продолжительности это означает, что события, которые происходят вне этого интервала времени, учитываются при измерении этого события. В этом случае интервал времени с ограниченной продолжительностью является скользящим интервалом времени. Этот скользящий интервал времени имеет ограниченную продолжительность, который изменяется так и когда время истекает так, чтобы только самые последние события учитывались для измерения этого события. Неограниченная продолжительность означает, что все события, начинающиеся с момента времени активизации измерения этого события, учитываются для измерения.

В этом случае, измерение события заключается в подсчете числа раз, которое произошло это событие во время интервала времени, связанного с этим событием. Таким образом, каждый из регистров содержит число, представляющее собой число происшествий одного и того же события. Поэтому ниже в этом описании регистры Ci называются счетчиками Ci.

Существует большое количество измеряемых событий. Обычно измеренные события относятся к одной из следующих категорий:

- нормальные события, которые легальный пользователь может активизировать, но которые, если они происходят в большом количестве, представляют собой ненормальное использование процессора 12,

- получение с помощью процессора 12 ошибочных или ненужных сообщений, т.е. сообщений, которые не существуют во время нормального и свободного от ошибок использования,

- обнаружение ошибок функционирования процессора 12.

Существуют многочисленные ошибки функционирования. Например, ошибки функционирования могут представлять собой ошибки при выполнении кода операционной системы процессора 12, ненормальную ситуацию, измеренную датчиками 26 или 27 ошибки целостности, обнаруженной в обработанных данных и т.д. В общем, события обнаружения рабочих ошибок, процессы обработки, выполняемые в текущий момент времени, прерываются, и процессор 12 автоматически производит сброс.

Ниже будет подробно описан пример событий, измеренных для каждого счетчика.

Счетчик C1 содержит число раз, которое было принято командой для консультации данных, подаваемых из процессора 12. Действительно, определенное число частей данных, которые содержатся в процессоре 12, можно свободно консультировать. Например, существуют команды для консультации идентификационного номера процессора 12 или прав доступа, записанных в процессоре 12. Поэтому получение команды консультации является нормальным событием, поскольку она остается редкой. Однако подсчет большого количества команд для консультации данных в процессоре 12 в пределах короткого периода времени может быть вызвано попыткой атаки.

Счетчик С2 показывает наличие необычных прав, записанных в процессоре 12. Необычное право представляет собой право, которое оператор системы 2 не использует нормальным образом. Например, большинство операторов никогда не записывают право в процессоре безопасности, для которого продолжительность срока действия больше, чем один год. Это означает, что право, записанное в процессоре 12 с продолжительностью срока действия более чем на один год, например право с неограниченной продолжительностью срока действия, является необычным правом даже в случае, если это возможность технически не предусмотрена. Аналогично, обычно оператор никогда не записывает право, которое авторизует доступ к и дешифрирует все мультимедийные контенты в процессорах безопасности. Таким образом, регистрация права, которая разрешает доступ ко всем мультимедийным контентам в процессоре 12, рассматривается как необычное право. Запись необычного права в процессоре 12 может происходить из-за ошибки оператора, но может также представлять собой попытку атаки.

Счетчик С3 подсчитывает число сообщений, принятых процессором 12, которые не имеют функциональной пригодности для процессора. Например, такое сообщение с отсутствием функциональной пригодности может представлять собой:

- сообщение для обращения к данным, которые не существуют в процессоре,

- сообщение для стирания несуществующей части данных (например, кода доступа и т.д.) в процессоре, или

- два последовательных сообщения для считывания одинаковой части данных в процессоре 12.

Эти сообщения являются синтаксически правильными и не вызывают никаких ошибок выполнения в процессоре 12. Однако они являются ненужными. Такие ненужные сообщения может ошибочно посылать оператор. Они могут также использоваться во время попытки атаки.

Счетчик С4 подсчитывает число синтаксических ошибок в сообщениях, переданных в процессор 12, т.е. в сообщениях ЕСМ и EMM, переданных в этот процессор. Действительно, синтаксис или структура сообщений ЕСМ и EMM соответствуют предопределенной грамматике. Поэтому процессор 12 может обнаружить эти ошибки синтаксиса и посчитать их в счетчике С4. Ошибки синтаксиса могут быть вызваны ошибкой оператора, но также могут происходить во время попытки атаки.

Счетчик С5 представляет собой счетчик повторно воспроизводимых команд, тогда как они не должны обычно повторно воспроизводиться несколько раз. Повторное воспроизведение команды заключается в отправлении несколько раз одной и той же команды в процессор безопасности. Например, команда может представлять собой сообщение обновления, для обновления определенных частей данных, записанных в процессоре 12. Повторное воспроизведение сообщения можно обнаружить с помощью процессора 12 путем записи даты последнего сообщения обновления.

Счетчик С6 подсчитывает число ошибок целостности, обнаруженных в сообщениях, принятых с помощью процессора 12. Действительно, сообщения, принятые процессором 12, содержат данные, а также криптографическую избыточность этих частей данных, что позволяет процессору 12 проверить, что в принятых данных ошибка отсутствует. Например, избыточность в данных можно получить путем интегрирования подписи или данных с CRC (циклический контроль избыточности), которые содержатся в этом сообщении. Ошибки в данных, которые содержатся в сообщении, могут быть вызваны помехами при их транспортировке в сети 8 или в декодере 10. Однако ошибочные данные также используются во время попытки атаки.

Счетчик С7 подсчитывает число ошибок целостности в частях данных, которые содержатся в процессоре 12. Действительно, определенное число частей данных, записанных в процессоре 12, связано с криптографической избыточностью, которая используется для проверки целостности записанных соответствующим образом частей данных. Иногда это может произойти случайно, например, в результате электромагнитных помех, которые могут привести к тому, что часть данных, записанных в процессоре 12, будет ошибочной. Однако наличие ошибочных данных, записанных в процессоре 12, может также представлять собой попытку атаки.

Счетчик C8 подсчитывает число плохих ветвлений во время выполнения исполнения кода операционной системы процессора 12. Плохое ветвление представляет собой несвоевременный или ошибочный переход в инструкции, выполняемый процессором 12 для другой инструкции. Эти плохие ветвления при исполнении кода можно обнаружить путем выполнения одинаковых инструкций над одинаковыми частями данных два раза подряд. Если два исполнения кода не дали одинакового результата, это означает, что там было плохое ветвление. Несвоевременные переходы из инструкций в коде, который исполняется процессором 12, можно подсказать, используя напряжение питания процессора 12 или направляя лазерный луч на этот процессор 12.

Счетчик С9 подсчитывает, сколько раз процедура поиска данных выполняется после того, как извлекается процессор 12. Извлечение процессора 12 состоит в удалении процессора 12 из декодера 10 во время работы так, что подача питания в процессор 12 прерывается во время обработки данных. Процедура поиска данных становится возможной после такого прекращения подачи питания для возврата процессора 12 в состояние, в котором он находился перед прекращением подачи питания. Процессор 12 можно случайно извлечь из декодера 10. Однако несвоевременные прекращения подачи питания в процессоре 12 также часто используются во время попыток атаки для предотвращения выполнения контрмер с помощью процессора 12.

Счетчик С10 подсчитывает, сколько раз датчик 26 измеряет ненормальную подачу питания, которое равно числу раз, когда датчик 27 обнаруживает лазерный луч. Действительно, ненормальные напряжения, а также наличие лазерного луча являются типичной попыткой атаки на процессор 12. Однако эти датчики 26 и 27 могут также обнаружить ненормальное напряжение или наличие лазерного луча, которые случайно следуют, например, за электромагнитными помехами, вызванными устройством поблизости от процессора 12 даже в случае, когда отсутствует попытка атаки. Например, подача питания на декодер 12 может привести к обнаружению ненормального напряжения с помощью датчика 26.

Счетчик С0 должен отличаться от предыдущих счетчиков, так как он подсчитывает событие, которое происходит только во время нормальной работы процессора 12 и не может быть вызвано попыткой атаки. Например, событие, подсчитанное счетчиком С0, равно в этом случае числу сообщений ЕСМ и EMM, правильно обработанных процессором 12.

Значения этого счетчика С0 используются для ограничения временной памяти некоторых предыдущих счетчиков скользящим интервалом времени с ограниченной продолжительностью. Например, с этой целью, значение счетчика С0 вычитается из значения счетчика Ci, где i>0, и только разность между этими двумя счетчиками, доведенная до 0, если она является отрицательной, используется для вычисления индекса отношения между событиями, как будет описано ниже. Например, в этом случае, кроме значения счетчиков C8 и С10, для вычисления показателей отношения между событиями используется только разность между значениями счетчиков Ci и С0. Путем использования значения счетчика С0, события, которые произошли вне скользящего интервала времени, определенного таким образом, не учитываются для обнаружения попытки атаки. Следует отметить, что продолжительность скользящего интервала времени, определенного посредством счетчика С0, не является постоянной и зависит от использования процессора 12.

Компьютер 24 подсоединен к памяти 32, содержащей различные части данных и инструкции, необходимые для функционирования процессора 12. В частности, память 12 содержит:

- инструкции, необходимые для выполнения способа, изображенного на фиг. 4, при их исполнении компьютером 24,

- матрицу 36 коэффициентов взвешивания и таблицу 38 порогов предупреждения.

Пример матрицы 36 представлен более подробно на фиг. 2. Эта матрица 36 содержит столько элементов данных, сколько имеется счетчиков событий, которые должны активизироваться в результате попытки атаки. Поэтому в этом случае матрица 36 представляет собой матрицу с десятью столбцами, каждый из которых связан с счетчиком Ci. Матрица 36 также содержит девять строк, связанных соответственно с счетчиками С2-С10.

Элемент, расположенный на пересечении i-го столбца слева и j-й строки сверху содержит коэффициент mij взвешивания, связанный с индексом отношения между событиями CiCj+1. Показатель отношения между событиями CiCj+1 представляет собой индекс, вычисленный из значений счетчиков Ci и Cj+1, которые предоставляют показатель отношения между событиями, подсчитанными счетчиком Ci, и событиями, подсчитанными счетчиком Cj+1. В этом случае, каждый индекс отношения между событиями создан так, чтобы каждое его значение было выше, так как большое количество событий, измеренных, соответственно, с помощью датчиков Ci и Cj+1, произошло поблизости в тот же самый момент времени. С этой целью в этом варианте осуществления каждый индекс отношения между событиями CiCj+1 соответствует произведению значений счетчиков Ci и Cj+1 в тот же самый момент времени.

Таблица порогов 38 предупреждения, изображенная на фиг. 3, содержит первый столбец, содержащий четыре порога S1-S4 предупреждения. Каждый порог предупреждения имеет численное значение, и эти пороги предупреждения классифицируются по возрастанию порядка сверху вниз в таблице 38.

Таблица 38 также имеет второй столбец, связывающий одну или более контрмер, обозначенных как CMi с каждым порогом Si. Контрмеры представляют собой действия, выполняемые процессором 12 безопасности, которые предназначены для создания большего затруднения для извлечения или определения данных, которые содержатся в процессоре 12 или незаконно используют этот процессор 12.

В этом случае контрмеры CMi, связанные с порогом Si, являются менее строгими и влекут за собой меньшие штрафы для пользователя процессора, чем таковые, связанные с более высоким порогом Si+1 предупреждения. Таким образом, чем выше переход порога Si предупреждения, тем строже будут выполняться ответные контрмеры CMi.

Посредством иллюстрации, контрмеры CM1 состоят из добавления избыточности к дополнительному ветвлению кода, который будет исполняться процессором 12. Например, эта избыточность получается путем выполнения условного перехода несколько раз и проверки того, что полученный результат является тем же самым при каждом выполнении.

Контрмера CM1 заключается в дополнительном добавлении избыточности к операции проверки целостности обработанных данных. Например, целостность данных проверяется несколько раз, тогда как, если порог S1 не перейден, верификация выполняется один раз. Она также заключается в проверке целостности данных, чья целостность не проверяется, если не превышен порог S1.

Контрмера СМ2 заключается, например, в добавлении ограничений к возможностям строковых команд кода, выполняемого с помощью процессора 12. Ее можно получить путем форсирования процессора 12 для выполнения полного блока инструкций без учета любого прерывания между выполнением команд этого блока.

Контрмера СМ2 также заключается в исключении некоторых функций процессора 12, до сих пор разрешенных в случае, когда порог S2 не был превышен. Например, добавление новых услуг, таких как добавление нового оператора или нового абонента, запрещено. Доступ к административным функциям процессора 12 можно также запретить, если порог S2 превышен.

Например, контрмера СМ3 заключается в модификации коэффициентов взвешивания, присутствующих в матрице 36 для того, чтобы верхний порог, то есть S4, легко и быстро достигался при измерении событий. Таким образом, как описано со ссылкой на фиг. 4, чувствительность процессора 12 для обнаружения попытки атаки увеличивается. Контрмеры СМ3 также включают в себя систематическую и дублированную проверку ценности каждого принятого сообщения. Контрмера СМ3 может также заключаться в повышении контроля над выполнением последовательности операций. Она особенно заключается в получении каждой части исполняемого кода, который будет исполняться дважды процессором 12, и в проверке путем сравнения в конце этих двух исполнений, что полученные результаты являются одинаковыми. В случае несоответствия между полученными результатами счетчик C8 выполняет приращение.

В итоге, контрмера СМ4 окончательно делает недействительным процессор 12 с тем, чтобы он был окончательно неиспользуемым. Например, с этой целью конфиденциальная информация, которая содержится в процессоре 12, стирается.

Функционирование процессора 12 будет более подробно описано ниже со ссылкой на способ, изображенный на фиг. 4.

Наряду с нормальной работой процессора 12, этот процессор также выполняет способ для обнаружения попытки атаки. С этой целью, на этапе 50, он измеряет события, которые, вероятно, были вызваны попыткой атаки. В этом случае, это измерение заключается в подсчете соответствующего события в счетчиках Ci.

Затем во время этапа 52, процессор 12 создает три показателя атак I1, I2 и I3, соответственно.

Индикатор I1 выполнен так, чтобы быть более чувствительным к попыткам атак, которые используют лазерную помеху, а не показатели I2 и I3. Атака с помощью лазерной помехи заключается в наведении лазерного луча на процессор безопасности для указания переходов инструкций в коде, исполняемом с помощью этого процессора в ключевые моменты при их выполнении. Ключевые моменты обычно соответствуют условным переходам.

В этом случае, значение показателя I1 приведено в виде следующего отношения:

I1=m2,6С2С7+m2,7C2C8+m2,9С2С10+m7,7C7C8+m7,9С7С10+m8,9C8C10,

где mij - коэффициент взвешивания, значение которого содержится в матрице 36.

Показатель I2 предназначен для большей чувствительности к логическим атакам, чем другие два показателя. Логическая атака заключается в создании поиска для логической ошибки или ошибки реализации в коде, исполняемым процессором 12 для того, чтобы получить ненормальное поведение в этом процессоре. Например, логическая атака заключается в посылке очень большого количества ошибочных сообщений в процессор 12, каждое из которых отличается друг от друга до тех пор, пока одно из этих сообщений не укажет на ненормальное поведение в процессоре 12.

Например, значение показателя I2 создано посредством следующего соотношения:

I2=m1,2С1С3+m1,3C1C4+m3,3С3С4.

В итоге, показатель I3 предназначен для большей чувствительности к попыткам атак DPA (дифференциальный анализ мощности). Атака DPA представляет собой атаку, в которой большое количество сообщений посылается в процессор 12 для указания большого количества указаний исполнений криптографических алгоритмов над большим числом различных частей данных и в то же самое время измеряется потребление тока процессора 12. Затем, путем статистического анализа собранных данных можно обнаружить значение ключей или конфиденциальность данных, записанных в процессоре 12.

Например, показатель I3 создан посредством следующих соотношений:

I3=m4,4С4С5+m4,5С4С6+m5,5С5С6.

Затем, раз значение показателей I1-I3 было создано, на этапе 54, значение этих индикаторов сравнивают с различными порогами предупреждения, записанными в таблице 38 для обнаружения попытки атаки.

Если ни один из этих показателей не имел своего значения для превышения порога Si, то на этапе 56 не выполняют контрмеру.

Напротив, если значение одного из этих показателей превышает один из порогов Si, то контрмера, связанная с самым высоким превышенным порогом Si, выполняется на этапе 58.

В конце этапов 56 и 58 способ возвращается на этап 50.

В то же самое время в качестве этапов 50-58, во время этапа 60, передатчик 4, использующий, например, сообщение типа EMM или ЕСМ, передает новые значения для коэффициентов взвешивания, затем, на этапе 62, процессор 12 принимает это сообщение и обновляет значения коэффициентов взвешивания, которые содержатся внутри матрицы 36.

Обновление коэффициентов взвешивания позволяет легко модифицировать чувствительность показателя для конкретной попытки атаки. В частности, можно отметить, что для того, чтобы модифицировать эту чувствительность показателя до конкретной попытки атаки, что необходимо только для модификации коэффициентов взвешивания, записанных в матрице 36 без необходимости модифицировать другие инструкции, исполняемые процессором 12.

Возможны многочисленные другие варианты осуществления. Например, процессор 12 может включать в себя несколько различных матриц коэффициента взвешивания. Каждую из этих матриц можно использовать для вычисления соответствующего показателя атаки. Затем это позволяет присвоить каждый индекс отношения между событиями различному коэффициенту взвешивания в зависимости от созданного показателя атаки. Использование нескольких матриц коэффициентов взвешивания может быть также полезным для модифицирования матрицы взвешивания, используемой при превышении нового порога предупреждения.

Напротив, вместо нескольких показателей можно создать один индикатор атаки.

В качестве варианта, существует столько таблиц порогов предупреждения, сколько существует созданных показателей атак. В этом варианте, пороги предупреждения, связанные с одним конкретным показателем атаки, не являются обязательно одинаковыми, как пороги предупреждения, связанные с другим показателем атаки.

Таблицу 38 можно также заменить на один порог предупреждения, связанный с контрмерами.

Один из счетчиков Ci позволяет просто вычислить существование событий без подсчета числа происшествий этого события. В этом случае, значение этого счетчика кодируется посредством одного информационного бита. Даже в этом случае, значение счетчика существования можно связать с интервалом времени бесконечной или конечной продолжительности.

Датчики, которые отличаются от тех, которые описаны, можно реализовать в процессоре 12. Например, процессор 12 может включать в себя датчик температуры.

Индекс отношения между событиями не ограничивается произведением двух измерений. Например, это может также соответствовать произведению более чем двух измерений. Однако увеличение числа измерений, перемноженных вместе, также увеличивает размер матрицы коэффициента взвешивания.

Кроме того, можно вычислить индекс отношения между событиями, представляющими собой близость во времени, по меньшей мере, между двумя событиями с помощью математических операций, которые отличаются от умножения.

Многочисленные контрмеры, которые отличаются от тех, которые указаны здесь выше, можно выполнить в ответ на превышение порога предупреждения с помощью одного из показателей атаки. Например, другие контрмеры могут заключаться в модификации криптографического алгоритма, который исполняется процессором 12. Контрмера может также состоять из использования или измерения многочисленных событий для создания показателя атаки, который до сих пор не был измерен. Например, в ответ на превышение порога предупреждения, событие, измеренное с помощью одного из датчиков 26 или 27, можно подсчитать, тогда как ранее они не были подсчитаны.

Компьютер 24 можно выполнить с помощью одного или более процессоров. Например, его можно выполнить с помощью процессора, с помощью которого существует связанный сопроцессор. Способ обнаружения можно затем выполнить как с помощью процессора, так и с помощью сопроцессора.

Измерение было описано здесь в конкретном случае, где необходимо подсчитывать число происшествий события. Однако измерение может также состоять из записи, в одном из регистров, значения события, такого как, например, значения, измеренного с помощью одного из датчиков 26 или 27. Для того чтобы подсчитать число происшествий события, значения счетчиков можно также подвергнуть отрицательному приращению вместо приращения, описанного здесь выше.

Архитектура приемника 6 является только иллюстрацией конкретной ситуации, в частности, дескремблер 18 можно также выполнить съемным. Напротив, дескремблер и процессор безопасности можно реализовать без любой степени свободы в декодере. В этом случае, дескремблер и процессор безопасности могут принимать вид компонентов программного обеспечения.

Изобретение относится к области процессоров безопасности. Техническим результатом является обнаружение попытки атаки на процессор безопасности с помощью непосредственно процессора безопасности. Раскрыт способ обнаружения попытки атаки процессора безопасности с помощью самого процессора безопасности, содержащий этапы, на которых: измеряют несколько различных событий, происходящих независимо друг от друга в отсутствие попыток атак; создают значение по меньшей мере одного показателя атаки в зависимости по меньшей мере от одного индекса отношения по меньшей мере между двумя различными измеренными событиями, причем индекс отношения представляет собой близость по времени между двумя различными измеренными событиями и обнаруживают попытку атаки в случае, если значение показателя атаки превышает заданный порог. 3 н. и 5 з.п. ф-лы, 4 ил.

1. Способ обнаружения попытки атаки процессора безопасности с помощью самого процессора безопасности, характеризующийся тем, что измеряют (50) множество различных событий, происходящих независимо друг от друга в отсутствие попыток атаки,

при этом способ содержит этапы, на которых:

получают по меньшей мере один индекс отношения по меньшей мере между двумя результатами измерений путем перемножения указанных результатов измерений друг на друга, причем индекс отношения между событиями характеризует близость по времени между двумя различными измеренными событиями;

создают (52) значение по меньшей мере одного показателя атаки в зависимости от упомянутого по меньшей мере одного индекса отношения по меньшей мере между двумя различными измеренными событиями, причем значение показателя атаки создают (52) на основе множества индексов отношения между различными измеренными событиями путем взвешивания значимости указанных индексов отношения относительно друг друга посредством заданного набора коэффициентов взвешивания; и

обнаруживают (54) попытку атаки, если значение показателя атаки превышает заданный порог.

2. Способ по п. 1, в котором создают (52) множество значений показателя атаки путем использования множества различных наборов коэффициентов взвешивания для одинаковых индексов отношения, причем каждый набор коэффициентов взвешивания задан так, чтобы быть более чувствительным к некоторой попытке атаки, отличной от попыток атаки, к которой более чувствительны другие показатели.

3. Способ по п. 2, в котором коэффициент взвешивания одинакового индекса отношения является одинаковым во всех наборах коэффициентов взвешивания, используемых для создания различных значений показателя атаки.

4. Способ по п. 1, в котором измерение (50) события ограничено скользящим интервалом времени с тем, чтобы не учитывать события, происшедшие вне указанного интервала времени.

5. Способ по п. 1, в котором по меньшей мере одно из измеренных событий представляет собой обнаружение ошибки функционирования процессора безопасности, причем каждый случай приводит к прекращению процессором безопасности выполняемых операций обработки и выполнению автоматического сброса для возобновления указанных операций сначала.

6. Способ по п. 1, в котором измерение (50) события заключается в подсчете с помощью счетчика, сколько раз произошло указанное событие, причем значение счетчика образует результат измерения.

7. Носитель записи информации, содержащий инструкции для выполнения способа обнаружения по любому из пп. 1-6 при выполнении инструкций с помощью электронного компьютера.

8. Процессор безопасности, содержащий:

регистры (C1-С10) для хранения результатов измерения множества событий, происходящих независимо друг от друга в отсутствие попыток атаки; и

компьютер (24), выполненный с возможностью

получения по меньшей мере одного индекса отношения по меньшей мере между двумя результатами измерений путем перемножения указанных результатов измерений друг на друга, причем указанные результаты измерений хранятся в регистрах, а индекс отношения характеризует близость по времени между двумя различными измеренными событиями,

создания значения по меньшей мере одного показателя атаки в зависимости от упомянутого по меньшей мере одного индекса отношения по меньшей мере между двумя различными измеренными событиями, причем значение показателя атаки создается на основе множества индексов отношения между различными измеренными событиями путем взвешивания значимости указанных индексов отношения относительно друг друга посредством заданного набора коэффициентов взвешивания, и

обнаружения попытки атаки, если значение показателя атаки превышает заданный порог.

| US 5533123 A, 02.07.1996 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Струйный вакуумный насос | 1985 |

|

SU1252561A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| УСОВЕРШЕНСТВОВАННОЕ УСТРОЙСТВО ОБРАБОТКИ СЕТЕВОЙ СТАТИСТИКИ | 2005 |

|

RU2346399C2 |

Авторы

Даты

2015-11-20—Публикация

2010-06-23—Подача