Изобретение относится к аналоговой вычислительной технике, предназначено для исследования нелинейных динамических объектов с использованием аппарата дифференциальных преобразований и может быть использовано также для запоминания функций, заданных ре апьными физическими сигналами, преобразования масштаба аргумента и введения регулируемого запаздывания.

Цель изобретения - повьшение точности и .расширение функциональных возможностей устройства для решения дифференциальных уравнений в части обратимости его работы.

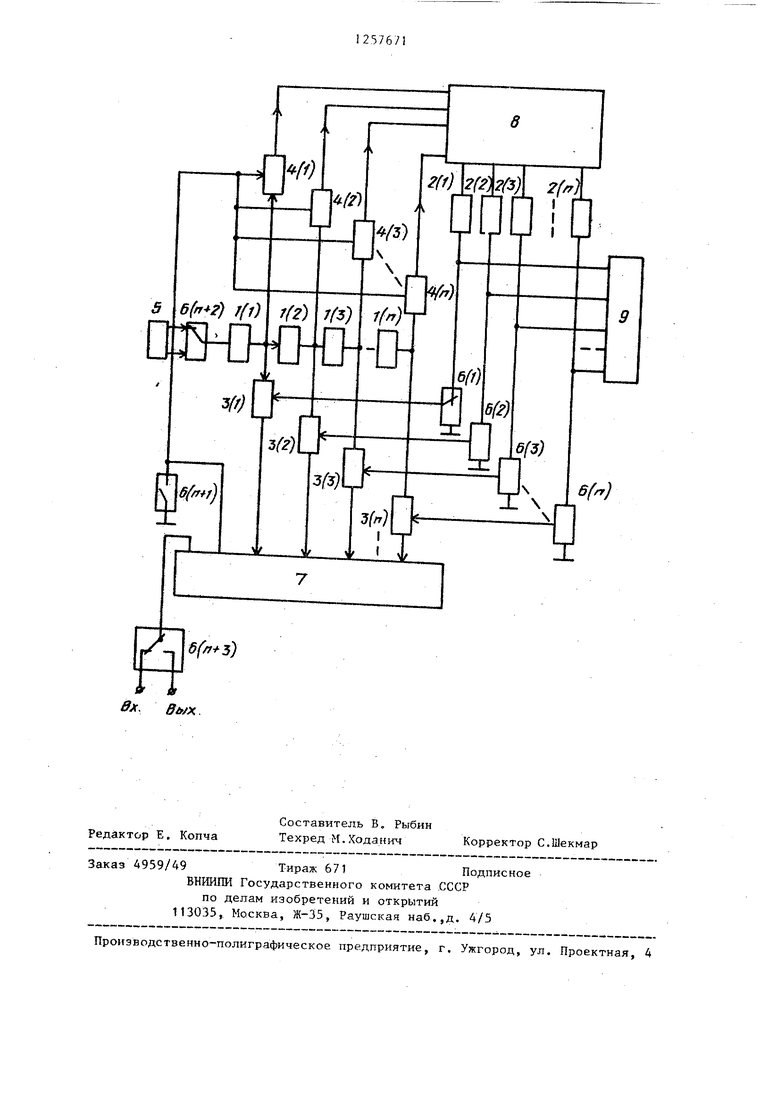

На чертеже схематично изображено предлагаемое устройство.

Устройство содержит интеграторы 1(1), 1(2),...,1(п) первой группы.

10

15

изменение масштаба аргумента и введение запаздывания.

В первом режиме переключатели 6(1) 6(2),...,6(п) находятся в положении, при котором выходы интеграторов 2(1), 2(2),.,.,2(п) второй группы отключены от входов умножителейЗ(1)53(2), . . . «,.,3(ii) первой группы, которые этими же переключателями соединены с шиной нулевого потенциала. Тем самым на выходах умноясителей 3(1), 3(2) ,.. . ,3(п) первой группы. Соединенных с соответствующими п выводами обратимого сумматора 7, находятся нулевые потенциалы. Обратимый сумматор 7 эквивалентен двухвходовому сумматору, на одном из выводов которого действует анализируемый или запоми ае а1й сигнал, В соответствии с уравнением обратимого

25

30

ся выводе появится этот анализируе- мьтй сигнап с противоположным знаком Переключатель 6(п+1) находится в разомкнутом состоянии и не препятствует поступлению инвертированного значения входного сигнала на объединенные входы умножителей 4(1), 4(2), ...,4(п) второй группы. На вторые входы этих умножителей поступают сигналы.

поступают / -t к пропорциональные kfp) .с Mf,f.Jt,l t J.iJ V/i-I. CW A JJl llJIt U - 9

ходов каскадно соединенных интеграторов 1(1), 1(2),,.„,1(n) первой труппы.

35

интеграторы 2(1) ,2(2) ,.,. ,,2(п) второй 20 сумматора в этом случае на оставшем- группы, умножители первой группы 3(О, 3(2) ,.... ,3(п), умножители второй группы 4(1),4(2) ,...,4(п)5 блок 5 задания начальных условий, переключатели 6(1), 6(2),...,6(п+2), 6(п+3), обратимый сумматор 7 5 блок 8 формирования линейного преобразования, блок 9 регистрации.

Устройство работает следующим образом.

Устройстззо предназначено для определения аппроксимирующего дифференциального спектра сигнала, действующего на (п+2)-м выводе обратимого сумматора 7, запоминания этого спектра и формирования восстановленного сигнала с возможностью измерения временного масштаба и реализации функции запаздывающего аргумента.

В зависимости от положения переключателей 6(1) , 6(2),...,6(п+2), 6(п+3) устройство может находиться в из трех следующих реяшмов.

Режим определения аппроксимирующего Дифференциального спектра сигнала. 45 Этот же режим используется для записи аналогового сигнала как функции времени.

Режим хранения элементов аппроксимирующего дифференциального спектра исследуемого сигнала В этом же режиме осуществляется экономное хранение элементов спектра запоминаемой функции.

Режим восстановления аппроксимированного сигнала. Этот же режим является режимом воспроизведения записанной функции, при котором возмоя-ло

40

Переключатель 6(п+2) находится в положении, при котором с выхода блока 5 задания начальных условий на вход интегратора 1(1) первой группы поступает напряжение положительной полярности..

Интеграторы обеих групп работают в теченье анализируемого отрезка времени О t :й Т одновременно с поступлением входного сигнала,

J к

Сигналы, пропорциональные (--) , проходя через умножители 4(1), 4(2), ,,.,4(ц) второй группы, умножаются на :на инвертированное значение входного сигнала и поступают на входы блока 8 50 формирования линейного преобразова- ВИЯ таким образом, что на входы интеграторов 2(1), 2(2),..,,2(п) второй группы поступают линейные комбинации упомянутых произведений, необходимые для об.разования компонент аппроксимирующего дифференциального спектра на выходах интеграторов 2(1), 2(2),..., 2(п) второй группы. Эти компоненты

55

изменение масштаба аргумента и введение запаздывания.

В первом режиме переключатели 6(1), 6(2),...,6(п) находятся в положении, при котором выходы интеграторов 2(1), 2(2),.,.,2(п) второй группы отключены от входов умножителейЗ(1)53(2), . . . «,.,3(ii) первой группы, которые этими же переключателями соединены с шиной нулевого потенциала. Тем самым на выходах умноясителей 3(1), 3(2) ,.. . ,3(п) первой группы. Соединенных с соответствующими п выводами обратимого сумматора 7, находятся нулевые потенциалы. Обратимый сумматор 7 эквивалентен двухвходовому сумматору, на одном из выводов которого действует анализируемый или запоми ае а1й сигнал, В соответствии с уравнением обратимого

ся выводе появится этот анализируе- мьтй сигнап с противоположным знаком Переключатель 6(п+1) находится в разомкнутом состоянии и не препятствует поступлению инвертированного значения входного сигнала на объединенные входы умножителей 4(1), 4(2), ...,4(п) второй группы. На вторые входы этих умножителей поступают сигналы.

поступают / -t к пропорциональные kfp) .с Mf,f.Jt,l t J.iJ V/i-I. CW A JJl llJIt U - 9

ходов каскадно соединенных интеграторов 1(1), 1(2),,.„,1(n) первой труппы.

сумматора в этом случае на оставшем-

Переключатель 6(п+2) находится в положении, при котором с выхода блока 5 задания начальных условий на вход интегратора 1(1) первой группы поступает напряжение положительной полярности..

Интеграторы обеих групп работают в теченье анализируемого отрезка времени О t :й Т одновременно с поступлением входного сигнала,

J к

Сигналы, пропорциональные (--) , проходя через умножители 4(1), 4(2), ,,.,4(ц) второй группы, умножаются на :на инвертированное значение входного сигнала и поступают на входы блока 8 формирования линейного преобразова- ВИЯ таким образом, что на входы интеграторов 2(1), 2(2),..,,2(п) второй группы поступают линейные комбинации упомянутых произведений, необходимые для об.разования компонент аппроксимирующего дифференциального спектра на выходах интеграторов 2(1), 2(2),..., 2(п) второй группы. Эти компоненты

поступают также на входы блока 9 регистрации.

В режиме хранения переключатели 6(1), 6(2) ,, ... ,6(п) остаются в прежнем состоянии, а переключатель 6(п+1 переключается в противоположное состояние и подключает шину нулевого потенциала к объединенным взводам умножителей 4(1), 4(2) ,..., 4(г1) второй группы и соответствующему входу обратимого сумматора 7.

Это состояние может сохраняться неограниченно долго в зависимости от свойств интеграторов 2(1), 2(2),..., 2(п) второй группы, которые находятс в режиме хранения напряжений конденсаторов, включенных в обратные связи операционных усилителей.

В последнем режиме работы устройства переключатели 6(1), 6(2),..,, 6(п) переключаются в противоположные положения, при которых входы умножителей 3(1), 3(2),...,3(п) первой группы подключаются к выходам интеграторов 2(1), 2(2),...,2(п) второй группы. Переключатель 6(п+1) сохраняет свое положение, соответствующее режиму хранения, а переключатель 6(п+2) переключается в противоположное положение, обеспечивающее подачу напряжения отрицательной полярности с второго выхода блОка 5 начальных условий на вход интегратора 1(1) первой группы. Переключение (п+3)-гЬ переключателя обеспечивает режим ввода или вьюода для (п+2)-го вьшода обратимого сумматора 7.

Таким образом, обратимый сумматор 7 превращается в (п+2)-е входовое устройство, причем на выходе этого сумматора, где ранее действовал анализируемый сигнал, теперь с началом работы интеграторов 1(1), 1(2),..., 1(п) первой группы появляется его ап- прок;симация в соответствии с формулой

X(t) |:X(k)() К О п

Масштабная постоянная Н , входя- щая Б выражение (1), принципиально может иметь значения, отличающиеся от значений, которые она имела в первом режиме работы устройства, и

10

20

) 5 5

30-jQ

25

50

тем самым обеспечивается изменение масщтаба аргумента.

Формула изобре.тения

Устройство для решения дифференциальных уравнений, содержащее блок задания начальных условий, п+1 переключателей, блок регистрации, блок формирования линейного преобразования, две группы из п умножителей, две группы из п интеграторов, выход каж дого i-ro интегратора первой группы соединен с входом (п+1)-го интегратора первой группы и с первыми входами соответствукнцих умножителей первой и второй групп, выходы умножителей второй группы соединены с группой входов блока формирования линейного преобразования, группа выходов которого подключена к соответствующим входам интеграторов второй группы, выходы которых соединены с группой входов блока регистрации и через п переключателей подключены к вторым входам соответствующих умножителей первой группы и соединены с шиной нулевого потенциала, вторые входы умножителей второй группы через, (п+1)-и переключатель подключены к шине нулевого потенциала, отличающее- с я тем, что, с целью повышения точности и расширения класса решаемых задач за счет учета запаздывания и возможности изменения масштаба времени, в него введены (п+2)-й и (п+3)-й переключатели и обратимый сумматор, первые п вьшодов которого соединены с соответствукяцими выходами .умножителей первой группы, вход первого интегратора первой группы через (п+2)-гЙ переключатель подключен к напряжения положительной и отрицательной полярности блока задания начальных условий, (п+1)-и вывод обратимого сумматора подключен к вторым входам умножителей второй группы, (п+2)-й вывод обратимого сумматора через (п+3)-й переключатель соединен с входом задания анализируемого дифференциального сигнала устройства и выходом аппроксимации дифференциального спектра устройства.

V/;

о

«/:)

б() ///;

им

5(г)

Yf)

1(1

WO

ъ(г}

)

т

F

)

Ул/х

Редактор Е, Копча

Составитель В„ Рыбин

Техред М.ХодаЕ ич Корректор С.Шекмар

Заказ 4959/49Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

V3)

2(f

П

//.;

б//}

х

л;

j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1985 |

|

SU1305728A1 |

| Устройство для решения дифференциальных уравнений | 1986 |

|

SU1403079A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1171815A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Функциональный преобразователь | 1979 |

|

SU911553A1 |

| Цифровой интегратор | 1980 |

|

SU928351A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Устройство для решения задачи Лагранжа | 1990 |

|

SU1817090A1 |

| Анализатор комплексного спектра | 1979 |

|

SU917119A1 |

| Устройство для вычисления коэффициентов Фурье взаимного спектра | 1980 |

|

SU920739A1 |

Изобретение относится к области аналоговой вычислительной техники и предназначено для осуществления прямого и обратного дифференциальных преобразований функций, заданных реальными сигналами, а также для аналитической аппроксимации сигналов, построения экономичных аналоговых запоминающих устройств и т.п. Цель изобретения - повьпление точности и расширение функциональных возможностей устройства для решения дифференциальных уравнений с использованием операционных методов. Устройство содержит две группы интеграторов, две группы умноясителей, переключатели, блок формирования линейного преобразования матричного типа, блок регистрации и обратимый сумматор. Новым в предлагаемом устройстве является то, что оно содержит обратимый сумматор, связанный с перечисленными вьнпе элементами соответствующими связями,что позволяет за счет введения эффекта обратимости повысить производительность аналоговых и гибридных вычислительных систем при реализации функций запоминания аналоговых сигналов и реализации систем с запаздывакяцим аргументом. 1 ил.

| Пухов Г.Е | |||

| Дифференциальный анализ электрических чисел | |||

| Киев; Наукова думка, 1982 | |||

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1171815A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1984-12-25—Подача