Описание

Изобретение относится к управлению процессором с использованием резервирования и способу управления, в частности к управлению двумя процессорами с использованием резервирования, а также к многоядерной резервной контрольно-вычислительной системе.

Известно, когда два процессора могут выполнять одновременно одни и те же команды и путем сравнения выходных данных можно определить, есть ли ошибка. При этом два процессора могут работать синхронно в такт или с определенным смещением во времени (которое при сравнении можно соответствующим образом компенсировать). При этом могут возникать как постоянные ошибки, вызванные дефектом, появившимся, например, при изготовлении, так и случайные ошибки, вызванные, например, временной электромагнитной паразитной связью. При появлении синхронной ошибки, при которой выходные данные двух процессоров отличаются друг от друга, выполнение программы прерывается и в самом простом случае вычислительная система отключается.

Подготовка помехоустойчивости, после чего при появлении ошибки вычислительная система продолжает выполнять желаемую программу, образует, однако, особую задачу для процессоров с двойным резервированием. Были предприняты попытки, направленные на поддержку помехоустойчивости в системах безопасности с помощью только двух процессоров с резервированием. Патент US 5915082 В2 раскрывает архитектуру системы, в которой внутренние шины имеют биты контроля четности, которые можно сравнивать. После распознавания ошибки по четности на одной стороне соответствующий процессор отделяют, так что он в системе больше ни на что не влияет. После каждой ошибки синхронизации (lockstep error), которая появляется без ошибки по четности, систему отключают. Этот базирующийся на проверке четности принцип работы не предлагает достаточной защиты от тех случаев, когда возможность использования резервной системы очень желательна даже после появления ошибки синхронизации. Проверка четности может привести, например, к неправильному решению, если два внутренних резервных блока одновременно показывают разные ошибки в двоичном разряде.

Другие известные помехоустойчивые архитектуры системы включают в себя, по меньшей мере, три ядерных процессора с раздельно или совместно используемой памятью. При этом синхронную работу процессоров постоянно проверяют путем слежения за сигналом шины. Далее синхронная работа обозначена как синхронное выполнение процессорами программы или частей программы.

Если активный процессор дает сбой, то «собственность» переходит к другому процессору через область памяти и компоненты, которыми управляет активный процессор через каналы ввода и вывода данных. В состоянии неисправности из-за нарушения синхронизации, которая следует за блокирующей ошибкой шага, доступ к данным и процессы управления в активном процессоре прекращаются и поддерживаются другим процессором.

Классическая минимальная конфигурация, состоящая из тройного модульного резервирования процессоров и совместно используемой памяти, для помехоустойчивой системы представляет собой довольно дорогое решение для многих архитектур безопасности, у которых концепция надежности базируется на применении двух резервных, синхронно работающих процессоров. Помехоустойчивость представляет собой, однако, особую задачу для процессоров с двойным резервированием.

В патенте US 7366948 В2 и US 2006/0107106 описан способ поддержки безотказности эксплуатации системы, состоящей из нескольких пар процессоров, работающих в синхронном режиме. В каждой паре объединены резервные процессоры, выходные сигналы которых постоянно сравнивают. Если в одной паре процессоров появляется погрешность, управление системой берет на себя другая пара процессоров в качестве загрузочной пары. Между тем пара процессоров, в которой возникла ошибка, пытается вернуть синхронизацию и выступить в качестве запасной пары процессоров. Тем самым достигается безотказность работы системы. Этот способ, однако, слишком дорогой для многих встроенных систем, так как одну пару процессоров не используют в случае отсутствия ошибки, и описанный способ предлагает, таким образом, плохое соотношение цены и качества. Четыре процессора, разделенных на две пары, у которых попарно сравнивают выходные сигналы, должны всегда выполнять одну единственную задачу. Если обнаруживается ошибка синхронизации (прекращение синхронизации) или другая погрешность внутри процессора процессорной пары, рабочая система останавливает неисправную пару процессоров и активизирует другую пару.

В патенте ЕР 1380953 В1 описана помехоустойчивая компьютерная система с синхронизацией, которая содержит множество вычислительных модулей с одним процессором и памятью и способ для его повторной синхронизации. Так как каждый вычислительный модуль синхронно выполняет одни и те же команды, эта вычислительная система является малоэффективной.

В патенте ЕР 1456720 В1 описан вычислительный комплекс для критичного с точки зрения безопасности применения в автомобилях, состоящий из нескольких контрольно-вычислительных систем, каждая из которых содержит два работающих синхронно в такт управляющих вычислительных устройства с частично или полностью резервными периферийными элементами и частично или полностью резервными элементами памяти, которые встроены в чип. Работающие синхронно в такт управляющие вычислительные устройства контрольно-вычислительной системы связаны с блоком арбитрирования, который проверяет их на наличие погрешностей и подключает коммуникационный контроллер, приданный контрольно-вычислительной системе, к шине данных автомобиля или отключает его. При работе со сбоями одного управляющего вычислительного устройства соответствующую контрольно-вычислительную систему частично или полностью отключают.

Из патента DE 102009000045 А1 известно устройство для эксплуатации устройства управления, которое имеет вычислительную систему из двух пар, каждая из которых имеет два исполнительных блока и, в частности, применяется в автомобиле. Исполнительные блоки каждой пары выполняют одну и ту же программу, а выходные сигналы каждого исполнительного блока сравнивают между собой с помощью блока сравнения, и при появлении отклонения подается сигнал об ошибке. Если сигнал поступает для первой пары исполнительных блоков, то ее отключают, а вычислительная система работает дальше со второй парой исполнительных блоков, причем водитель получает предупредительный сигнал.

Указанные источники имеют недостатки, заключающиеся в том, что должно сохраняться высокое резервирование, так как и в случае исправной работы не действует, по меньшей мере, одна процессорная пара или выполняет ту же программу, что и активная пара, которая управляет периферийными устройствами. Поэтому каждый отдельный процессор должен подготовить общие необходимые вычислительные возможности, в результате чего известные вычислительные системы работают малоэффективно. Это нежелательно по причине стоимости, в частности для систем, изготовленных большими партиями.

Описанный в патенте US 7366948 В2 способ представляет собой очень дорогостоящее техническое решение для встроенных систем. К тому же имеется тот факт, что другие компоненты, кроме ядер процессоров, не всегда можно реализовать с резервированием. Обычным образом причины стоимости играют важную роль при разработке архитектур надежности для различных важных с точки зрения безопасности систем, например при применение тормоза. Программная память, например флэш-память, не является резервной, а используется всеми имеющимися процессорами. Традиционные способы не рассматривают это основное условие нерезервированных компонентов в связи с обеспечением безотказности эксплуатации архитектур безопасности, базирующихся на резервных процессорах. Другая проблема, касающаяся обеспечения безотказности работы процессоров в архитектурах безопасности, заключается в том, что ввод в действие ранее неисправного процессора может произойти только после успешно завершенной и надежной проверки.

Исходя из этого, имеется потребность в архитектуре надежности только с двумя резервными процессорами, которые дают возможность эксплуатировать систему с высокой степенью безотказности при работе. Кроме того, имеется потребность в архитектуре надежности с тремя или более трех процессорами, например с двумя процессорами, каждый - по два ядра, которые дают возможность эксплуатации с высокой степенью безотказности.

Согласно одному из аспектов задачей предложенного изобретения является создание контрольно-вычислительной системы, одновременно помехоустойчивой и эффективной.

Согласно одному из вариантов выполнения изобретения архитектура надежности, базирующаяся на парах резервных ядерных процессоров, построена так, что уже имеющиеся ступени надежности остаются и обеспечивается высокая степень безотказности при эксплуатации системы. Наряду с этим процессоры при нормальной работе (без ошибок) должны показать высокую работоспособность. После обнаружения ошибки безотказная эксплуатация системы должна поддерживаться с учетом надежной привязки нерезервных компонентов.

Исходя из этого, создана контрольно-вычислительная система по п.1. Кроме того, подготовлено двухпроцессорное устройство управления. Помимо этого подготовлен способ управления контрольно-вычислительной системой по пп.22-33. И далее описано применение контрольно-вычислительной системы по п.32.

Согласно примеру выполнения создана контрольно-вычислительная система. Контрольно-вычислительная система включает в себя, по меньшей мере, два резервных модуля; по меньшей мере, один блок сравнения для контроля состояния синхронизации, по меньшей мере, два резервных модуля для обнаружения ошибки синхронизации; по меньшей мере, один периферийный блок; по меньшей мере, одну переключающую матрицу, которая предназначена для разрешения доступа или блокировки доступа, по меньшей мере, к двум резервным модулям или доступа, по меньшей мере, двух резервных модулей к периферийному блоку. Кроме того, контрольно-вычислительная система включает в себя блок обнаружения и устранения ошибки, предназначенный для улавливания сигналов, по меньшей мере, одного блока сравнения и управления, по меньшей мере, одной переключающей матрицей в целях воспрепятствования - в целом или выборочно - доступа, по меньшей мере, к двум резервным модулям или доступа, по меньшей мере, двух резервных модулей к периферийному блоку.

В случае обнаружения ошибки доступ к неисправному модулю или доступ неисправного модуля к периферийному устройству исключается благодаря переключающей матрице, которой управляет блок обнаружения и устранения ошибки. Согласно одной форме выполнения блок обнаружения и устранения ошибки инициирует и контролирует один или несколько тестов для проверки резервных модулей на наличие ошибки и управляет переключающей матрицей при распознавании ошибки таким образом, что неисправный модуль больше не учитывают, в частности, при существенном для безопасности применении.

Согласно одной из форм выполнения, по меньшей мере, два резервных модуля, по меньшей мере, двух процессорных блоков для синхронного выполнения программы управления или другие блоки выполнены, например, в виде резервных модулей памяти.

Согласно одной форме выполнения контрольно-вычислительная система включает в себя, по меньшей мере, четыре процессорных блока, причем процессорные блоки могут быть отдельными процессорами, процессорными парами или ядрами двухъядерных или многоядерных процессоров.

Согласно одной из форм выполнения архитектура надежности, базирующаяся на паре резервных процессорных ядер, устроена так, что неисправная пара процессоров, одно отдельное неисправное ядро процессора, имеющего, по меньшей мере, два процессорных ядра, и/или неисправные компоненты исключаются из управления существующих исполнительных элементов, так как независимый модуль после обнаружения ошибки блокирует любой доступ неисправной процессорной пары к важным для безопасности периферийным блокам. Пара или пары процессоров или процессорное ядро или процессорные ядра или неисправные компоненты исключаются из нормальной работы для обеспечения работы в аварийном режиме. В аварийном режиме каждая пара процессоров или каждое исправное ядро процессора принимают на себя по необходимости некоторые задачи неисправной пары процессоров или ядра процессора и выполняют дальше множество первоначальных задач. Для каждой пары процессоров или для каждого ядра процессоров программы, относящиеся к математическому обеспечению и направленные на выполнение задачи, делятся на две группы. Одна группа программ, относящихся к математическому обеспечению, должна функционировать как в нормальном режиме, так и в аварийном, тогда как программы математического обеспечения другой группы при аварийном режиме работы отключаются. Таким образом, исправная процессорная пара или исправное ядро процессора имеют возможность принимать на себя в аварийной ситуации дополнительные задачи. Каждый компонент программного обеспечения относят на случай аварийной ситуации к определенным категориям как годный/негодный и/или способный отказать/неспособный отказать. Если пара процессоров пара или ядро процессора неисправны, то задачи, необходимые для чрезвычайной ситуации, принимает на себя исправная пара процессоров пара или исправное ядро процессора.

В предпочтительном примере выполнения изобретения стремятся возобновить нормальную работу архитектуры надежности, из-за чего неисправную пару процессоров пара или неисправное ядро процессора подвергают целому ряду проверочных тестов. Во время проведения этих тестов эта процессорная пара или ядро процессора выдает разные результаты, которые должны совпасть с результатами проведенных алгоритмов, известных ранее. При этом независимый модуль, содержащий аппаратные средства, проверяет точность результатов. После успешной проверки условий возобновления работы все процессорные пары или ядра процессоров возвращаются к нормальной работе.

Благодаря тому, что заявленная контрольно-вычислительная система может блокировать доступ неисправной процессорной пары или неисправного ядра процессора к периферии, в результате срабатывания исполнительного элемента неисправной процессорной пары или неисправного ядра процессора устраняют причиненный вред.

В случае отсутствия ошибки отдельные пары процессоров, или ядро процессора, или ядра процессоров заявленной контрольно-вычислительной системы выполняют разные программы, благодаря чему достигается высокая производительность вычислений. Если появляется ошибка, то исправная процессорная пара, или исправное ядро процессора, или ядра процессоров принимают на себя критические функции неисправной процессорной пары или ядер процессора, между тем как некоторые некритические функции больше не предоставляются. Эта чрезвычайная ситуация дает возможность высокой помехоустойчивости заявленной контрольно-вычислительной системы.

Изобретение относится также к применению заявленной контрольно-вычислительной системы в автомобиле, в частности для управления или регулирования тормозной системы.

Согласно одной или нескольким примерам выполнения контрольно-вычислительная система, например, в форме резервного двухпроцессорного устройства управления включает в себя первый процессор (или первое ядро процессора) и второй процессор (или второе ядро процессора) для синхронного выполнения программы управления, по меньшей мере, один первый умножитель для выборочного связывания, по меньшей мере, одного управляемого первого периферийного блока с одним из двух процессоров, и, по меньшей мере, один первый блок сравнения (компаратор) для контроля за состоянием синхронности обоих процессоров и для обнаружения ошибки синхронизации. Кроме того, контрольно-вычислительная система (устройство управления) включает в себя переустановочное контрольное устройство (обозначенное в некоторых примерах выполнения как SVM-модуль), предназначенное для контроля выполнения, по меньшей мере, одной тестовой программы обоими процессорами после появления ошибки синхронизации и оценки результатов тестирования, и, кроме того, для создания конфигурации, по меньшей мере, первого умножителя.

С помощью блока сравнения наблюдают за синхронной работой процессоров, т.е. за работой «шаг в ногу». Это может происходить за счет того, что выполнение программы управления сравнивают «построчно», причем должны быть получены одинаковые результаты в одно и то же время. Если этого нет, то налицо ошибка синхронизации или сдвиг, т.е. процессоры больше не работают синхронно.

Синхронное выполнение программы управления является важным признаком резервной системы, так как с ее помощью можно проверить, работает ли процессор, активный в настоящий момент, без ошибок, причем при этом допускается, что одновременное появление одной и той же ошибки в обоих процессорах является статистически очень неправдоподобным. При появлении ошибки синхронизации, тем не менее, сначала неясно, где произошла ошибка - в активном или пассивном процессоре (ядре). Под активным процессором (ядром) здесь нужно понимать процессор, который фактически управляет периферийным блоком. Пассивным процессором (ядром) является тот, который лишь синхронно выполняет совместную работу, т.е. он содержит те же данные и выполняет те же шаги программы, что и активный процессор.

Таким образом, при появлении ошибки синхронизации больше нет гарантии того, что управление будет выполнено точно, т.е. существует риск, в частности, в системах, отвечающих за безопасность, которые существуют, например, в автомобилях, а также в других системах. Обычно система управления, показанная, например, на фиг.7 и 8, должна быть полностью отключена.

В предложенном здесь решении предусмотрено переустановочное контрольное устройство (независимый модуль с аппаратными средствами), которое при появлении ошибки синхронизации тестирует оба процессора (ядра), чтобы определить, какой из двух процессоров содержит ошибку. После проведения теста и оценки результатов тестирования переустановочное контрольное устройство решает, какие дальнейшие шаги предпринять.

Поскольку тестируют оба процессора, то исходят из того, что оба процессора исправны. В этом случае синхронное выполнение программы управления продолжается.

Это решение имеет сокрушительное преимущество, заключающееся в том, что управление периферийным блоком может продолжаться при сохранении высокой степени безопасности, так как оба процессора подверглись тесту на исправность. Это представляет собой решающее преимущество в отличие от других решений, в которых после появления ошибки синхронизации происходит в принципе полное отключение, и систему можно снова восстановить только извне. При этом следует учитывать, что простое восстановление системы для безопасного применения зачастую не представляет собой удовлетворительное решение, так как не было оценки ошибок, т.е. осталось неизвестным, что именно привело к ошибке синхронизации. Описанное здесь решение предлагает путь уйти от ошибок синхронизации и восстановить синхронизацию двух резервных систем после «сдвига шага» или ошибки синхронизации.

Если, наоборот, процессор (ядро) считают неисправным, то устройство управления (контрольно-вычислительная система) меняет конфигурацию с помощью переустановочного контрольного устройства (SVM-модуля). И причем так, что выходные данные процессора, содержащего ошибку, отныне игнорируются и обеспечивается то, что теперь периферийным блоком может управлять только исправный процессор, но ни в коем случае не процессор, содержащий ошибку. Обычно это происходит за счет изменения конфигурации первого умножителя, так что поток данных все еще возможен между периферийным блоком и исправным процессором. Кроме того, изменение конфигурации приводит к тому, что блок сравнения больше не осуществляет контроль.

Это решение имеет такое решающее преимущество, что управление периферийным блоком можно продолжить, даже если это происходит без резервирования со стороны процессора. Это является значительным преимуществом в отличие от известных решений, в которых управление при появлении ошибки синхронизации полностью отключается. Предложенное решение повышает при этом степень безотказности системы при эксплуатации, что особенно важно при критических применениях, чтобы контроль и дальше поддерживался системой. Устройство управления может, тем не менее, подавать сигнал об ошибке, чтобы указать на работу теперь одного процессора, так что теперь можно провести техническое обслуживание.

Предложенное здесь резервное устройство управления со средствами для регулирования ошибки синхронизации можно применять в любых системах, отвечающих за безопасность. Примером тому является применение тормозов в автотранспортных средствах. При этом устройство управления, базирующееся только на двух резервных процессорах, выполнено так, что оно сохраняет имеющиеся ступени безопасности и дает возможность безотказной работы системы.

Под управляемым периферийным блоком можно понимать в принципе каждый блок, к которому получает доступ соответствующий процессор. Примерами являются блоки памяти, исполнительные элементы, блок ввода и вывода данных и датчики.

Согласно одному или нескольким примерам выполнения переустановочное контрольное устройство настроено так, чтобы причислить ошибку синхронизации к определенному типу ошибок и исходя из типа ошибок выбрать тестовую программу. Возникшую ошибку анализируют, чтобы выяснить, где могла произойти ошибка или каким из компонентов она была вызвана. На этом основании затем выбирают подходящую тестовую программу, причем тестовую программу, а также полученные результаты тестирования сначала записывают в память, например в переустановочное контрольное устройство. Если обнаруживается ошибка, т.е. разница в выходных данных обоих процессоров в разном адресе памяти, то можно, например, выбрать тестовую программу, с помощью которой распознать сбой памяти. Такой подход к решению совершенствует определение места неисправности.

Согласно одному или нескольким примерам выполнения переустановочное контрольное устройство (SVM-модуль) настроено на создание конфигурации первого умножителя на базе результатов тестирования. Конфигурация умножителя и вообще устройства управления задается в зависимости от результатов тестирования. Возможно, чтобы функцию умножителя взяла на себя шинная матрица.

В соответствии с одним или несколькими примерами выполнения устройство управления имеет, кроме прочего, по меньшей мере, один второй умножитель для избирательной связи, по меньшей мере, одного управляемого второго периферийного блока с одним из двух процессоров, причем для второго умножителя конфигурацию задает переустановочное контрольное устройство. Устройство управления дает возможность выборочного управления несколькими периферийными блоками с учетом аспектов безопасности.

Согласно одному или нескольким примерам выполнения устройство управления имеет, кроме того, по меньшей мере, один второй блок сравнения (компаратор) для контроля состояния синхронизации обоих процессоров и для распознавания ошибки синхронизации. Он делает возможным попеременный контроль и повышает тем самым безопасность системы.

Согласно одному или нескольким вариантам выполнения изобретения устройство управления имеет первую шинную матрицу, которая связывает первый процессор с первым умножителем, и вторую шинную матрицу, которая связывает второй процессор со вторым умножителем.

В соответствии с одним или несколькими примерами выполнения первый периферийный блок является общим блоком, которым может управлять избирательно один из двух процессоров. Кроме того, устройство управления имеет согласно одному варианту выполнения, по меньшей мере, два других периферийных блока, причем с первым процессором связан только один из двух периферийных блоков, а со вторым процессором связан только другой из двух периферийных блоков в качестве собственных периферийных блоков, к которым в каждом случае может иметь доступ только соответствующий процессор. Под общим периферийным блоком или компонентом здесь следует понимать устройство, управляемое с резервированием, т.е. управление происходит избирательно с помощью одного из двух процессоров, причем другой служит для сравнения. Собственным блоком, наоборот, управляет каждый раз только один из двух процессоров. Соответственно другой процессор не имеет доступа к этому блоку даже через умножитель или умножители. Представленное здесь решение позволяет снова наладить синхронность между двумя резервными процессорами с учетом нерезервных компонентов, которые обычно внедряются в различные встроенные системы из-за стоимости.

В соответствии с одним или несколькими примерами выполнения два других периферийных блока являются резервными блоками, т.е. в физическом смысле они идентичны и предназначены для выполнения той же функции.

Согласно одной или нескольким вариантам выполнения первый и/или второй блок сравнения настроены на формирование сигнала об ошибке в синхронизации при появлении такой ошибки. Сигналом об ошибке в синхронизации может быть, например, сигнал прерывания.

В соответствии с одним вариантом выполнения контрольно-вычислительная система создана, например, как резервное двухпроцессорное устройство управления, Контрольно-вычислительная система включает в себя: первый процессор и второй процессор для синхронного выполнения программы управления; по меньшей мере, один первый умножитель для избирательной связи общего первого периферийного блока с одним из двух процессоров; по меньшей мере, два других периферийных блока, причем один из двух периферийных блоков связан только с первым процессором, а другой из двух периферийных блоков - только со вторым процессором в качестве собственных периферийных блоков, к которым имеет доступ только соответствующий процессор; по меньшей мере, первый блок сравнения для проверки состояния синхронизации обоих процессоров и для распознавания ошибки синхронизации, если оба процессора теряют синхронность; переустановочное контрольное устройство, настроенное на проверку выполнения, по меньшей мере, одной тестовой программы с помощью обоих процессоров после появления ошибки синхронизации и оценку результатов тестирования и создание конфигурации первого умножителя на базе результатов тестирования.

В соответствии с одним вариантом выполнения контрольно-вычислительная система включает в себя, кроме прочего: первую шинную матрицу, которая связывает первый процессор с первым умножителем; вторую шинную матрицу, которая связывает второй процессор с первым умножителем.

Согласно одной форме выполнения контрольно-вычислительная система создана, например, в виде резервного двухпроцессорного устройства управления и включает в себя: первый процессор и второй процессор для синхронного выполнения программы управления; по меньшей мере, один первый и один второй периферийный блок; по меньшей мере, один первый умножитель для избирательной связи первого периферийного блока с одним из двух процессоров; по меньшей мере, один второй умножитель для избирательной связи второго периферийного блока с одним из двух процессоров; по меньшей мере, один первый и один второй блок сравнения для соответствующей проверки состояния синхронизации обоих процессоров и для распознавания ошибки синхронизации; переустановочное устройство, настроенное на проверку выполнения, по меньшей мере, одной тестовой программы с помощью обоих процессоров после появления ошибки синхронизации и на оценку результатов тестирования и на создание конфигурации первого и второго умножителя на базе результатов тестирования.

Согласно одному варианту выполнения контрольно-вычислительная система, например, в форме резервного двухпроцессорного устройства управления включает в себя: первую шинную матрицу, которая соединяет первый процессор с первым умножителем; вторую шинную матрицу, которая соединяет второй процессор со вторым умножителем.

В соответствии с одним или несколькими вариантами выполнения изобретения подготавливают способ управления. Способ управления заключается в синхронном выполнении программы управления с помощью первого и второго процессоров, которые связаны через умножитель, по меньшей мере, с одним управляемым периферийным блоком, причем только один из двух процессоров управляет периферийным блоком в определенное время. Синхронное выполнение программы управления проверяется с помощью блока сравнения. Сигнал об ошибке синхронизации подается тогда, когда оба процессора теряют синхронизацию. После выхода сигнала об ошибке синхронизации обоих процессоров выполнение программы управления прерывается. Затем проводится проверочный тест на неисправность одного из двух процессоров. Если оба процессора исправны, то они оба продолжают синхронное выполнение программы управления. Если, наоборот, установлено, что один из процессоров содержит ошибку, умножителю и блоку сравнения задают конфигурацию таким образом, что прекращается дальнейшая связь с неисправным процессором и проводится дальнейшая проверка с помощью блока сравнения и что процессор, не содержащий ошибку, управляет периферийным блоком. Выполнение программы управления продолжает исправный процессор. Если оба процессора содержат ошибку, происходит отключение управления.

Согласно одному или нескольким вариантам выполнения тест заключается в одновременном выполнении двумя процессорами, по меньшей мере, одной тестовой программы, причем один процессор рассматривают как неисправный, если выполнено, по меньшей мере, одно из следующих условий:

- процессор не выполнил тестовую программу в течение первого интервала времени Т1,

- процессор не выполнил тестовую программу успешно,

- по истечении первого интервала времени Т1 процессор не перешел в состояние покоя для второго промежутка времени Т2.

Тем самым учитывают не только правильное или неправильное выполнение, но также определяют, выполнили ли процессоры тест в течение заданного времени. Проверка состояния покоя служит для определения, выводит ли процессор, несмотря на это, данные, хотя он и не выполняет никаких инструкций. Это так же свидетельствует об ошибке в процессоре.

В соответствии с одним или несколькими примерами выполнения ошибку синхронизации оценивают и определяют ее тип, причем для проверки процессоров выбирают, по меньшей мере, одну тестовую программу в зависимости от типа ошибки. Таким образом, можно выбрать одну или при необходимости несколько специальных для этой ошибки тестовых программ.

Другие варианты выполнения, модификации и преимущества представлены в дальнейшем описании, на чертежах и в пунктах формулы изобретения. Изобретение описывается с помощью конкретных примеров выполнения, представленных на фигурах. Однако они не должны рассматриваться как ограничивающие. Из последующего описания для специалиста понятны другие модификации, которые должны быть включены в область охраны.

Фиг.1 контрольно-вычислительная система в виде устройства управления

согласно форме выполнения в нормальном режиме,

Фиг.2 контрольно-вычислительная система (устройство управления) при

наличии помех в процессоре,

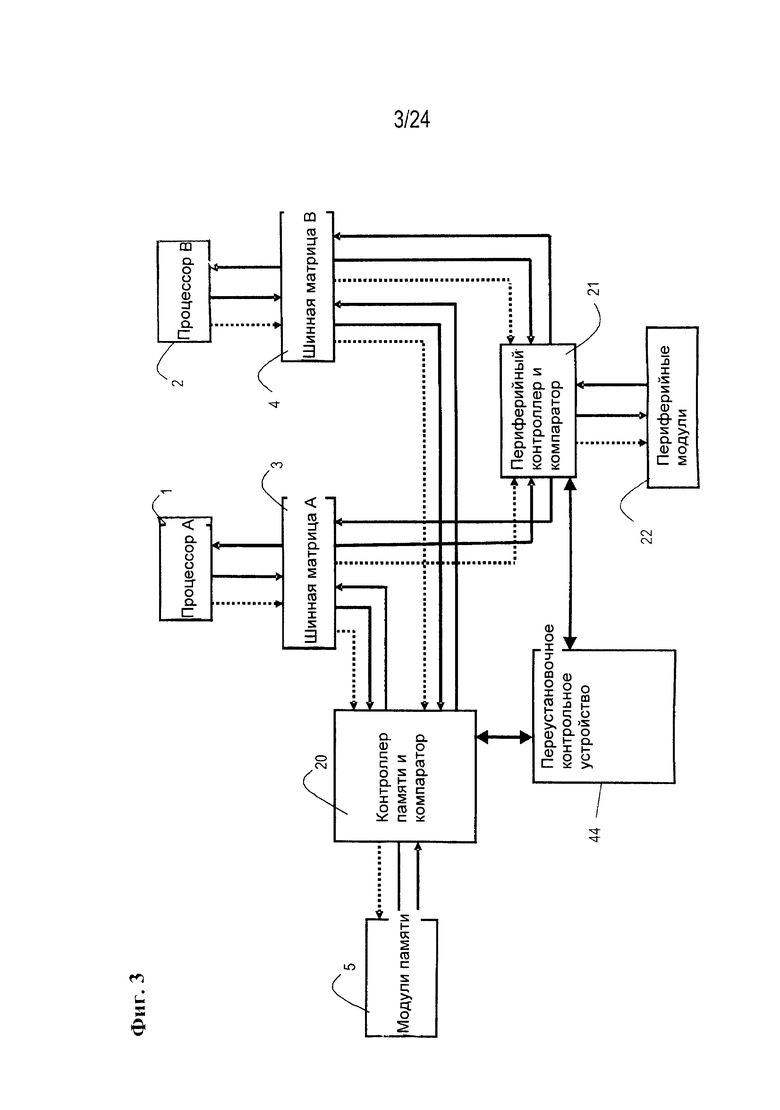

Фиг.3 контрольно-вычислительная система в виде устройства управления

согласно форме выполнения,

Фиг.4 контрольно-вычислительная система в виде устройства управления

согласно форме выполнения,

Фиг.5 контрольно-вычислительная система в виде устройства управления

согласно форме выполнения,

Фиг.6 выполнение программы управления согласно форме выполнения,

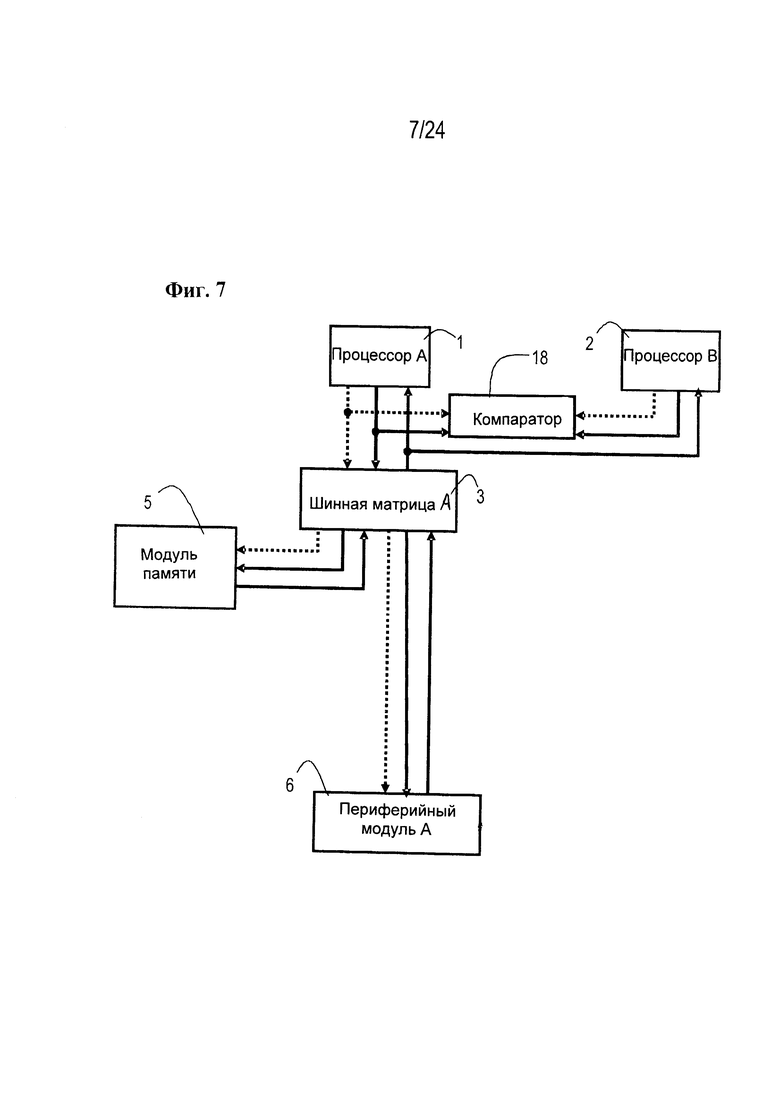

Фиг.7 архитектура с двумя процессорами,

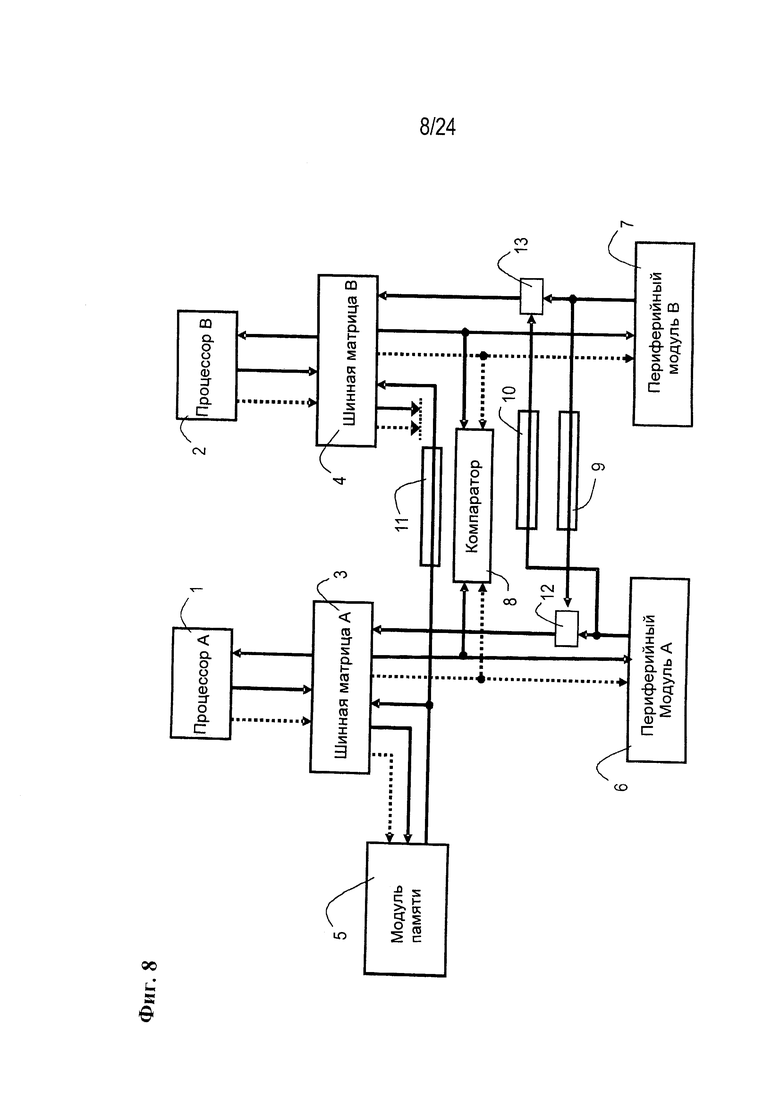

Фиг.8 архитектура с разделением периферийных модулей на две группы А и В,

Фиг.9 контрольно-вычислительная система,

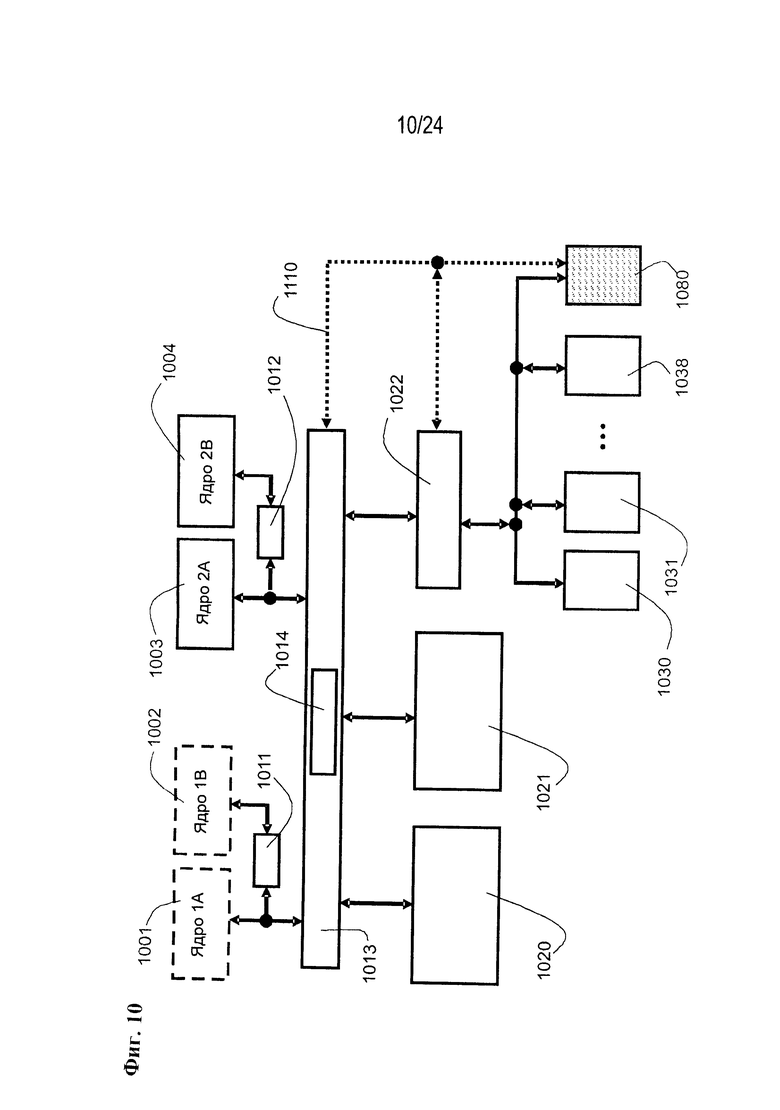

Фиг.10 контрольно вычислительная система согласно форме выполнения,

Фиг.11 план выполнения способа обнаружения и устранения ошибки согласно форме выполнения,

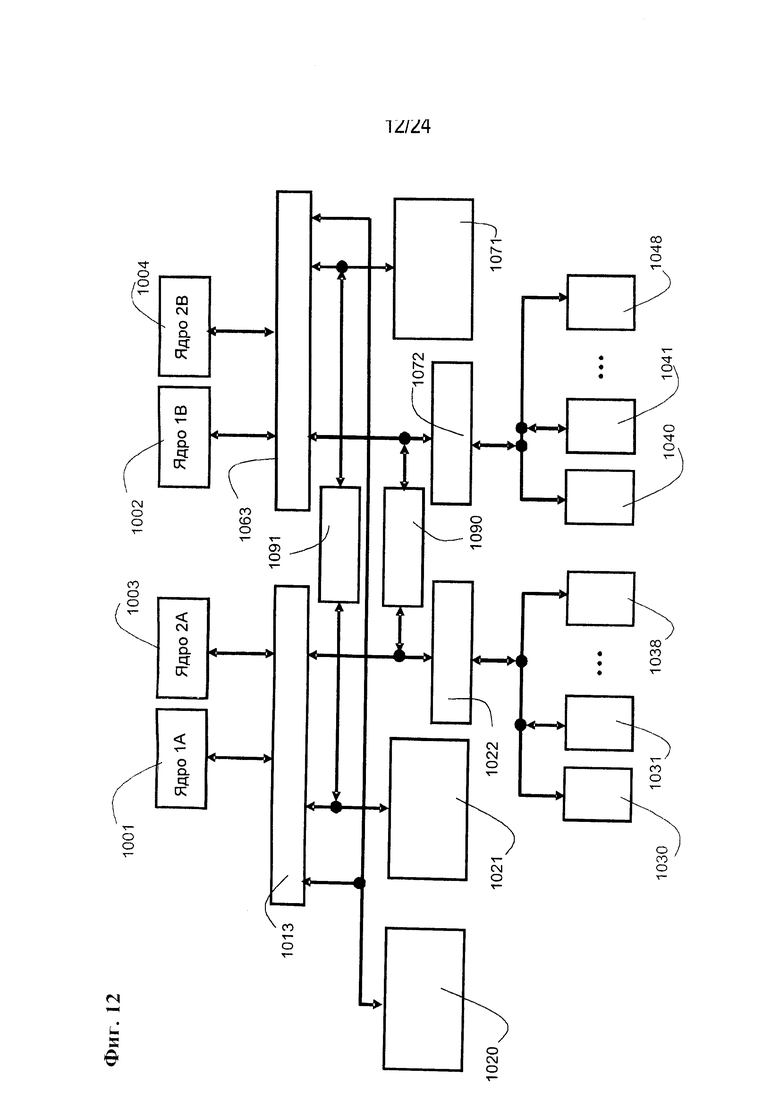

Фиг.12 другая контрольно-вычислительная система,

Фиг.13 контрольно-вычислительная система согласно форме выполнения,

Фиг.14 заявленная контрольно-вычислительная система в архитектуре фиг.13 с отключенным ядром процессора 2В после успешной переустановки.

Фиг.15 заявленная контрольно-вычислительная система в архитектуре фиг.13 с отключенными ядрами процессоров 1А и 2В после успешной переустановки.

Фиг.16 заявленная контрольно-вычислительная система в архитектуре фиг.13 с отключенными ядрами процессора 1В и 2В после успешной переустановки.

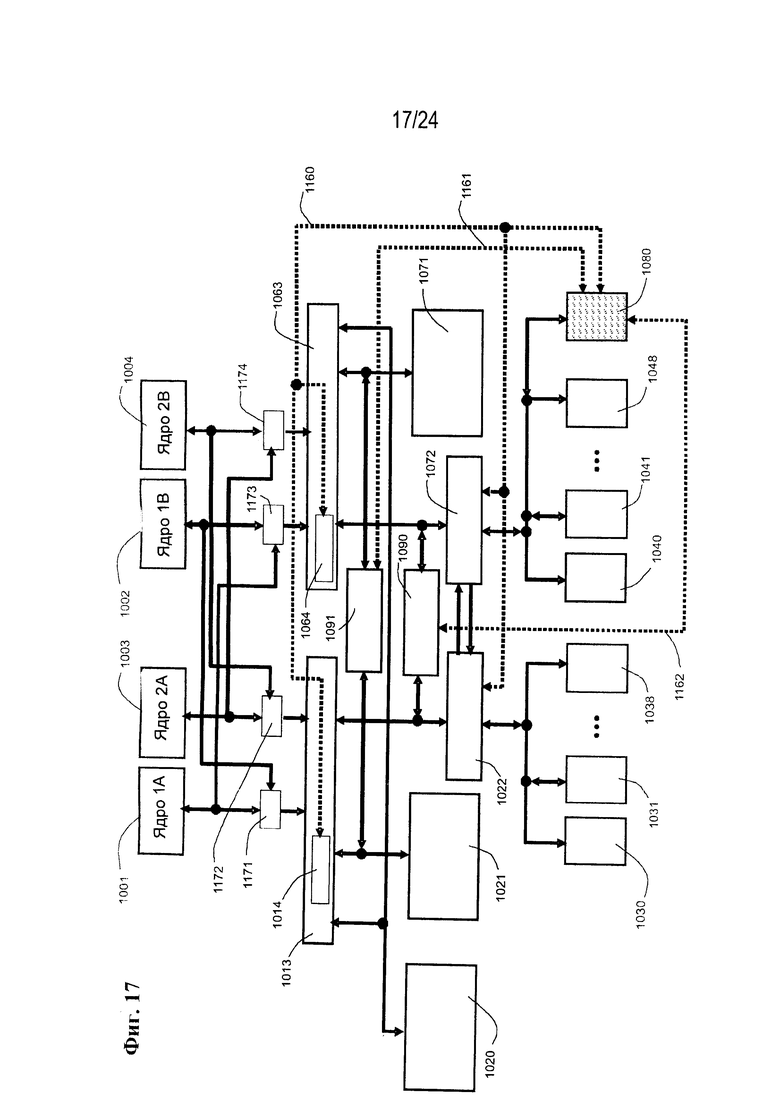

Фиг.17 контрольно-вычислительная система согласно форме выполнения.

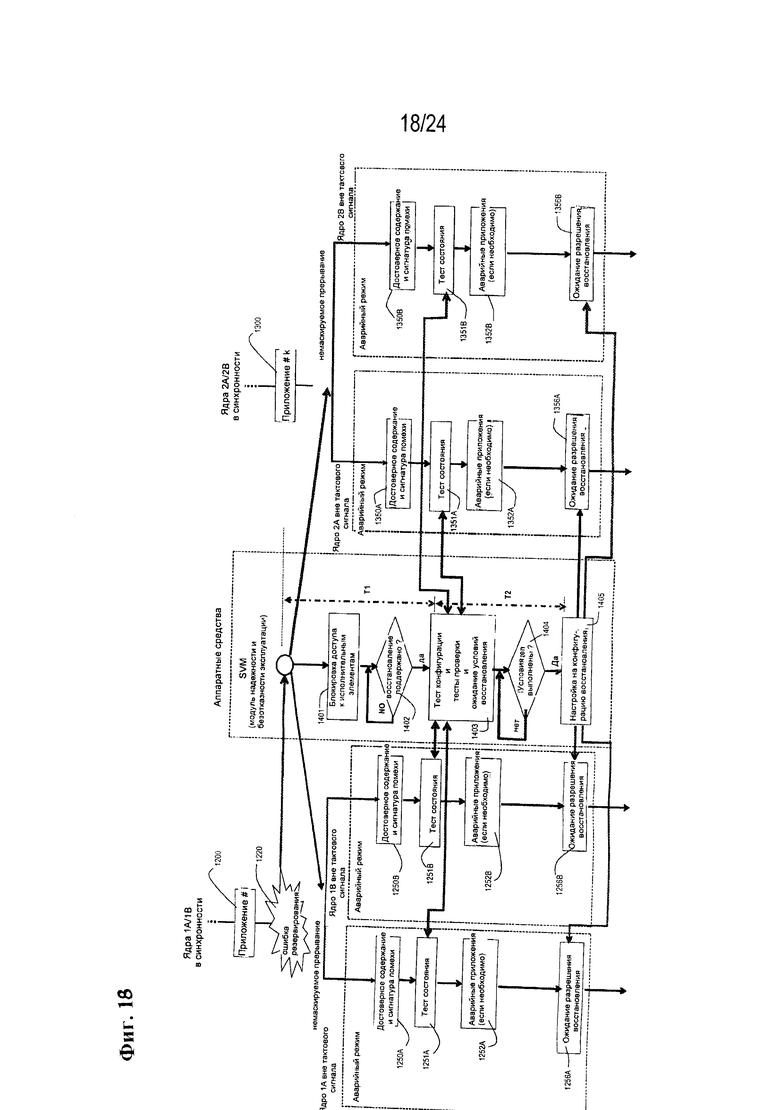

Фиг.18 план выполнения способа для обнаружения и устранения ошибки согласно форме выполнения,

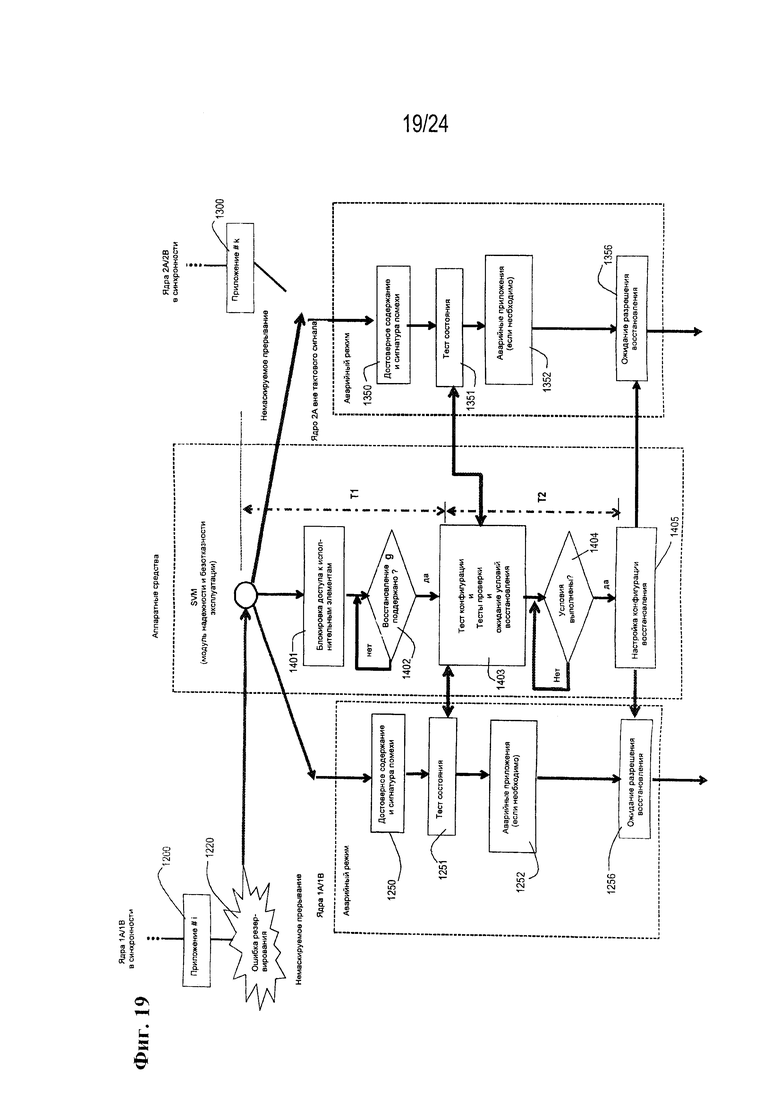

Фиг.19 план выполнения способа обнаружения и устранения ошибки согласно форме выполнения,

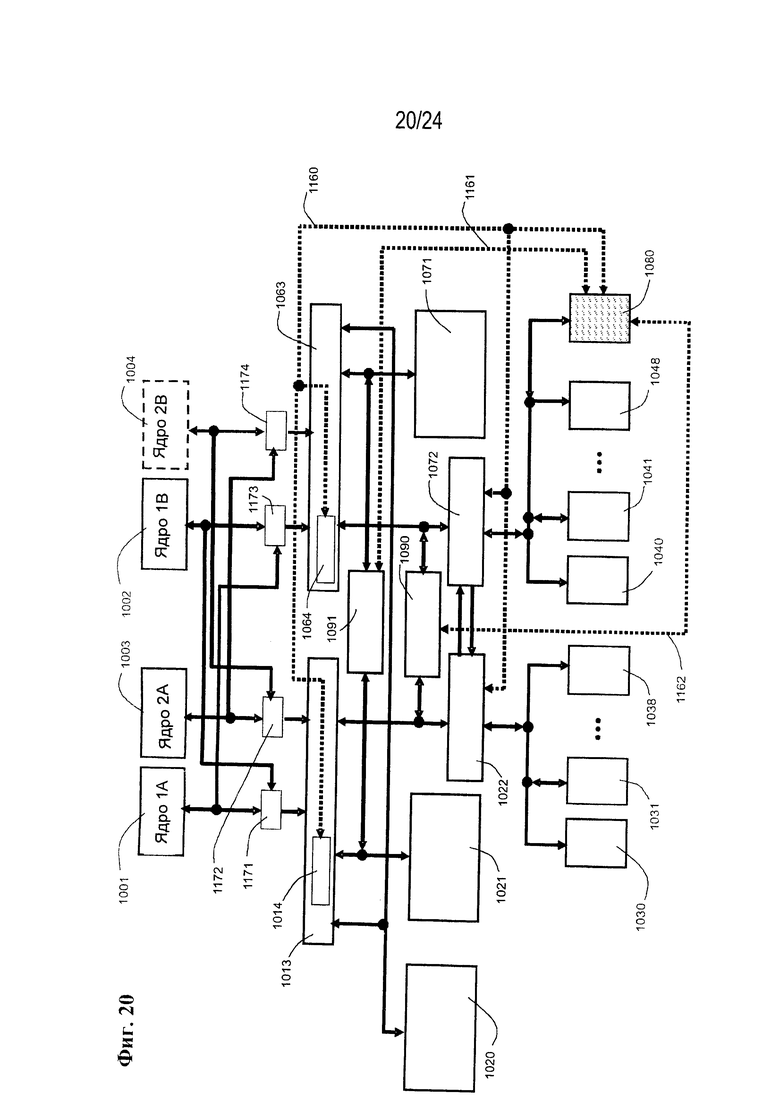

Фиг.20 архитектура фиг.17 с отключенными ядрами процессора 2В после переустановки,

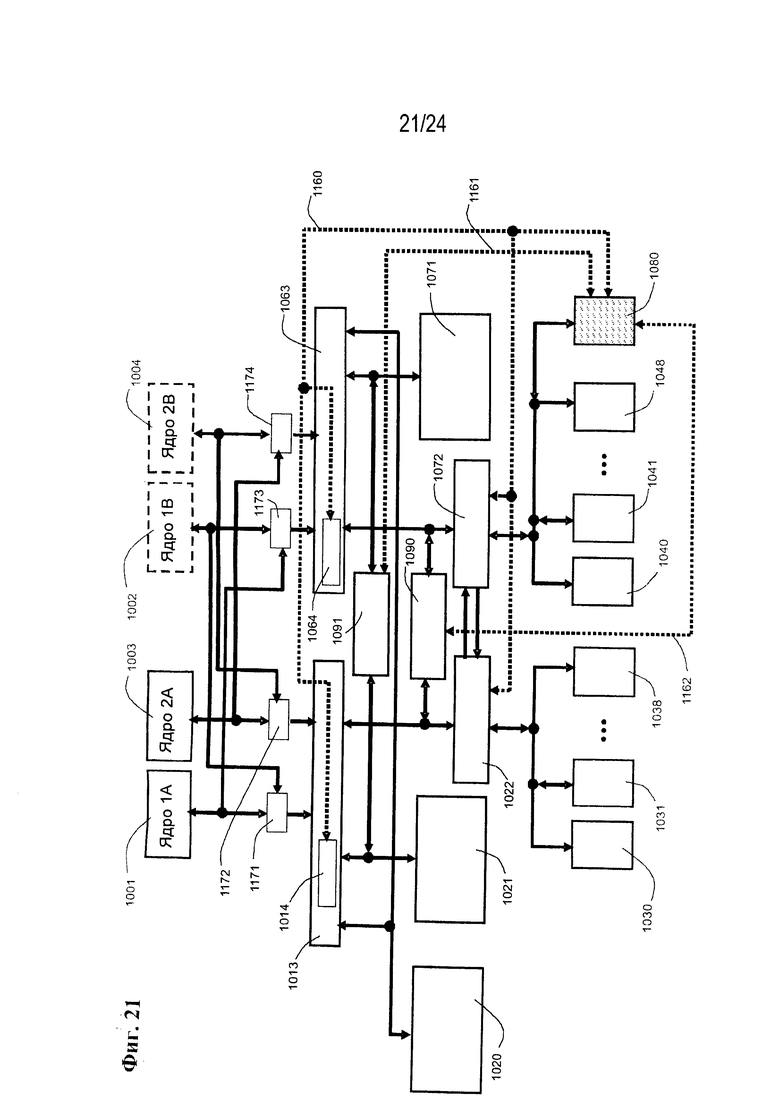

Фиг.21 архитектура фиг.17 с отключенными ядрами 1В и 2В после переустановки,

Фиг.22 архитектура фиг.17 с отключенными ядрами процессора 1А, 2А и 1В после переустановки,

Фиг.23 архитектура фиг.17 с отключенными ядрами процессора 1А и 2В после переустановки,

Фиг.24 архитектура фиг.17 с отключенной памятью для данных 21 после переустановки.

На фиг.1 схематично изображена контрольно-вычислительная система или устройство управления с первым и вторым процессорами 1, 2 и первым и вторым умножителями 91, 92. Каждый умножитель 91, 92 образует блок со своим устройством сравнения, обозначенным на фигурах как компаратор. Каждый умножитель 91, 92 связан со своим периферийным блоком 95, 96 и дает возможность избирательного доступа процессоров 1, 2 к периферийным блокам 95, 96. Переустановочное контрольное устройство 44 связано как с обоими процессорами 1, 2, так и с умножителями 95, 96.

Что касается процессоров 1, 2, то речь может идти также и о ядрах процессоров.

На фиг.1 жирной стрелкой обозначен реальный поток данных от процессоров 1, 2 к периферийным блокам 95, 96, переданных умножителями 91, 92. Процессор 1 связан с периферийным блоком 95 и управляет им, а процессор 2 связан с периферийным устройством 96 и управляет им. Процессор 1, умножитель/компаратор 91 и периферийный блок 95 образуют здесь ветвь А, тогда как процессор 2, умножитель/компаратор 92 и периферийный блок 96 образуют ветвь В. Разумеется, имеются перекрещивающиеся пути связи, а именно, во-первых, между процессором 2 и умножителем/компаратором 91, а во-вторых, между процессором А и умножителем/компаратором 92.

Каждый компаратор 91, 92 сравнивает, работают ли процессоры синхронно между собой, т.е. выдают ли они одновременно одинаковые результаты. Если нет, то налицо ошибка синхронизации. В этом случае процессоры тестируют и в зависимости от этого задают другую конфигурацию устройству управления. Это схематично представлено на фиг.2.

На фиг.2 предполагается, что тест, с помощью которого переустановочное контрольное устройство 44 проводит проверку и оценку, определяет, что процессор 1 содержит ошибку. В этом случае обоим умножителям 91, 92 задают другую конфигурацию и именно такую, что оба умножителя 91, 91 игнорируют выходные данные процессора 1. Одновременно умножитель 91 создает теперь связь между процессором 2 и периферийным блоком 95. Теперь процессор 2 управляет периферийными блоками как в ветви А, так и в ветви В. Для этого процессор 2 необязательно нужно перепрограммировать, так как в любом случае процессор 2 с целью сравнения уже выполнил программу управления для периферийного блока 95 (ветвь А) в нормальном состоянии. Отличие только в том, что он теперь может обратиться к периферийному блоку 95 также «письменно». Кроме того, деактивизируется функция сравнения компараторов, так как они теперь больше не получают никаких входных данных от процессора 1. Это требуется для того, чтобы компараторы 91, 92 не выдавали никаких других сигналов об ошибке.

В результате выполнение программы управления, включая программы управления для периферийного блока 95 и периферийного блока 96, можно снова продолжить процесс. Благодаря этому надежность системы при эксплуатации повышается.

Если тест показал, что оба процессора 1, 2 исправны, т.е. не содержат ошибок, снова возникает состояние, представленное на фиг.1. На случай присутствия ошибки в двух процессорах происходит отключение системы.

Показанный на фиг.1 и 2 принцип действия имеет преимущество при наличии периферийных блоков, построенных без резервирования.

Показанная на фиг.1 и 2 архитектура заключается в делении периферийных модулей на две группы А и В. Каждая группа включает в себя, по меньшей мере, один процессор 1, 2, не показанный здесь переключатель шин и управляемые периферийные модули 95, 96. Модули памяти можно внедрить в обе группы. Стороной А в действительности (т.е. физически) всегда управляет процессор 1 (процессор А). Данные периферийных модулей 95 можно направить поперек через умножители 91, 92 дальше к стороне В. Процессор 1 может аналогичным образом считывать данные периферийных модулей 96.

На фиг.3 показан пример выполнения, в котором два процессора 1 и 2 управляют с резервированием периферийным блоком 22, который обозначен там как периферийный модуль, причем к предопределенному моменту времени только один из двух процессоров управляет блоком 22. Это происходит через умножитель 21. Другой периферийный блок 5, в отношении которого речь может идти об общем внутреннем периферийном блоке, например блоке памяти 5, связан с обоими процессорами 1, 2 через умножитель 20. Сами процессоры соединены через свои шинные матрицы 3,4 с умножителями 20, 21. И в этом примере выполнения умножителям 20, 21, которые имеются в блоке с соответствующими блоками сравнения (компараторами), можно задать подходящую конфигурацию в случае ошибки, чтобы управление было безотказным.

Согласно одному или нескольким примерам выполнения происходит четкое разделение между общими применяемыми компонентами и частными резервными областями управления. Каждому процессору 1, 2 подчинены частные компоненты или блоки, которыми управляет только он. Частные компоненты (на фиг.4 оба периферийных блока 61, 62) предпочтительно зарезервированы, чтобы по возможности обеспечить отличную симметрию резервированных частных областей. По соображениям цены некоторые компоненты, например память программы, можно внедрить только один раз и именно в общеприменяемую область. В режиме «шаг в ногу» оба процессора 1, 2 работают синхронно. Действительное управление общеприменяемых компонентов или периферийных блоков может принять на себя каждый из двух резервных процессоров и в действительности в определенный момент времени осуществляется только одним процессором, тогда как другой процессор благодаря работе «шаг в ногу» получает все данные своевременно.

После распознавания сбоя синхронности каждый процессор 1, 2 должен оставаться в промежуток времени Т1 по возможности активным в известной частной области и не должен выполнять важные для безопасности функции с эффектом вне архитектуры. Это означает, в частности, что управление внешними периферийными блоками или компонентами, которые демонстрируют свое действие в направлении наружу, прерывается.

Для необходимого доступа к нерезервным компонентам, например к памяти программы, возможна эксплуатация умножителей для двух резервных процессоров 1, 2 в промежуток времени Т1. Каждая ошибка синхронизации прерывает выполнение программы. При прерывании программы процессоры 1, 2 будут выполнять независимо друг от друга одинаковые тестовые программы, а результаты тестирования для последующей проверки с помощью автономного аппаратного обеспечения поступают в переустановочное контрольное устройство 44.

Многие тестовые программы можно формировать из суммы сведений об ошибках. Например, возникающую ошибку классифицируют и причисляют к определенному типу и используют это для выбора тестовой программы или соответствующих тестовых программ.

Каждый процессор должен закончить выполнение прерывания плавно без скачков. Предпосылкой этому является то, что тестовая программа была запущена с помощью сигнала прерывания и после выполнения тестовой программы процессоры 1, 2 снова продолжают нормально выполнять программу управления, прерванную из-за сигнала прерывания. Она должна была прерваться, а процессоры 1, 2 должны перейти в состояние покоя. Если это произошло, то это и есть часть теста.

Затем каждый процессор должен сбросить свои признаки, например, в реестр, читаемый автономным проверочным модулем, относящимся к аппаратным средствам (переустановочным контрольным устройством 44). Время выполнения измеряют с помощью счетчика времени автономного проверочного модуля, относящегося к аппаратным средствам.

По истечении этого неясного времени резервные процессоры должны иметь «режим холостого хода» (состояние покоя) на время Т2. Если процессор в промежуток времени Т2 имеет доступ к компоненту, например к модулю памяти или периферийному модулю, то он автоматически отключается переустановочным устройством 44 от процесса восстановления. По истечении промежутка времени Т2 переустановочное контрольное устройство 44 сравнивает результаты тестирования двух процессоров 1, 2 со значениями, запрограммированными в аппаратной части. Если результаты тестирования процессора не совпадают с заданными значениями, соответствующий процессор больше не учитывают при текущем испытании синхронизации. В соответствии с этим также и записанные в память признаки состояния процессоров 1, 2 должны подходить для восстановления. В случае положительной оценки результатов переустановочное контрольное устройство 44 с помощью прерывания обеспечивает возврат в синхронный режим. Если все тесты успешно выполнил только один процессор, он будет управлять принадлежащим ему периферийным модулем и всеми общеприменяемыми компонентами.

Этот аварийный режим повышает безотказность при эксплуатации системы и протекает с восстановленной ступенью безопасности.

На фиг.4 показана другая форма выполнения, которая основана на той, что представлена на фиг.3. Архитектура устройства управления поделена на две частные области 30 и 31, обозначенные как области А и В, и одну общую область 40. Частные области содержат модули или периферийные блоки и компоненты, которые физически являются резервными. Переустановочное контрольное устройство 44 в виде модуля, принадлежащего аппаратной части, служит надежному восстановлению синхронизации после сбоя или ошибки синхронизации. Если возникает сбой в синхронизации, переустановочное контрольное устройство 44 блокирует все доступы к важным для безопасности периферийным модулям или блокам. В отношении блоков речь идет, в частности, об общей периферии 72 и, например, об имеющихся в резерве периферийных блоках 61 и 63. Они подключены через соответствующие периферийные шлюзы 60, 71 и 62.

Ошибка, заключающаяся в сдвиге шага, инициирует прерывание процесса выполнения программы. В последующем выполнении прерывания программы каждый процессор 1, 2 может иметь доступ только к модулям, которые находятся в его соответствующей частной области и не выполняют подфункции. Кроме того, возможен доступ к несущественным для безопасности компонентам 41, 42 в режиме работы умножителя. Такими компонентами 41, 42 являются, например, программный домен 42 и общий ОЗУ-домен. Компонент 42 оснащен модулем 50, который имеет умножитель, контроллер и компаратор и собственную программную память. Компонент 41 оснащен модулем 53, который содержит умножитель, контроллер и компаратор и память 52, которая является здесь памятью прямого доступа (RAM).

В частной периферийной области зарезервировано в каждом случае небольшое адресное пространство для тестирования соответствующего процессора. Программа прерывания служит для проверки неповрежденности архитектуры и, прежде всего, процессоров. В конце программы прерывания процессоры должны сбросить результаты расчетов в адресную область памяти, зарезервированную для целей тестирования. Правильные результаты хранятся в памяти в предварительной зоне переустановочного контрольного устройства 44. Программа прерывания состоит из тестовых программ, причем каждая тестовая программа внутри определенного интервала времени должна выдать правильный результат. По истечении заданного времени переустановочное контрольное устройство 44 проверяет правильность результатов, переданных процессорами. Восстановление синхронной работы предполагает, что все результаты, проверяемые переустановочным контрольным устройством 44, являются правильными. В противном случае для текущего приложения активным будет оставаться только тот процессор, который имеет правильные результаты.

Так как программа прерывания выполняется не в синхронном режиме, модуль 50 имеет такую конфигурацию, что оба процессора 1, 2 при работе умножителя могут иметь доступ к программной памяти 51.

На фиг.5 представлена форма выполнения в развитии фиг.1 и 2. При этом переустановочное контрольно устройство 44 работает подобно тому, как представлено на фиг.4. Если процессор 1, 2 не выдает правильные результаты для восстановления синхронной работы, то переустановочное контрольное устройство 44 задает соответствующим периферийным контроллерам 91 или 92, которые образуют здесь умножители и компараторы, такую конфигурацию, что расположенными под ними периферийными модулями или блоками 95, 96 управляет другой процессор.

Архитектура на фиг.5 имеет также два резервных модуля ОЗУ 80, 91. Когда ошибка синхронизации вызвана ошибкой в ОЗУ, адрес ОЗУ с ошибкой сохраняется. В программе прерывания этот адрес проверяется. Если ошибка в памяти прямого доступа неисправима, переустановочное контрольное устройство 44 больше не включает упомянутые стороны А и В (т.е. процессор и ОЗУ) в активное управление. После этого переустановочное контрольное устройство 44 отвечает за то, что периферийными модулями, до сих пор управляемыми процессором или ОЗУ с ошибкой, теперь управляет процессор с другой стороны.

На фиг.6 схематично представлено выполнение программы управления. После появления сбоя в синхронизации выполнение программы 300, 500 прерывается с помощью программы прерывания, а соответствующее состояние (начальное состояние) записывается в 321, 521. Прерывание ведет одновременно к активизации переустановочного контрольного устройства, обозначенного здесь как аппаратное средство.

Переустановочное контрольное устройство запускает счетчик времени 400. Процессоры выполняют затем на этапах 322, 522 тестирование, заданное переустановочным контрольным устройством, причем по окончании тестирования происходит возврат в режим без прерывания в 323, 523. После этого процессоры должны перейти в состояние покоя.

Переустановочное контрольное устройство проверяет, выполнялись ли тесты за время Т1 (325, 525) и перешли ли процессоры в состояние покоя (401). По истечении заданного времени Т2 переустановочное контрольное устройство проверяет в 402, 326, 526, находятся ли процессоры все еще в состоянии покоя.

Затем проверяют результаты тестирования. Условиями переустановки 404 являются безошибочные результаты тестирования, чтобы соответствующий процессор до истечения времени Т1 перешел в состояние покоя и чтобы процессор и по истечении времени Т2 находился в состоянии покоя. Если это произошло с двумя процессорами, выполняется восстановление прерывания для обоих процессоров, в противном случае только для исправного процессора, и снова получается исходное состояние (341, 541). В последнем случае переустановочное контрольное устройство возвращает устройству управления конфигурацию, как это было описано выше. Выполнение программы продолжается.

На фиг.7 представлена обычная архитектура с двумя процессорами 1 и 2, причем процессор 2 предназначен для проверки процессора 1. Общее управление периферийными модулями, а также все доступы к памяти выполняет процессор 1. Эта архитектура непригодна для обнаружения и устранения ошибок, возникающих от потери синхронизации.

На фиг.8 представлена обычная архитектура с разделением периферийных модулей на две группы - А и В. Каждая группа содержит, по меньшей мере, один процессор 1, 2, переключатель шин (шинную матрицу) 3, 4 и периферийные модули 6, 7. Модули памяти 5 можно внедрить в одну группу или в обе группы и ими можно управлять с помощью байпасного модуля 11. Стороной А фактически (т.е. физически) управляет всегда процессор 1. Стороной В фактически всегда управляет процессор 2. Данные периферийных модулей 6 можно передавать дальше в поперечном направлении через байпасный модуль 10 и умножитель данных 12 на сторону В. Процессор 1 может таким же образом считывать данные периферийных модулей 6 (через байпасный модуль 9 и умножитель данных 13). Этот механизм, с помощью которого процессор может считывать периферийные данные с другой стороны, действует до тех пор, пока два процессора 1 и 2 не будут работать синхронно. Проверку проводит компаратор 8. Когда процессор 1, например, не работает, вся сторона А (т.е. все без исключения периферийные модули и запоминающие устройства на этой стороне) являются больше неуправляемыми. Таким образом, получается плохая поддержка безотказности при эксплуатации. Когда два процессора больше не работают синхронно, они имеют возможность восстановить свое прежнее состояние. Для существенных для безопасности приложений возврат процессоров в прежнее состояние не разрешен, пока не будут однозначно установлены причины потери синхронности.

В связи с фиг.1-8 были описаны двухпроцессорные устройства управления. Далее описываются устройства управления с несколькими процессорами или ядрами процессоров с помощью контрольно-вычислительных систем. Число процессоров или ядер процессоров не ограничивается, однако, конкретно представленным числом, но может быть любым по мере необходимости.

На фиг.9 представлена контрольно-вычислительная система (устройство управления). Она имеет две пары процессоров 1001 и 1002 (или ядра 1А и 1В) и 1003 и 1004 (или ядра 2А и 2В), два блока сравнения 1011 и 1012, переключающую матрицу 1013 (обозначенную также как переключающий элемент), память 1020 и 1021, а также периферийный шлюз 1022, к которому подключены несколько периферийных блоков 1030, 1031, …1038. Каждая пара процессоров может иметь два отдельных процессора, а один процессор может быть двухъядерным. В следующих примерах выполнения число процессоров или ядер может быть любым. Например, можно применять три процессора или более трех, каждый с двумя ядрами, которые являются друг для друга резервными. В принципе можно также объединить три процессора для получения резервного комплекса, причем контрольно-вычислительная система может иметь два или более двух таких комплексов.

В первой паре процессоров процессор 1001 (или ядро 1А) имеет в действительности доступ к различным ресурсам, таким как память и периферийные блоки. Блок сравнения 1011 сравнивает выходные данные процессоров 1001 и 1002 и направляет входные данные в оба процессора, причем проверяемый процессор 1002 не имеет доступ к памяти и периферийным блокам. Оба процессора (ядра) 1001 и 1002 имеют идентичное выполнение и работают синхронно или в синхронном режиме, благодаря чему блок сравнения 1011 в случае отсутствия ошибки получает каждый раз одинаковые выходные данные. Пара процессоров 1003 и 1004 имеет соответственное выполнение, процессор 1003 имеет в действительности доступ к памяти и периферийным блокам, а блок сравнения 1012 передает входные данные далее в проверяемый процессор 1004. Переключающая матрица 1013 дает доступ процессорам к памяти или периферийным блокам. Каждый доступ к периферийным блокам осуществляется через центральный периферийный шлюз 1022. В случае отсутствия ошибки контрольно-вычислительная система предоставляет в распоряжение два независимых процессора 1001 и 1003 (ядра процессоров 1А и 1В).

Пример выполнения заявленной контрольно-вычислительной системы представлен на фиг.10. Как и показанная на фиг.9, контрольно-вычислительная система содержит здесь две пары процессоров 1001, 1002 и 1003, 1004, два блока сравнения 1011 и 1012, переключающую матрицу 1013, память 1020 и 1021, а также периферийный шлюз 1022, к которому подключены несколько периферийных блоков 1030, 1031, …1038. Кроме того, заявленная контрольно-вычислительная система имеет в своем распоряжении блок обнаружения и устранения ошибок (восстанавливающий блок) 1080, который принимает сигналы блоков сравнения 1011, 1012. Блок обнаружения и устранения ошибок 1080 может управлять переключающей матрицей 1013 и периферийным шлюзом 1022 для воспрепятствования доступа отдельного процессора 1001, 1002, 1003, 1004 (или ядра 1А, 1В, 2А, 2В) или пары процессоров к памяти и/или периферийным блокам. В предпочтительном варианте выполнения изобретения переключающая матрица 1013 содержит блок проверки 1014, который не только препятствует доступу, но и может составлять протокол. Предпочтительно сигналы блоков сравнения 1011, 1012 могут передаваться прямо в блок обнаружения и устранения ошибок 1080 и не проходят в переключающую матрицу 1013. Блок обнаружения и устранения ошибок 1080, как уже было описано выше в связи с переустановочным контрольным устройством, настроен на создание подходящей конфигурации для переключающей матрицы 1013 или периферийного блока 1022 после возникновения ошибки. Если при проведении сравнения, например, между процессорами 1001 и 1002 (или ядрами 1А и 1В первой пары процессоров) имеет место ошибка, то блок обнаружения и устранения ошибок 1080 посылает управляющие сигналы 1110 переключающей матрице 1013 и периферийному шлюзу 1022. После этого доступ пары процессоров 1001/1002 к памяти блокируется или составляется протокол и/или прерывается доступ к периферийным блокам. Таким образом, процессор, содержащий ошибку, не может управлять, например, исполнительными элементами, иначе могли бы возникнуть серьезные повреждения.

Другими словами, обычная архитектура расширена на один модуль 1080. который принимает функцию переустановочного контрольного устройства. Этот модуль 1080 обозначен также как SVM-модуль (модуль надежности и безотказности при эксплуатации). В зависимости от типа ошибки SVM-модуль 1080 управляет блоком проверки 1014 внутри переключающего элемента (переключающей матрицы) 1013 для запрета доступа процессора, содержащего ошибку, к определенным периферийным модулям и памяти прямого доступа. SVM-модуль 1080 сразу же выдает сообщение, если компараторы в модулях (блоках сравнения) 1011 и 1012 обнаружили ошибку. На основании сигналов об ошибке SVM-модуль 1080 обеспечивает невозможность для соответствующих ядер процессоров 1А или 2А (процессоров 1001, 1002) управлять исполнительными элементами через периферийные модули. С помощью управляющих сигналов 1110 SVM-модуль 1080 может препятствовать доступу к периферийным модулям в переключающем элементе 1013 или в периферийном шлюзе 1022.

Пример выполнения заявленного способа управления контрольно-вычислительного устройства представлен на фиг.11, причем конфигурация контрольно-вычислительной системы соответствует конфигурации, описанной в связи с фиг.10.

Если компаратор распознает в модуле (блоке сравнения) 1011 ошибку 1220, происходит прерывание работы для обоих пар процессоров 1А/1В и 2А/2В. Пара процессоров 1А/1В прекращает выполнение поставленной задачи 1200 и начинает выполнять программу прерывания. Контекст или содержание для нормального режима работы записывается в память блока 1250, прежде чем пара процессоров 1А/1В подвергнется проверочному тестированию на состояние в блоке 1251. Запросный блок 1252 проверяет пару процессоров 1А/1В, является ли ошибка постоянной. Если пара процессоров 1А/1В имеет постоянную ошибку, эту пару больше не учитывают для восстановления. В блоке 1254 определяется тип ошибки и записывается в энергонезависимой памяти, например во внешнем блоке памяти. В блоке 1255 в памяти записывается шифр и отмечается время возникновения случайной ошибки. Если та же ошибка повторяется, то данные, хранящиеся в памяти в блоке 1255, должны помочь в определении частоты повторений. Такую частоту повторений можно использовать в качестве решающего критерия для дальнейших попыток восстановления. В блоке 1256 пара процессоров 1А/1В ожидает сигнал, сообщающий, должна ли состояться попытка восстановления.

После поступления прерывающего сигнала пара процессоров 2А/2В переходит в аварийный режим в качестве исправной пары процессоров. Сначала пара процессоров 2А/2В «покидает» выполненное приложение в блоке 1300 и хранит в памяти контекст для нормального режима работы (блок 1350). Проверочные тесты, касающиеся ошибки, проводят в блоке 1351. В блоке 1352 выполняются части программы (обязательные модули программного обеспечения), необходимые для нормального режима работы. Эти необходимые программные части составлены из выбранных приложений, которые первоначально были согласованы с разными парами процессоров. Во время аварийной работы пара процессоров 2А/2В проводит постоянную проверку на наличие сигнала для попытки восстановления. Если восстановление нормального режима работы происходит в блоке 1353, пара процессоров 2А/2В ожидает выход сигнала для попытки восстановления в блоке 1354.

После выхода прерывающего сигнала SVM-модуль 1080 в блоке 1401 блокирует все без исключения доступы пары процессоров 1А/1В, содержащих ошибку, к важным для безопасности периферийным модулям. С помощью этого блока можно избежать любого ненадежного управления исполнительными элементами. Когда восстановление нормального режима работы не нужно поддерживать, SVM-модуль 1080 остается в блоке 1402, а управление осуществляет теперь пара процессоров 2А/2В. В противном случае SVM-модуль 1080 в блоке 1403 настраивается на условия, которые необходимы для попытки восстановления и которые должны поступить от пары процессоров, содержащих ошибку. После этого эти условия проверяют в блоке 1405. Если условия восстановления выполнены, то SVM-модуль 1080 инициирует попытку восстановления с помощью всех пар процессоров. После успешного восстановления в распоряжении снова имеется полная мощность контрольно-вычислительной системы.

Восстановление, в частности проверка, может происходить так, как показано на фиг.6.

Согласно примеру выполнения управляющие программные средства контрольно-вычислительной системы подходящим образом направлены на возможность возникновения ошибок и их устранение. Управляющие программные средства содержат, по меньшей мере, два типа модулей программного обеспечения, во-первых, обязательные модули, а во-вторых, дополнительные модули. При нормальной работе модули разделены на две пары процессоров. При сбое обязательные модули программного обеспечения (обозначенные также как аварийные модули) приводятся в исполнение оставшейся парой процессоров, а дополнительные, наоборот, не ограничены или все еще ограничены. Таким образом, возможно, чтобы пара процессоров, не содержащая ошибок, могла взять на себя также и обязательные модули программного обеспечения пары процессоров, содержащих ошибки. Таким образом, модули программного обеспечения, в обязательном порядке необходимые для управления периферийными блоками, можно выполнить таким образом, чтобы это не привело к потере резервности. Только дополнительные модули программного обеспечения имеют полную или неполную компоновку. Это, однако, не представляет собой ограничение безопасности.

Представленная на фиг.12 другая архитектура контрольно-вычислительной системы с двумя парами процессоров имеет в распоряжении два резервных переключающих элемента (или переключающие матрицы) 1013, 1063. Ядра процессоров 1А и 2А (процессоры 1001, 1003) могут иметь доступ через переключающий элемент 1013 к модулю памяти 1020 и 1021. Ядра процессоров 1В и 2В (процессоры 1002, 1004) имеют доступ через переключающий элемент 1063 к модулям памяти 1020 и 1071. Модуль памяти 1021 может использоваться только ядрами процессоров 1А и 2А, тогда как модуль памяти 1071 предоставлен в распоряжение только ядрам процессоров 1В и 2В. Таким образом, блок, состоящий из ядер процессоров 1А и 2А, переключающего элемента 1013 и модуля памяти 1021, полностью симметричен (является резервным) блоку с ядрами процессоров 1В и 2В, переключающим элементом 1063 и модулем памяти 1071. Модуль памяти 1020 может считываться всеми процессорами.

В нормальном режиме работы процессоры 1А и 1В работают синхронно, так что один процессор образует механизм проверки для другого процессора. В соответствии с этим и ядра процессоров 2А и 2В работают синхронно и осуществляют взаимную проверку. Проверку осуществляют компараторы, которые внедрены в модули (блоки сравнения) 1091 и 1090. Блок сравнения 1091 следит за всеми доступами к резервным модулям памяти 1021 и 1071, а блок сравнения 1090 следит за всеми доступами к периферии. Эту архитектуру можно реализовать таким образом, чтобы все периферийные модули были резервными. Например, периферийные модули 1040, 1041, …1048 могут быть резервными по отношению к периферийным модулям 1030, 1031, …1038. В этом случае блок сравнения 1090 может содержать только компараторы для доступа к периферии.

По причинам стоимости многие периферийные модули не имеют резерва. В этом случае блок сравнения 1090 наряду с периферийными компараторами содержит дополнительные переключательные схемы, которые данные нерезервных периферийных модулей синхронно передают дальше к резервных переключающим элементам 1013 и 1063.

На фиг.13 представлен другой пример выполнения заявленной контрольно-вычислительной системы. При этом архитектура, представленная на фиг.12, расширяется для поддержки концепции гарантии улучшенной безотказности при эксплуатации электронных регулировочных алгоритмов, подготовленных контрольно-вычислительной системой. Между каждым ядром процессоров 1А, 2A, 1B, 2В и соответствующим переключающим элементом 1013, 1063 установлены умножители 1171, 1172, 1173 и 1174, так что каждое второе ядро пары процессоров может иметь доступ к шине данных и адресной шине первого ядра процессорной пары, и, наоборот, может существовать также доступ первого процессора одной пары к шине данных и адресной шине второго процессора. При отказе ядра процессора 1А, например, умножитель 1171 обеспечивает то, чтобы переключающий элемент 1013 снабжался данными резервного ядра процессора 1В. Управление умножителями 1117, 1172, 1173 и 1174 осуществляется в SVM-модуле 1080, в котором все сигналы об ошибке 1161, 11622 проверяются компараторами. После распознавания ошибки в синхронности SVM-модуль 1080 блокирует доступ к важным для безопасности компонентам, препровождая дальше соответствующие сигналы управления 1160 в устройства проверки 1014 и 1064 в переключающие элементы 1013 и 1014, а также в периферийные шлюзы 1022 и 1072. Возобновление работы после исследования ошибки происходит в принципе по схеме, представленной на фиг.11, 18 и/или 19, с вменением в случае надобности необходимых корректировок.

SVM-модуль 1080 (переустановочное контрольное устройство) подходящим образом задает конфигурацию переключающих элементов 1013, 1063 и умножителей 1171, 1172, 1173 и 1174, чтобы исключить доступ процессоров или других компонентов, содержащих ошибку, к периферии. Это происходит также с помощью других резервных компонентов, например с помощью модулей памяти. И здесь неисправный модуль памяти отключается за счет создания другой конфигурации переключающего элемента 1013, 1063 и умножителей 1171, 1172, 1173 и 1174.

На фиг.14, 15 и 16 представлена заявленная контрольно-вычислительная система в архитектуре фиг.13, причем были отключены соответственно один или несколько процессоров, находящихся длительное время в состоянии присутствия ошибки. Оставшееся ядро процессора или оставшиеся ядра процессоров управляет/управляют периферией, причем при необходимости пользователю поступает предупреждение, и критические для безопасности функции реализуются преимущественно только в процессорах, которые имеют еще способный действовать проверяющий процессор, причем, таким образом, работает полноценная процессорная пара. Предпочтительно процессоры не реализуют критические для безопасности функции без проверяющего процессора. Неисправные процессоры (ядра) представлены заштрихованными.

Так, например, на фиг.14 показан сбой в работе ядра процессора 2В. Ядра процессора 1А и 1В, кроме того, являются резервными и принимают на себя выполнение всех критических для безопасности приложений (обязательные модули программного обеспечения), включая те, которые первоначально выполнялись процессорной парой 2А/2В. Ядро процессора 2А может выполнять несущественные для безопасности приложения (дополнительные модули программного обеспечения), включая дополнительные модули программного обеспечения, первоначально приводимые в исполнение процессорной парой 1А/1В. Таким образом, все значительные для безопасности приложения перешли ко все еще остающейся в резерве процессорной паре 1А/1В. Преимущество такого принципа действия заключается в том, что для аварийного режима работы (неисправность процессорной пары или одного отдельного ядра процессорной пары) не нужны никакие дополнительные резервные пары процессоров, которые в нормальном режиме работы (все процессоры исправны) не выполняют никакую функцию. Только выполнение команд дополнительных модулей программного обеспечения ограничено при появлении ошибки. Это, однако, не является определяющим для безопасности.

На фиг.17 представлена еще одна архитектура контрольно-вычислительной системы с процессорными парами в расширенном двойном резерве согласно примеру выполнения.

В отличие от архитектуры, представленной на фиг.9, резервными являются не только процессоры 1001, 1002, 1003, 1004, но и другие компоненты. Например, резервными являются шинные матрицы (переключающие элементы) 1013 и 1062, а также память данных 1021 и 1071. Связи между периферийными шлюзами 1022 и 1071, имеющиеся в этой форме выполнения, отвечают за то, чтобы данные нерезервных периферийных компонентов были синхронно переданы в резервные пары 1А/1В и/или 2А/2В ядер процессоров.

Представленная на фиг.17 архитектура имеет расширение на SVM-модуль 1080 и переключающие элементы 171, 172, 173 и 174. В зависимости от типа ошибки SVM-модуль 1080 будет управлять блоком проверки 1014 и 1064 внутри переключающих матриц или переключающих элементов 1013 и 1061, а также переключающими элементами 171, 172, 173 и 174, чтобы запретить паре процессоров 1А/1В, 2А/2В, содержащих ошибку, или только процессору 1А, 1В, 2А, 2В, содержащему ошибку, доступ к определенным периферийным модулям и памяти прямого доступа. SVM-модуль 1080 сразу же выдает сообщение, если компараторы в модулях (блоках сравнения) 1090 и 1091 обнаружили ошибку. На основании сигналов об ошибке SVM-модуль отвечает за то, чтобы соответствующая пара 1А/1В или 2А/2В или соответствующий процессор 1А, 1B, 2А или 2В не могли больше управлять исполнительными элементами через периферийные модули. С помощью управляющих сигналов 1160 SVM-модуль 1080 может блокировать доступы к периферийным модулям в шинных матрицах 1013 и 1063 или в периферийных шлюзах 1022 и 1072.

На фиг.18 представлено примерное изображение хода процесса после обнаружения ошибки согласно форме выполнения. Если компаратор в модулях 1090 и 1091 на фиг.17 обнаруживает ошибку 1220, происходит прерывание работы для обоих процессоров пары 1А/1В и 2А/2В.

Процессоры 1А и 1В прекращают синхронную работу в блоке 1200 и асинхронно переходят к выполнению программы прерывания. Процессоры 2А и 2В так же прекращают синхронную работу на этапе 1300 и асинхронно переходят к выполнению программы прерывания. Каждый процессор сначала «спасает» контекстные данные или содержание (1250А, 1250В, 1350А, 1350В), необходимые для текущего приложения. Показателем хорошего состояния является выполнение всеми процессорами 1А, 1B, 2А и 2В записи (1250А, 1250В, 1350А, 1350В) цифрового шифра, проверяемого и распознаваемого SVM-модулем, в реестр SVM-модуля 1080. Если созданный процессором шифр неправильный или он отсутствует в течение заданного интервала времени Т1, процессор больше не учитывают в процессе восстановления. В этом случае SVM-модуль 1080 управляет всеми переключающими элементами 1014, 1064, 1171, 1172, 1173 и 1174, чтобы блокировать любой доступ процессора, содержащего ошибку, к модулям памяти и периферийным модулям. Для каждого типа ошибки в памяти SVM-модуля 1080 записан код ошибки. Остальные процессоры подвергаются дальнейшему тестированию в блоках 1251А, 1251В, 1351А или 1351В. В зависимости от кода ошибки проводят различные тесты в математическом обеспечении и/или аппаратной части. Тесты аппаратных средств, например, в форме логического формирования с самотестированием, применяют, в частности, для серьезных ошибок, а также при неясности того, к какому классу отнести ошибку. Результаты тестирования в блоках 1251А, 1251В, 1351А или 1351В записывают в память SVM-модуля 1080, а затем через определенный промежуток времени Т2 оценивают. На основании собранных результатов SVM-модуль 1080 решает, какой процессор или какие процессоры содержит/содержат ошибку, и в соответствии с этим задает переключающим элементам 1014, 1064, 1171, 1172, 1173 и 1174 такую конфигурацию, чтобы в процессе восстановления участвовали только исправные (не содержащие ошибок) процессоры. Для процессоров, содержащих ошибки, доступ закрыт.

Представленный на фиг.18 порядок действий можно расширить таким образом, чтобы компоненты, содержащие ошибки, можно было распознать в других резервных модулях. Главная идея заключается в том, чтобы двойное резервирование в имеющейся архитектуре использовать везде для гарантии улучшенную безотказность при эксплуатации системы безопасности. Это подходит для резервной памяти. С помощью подходящих тестов 1251А, 1251В, 1351А и 1351В SVM-модуль 1080 может точно определить, какой из двух резервных модулей памяти содержит ошибку. Изменив конфигурацию переключающих элементов 1014, 1064, 1171, 1172, 1173 и 1174, можно изменить направление доступов к резервных модулям памяти 1021 или 1071 таким образом, чтобы только одна память сохраняла и передавала дальше действительно достоверные данные. Дальнейший процесс может происходить по аналогии с процессом, представленным на фиг.11.

Представленная на фиг.17 архитектура предлагает более высокую степень свободы и помехозащищенности, чем архитектура, представленная на фиг.12, на основе большого числа резервных компонентов.

На фиг.19 представлено примерное изображение хода процесса после обнаружения ошибки согласно форме выполнения. Если компаратор в модуле 1011 на фиг.10 обнаруживает ошибку 1220, то для обеих пар процессоров 1А/1В и 2А/2В осуществляется прерывание работы. Порядок действий аналогичен тому, который показан на фиг.18. Для представленной на фиг.10 архитектуры резервные процессоры можно не делить на пары. Поэтому SVM-модуль 1080 будет только устанавливать, какая пара процессоров содержит ошибку. С помощью соответствующей конфигурации переключающего элемента 1014 блокируются все доступы этой неисправной процессорной пары к данным. В общем, выполнение осуществляется по аналогии с фиг.11.

На фиг.20 представлена архитектура фиг.17 с отключенным ядром процессора 2В после восстановления.

Фиг.21 показывает архитектуру фиг.17 с отключенными ядрами процессоров 1В и 2В после восстановления.

На фиг.22 представлена архитектура фиг.17 с отключенными ядрами процессоров 1А, 2А и 1В после восстановления. Здесь больше нет резервности для процессоров. Однако с помощью описанной выше проверки, например, по аналогии с порядком действий, представленных на фиг.6, 11, 18 и 19, обеспечивается то, что все процессоры, содержащие ошибку, определены правильно и исключены для доступа к периферии.

На фиг.23 представлена архитектура фиг.17 с отключенными ядрами процессоров 1А и 2В после восстановления.

На фиг.24 показана архитектура фиг.17 с отключенной памятью данных 21 после восстановления. Эта архитектура как таковая имеет резервную память данных 21 и 71, причем после возникновения помех в модуле памяти 1021 его точно идентифицируют как неисправный и отключают.

В общем, описанная здесь контрольно-вычислительная система имеет в своем распоряжении улучшенную подготовку важных для безопасности функций, надежную идентификацию и исключение компонентов, содержащих ошибку.

Согласно форме выполнения контрольно-вычислительная система (устройство управления) содержит, по меньшей мере, две пары процессоров, по меньшей мере, два блока сравнения (компараторы) для распознавания ошибок, по меньшей мере, одну память, по меньшей мере, один периферийный блок, по меньшей мере, один переключающий элемент, например в форме переключающей матрицы, разрешающей процессорам доступ к памяти и периферийным блокам или блокирующей этот доступ, причем предпочтительно общий блок обнаружения и устранения ошибок (переустановочное контрольное устройство; SVM-модуль) принимает сигналы, по меньшей мере, двух блоков сравнения и управляет, по меньшей мере, одной переключающей матрицей для воспрепятствования доступа процессора или пары процессоров к памяти и/или периферийным блокам в целом или выборочно.

Согласно форме выполнения при появлении ошибки предотвращается доступ, по меньшей мере, одной неисправной пары процессоров к периферийным блокам, в частности исполнительным элементам.

В соответствии с формой выполнения осуществляется доступ к периферийным блокам через периферийные шлюзы, которыми управляет блок обнаружения и устранения ошибок (переустановочное контрольное устройство; SVM-модуль).

В соответствии с формой выполнения, по меньшей мере, два блока сравнения напрямую связаны с обоими процессорами пары.

Согласно форме выполнения блок сравнения содержит, по меньшей мере, две раздельные переключающие матрицы, причем первая переключающая матрица связана с первым периферийным шлюзом и, по меньшей мере, с первой памятью, тогда как вторая переключающая матрица связана со вторым периферийным шлюзом и, по меньшей мере, с одной второй памятью.

В соответствии с формой выполнения первый процессор пары связан с первой переключающей матрицей, а второй процессор пары связан со второй переключающей матрицей.

Согласно форме выполнения сравнивают данные блока сравнения, перемещающиеся между первой переключающей матрицей и первой памятью, с данными, перемещающимися между второй переключающей матрицей и второй памятью, причем данные блока сравнения, перемещающиеся между первой переключающей матрицей и первым периферийным шлюзом, сравнивают с данными, перемещающимися между второй переключающей матрицей и вторым периферийным шлюзом.

Согласно форме выполнения между процессорами и переключающими матрицами в каждом случае установлен по месту умножитель, причем они подключены так, что первый процессор пары может иметь доступ ко второй переключающей матрице, а второй процессор пары может иметь доступ к первой переключающей матрице, как только блок обнаружения и устранения ошибок (восстанавливающий блок, SVM-модуль) начнет соответствующим образом управлять умножителями.

В соответствии с формой выполнения, по меньшей мере, одна переключающая матрица имеет блок проверки, который может блокировать доступ к памяти или периферийным блокам или писать протокол во внешней или внутренней памяти, предпочтительно энергонезависимой памяти.

Согласно форме выполнения блок обнаружения и устранения ошибок принимает сигналы, по меньшей мере, двух блоков сравнения напрямую, без использования промежуточной переключающей матрицы.

Согласно форме выполнения контрольно-вычислительная система содержит первую и вторую энергозависимую память, а также энергонезависимую память, причем, в частности, одна процессорная пара имеет доступ к первой энергозависимой памяти, а вторая пара процессоров - ко второй энергозависимой памяти, и обе пары процессоров имеют доступ к энергонезависимой памяти.

Согласно форме выполнения первый процессор пары напрямую связан, по меньшей мере, с одной переключающей матрицей, т.е. может иметь доступ к памяти и/или периферийным устройствам, считывая и записывая, тогда как второй процессор пары имеет доступ к данным, только лишь считывая их, причем, в частности, блок сравнения, напрямую связанный с обоими процессорами пары, передает данные во второй процессор объединенной процессорной пары.

В соответствии с формой выполнения подготавливают способ управления контрольно-вычислительной системы, которая содержит, по меньшей мере, две пары процессоров, по меньшей мере, два блока сравнения для идентификации ошибок, по меньшей мере, одну переключающую матрицу, которая дает возможность доступа процессору или паре процессоров к памяти и/или периферийным блокам или блокирует этот доступ, и, по меньшей мере, один блок обнаружения и устранения ошибок, который может управлять, по меньшей мере, переключающей матрицей, причем способ реализуется таким образом, что пары процессоров в безошибочном режиме работы могут выполнять разные программы для подготовки функций, а при возникновении ошибки процессорная пара, не содержащая ошибок, принимает на себя некоторые функции процессорной пары, содержащей ошибку.

Согласно форме выполнения для надежности устройства, управляемого контрольно-вычислительной системой, реализуются критические функции независимо от появления ошибки.

Согласно форме выполнения при возникновении ошибки больше не подготавливаются критические для безопасности функции, по меньшей мере часть их.

В соответствии с формой выполнения при возникновении ошибки блокируется доступ процессора или пары процессоров, содержащих ошибку, к периферии.

Согласно форме выполнения после возникновении ошибки процессорная пара, содержащая ошибку, составляет диаграмму.

Согласно форме выполнения возникшие ошибки классифицируют, причем проводят различие между случайными и постоянными ошибками.

В соответствии с формой выполнения после появления постоянной ошибки неисправную пару процессоров отключают на длительное время.

Согласно форме выполнения обе пары процессоров могут снова выполнять разные программы, если пара процессоров, содержащая ошибку, выполнила диагностическую программу без идентификации устойчивой ошибки.

В соответствии с формой выполнения блок обнаружения и устранения ошибок протоколирует возникновение ошибки в энергонезависимой памяти.

Согласно форме выполнения процессорную пару отключают на длительное время, если число ошибок и/или частота повторяемости возникших ошибок превышает пороговое значение.

Согласно форме выполнения одну из описанных выше контрольно-вычислительных систем можно применять в автотранспортном средстве, в частности для управления и регулирования тормозной системы.

Изобретение не ограничивается описанными выше примерами выполнения, а может быть подходящим образом расширено и модифицировано. Следующие далее пункты формулы представляют собой первую, ни к чему не обязывающую попытку сформулировать изобретение в общем и целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| СИСТЕМЫ И СПОСОБЫ УПРАВЛЕНИЯ ДРАЙВЕРАМИ В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 2002 |

|

RU2304305C2 |

| КОНФИГУРАЦИЯ АРХИТЕКТУРНОГО РЕЖИМА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 2015 |

|

RU2664413C2 |

| СПОСОБ, ОПЕРАЦИОННАЯ СИСТЕМА И ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ КОМПЬЮТЕРНОЙ ПРОГРАММЫ | 2005 |

|

RU2431182C2 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОПОТОКОВОЙ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ И СПОСОБ ОБРАБОТКИ С ИСПОЛЬЗОВАНИЕМ ДАННОГО МОДУЛЯ | 2018 |

|

RU2708794C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ГЕНЕРИРОВАНИЯ СИГНАЛА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, ВКЛЮЧАЮЩЕЙ В СЕБЯ НЕСКОЛЬКО КОМПОНЕНТОВ | 2005 |

|

RU2384877C2 |

| МНОГОПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2012 |

|

RU2502126C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ДОСТУПОМ К ПАМЯТИ В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ ПО МЕНЬШЕЙ МЕРЕ С ДВУМЯ ИСПОЛНИТЕЛЬНЫМИ БЛОКАМИ | 2006 |

|

RU2406114C2 |

| Вычислительная система для научно-технических расчетов | 2018 |

|