(54) СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Цифровой синтезатор частоты | 1985 |

|

SU1325693A1 |

| Синтезатор частот | 1985 |

|

SU1327288A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

Изобретение относится к радиотехнике, может использоваться для формирования сетки частот в радиопередающих и радиоприемных устройствах.

Известен синтезатор частот, содержащий последовательно соединенные опорный генератор, фазовый детектор, первый фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления 1.

Однако известный синтезатор частот имеет недостаточно высокое быстродействие и недостаточно малый уровень выходных щумов, обусловленные узкололосностью контура фазовой автоподстройки частоты (ФАПЧ) и его ограниченной полосы пропускания.

Цель изобретения - повышение быстродействия и снижение уровня выходных щумов.

Для этого в известный синтезатор частот между выходом делителя частоты с переменным коэффициентом деления и другим входом фазового детектора введены последовательно -соединенные сумматор, цифроаналоговый преобразователь, второй фильтр нижних частот и формирователь импульсов, при этом к информационным входам сумматора подключен вновь введенный регистр кода.

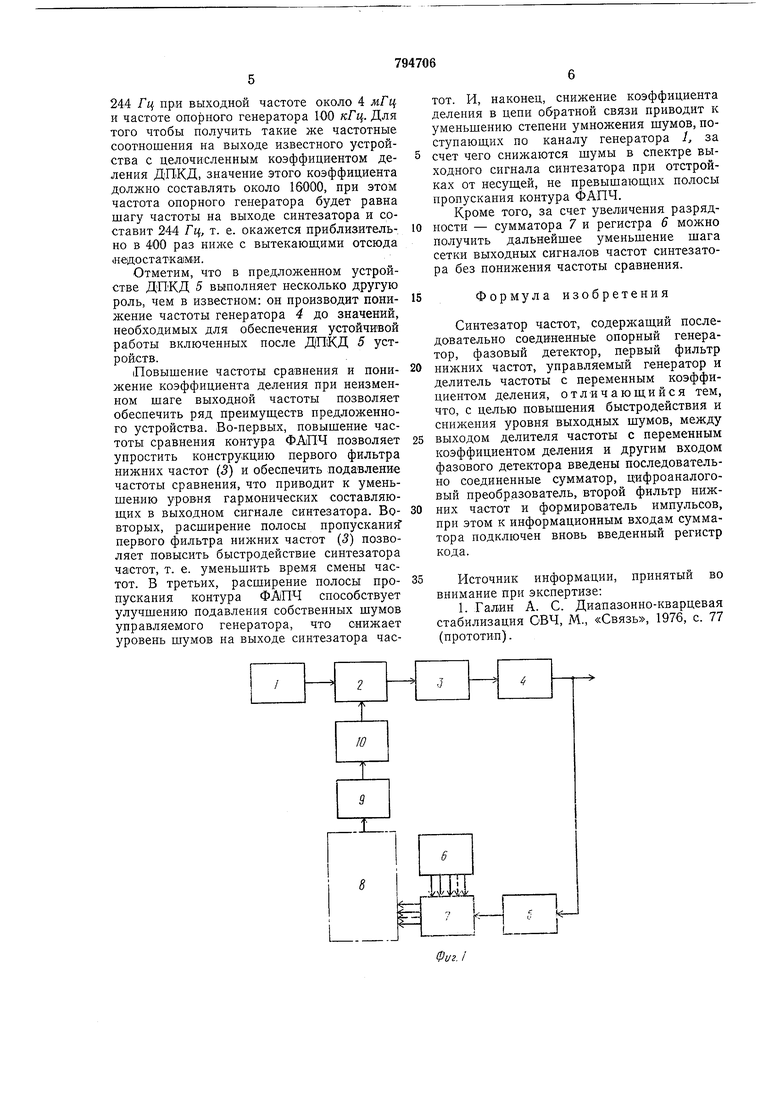

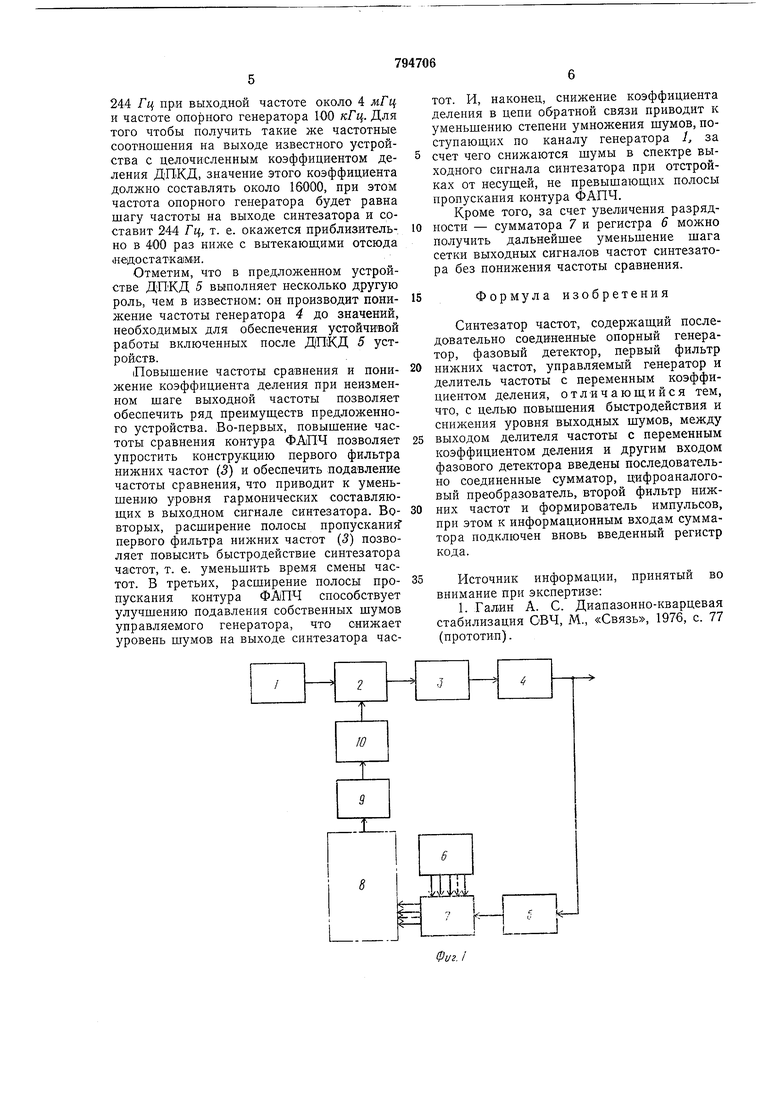

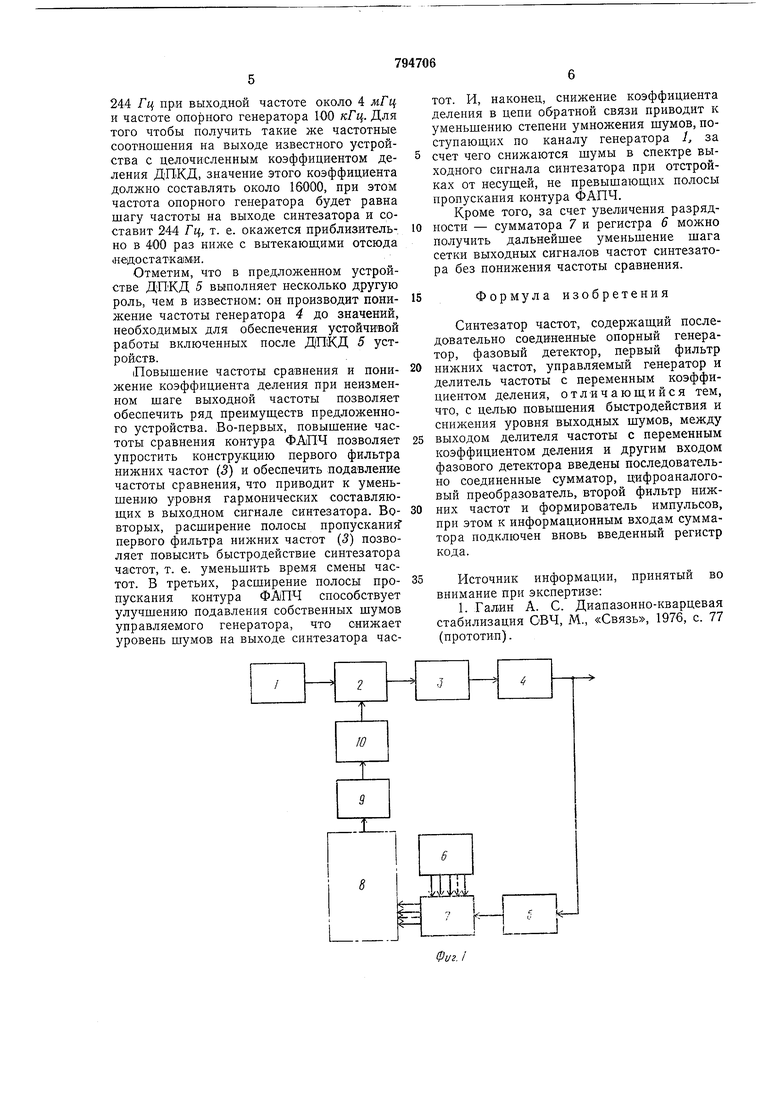

На фиг. 1 представлена структурная схема предлагаемого синтезатора частот; на фиг. 2 - временные диаграммы работы устройства. Синтезатор частот содержит

опорный генератор 1, фазовый детектор 2, первый фильтр нижних частот 3, управляемый генератора, делитель 5 частоты с переменным коэффициентом деления (ДПКД), регистр 6 кода, сумматор 7, цифроаналоговый преобразователь (ДАП) 8, второй фильтр 9 нижних частот и формирователь 10 импульсов.

Синтезатор частот работает следующим образом.

Генератор / предназначен для синхронизации синтезатора частоты. Детектор 2 сравнивает частоту генератоа / с частотой, поступающей на детектор 2 по цепи обратной связи с выхода формирователя 10, и

вырабатывает сигнал ошибки, пропорциональный разности фаз сравниваемых сигналов, фильтр 3 выделяет постоянную составляющую сигнала и подает ее на вход управляемого генератора 4. Генератор 4

служит для формирования сетки частот: его выход является выходом синтезатора. ДПКД 5 предназначен для предварительного деления частоты генератора 4; коэффициент деления ДПКД 5 в предложенном

синтезаторе выбирается значительно меньшим, чем в известном. Сумматор 7 используется для последовательного суммирования при поступлении импульсов с выхода ДПКД 5 значения кода частоты, записываемого в регистре кода 6.

Преобразователь 8 преобразует код сумматора 7 в соответствующие значения напряжения. Фильтр 9 используется для формирования аналогового синусоидального сигнала по дискретным выборкам.

Формирователь 10 служит для формирования импульсов, соответствующих нулям синусоиды на выходе фильтра 9.

На фиг. 2 приведены временные диаграммы, поясняющие работу синтезатора частот. Здесь U, -- сигнал на выходе генератора 4, Us - сигнал на выходе ДПКД 5, Кл - код, записанный в накопительном сумматоре 7, N - полная емкость накопительного сумматора 7, п - код, установленный в регистре кода 6, tn - момент переполнения накопительного сумматора 7, С - остаток кода после переполнения накопительного сумматора 7, Us - сигнал на выходе преобразователя 8, UQ - выходной сигнал фильтра 9, f/io - выходной сигнал формирователя 10, Дт - фазовый сдвиг сигнала на выходе формирователя 10 относительно сигнала генератора 4, U - сигнал на выходе генератора 1, U - сигнал на выходе детектора 2.

Выходная частота генератора 4 предварительно делится на коэффициент М ДпКД 5 до частоты, необходимой для устойчивой работы устройств, подключенных к выходу ДПКД 5 (на фиг. 2 для примера М 2). Импульсы с выхода ДПКД 5 поступают на синхронизирующий вход сумматора 7, и при поступлении калсдого нмпульса в сумматор 7 заносится содержимое регистра кода частоты п. При превышении емкости N сумматора 7 происходит его переполнение (момент /„), и процесс повторяется, но на этот раз суммирование начинается со значения С - остатка кода после переполнения.

Выходной код сумматора 7 поступает на ВХОД ЦАП 8, который сначала выполняет лреобразование кода сумматора 7 в код синусоиды, ирнчем емкость сумматора 7 N полагается равной одному нериоду синусоиды, т. е. 2я, частота синусоиды которой будет в NIn раз меньще частоты сигнала на выходе сумматора 7, следовательно, выходная частота генератора 4 будет уменьшена в М NIn раз. Затем цифровые значения синусоиды преобразуются в соответствующее входному коду напряжение. Напряжение с выхода преобразователя 8 поступает на фильтр 9, который выделяет аналоговый синусоидальный сигнал из выходного сигнала. Формирователь 10 вырабатывает сигналы, соответствующие моментам пере.хода синусоиды через нулевой уровень; затем фаза выходного сигнала формирователя 10 сравнивается на детекторе 2 с фазой сигнала генератора /. На выходе детектора 2 вырабатывается сигнал ощибки, который фильтруется на фильтре 3 и поступает на вход генератора 4 для подстройки частоты.

Частота синусоиды на выходе фильтра 9 (/ос ) связана с частотой на выходе генератора 4 (tyr) следующим соотнощением:

,.гflлл

/OJ zir /уг д| дг; 1Де /И--коэффициент деления

ДПКД 5. Таким образом, выходная частота генератора 4 будет разделена на М NIn. Поскольку в синтезаторах с делителем в цепи обратной связи частота выходного сигнала равна частоте входного, умнолсенной на коэффициент деления в цепн обратной связи, то для рассматриваемой схемы можно записать

M-N

п

где /ог - частота опорного генератора /.

Поскольку в общем случае числа М и п, N и п не являются кратными, то результирующий коэффициент умножения оказывается дробным.

Момент появления сигнала на выходе формирователя 10 в общем случае не совпадает с моментом появления сигнала на выходе генератора 4 (фазовый сдвиг Ат), что соответствует некратному делению частоты генератора 4 (фиг. 2).

Указанное некратное деление частоты выполняется с помощью цифровых методов, что обеспечивает высокую точность деления, и, кроме того, синусоида, иа выходе

второго фильтра нижних частот получается равномерно распределенной относительно выходного сигнала управляемого генератора.

:Как следует из теории Котельникова,

для формирования аналоговой синусоиды по дискретным выборкам необходимо не менее двух выборок на период синусоиды. На практике однако для облегчения требований к фильтру нижних частот (блок 9 в

данном устройстве, фиг. 1), берется не менее четырех выборок. Следовательно, отнощение NIn должно быть ие меньше 4. Для примера возьмем М 10, N 2, п -i 116383. При этом результирующий коэффициент деления будет равен 10 X Хв5636/16383 40,00244. Если задать п 16382, то результирующий коэффициент деления составит 10X65536/l&3i82 40,00488. Если выбрать, например, частоту генератора / равной ГОО кГц, то двум этим коэффициентам будут соответствовать следующие значения частоты управляемого генератора (и, следовательно, синтезатора) : 4,000244 мГц и 4,000488 мГц. Шаг частоты на выходе синтезатора составит

244 Гц пр,и выходной частоте около 4 мГц и частоте опорного генератора 100 кГц. Для того чтобы получить такие же частотные соотношения на выходе известного устройства с целочисленным коэффициентом деления ДПКД, значение этого коэффициента должно составлять около ШООО, при этом частота опорного генератора будет равна шагу частоты на выходе синтезатора и составит 244 Гц, т. е. окажется приблизительно в 400 раз нилсе с вытекаюш,ими отсюда (Недостатками.

Отметим, что в предложенном устройстве ДПКД 5 выполняет несколько другую роль, чем в известном: он производит понижение частоты генератора 4 до значений, необходимых для обеспечения устойчивой работы включенных после 5 устройств.

Повышение частоты сравнения и понижение коэффициента деления при неизменном шаге выходной частоты позволяет обеспечить ряд преимуществ предложенного устройства. Во-первых, повышение частоты сравнения контура ФАПЧ позволяет упростить конструкцию первого фильтра нижних частот (5) и обеспечить лодавление частоты сравнения, что приводит к уменьшению уровня гармонических составляющих в выходном сигнале синтезатора. Вовторых, расширение полосы пропускани5Г первого фильтра нижних частот (5) позволяет повысить быстродействие синтезатора частот, т. е. уменьшить время смены частот. В третьих, расширение полосы пропускания контура ФАШЧ способствует улучшению подавления собственных шумов управляемого генератора, что снижает уровень шумов на выходе синтезатора частот. И, наконец, снижение коэффициента деления в цени обратной связи приводит к уменьшению степени умножения шумов, поступающих по каналу генератора /, за счет чего снижаются шумы в спектре выходного сигнала синтезатора при отстройках от несущей, не превышающих полосы пропускания контура ФАПЧ.

Кроме того, за счет увеличения разрядности - сумматора 7 и регистра 6 можно получить дальнейшее уменьшение шага сетки выходных сигналов частот синтезатора без понижения частоты сравнения.

Формула изобретения

Синтезатор частот, содержащий последовательно соединенные опорный генератор, фазовый детектор, первый фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, отличающийся тем, что, с целью повышения быстродействия и снижения уровня выходных шумов, между выходом делителя частоты с переменным коэффициентом деления и другим входом фазового детектора введены последовательно соединенные сумматор, цифроаналоговый преобразователь, второй фильтр нижних частот и формирователь импульсов, при этом к информационным входам сумматора подключен вновь введенный регистр кода.

Источник информации, принятый во внимание при экспертизе:

Js

7

.7

А /

ю

жт

w

Авторы

Даты

1981-01-07—Публикация

1978-11-27—Подача