Предлагаемое изобретение относится к вычислительной и информационно-измерительной технике.

Известно интегрирующее устройство, содержащее интегрирующий и дозирующий конденсаторы, преобразователь тока в частоту следования импульсов, делитель частоты и шестриразрядный счетчик (А.с. СССР №432529, кл. G06G 7/18, 1974).

Недостатком этого устройства являются ограниченные функциональные возможности - неспособность определять также скорость изменения входного сигнала.

Наиболее близким техническим решением является интегратор постоянного напряжения, содержащий генератор импульсов, подключенный к входу двоичного счетчика, и последовательно соединенные делитель частоты и счетчик, а также компаратор, цифроаналоговый преобразователь и элемент И, входы которого соединены соответственно с выходами компаратора и генератора импульсов, а выход подключен к делителю частоты, выходы двоичного счетчика - к входу цифроаналогового преобразователя, выход которого соединен с первым входом компаратора, второй вход которого является входом интегратора (А.с. СССР №942052, кл. G06G 7/18, 1982).

Недостатком этого устройства являются также ограниченные функциональные возможности - неспособность определять скорость изменения входного сигнала.

Техническая сущность предлагаемого изобретения состоит в дополнительном введении в устройство Т-триггера, реверсивного счетчика импульсов и регистра памяти.

Техническим результатом предлагаемого изобретения является расширение функциональных возможностей устройства - способности определять не только интегральное значение входного сигнала, но и скорость его изменения.

Технический результат достигается тем, что интегратор постоянного напряжения, содержащий генератор импульсов, подключенный к входу двоичного счетчика, и последовательно соединенные делитель частоты и счетчик, а также компаратор, цифроаналоговый преобразователь и элемент И, входы которого соединены соответственно с выходами компаратора и генератора импульсов, а выход подключен к делителю частоты, выходы двоичного счетчика - к входам цифроаналогового преобразователя, выход которого соединен с вторым входом компаратора, первый вход которого является входом интегратора, дополнительно снабжен Т-триггером, реверсивным счетчиком импульсов и регистром памяти, входы которого связаны с выходами реверсивного счетчика, а выход компаратора через последовательно соединенный Т-триггер соединен с входом управления режимом работы реверсивного счетчика, счетный вход которого подключен к выходу делителя частоты и входу счетчика.

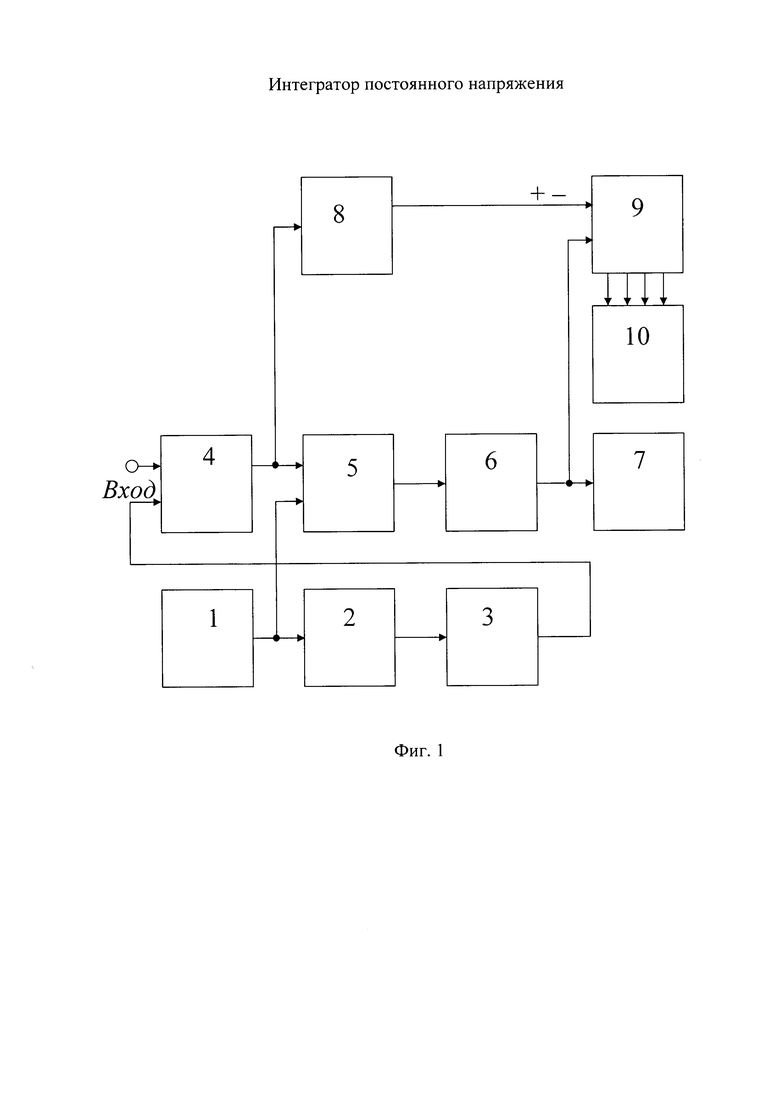

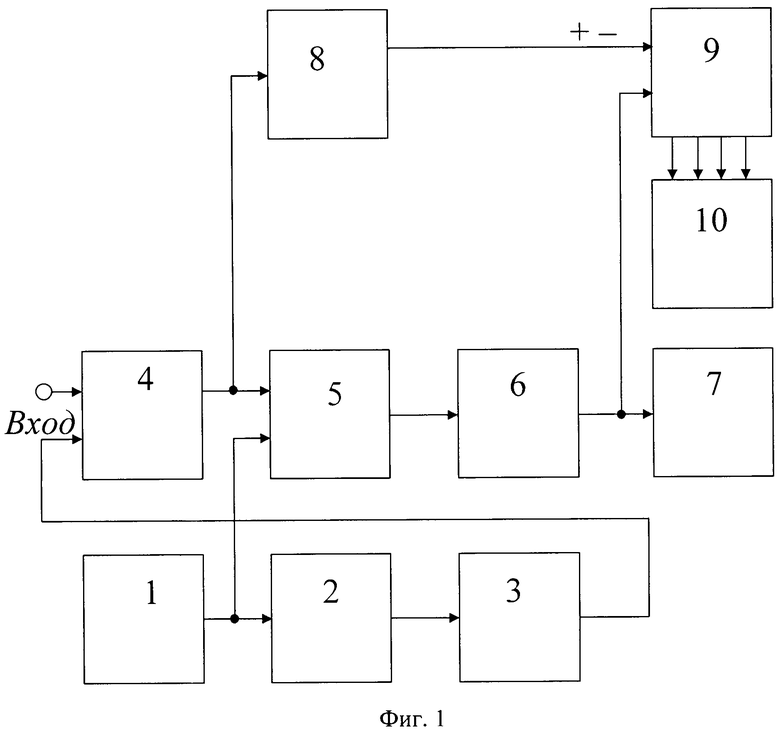

Схема интегратора постоянного напряжения представлена на фиг. 1.

Интегратор постоянного напряжения содержит генератор 1 импульсов, двоичный счетчик 2, соединенный своими выходами с входом цифроаналогового преобразователя 3, подключенного выходом ко второму входу компаратора 4, первый вход которого соединен с входом устройства, а выход компаратора 4 через последовательно соединенные схему И 5 и делитель частоты 6 связан с входом счетчика импульсов 7, выход компаратора 4 через Т-триггер 8 соединен с входом управления режимом работы реверсивного счетчика (PC) импульсов 9, счетный вход которого связан с выходом делителя частоты 6 и входом счетчика 7, а выходы PC 9 подключены к регистру памяти 10, при этом выход генератора 1 соединен со счетным входом счетчика 2 и вторым входом схемы «И» 5, первый вход которого связан с выходом компаратора 4.

Интегратор постоянного напряжения работает следующим образом.

Двоичный счетчик 2 заполняется импульсами генератора 1 образцовой частоты. Цифроаналоговый преобразователь (ЦАП) 3 преобразует код счетчика 2 в ступенчато-изменяющееся напряжение на втором входе компаратора 4.

В исходном состоянии Т-триггер 8 и счетчик 2 находятся в нулевом состоянии, компаратор 4 своим выходным сигналом на 1-ом входе схемы «И» 5 разрешает импульсам с генератора 1 поступать через делитель частоты 6 на суммирующий вход счетчика 7, Т-триггер 8 устанавливает PC 9 в режим сложения. Как только напряжения на выходе ЦАП 3 и первом входе компаратора 4 сравняются компаратор переключается, закрывая схему «И» 5. Счетчик 2 продолжает заполняться импульсами генератора 1 до своего полного заполнения и появления импульса переполнения, т.е. своего обнуления и падения напряжения на выходе ЦАП 3. Процесс интегрирования циклически повторяется. Значение интеграла входного сигнала записывается в счетчике 7.

При падении напряжения на выходе ЦАП 3 и переключении компаратора 4 происходит переключение Т-триггера 8, который переводит PC 9 в режим вычитания. В режиме вычитания из ранее записанного числа в PC 9 происходит вычитание импульсов в последующем цикле. После окончания цикла вычитания разность чисел переносится в регистр памяти 10 (шина установки схемы в исходное состояние и переноса кода разности из PC 9 в регистр памяти 10 условно не показана).

Таким образом, введение в схему интегратора постоянного напряжения Т-триггера, реверсивного счетчика импульсов и регистра памяти позволило существенно расширить функциональные возможности прототипа, а именно получать информацию не только об интегральном значении входной величины, но и о скорости ее изменения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ | 1991 |

|

RU2010414C1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Цифровой синтезатор синусоидальных сигналов | 1988 |

|

SU1596427A1 |

| Устройство для управления синусоидальными вибрациями | 1985 |

|

SU1269112A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Устройство для сварки | 1988 |

|

SU1590284A1 |

| Устройство демодуляции телевизионного сигнала системы Секам | 1989 |

|

SU1688458A1 |

| Адаптивный аналого-цифровой преобразователь | 1984 |

|

SU1226666A1 |

| Регулятор частоты автономного генератора | 1989 |

|

SU1728958A1 |

Изобретение относится к вычислительной и информационно-измерительной технике. Технический результат - способность определять не только интегральное значение входного сигнала, но и скорость его изменения. Интегратор постоянного напряжения содержит генератор 1 импульсов, двоичный счетчик 2, цифроаналоговый преобразователь 3, компаратор 4, первый вход которого соединен с входом устройства, а выход компаратора 4 через последовательно соединенную схему И 5 и делитель частоты 6 связан с входом счетчика импульсов 7. Выход компаратора 4 через Т-триггер 8 соединен с входом управления режимом работы реверсивного счетчика импульсов 9. Счетный вход счетчика 9 связан с выходом делителя частоты 6 и входом счетчика 7. Выходы счетчика 9 при этом подключены к регистру памяти. Выход генератора 1 соединен со счетным входом счетчика 2 и вторым входом схемы И 5, первый вход которой связан с выходом компаратора 4. Изобретение позволяет, например, наряду с высокоточным измерением количества вещества в процессе интегрирования осуществлять высокоточное измерение скорости поступления этого вещества, что является важным в технологических процессах. 1 ил.

Интегратор постоянного напряжения, содержащий генератор импульсов, подключенный к входу двоичного счетчика, и последовательно соединенные делитель частоты и счетчик, а также компаратор, цифроаналоговый преобразователь и элемент И, входы которого соединены соответственно с выходами компаратора и генератора импульсов, а выход подключен к делителю частоты, выходы двоичного счетчика - к входам цифроаналогового преобразователя, выход которого соединен с вторым входом компаратора, первый вход которого является входом интегратора, отличающийся тем, что он дополнительно снабжен Т-триггером, реверсивным счетчиком импульсов и регистром памяти, входы которого связаны с выходами реверсивного счетчика, а выход компаратора через последовательно соединенный Т-триггер соединен с входом управления режимом работы реверсивного счетчика, счетный вход которого подключен к выходу делителя частоты и входу счетчика.

| Интегратор постоянного напряжения | 1980 |

|

SU942052A1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU432529A1 |

| Интегратор | 1981 |

|

SU1081643A2 |

| JPS5680775 A, 02.07.1981 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ РЕБРИСТЫХ ПАНЕЛЕЙ | 2010 |

|

RU2443527C2 |

| JPH05151372 A, 18.06.1993. | |||

Авторы

Даты

2016-11-20—Публикация

2015-07-07—Подача