Изобретение относится к области радиотехники и автоматики и может быть также использовано в измерительной технике в качестве устройства усиления сигналов различных сенсоров с токовым выходом.

В современной микроэлектронике широкое распространение получили дифференциальные усилители напряжения (ДУН), обеспечивающие подавление входных синфазных и усиление входных дифференциальных (разностных) напряжений [1, 2]. В то же время схемотехника дифференциальных усилителей токов (ДУТ), эффективно подавляющих синфазную составляющую двух независимых входных токов и усиливающих их разность при малом собственном токопотреблении, в технической литературе не описаны. Заявляемое устройство относится именно к этому (дуальному ДУН) классу преобразователей сигналов. Разработка микросхем дифференциальных усилителей двунаправленных входных токов позволяет создать сотни новых устройств автоматики и измерительной техники, эффективно использующих особые качества предлагаемого функционального узла - усиление независящих друг от друга и имеющих малое входное сопротивление по каждому из входов дифференциальных токов в широком диапазоне их изменений.

В соответствии с классическим определением идеальный усилитель тока I1 (УТ) должен иметь нулевое входное сопротивление, большое выходное сопротивление, а также нулевой потенциал входного узла как на постоянном, так и на переменном токах, а кроме этого обеспечить преобразование как втекающего, так и вытекающего токов в широком диапазоне изменений их амплитуды.

Дифференциальный усилитель тока (ДУТ) характеризуется также ослаблением синфазных составляющих входных токов I1 и I2.

Известные схемы дифференциальных усилителей тока [3-23] удовлетворяют вышеперечисленным свойствам не в полной мере:

1. В дифференциальном усилителе тока, представленном в патенте US 5.798.660 (fig. 3), статические потенциалы токовых входов значительно отличаются от потенциала общей шины.

2. Преобразование однонаправленных фототоков различных типов фотодиодов осуществляется с помощью усилителей токов с отрицательной обратной связью [US 6.125.094 fig. 3, fig. 4; US 5.867.066 fig. 4; ЕР 0738038 fig. 3].

3. В технике усиления и преобразования сигналов находят применение так называемые операционные усилители с токовой отрицательной обратной связью [US 8.159.304, fig. 5, US 5.479.133, fig. 1], которые имеют два неравнозначных входа - один токовый низкоомный, второй потенциальный с высоким входным сопротивлением. Такая несимметрия по входам сужает области применения данных устройств.

4. В известном дифференциальном усилителе токов [US 6.281.741, fig. 3, fig. 4] максимальные значения вытекающих входных токов жестко связаны со статическим током входных транзисторов схемы, что отрицательно сказывается на ее энергетических параметрах. Эти схемы не обеспечивают эффективное усиление двунаправленных входных токов, если их величина превышает некоторое максимальное значение Iвх.max, зависящие от статического тока эмиттера транзисторов схемы. Такой режим характерен для транзисторных каскадов, работающих в режиме класса «А».

5. Для «цифрового» преобразования однополярных токовых сигналов (I1, I2) дифференциальной линий связи используют ДУТ на полевых транзисторах [US 2002/0008549 fig. 3]. В данных схемах максимальные значения I1 и I2 жестко связаны с токовыми координатами входных КМОП транзисторов в статическом режиме.

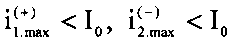

6. В микроэлектронике применяются также дифференциальные усилители приращений двух входных токов  ,

, относительно их статического уровня I0 [US 5.132.640, фирма Toshiba]. Для ДУТ данного подкласса также характерна взаимосвязь между максимальными приращениями входных токов и статическим током потребления (

относительно их статического уровня I0 [US 5.132.640, фирма Toshiba]. Для ДУТ данного подкласса также характерна взаимосвязь между максимальными приращениями входных токов и статическим током потребления ( ).

).

7. В дифференциальных усилителях однополярных (втекающих) токов, представленных в патенте фирмы Hitachi [US 4.258.330], работоспособность обеспечивается только в том случае, если один из входных токов (Iвx.1) всегда больше второго входного тока (Iвx.2)> т.е. Iвx.1≥ Iвx.2. Данное ограничение сужает область практического применения ДУТ данного подкласса.

8. Известны также схемы дифференциальных усилителей тока [US 4.429.283, fig. 2], которые обеспечивают усиление (преобразование) токов только одной полярности (втекающих или вытекающих). При высоких внутренних сопротивлениях токовых источников сигналов в данных схемах возникает проблема установления стабильного статического режима.

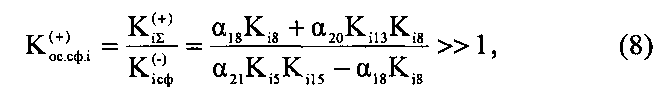

Ближайшим прототипом заявляемого устройства является усилитель тока по патенту US 7.791.414. Он содержит первый 1 и второй 2 дифференциальные входы устройства, первый 3 входной каскад усиления тока, низкоомный вход которого соединен с первым 1 входом устройства, первый 4 токовый выход первого 3 входного каскада усиления тока связан со входом первого 5 токового зеркала, согласованного с первой 6 шиной источника питания, второй 7 токовый выход первого 3 входного каскада усиления тока связан со входом второго 8 токового зеркала, согласованного со второй 9 шиной источника питания, токовый выход устройства 10 связан с токовыми выходами первого 5 и второго 8 токовых зеркал.

Существенный недостаток известного устройства состоит в том, что он не обеспечивает усиление разности двух независящих друг от друга входных токов произвольной полярности и подавление их синфазной (одинаковой) составляющей.

Основная задача предлагаемого изобретения состоит в создании энергоэкономичного устройства для усиления разности двух входных токов произвольной полярности (втекающих или вытекающих) и подавления их синфазной составляющей в широком диапазоне, независимо от статического токопотребления (Iпот) устройства. В частном случае при нулевых входных токах общий потребляемый от источника питания ток заявляемого устройства может быть достаточного мал или близок к нулю (Iпот≈0).

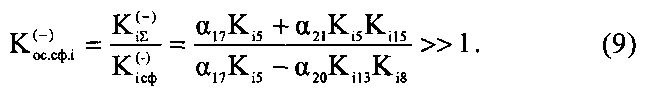

Поставленная задача решается тем, что в усилителе тока фиг. 1, содержащем первый 1 и второй 2 дифференциальные входы устройства, первый 3 входной каскад усиления тока, низкоомный вход которого соединен с первым 1 входом устройства, первый 4 токовый выход первого 3 входного каскада усиления тока связан со входом первого 5 токового зеркала, согласованного с первой 6 шиной источника питания, второй 7 токовый выход первого 3 входного каскада усиления тока связан со входом второго 8 токового зеркала, согласованного со второй 9 шиной источника питания, токовый выход устройства 10 связан с токовыми выходами первого 5 и второго 8 токовых зеркал, предусмотрены новые элементы и связи - в схему введен второй 11 входной каскад усиления тока, низкоомный вход которого соединен со вторым 2 входом устройства, первый 12 токовый выход второго 11 входного каскада усиления тока связан со входом третьего 13 токового зеркала, согласованного с первой 6 шиной источника питания, второй 14 токовый выход второго 11 входного каскада усиления тока связан со входом четвертого 15 токового зеркала, согласованного со второй 9 шиной источника питания, причем токовый выход третьего 13 токового зеркала соединен со входом второго 8 токового зеркала, а токовый выход четвертого 15 токового зеркала соединен со входом первого 5 токового зеркала.

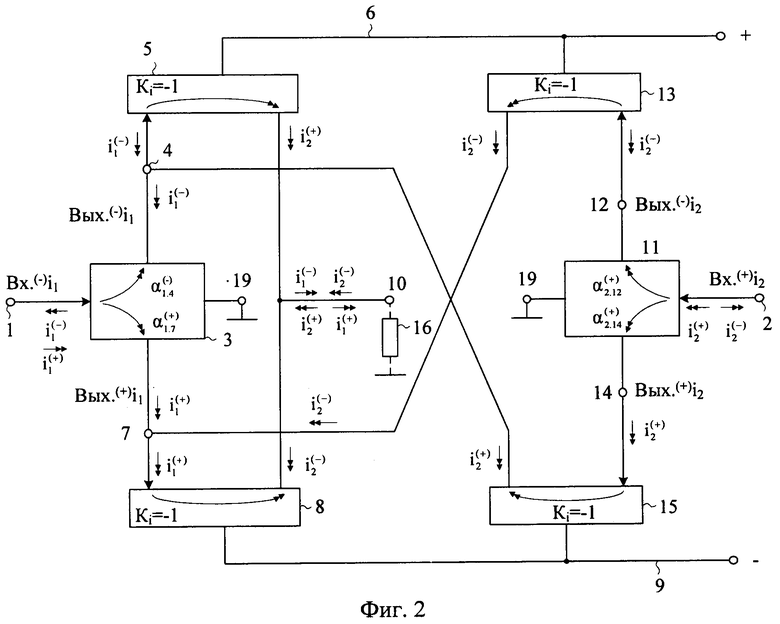

На фиг. 1 представлена схема ДУТ - прототипа, а на фиг. 2 схема заявляемого устройства в соответствии с пунктом 1 формулы изобретения.

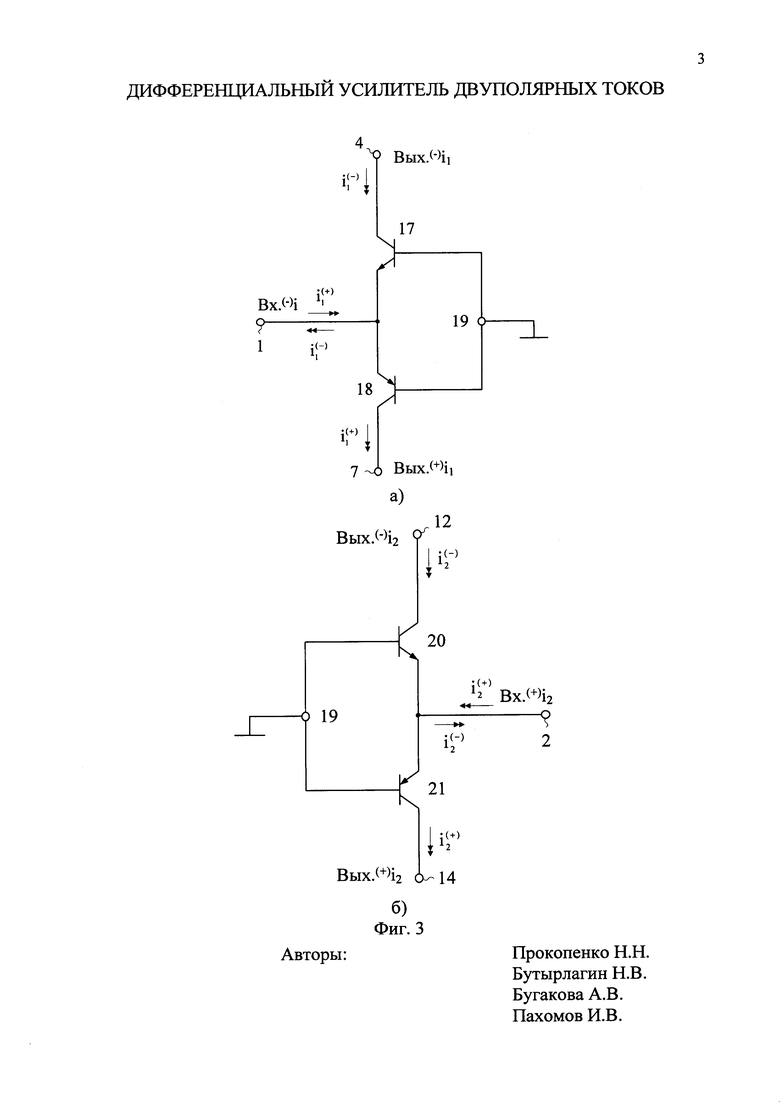

На фиг. 3а показана схема первого 3 входного каскада усиления тока в соответствии с пунктом 2 формулы изобретения.

На фиг. 3б показана схема второго 11 входного каскада усиления тока в соответствии с пунктом 3 формулы изобретения.

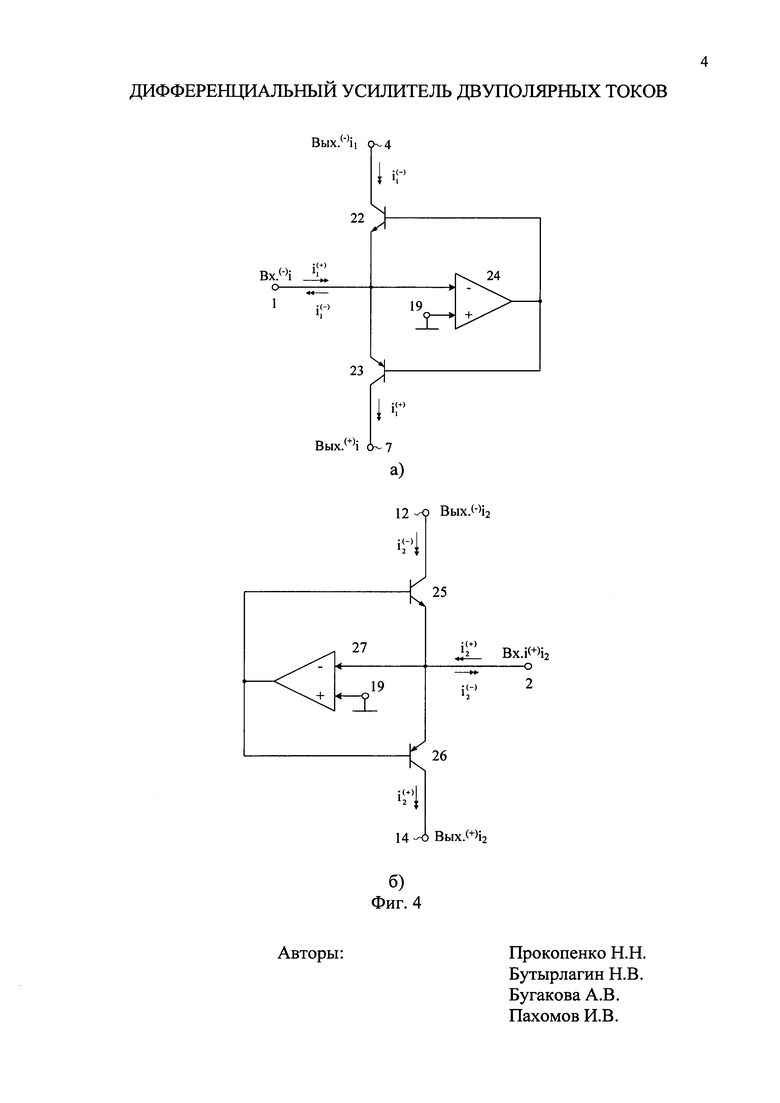

На фиг. 4а показана схема первого 3 входного каскада усиления тока в соответствии с пунктом 4 формулы изобретения.

На фиг. 4б показана схема второго 11 входного каскада усиления тока в соответствии с пунктом 5 формулы изобретения.

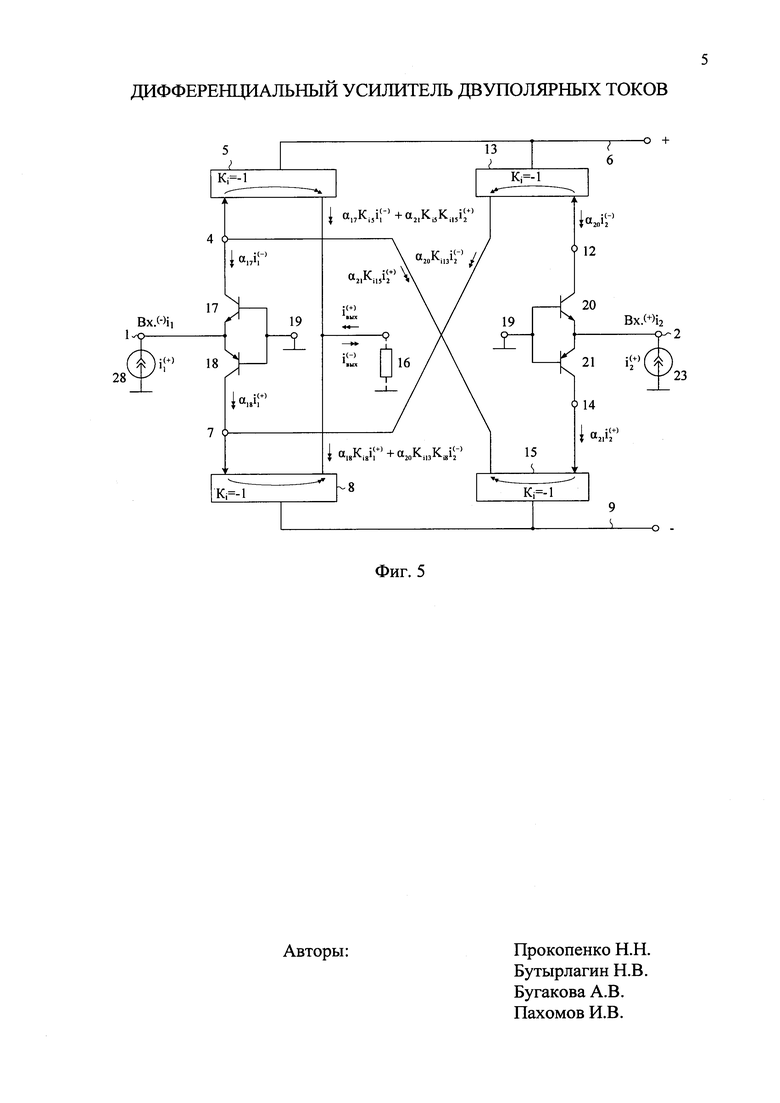

На фиг. 5 представлена схема заявляемого устройства фиг. 2 для случая, когда первый 3 и второй 11 входные каскады усиления тока выполнены соответственно на основе схем фиг. 3а и фиг. 3б.

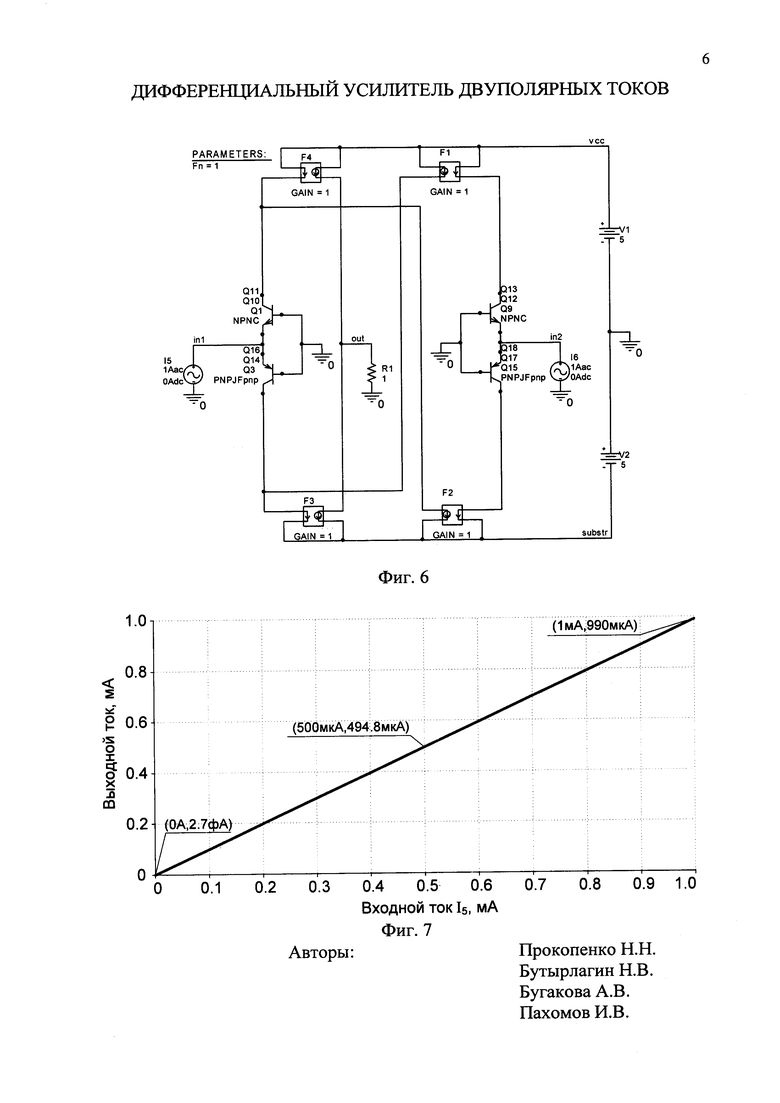

На фиг. 6 представлена схема заявляемого устройства фиг. 5 в среде PSpice на радиационно зависимых моделях интегральных транзисторов АБМК_1.4 ОАО «Интеграл» (г. Минск) для случая, когда входные каскады усиления тока 3 и 11 выполнены в соответствии с фиг. 3а и фиг. 3б.

На фиг. 7 приведена зависимость выходного тока устройства фиг. 6 от входного втекающего тока первого 1 входа устройства, при условии, что входной ток второго 2 входа равен нулю.

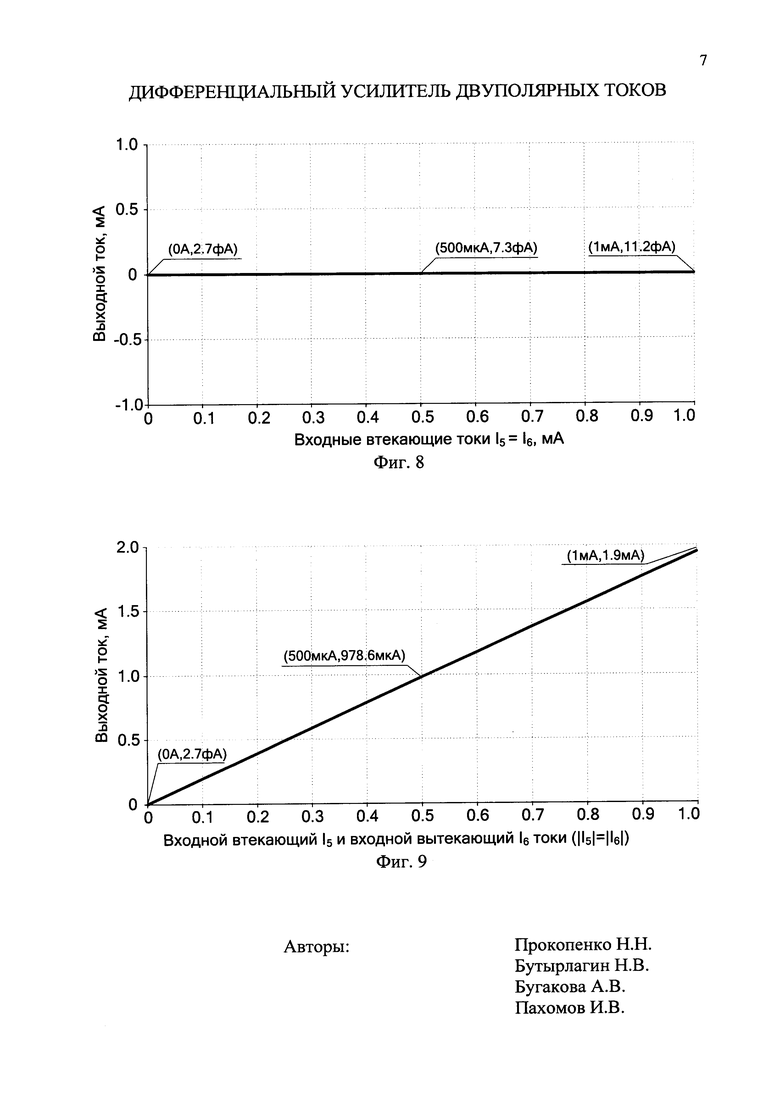

На фиг. 8 приведена зависимость выходного тока устройства фиг. 6 от входных втекающих токов первого 1 и второго 2 входов, для случая, когда эти токи синфазны (одинаковы). Из данного графика следует, что заявляемое устройство обеспечивает подавление синфазных входных токов.

На фиг. 9 приведена зависимость выходного тока устройства фиг. 6 от входных противофазных токов первого 1 и второго 2 входов, для случая, когда эти токи противофазны (один втекает, другой вытекает). Из данного графика следует, что устройство обеспечивает усиление дифференциальных входных токов.

Дифференциальный усилитель двуполярных токов фиг. 2 содержит первый 1 и второй 2 дифференциальные входы устройства, первый 3 входной каскад усиления тока, низкоомный вход которого соединен с первым 1 входом устройства, первый 4 токовый выход первого 3 входного каскада усиления тока связан со входом первого 5 токового зеркала, согласованного с первой 6 шиной источника питания, второй 7 токовый выход первого 3 входного каскада усиления тока связан со входом второго 8 токового зеркала, согласованного со второй 9 шиной источника питания, токовый выход устройства 10 связан с токовыми выходами первого 5 и второго 8 токовых зеркал. В схему введен второй 11 входной каскад усиления тока, низкоомный вход которого соединен со вторым 2 входом устройства, первый 12 токовый выход второго 11 входного каскада усиления тока связан со входом третьего 13 токового зеркала, согласованного с первой 6 шиной источника питания, второй 14 токовый выход второго 11 входного каскада усиления тока связан со входом четвертого 15 токового зеркала, согласованного со второй 9 шиной источника питания, причем токовый выход третьего 13 токового зеркала соединен со входом второго 8 токового зеркала, а токовый выход четвертого 15 токового зеркала соединен со входом первого 5 токового зеркала.

На фиг. 2 резистор 16 моделирует свойства нагрузки, подключаемой к токовому выходу устройству 10, а узел 19 является общей шиной источников питания 6 и 9.

На фиг. 3а в соответствии с п. 2 формулы изобретения первый 3 входной каскад усиления тока содержит первый 17 и второй 18 входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с первым 1 входом устройства, коллектор первого 17 входного транзистора соединен с первым 4 токовым выходом первого 3 входного каскада усиления тока, коллектор второго 18 входного транзистора соединен со вторым 7 токовым выходом первого 3 входного каскада усиления тока, причем объединенные базы первого 17 и второго 18 входных транзисторов связаны с общей 19 шиной источника питания.

На фиг. 3б в соответствии с п. 3 формулы изобретения второй 11 входной каскад усиления тока содержит третий 20 и четвертый 21 входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены со вторым 2 входом устройства, коллектор третьего 20 входного транзистора соединен с первым 12 токовым выходом второго 11 входного каскада усиления тока, коллектор четвертого 21 входного транзистора соединен со вторым 14 токовым выходом второго 11 входного каскада усиления тока, причем объединенные базы третьего 20 и четвертого 21 входных транзисторов связаны с общей 19 шиной источника питания.

На фиг. 4а в соответствии с п. 4 формулы изобретения первый 3 входной каскад усиления тока содержит пятый 22 и шестой 23 входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с первым 1 входом устройства, коллектор пятого 22 входного транзистора соединен с первым 4 токовым выходом первого 3 входного каскада усиления тока, коллектор шестого 23 входного транзистора соединен со вторым 7 токовым выходом первого 3 входного каскада усиления тока, причем между объединенными эмиттерами пятого 22 и шестого 23 входных транзисторов и объединенными базами этих транзисторов включен первый (24) дополнительный инвертирующий дифференциальный усилитель напряжения, неинвертирующий вход которого связан с общей (19) шиной источника питания.

На фиг. 4б в соответствии с п. 5 формулы изобретения второй 11 входной каскад усиления тока содержит седьмой 25 и восьмой 26 входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены со вторым 2 входом устройства, коллектор седьмого 25 входного транзистора соединен с первым 12 токовым выходом второго 11 входного каскада усиления тока, коллектор восьмого 26 входного транзистора соединен со вторым 14 токовым выходом второго 11 входного каскада усиления тока, причем между объединенными эмиттерами седьмого 25 и восьмого 26 входных транзисторов и объединенными базами этих транзисторов включен второй 27 инвертирующий дифференциальный усилитель напряжения, неинвертирующий вход которого связан с общей 19 шиной источника питания.

На фиг. 5 источники тока 28 и 29 характеризуют токовые входные сигналы, которые могут быть как втекающими (i(+)), так и вытекающими (i(-)).

Рассмотрим работу заявляемого устройства фиг. 2 на примере схемы фиг. 5.

В статическом режиме при отсутствии входных токов (i1=i2=0) все транзисторы схемы (17, 18, 20, 21) и токовые зеркала (5, 8, 13, 15) находятся в обесточенном состоянии. При этом общее электропотребление устройства близко к нулю, а выходной ток ДУТ также равен нулю.

Если на первый 1 вход поступает некоторый втекающий ток, то он через транзистор 18 и токовое зеркало 8 передается на выход устройства 10:

где α18≈1, Ki8≈l - коэффициенты передачи по току эмиттера транзистора 18 и токового зеркала 8.

При вытекающем входном токе  выходной ток устройства

выходной ток устройства

где α17≈1, Ki5≈l - коэффициенты передачи по току эмиттера транзистора 17 и токового зеркала 5.

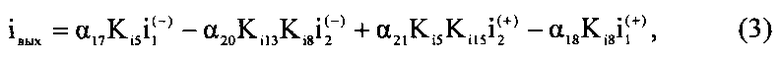

В общем случае при произвольных значениях и направлениях входных токов i1 и i2 выходной ток заявляемого устройства определяется суммой:

где αj, Kimn - коэффициенты передачи по току эмиттера j-го транзистора и mn-го токового зеркала.

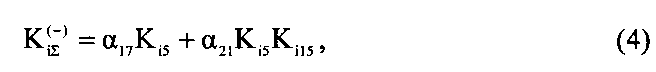

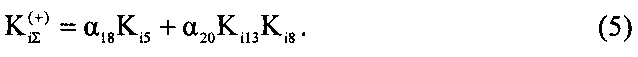

Из уравнения (3) следует, что дифференциальный коэффициент усиления одинаковых, но противофазных токов (при  втекающем, вытекающем

втекающем, вытекающем  )

)

или при  втекающем,

втекающем,  вытекающем:

вытекающем:

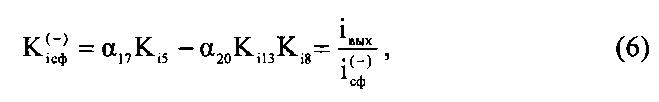

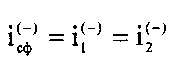

Аналогично можно найти коэффициенты передачи синфазных вытекающих токов

где - синфазный вытекающий входной ток.

- синфазный вытекающий входной ток.

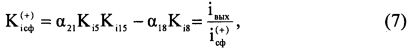

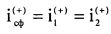

Для втекающих токов аналогичный коэффициент находится по формуле

где  - синфазный втекающий входной ток.

- синфазный втекающий входной ток.

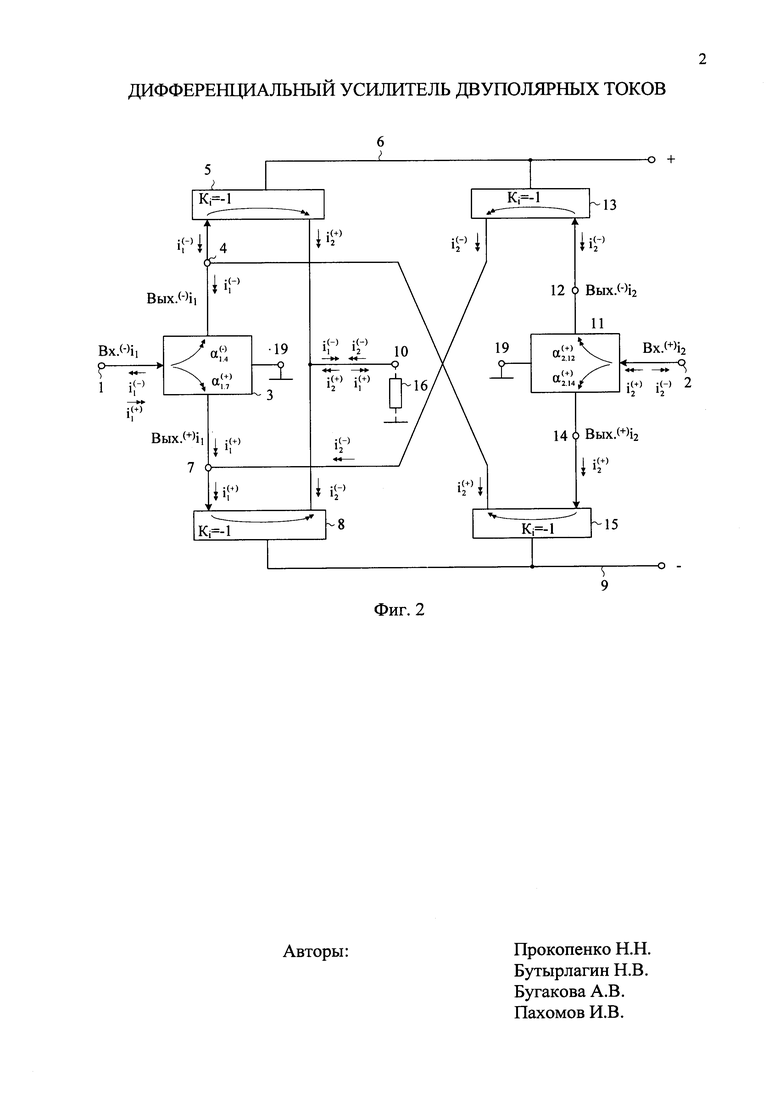

Из последних соотношений с учетом (1)-(5) можно определить коэффициенты ослабления входных синфазных токов заявляемого устройства:

Таким образом, заявляемое устройство усиливает дифференциальный токовый сигнал и ослабляет синфазную составляющую входных токов. Это подтверждается результатами моделирования (фиг. 8, фиг. 9, фиг. 10).

Для получения αij=1 в схемах фиг. 3 и фиг. 4 могут использоваться составные биполярные или КМОП транзисторы.

Численные значения коэффициентов Ki5 Ki8 Кi3 Кi15 определяются схемотехникой соответствующих токовых зеркал 5, 8, 13, 15 [1, 2] и могут (при необходимости) принимать значения Ki=1…100.

Неидентичность коэффициентов передачи токовых зеркал 5, 8, 13 и 15 может быть также минимизирована схемотехническими методами [1-2].

Для уменьшения входных сопротивлений (Rвх.1, Rвх.2) заявляемого устройства в качестве входных усилителей тока 3 и 11 могут применяться схемы фиг. 4. Здесь при соответствующем выборе коэффициента усиления по напряжению (Кy>>1) первого 24 и второго 27 дополнительных инвертирующих дифференциальных усилителей напряжения достаточно легко реализуются малые Rвх (Rвх.1≈0, Rвх.2≈0), а статические и переменные напряжения на входах 1 и 2 становятся близкими к нулю.

Таким образом, предлагаемое схемотехническое решение дифференциального усилителя токов имеет расширенные функциональные возможности и, в отличие от известных устройств данного класса, наиболее полно соответствует классическому определению дифференциальных усилителей токов.

Источники информации

1. Операционные усилители с непосредственной связью каскадов / В.И. Анисимов, М.В. Капитонов, Н.Н. Прокопенко, Ю.М. Соколов. - Л.: Энергия. Ленингр. отд-е, 1979. - 151 с.

2. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М.: Энергоатомиздат, 1983. - 216 с., ил.

3. Патент US 7.414.472.

4. Патент US 6.281.741, fig. 4.

5. Патент US 5.132.640, fig. 3, fig. 4.

6. Патент US 3.582.689.

7. Патент ЕР 0738038.

8. Патент US 5.055.719.

9. Патент US 6.125.094.

10. Патент US 6.583.670.

11. Патент US 6.885.247.

12. Патент US 5.867.066.

13. Патент US 5.821.777.

14. Патент JP 61-140210, fig. 1.

15. Патент US 4.429.283, fig. 1, fig. 2.

16. Патент US 8.913.050.

17. 3аявка на патент US 2012/0132965.

18. Патент DE 3140956.

19. Патент US 4.507.573.

20. Патент US 6.590.455.

21. Патент US 5.412.309.

22. 3аявка на патент US 2014/0361836 fig. 4a.

23. Патент US 7.215.198.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2013 |

|

RU2536376C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444116C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2589323C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2640744C1 |

| ДВОИЧНЫЙ ТОКОВЫЙ ПОРОГОВЫЙ RS-ТРИГГЕР | 2018 |

|

RU2695979C1 |

| КАСКОДНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797566C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797043C1 |

Изобретение относится к области радиотехники. Технический результат: создание энергоэкономичного устройства для усиления разности двух входных токов и подавления их синфазной составляющей. Для этого предложен дифференциальный усилитель двуполярных токов, который содержит первый и второй входы, первый входной каскад усиления тока, вход которого соединен с первым входом, первый выход первого входного каскада усиления тока связан со входом первого токового зеркала, согласованного с первой шиной питания, второй выход первого входного каскада усиления тока связан со входом второго токового зеркала, согласованного со второй шиной питания, выход устройства связан с выходами первого и второго токовых зеркал. В схему введен второй входной каскад усиления тока, вход которого соединен со вторым входом устройства, первый выход второго входного каскада усиления тока связан со входом третьего токового зеркала, согласованного с первой шиной питания, второй выход второго входного каскада усиления тока связан со входом четвертого токового зеркала, согласованного со второй шиной питания, причем выход третьего токового зеркала соединен со входом второго токового зеркала, а выход четвертого токового зеркала соединен со входом первого токового зеркала. 4 з.п. ф-лы, 9 ил.

1. Дифференциальный усилитель двуполярных токов, содержащий первый (1) и второй (2) дифференциальные входы устройства, первый (3) входной каскад усиления тока, низкоомный вход которого соединен с первым (1) входом устройства, первый (4) токовый выход первого (3) входного каскада усиления тока связан со входом первого (5) токового зеркала, согласованного с первой (6) шиной источника питания, второй (7) токовый выход первого (3) входного каскада усиления тока связан со входом второго (8) токового зеркала, согласованного со второй (9) шиной источника питания, токовый выход устройства (10) связан с токовыми выходами первого (5) и второго (8) токовых зеркал, отличающийся тем, что в схему введен второй (11) входной каскад усиления тока, низкоомный вход которого соединен со вторым (2) входом устройства, первый (12) токовый выход второго (11) входного каскада усиления тока связан со входом третьего (13) токового зеркала, согласованного с первой (6) шиной источника питания, второй (14) токовый выход второго (11) входного каскада усиления тока связан со входом четвертого (15) токового зеркала, согласованного со второй (9) шиной источника питания, причем токовый выход третьего (13) токового зеркала соединен со входом второго (8) токового зеркала, а токовый выход четвертого (15) токового зеркала соединен со входом первого (5) токового зеркала.

2. Дифференциальный усилитель двуполярных токов по п. 1, отличающийся тем, что первый (3) входной каскад усиления тока содержит первый (17) и второй (18) входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с первым (1) входом устройства, коллектор первого (17) входного транзистора соединен с первым (4) токовым выходом первого (3) входного каскада усиления тока, коллектор второго (18) входного транзистора соединен со вторым (7) токовым выходом первого (3) входного каскада усиления тока, причем объединенные базы первого (17) и второго (18) входных транзисторов связаны с общей (19) шиной источника питания.

3. Дифференциальный усилитель двуполярных токов по п. 1, отличающийся тем, что второй (11) входной каскад усиления тока содержит третий (20) и четвертый (21) входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены со вторым (2) входом устройства, коллектор третьего (20) входного транзистора соединен с первым (12) токовым выходом второго (11) входного каскада усиления тока, коллектор четвертого (21) входного транзистора соединен со вторым (14) токовым выходом второго (11) входного каскада усиления тока, причем объединенные базы третьего (20) и четвертого (21) входных транзисторов связаны с общей (19) шиной источника питания.

4. Дифференциальный усилитель двуполярных токов по п. 1, отличающийся тем, что первый (3) входной каскад усиления тока содержит пятый (22) и шестой (23) входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с первым (1) входом устройства, коллектор пятого (22) входного транзистора соединен с первым (4) токовым выходом первого (3) входного каскада усиления тока, коллектор шестого (23) входного транзистора соединен со вторым (7) токовым выходом первого (3) входного каскада усиления тока, причем между объединенными эмиттерами пятого (22) и шестого (23) входных транзисторов и объединенными базами этих транзисторов включен первый (24) дополнительный инвертирующий дифференциальный усилитель напряжения, неинвертирующий вход которого связан с общей (19) шиной источника питания.

5. Дифференциальный усилитель двуполярных токов по п. 1, отличающийся тем, что второй (11) входной каскад усиления тока содержит седьмой (25) и восьмой (26) входные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с вторым (2) входом устройства, коллектор седьмого (25) входного транзистора соединен с первым (12) токовым выходом второго (11) входного каскада усиления тока, коллектор восьмого (26) входного транзистора соединен со вторым (14) токовым выходом второго (11) входного каскада усиления тока, причем между объединенными эмиттерами седьмого (25) и восьмого (26) входных транзисторов и объединенными базами этих транзисторов включен второй (27) инвертирующий дифференциальный усилитель напряжения, неинвертирующий вход которого связан с общей (19) шиной источника питания.

| US 7791414 B1, 07.09.2010 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2284647C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292636C1 |

| US 4404528 A1, 13.09.1983. | |||

Авторы

Даты

2016-12-10—Публикация

2015-09-15—Подача