Изобретение относится к области техники связи, в частности к декодерам циклических кодов (коды Боуза-Чоудхури-Хоквингема - БЧХ-коды, коды Рида-Соломона - PC-коды) по рекомендации ITU-T G.975.1 на программируемых логических интегральных схемах (ПЛИС). Изобретение может быть использовано в высокоскоростных кодеках (кодер-декодер) волоконно-оптических систем связи, а также в других системах связи, в которых осуществляется передача и параллельное декодирование нескольких кодовых слов.

Рекомендация ITU-T G.975.1 предусматривает параллельную передачу в кадре N кодовых слов (сначала первые символы, потом вторые и т.д.).

Известны устройства параллельного декодирования N кодовых слов циклического кода [2]. Такие устройства, реализуемые на ПЛИС, включают в себя N одноканальных декодеров. Одноканальное устройство декодирования циклического кода включает в себя блок вычисления синдромов, блок формирования уравнения локаторов ошибок, блок вычисления позиций ошибок, блок вычисления значений ошибок для кодов Рида-Соломона, блок коррекции, запоминающее устройство.

К их недостаткам можно отнести высокую аппаратную сложность, связанную с одновременной работой нескольких блоков декодирования, в которых выполняются идентичные операции для всех поступивших кодовых слов.

Как правило, устройства параллельного декодирования для циклических кодов, реализуемые на ПЛИС [3], включают в себя:

- N вычислителей синдромов;

- мультиплексор синдромов;

- вычислитель коэффициентов уравнения локаторов ошибок;

- демультиплексор уравнений локаторов ошибок;

- N вычислителей позиций ошибок;

- N вычислителей значений ошибок (только для кодов Рида-Соломона);

- N корректоров информационных частей кодовых слов.

Устройства декодирования [3] имеет меньшую аппаратную сложность по сравнению с устройством [2] за счет использования только одного вычислителя коэффициентов уравнений локаторов ошибок. К недостаткам устройства относится увеличение времени декодирования N кодовых слов на (N-1)⋅Туло, где Туло - время вычисления коэффициентов уравнений локаторов ошибок одного кодового слова. Сокращение количества вычислителей коэффициентов УЛО (уравнений локаторов ошибок) обусловлено тем, что обычно Туло<<Тк, где Тк - время вычисления позиций ошибок в одном кодовом слове и Туло<<Тз, где Тз - время вычисления значений искаженных символов.

Целью предлагаемого изобретения является сокращение времени декодирования N кодовых слов устройством параллельного декодирования для циклических кодов, а также уменьшение аппаратных затрат ПЛИС при его реализации. В основе предлагаемого изобретения лежит тот факт, что в принятом кадре в подавляющем большинстве случаев не все N кодовых слов искажены, а только L<N, где L - это количество искаженных кодовых слов. Поставленная цель достигается тем, что в устройстве параллельного декодирования N - кодовых слов циклического кода на ПЛИС после параллельного вычисления синдромов N кодовых слов, только для L искаженных кодовых слов выполняется: последовательное формирование уравнений локаторов ошибок, параллельное вычисление позиций ошибок и их значений (для PC-кодов). Затем коррекция и передача на выход декодера N информационных частей кодовых слов циклического кода. В результате, уменьшается с N до L количество вычислителей позиций ошибок, а также значений ошибок для PC-кодов. Если синдром кодового слова, вычисленный в блоке вычисления синдромов, равен нулю, то мультиплексор синдромов относит кодовое слово к неискаженному. Иначе кодовое слово считается искаженным. Кроме того, известные устройства параллельного декодирования, например [3], в которых вычислитель коэффициентов уравнений локаторов ошибок осуществляет последовательное формирование уравнений локаторов ошибок, вычислители позиций и значений ошибок рассчитывают позиции и значения ошибок для всех N кодовых слов, в том числе и для неискаженных. Поэтому при использовании предлагаемого устройства параллельного декодирования для циклических кодов на ПЛИС сокращается время декодирования N кодовых слов за счет отказа от обработки «ненулевых» синдромов вычислителем коэффициентов уравнений локаторов ошибок.

Оценка p1 максимального количества искаженных кодовых слов L в кадре с инженерной точностью (3%) можно определить с помощью формулы

где ри=1-(1-р)n - вероятность искажения кодового слова длины n;

р - вероятность искажения бита в кодовом слове.

Например, по рекомендации ITU-T G.975.1 1.4 для БЧХ(2040,1952)-кода при количестве кодовых слов N=64 и р=3⋅10-4 максимальное количество искаженных кодовых слов L=37.

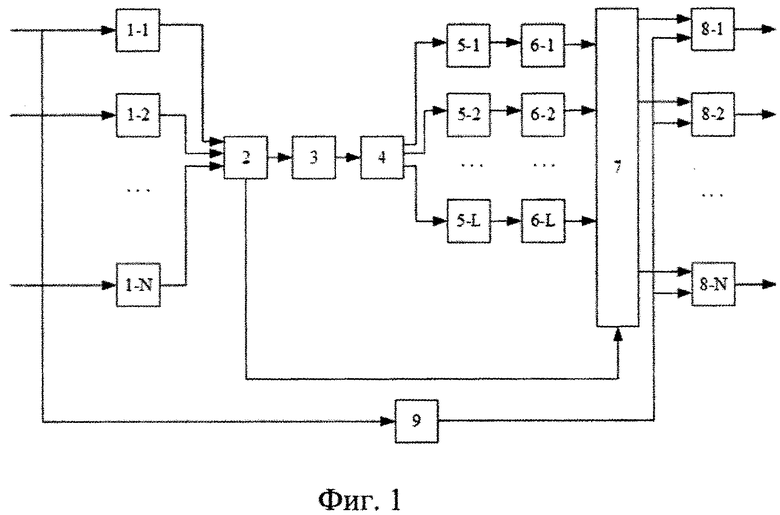

Сущность изобретения поясняется чертежом, представленным на фиг. 1, на котором изображено:

Блоки вычисления синдромов 1-1…1-N выполняют вычисление 2t синдромов для каждого принятого кодового слова соответственно.

Мультиплексор синдромов 2 выполняет параллельно-последовательное преобразование «ненулевых» синдромов (не более L), поступающих с блоков 1-1…1-N, на вход блока формирования уравнений локаторов ошибок 3. Кроме того, мультиплексор синдромов 2 формирует вектор-указатель соответствия «ненулевого» синдрома соответствующему искаженному кодовому слову и передает его распределителю векторов коррекции 7. Мультиплексор синдромов 2 содержит устройство, которое сравнивает с нулем, пришедший на его вход синдром и осуществляет его запоминание, если синдром не равен нулю. При этом любой из 2t синдромов от N кодовых слов может быть ненулевым.

Блок формирования уравнений локаторов ошибок 3 последовательно выполняет вычисление коэффициентов уравнений локаторов ошибок для искаженных кодовых слов (не более L).

Распределитель локаторов ошибок 4 последовательно распределяет уравнения локаторов ошибок, поступающие с выхода блока формирования уравнений локаторов ошибок 3 на входы блоков вычисления позиций ошибок 5-1…5-L.

Блоки вычисления позиций ошибок 5-1…5-L выполняют вычисление позиций ошибок для искаженных кодовых слов, которые вместе с рассчитанными уравнениями локаторов ошибок поступают на вход блоков вычисления значения ошибок 6-1…6-L.

Блоки вычисления значений ошибок 6-1…6-L выполняют вычисление значений ошибок на искаженных позициях кодовых слов и формируют векторы коррекции информационных частей кодовых слов, поступающие на вход распределителя векторов коррекции 7.

Распределитель векторов коррекции 7 распределяет поступившие на его вход векторы коррекции информационных частей кодовых слов на блоки коррекции информационных частей кодовых слов 8-1…8-N в соответствии со значением вектора указателя синдром - искаженное кодовое слово, поступившего с мультиплексора синдромов 2.

Блоки коррекции информационных частей кодовых слов 8-1…8-N корректируют искаженные информационные части N кодовых слов путем сложения по mod 2 соответствующих векторов коррекции и информационных частей N кодовых слов, поступающих на их входы. Откорректированные информационные части кодовых слов передаются на выход блоков коррекции информационных частей кодовых слов 8-1…8-N. Оперативное запоминающее устройство (ОЗУ) 9 предназначено для хранения информационных частей N кодовых слов циклического кода во время вычисления уравнений локаторов, позиций ошибок, значений ошибок, формирования векторов коррекции информационных частей кодовых слов, а также для последующей передачи информационных частей N кодовых слов на блоки коррекции информационных частей кодовых слов 8-1…8-N.

N блоков вычисления синдромов имеет N входов для параллельного ввода N кодовых слов циклического кода, оперативное запоминающее устройство имеет вход для ввода N кодовых слов циклического кода, а выходы N блоков вычисления синдромов соединены с N входами мультиплексора синдромов, а первый выход мультиплексора синдромов соединен с входом блока формирования уравнений локаторов ошибок искаженных кодовых слов, а второй выход мультиплексора синдромов соединен с первым входом распределителя векторов коррекции, а выход блока формирования уравнений локаторов ошибок соединен с входом распределителя локаторов ошибок, a L выходов распределителя локаторов ошибок соединены с входами L блоков вычисления позиций ошибок искаженных кодовых слов, а выходы L блоков вычисления позиций ошибок соединены с входами L блоков вычисления значений ошибок, a L выходов блоков вычисления значений ошибок соединены с L входами распределителя векторов коррекции, a L выходов распределителя векторов коррекции соединены с первыми входами L блоков коррекции информационных частей кодовых слов, а выход оперативного запоминающего устройства соединен с вторыми входами L блоков коррекции информационных частей кодовых слов, a L блоков коррекции информационных частей кодовых слов имеют L выходов для передачи откорректированных информационных частей L кодовых слов для дальнейшей обработки, где N - количество кодовых слов, поступивших на вход устройства декодирования; L - количество искаженных кодовых слов, поступивших на вход устройства декодирования.

Предлагаемое устройство работает следующим образом.

N кодовых слов циклического кода поступают на вход блоков вычисления синдромов 1-1…1-N и на вход оперативного запоминающего устройства (ОЗУ) 9 для хранения N информационных частей кодовых слов циклического кода.

Значения синдромов N кодовых слов, полученные в блоках вычисления синдромов 1-1…1-N, поступают на вход мультиплексора синдромов 2, который формирует вектор-указатель соответствия синдром искаженное кодовое слово и передает его на вход распределителя векторов коррекции 7. При этом мультиплексор синдромов 2 запоминает только «ненулевые» синдромы (не более L) и последовательно передает их на вход блока формирования уравнений локаторов ошибок 3.

Блок формирования уравнений локаторов ошибок 3 последовательно принимает синдромы искаженных кодовых слов и выполняет вычисление коэффициентов уравнений локаторов ошибок для искаженных кодовых слов (не более L).

Сформированные в блоке формирования уравнений локаторов ошибок 3 уравнения локаторов ошибок искаженных кодовых слов и их синдромы поступают на вход распределителя локаторов ошибок 4, который последовательно передает их на входы блоков вычисления позиций ошибок 5-1…5-L.

В блоках вычисления позиций ошибок 5-1…5-L для каждого искаженного кодового слова в соответствии с уравнением локаторов ошибок выполняется вычисление позиций ошибок в информационных частях искаженных кодовых слов. С выхода блоков вычисления позиций ошибок 5-1…5-L полученные позиции ошибок в информационных частях искаженных кодовых слов вместе со своими синдромами поступают на входы блоков вычисления значений ошибок 6-1…6-L, где выполняется вычисление значений ошибок на искаженных позициях информационных частей кодовых слов и формируются векторы коррекции информационных частей искаженных кодовых слов.

Сформированные векторы коррекции информационных частей искаженных кодовых слов поступают на вход оперативного запоминающего устройства (ОЗУ) 7, которое в соответствии со значениями вектора-указателя соответствия синдром - искаженное кодовое слово передает их на соответствующие блоки коррекции информационных частей кодовых слов 8-1…8-N. После завершения формирования векторов коррекции информационных частей искаженных кодовых слов (не более L) информационные части N кодовых слов с выхода оперативного запоминающего устройства (ОЗУ) 9 передаются на вход блоков коррекции информационных частей кодовых слов 8-1…8-N. В блоках коррекции информационных частей кодовых слов 8-1…8-N корректируются информационные части N искаженных кодовых слов и передаются на выход блоков коррекции информационных частей кодовых слов 8. Процесс декодирования N возможно искаженных кодовых слов завершен.

Достигаемым техническим результатом предложенного устройства параллельного декодирования для циклических кодов на ПЛИС является уменьшение аппаратной сложности на его реализацию за счет уменьшения с N до L количества блоков вычисления позиций ошибок 5 и блоков вычисления значения ошибок 6, а также сокращение времени декодирования N кодовых слов, так как в блоке формирования уравнения локаторов ошибок 3 расчет проводится только для искаженных кодовых слов.

Список литературы

1. Forward Error Correction for Submarine Systems, Telecommunication Standardizations Section, International Telecommunication Union, G. 975.1, 2004.

2. Yanni Chen, Keshab K. Parhi «Area efficient parallel decoder architecture for long BCH codes», Department of Electrical and Computer Engineering University of Minnesota, Minneapolis, MN 55455 USA, 2006.

3. Sangho Yoon, Hanho Lee, Kihoon Lee «High-Speed two-parallel concatenated BCH-Based Super-FEC Architecture for optical communications», IEICE Trans. Fundamentals, vol. e93-A, No. 4, April 2010.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| ИТЕРАТИВНЫЙ ДЕКОДЕР КАСКАДНОГО КОДА НА ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМАХ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2017 |

|

RU2668401C1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Устройство для декодирования составного корректирующего кода | 1983 |

|

SU1229969A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО КАСКАДНОГО КОДА (ВАРИАНТЫ) | 2006 |

|

RU2340091C2 |

| СПОСОБ ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХ КОДОВ С "ЖЕСТКИМ" РЕШЕНИЕМ ПО ВЕКТОРУ-УКАЗАТЕЛЮ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2014 |

|

RU2575394C1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

Изобретение относится к области связи и может быть использовано для реализации декодеров циклических кодов (кодов Боуза-Чоудхури-Хоквингема, кодов Рида-Соломона) на программируемых логических интегральных схемах. Техническим результатом является уменьшение аппаратной сложности и снижение времени декодирования. Устройство содержит блоки вычисления синдромов, мультиплексор синдромов, блок формирования уравнений локаторов ошибок, распределитель локаторов ошибок, блоки вычисления позиций ошибок, блоки вычисления значений ошибок, распределитель векторов коррекции, блоки коррекции информационных частей кодовых слов, ОЗУ. 1 ил.

Устройство параллельного декодирования циклических кодов на программируемых логических интегральных схемах, содержащее N блоков вычисления синдромов, мультиплексор синдромов, блок формирования уравнений локаторов ошибок, распределитель локаторов ошибок, L блоков вычисления позиций ошибок, N блоков коррекции информационных частей кодовых слов, оперативное запоминающее устройство и при этом количество блоков вычисления синдромов равно количеству блоков вычисления позиций ошибок, отличающееся тем, что дополнительно введены L блоков вычисления значений ошибок для вычисления значений ошибок на искаженных позициях кодовых слов и распределитель векторов коррекции для распределения векторов коррекции искаженных кодовых слов на соответствующие блоки коррекции искаженных кодовых слов в соответствии с номерами искаженных кодовых слов, при этом L всегда меньше N и равно количеству искаженных слов исходя из параметров кода и вероятности ошибки в канале связи, в котором определяется максимальное количество искаженных кодовых слов, при этом N блоков вычисления синдромов имеет N входов для параллельного ввода N кодовых слов циклического кода, оперативное запоминающее устройство имеет вход для ввода N кодовых слов циклического кода, а выходы N блоков вычисления синдромов соединены с N входами мультиплексора синдромов, а первый выход мультиплексора синдромов соединен с входом блока формирования уравнений локаторов ошибок искаженных кодовых слов, а второй выход мультиплексора синдромов соединен с первым входом распределителя векторов коррекции, а выход блока формирования уравнений локаторов ошибок соединен с входом распределителя локаторов ошибок, a L выходов распределителя локаторов ошибок соединены с входами L блоков вычисления позиций ошибок искаженных кодовых слов, а выходы L блоков вычисления позиций ошибок соединены с входами L блоков вычисления значений ошибок, a L выходов блоков вычисления значений ошибок соединены с L входами распределителя векторов коррекции, a L выходов распределителя векторов коррекции соединены с первыми входами L блоков коррекции информационных частей кодовых слов, а выход оперативного запоминающего устройства соединен со вторыми входами N блоков коррекции информационных частей кодовых слов, а N блоков коррекции информационных частей кодовых слов имеют N выходов для передачи информационных частей N кодовых слов для дальнейшей обработки, где N - количество кодовых слов, поступивших на вход устройства декодирования; L - количество искаженных кодовых слов, поступивших на вход устройства декодирования.

| YOON SANGHO ET AL, HIGH-SPEED TWO-PARALLEL CONCATENATED BCH-BASED SUPER-FEC ARCHITECTURE FOR OPTICAL COMMUNICATIONS, IEICE TRANS | |||

| FUNDAMENTALS, VOL.E93-A, NO.4 APRIL 2010, p | |||

| Телефонная трансляция | 1922 |

|

SU771A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ СИНДРОМНОГО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА (ВАРИАНТЫ) | 2006 |

|

RU2340088C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| US 5440570 A, 08.08.1995 | |||

| US 6694476 B1, 17.02.2004 | |||

| US 2007204207 A1, 30.08.2007. | |||

Авторы

Даты

2017-03-09—Публикация

2015-11-23—Подача