ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Изобретение относится к способу управления обменами транзакциями между двумя интегральными схемами. Изобретение также касается системы, адаптированной выполнять этот способ.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Однокристальная система или система на чипе (также называемая, согласно сокращению, SoC или SOC) относится к интеграции всех компонентов компьютера или другой электронной системы в одну интегральную схему (чип). Интегральная схема или монолитная интегральная схема (также упоминаемая как IC, чип и микрочип) является электронной схемой, изготовленной с помощью диффузии по образцу элементов трасс на поверхность тонкой подложки из полупроводникового материала. Она может содержать цифровые, аналоговые, смешанного сигнала и часто радиочастотные функции, все на одной подложке чипа. Типичным применением является область встроенных систем.

В современной системе на чипе разные компоненты взаимно соединены с помощью межсоединения на чипе. Межсоединение по существу может быть истолковано как шина для схем. Примерами такого межсоединения являются открытый базовый протокол (также называемый, согласно его сокращению, ОСР) или усовершенствованный расширяемый интерфейс (также называемый, согласно его сокращению, AXI) усовершенствованных RISC-машин® (также называемых, согласно их сокращению, ARM). Компонентами могут быть центральные процессоры (также называемые, согласно их сокращению, CPU). Процессор ядра A9 ARM является примером CPU. Подсистемы или периферийные устройства с прямым доступом к памяти (также называемым, согласно его сокращению, DMA), такие как универсальные асинхронные приемники передатчики (также называемые, согласно их сокращению, UART), могут также рассматриваться как компоненты.

Каждому компоненту обычно назначается память. Кроме того, компоненты обмениваются друг с другом транзакциями.

Такие транзакции содержат запрос, посылаемый в другой компонент, причем этот запрос выполняется. В качестве иллюстраций, запрос может быть инструкцией считывать из памяти, записывать в память или выбирать из памяти. Компонент, который посылает запрос, является компонентом-инициатором транзакций или компонентом-инициатором, в то время как компонент, который выполняет запрос, является компонентом-целью транзакций или компонентом-целью. Некоторые компоненты могут быть как инициатором транзакций, так и целью транзакций, в то время как другие могут быть только инициатором транзакции или целью транзакции.

Каждая транзакция, которая инициируется, будет иметь ответ, который содержит либо запрошенную информацию, либо статус первоначального запроса. В качестве примеров, запрашиваемая информация может быть считываемыми данными, в то время как статус может быть указаниями успешной или неудачной записи. Ответ посылается компонентом-целью в компонент, который инициировал транзакцию.

Дополнительно к транзакциям, которые посылаются в шине на чипе, компоненты также обмениваются информацией о статусе, такой как прерывания. Прерывания обычно являются сигналами боковой полосы частот, следовательно, межсоединения на чипе также содержат сигналы боковой полосы частот.

Иногда все функциональные возможности, необходимые в SoC, не могут быть эффективно осуществлены в одном кристалле. В таких случаях SoC разделяется на множество, обычно два. Например, некоторые компоненты содержат аналоговые модули, которые сконструированы в другом узле технологического процесса, в то время как другие компоненты являются чисто цифровыми и могут быть сконструированы в меньшем узле процесса.

Интерфейс с малым временем задержки (также называемый, согласно его сокращению, LLI) может использоваться, чтобы давать возможность такого гибкого разделения SoC или системы на множество физических кристаллов, в то время как программное обеспечение, осуществленное в системе, рассматривает их как один логический кристалл. LLI стандартизован в интерфейсе процессора промышленности мобильных устройств (также называемом, согласно его сокращению, MIPI). LLI является интерфейсом точка-точка, который позволяет двум кристаллам осуществлять связь, как если бы другой кристалл был расположен на рассматриваемом кристалле. LLI является двунаправленным интерфейсом, составленным из двойных симплексных подлиний связи. LLI позволяет обоим кристаллам одновременно инициировать и принимать транзакции. Иначе говоря, LLI можно представить себе как “расширение шины” или ”туннель межсоединения”. Посредством специальных транзакций, называемых “служебные транзакции”, LLI может переносить сигналы боковой полосы частот, такие как прерывания.

Для того чтобы эффективно управлять источником питания физической линии связи LLI, можно выключать питание линии связи или приводить линию связи в состояния очень малого энергопотребления. Физическая линия связи требует времени, чтобы активироваться при запуске из состояния малого энергопотребления. Такое время обычно заключается в пределах миллисекунд. Так как протоколы “туннеля межсоединения”, такие как LLI, должны быть способными гарантировать малое время задержки во время транспортировки транзакций, желательно, чтобы все незавершенные транзакции были завершены до того, как линия связи будет приведена в такие состояния малого энергопотребления, или в чрезвычайном случае будет выключено ее питание.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Задачей настоящего изобретения является ослабить, по меньшей мере, частично вышеупомянутые недостатки.

Более конкретно, изобретение имеет целью выключать питание линии связи между двумя IC или приводить линию связи в состояния очень малого питания безопасным способом.

Эту задачу выполняют с помощью способа управления обменами транзакциями между двумя интегральными схемами в системе, содержащей две интегральные схемы и источник питания, предназначенный для питания линии связи между двумя интегральными схемами, таким образом, давая возможность обменов транзакциями между обеими интегральными схемами. Система также содержит контроллер, управляющий интегральными схемами и источником питания. Это, в целом, может быть упомянуто как система управления линией связи. В терминологии LLI один чип называется “ведущее устройство системы”, так как он будет управлять IP LLI (в обоих чипах), а также управлять линией связи. Ведущее устройство системы является эквивалентным контроллеру 40. На фиг.1 наименование 40 “контроллер” указывает на обе IC для общности. Хотя, обычно только ведущее устройство имеет контроллер. В этом случае подчиненный “контроллер” управляет, например, тактовым генератором, питанием и возвратом в исходное состояние в подчиненном устройстве. Главный контроллер 40 также мог бы управлять подчиненным устройством с помощью выдачи команд в подчиненное PMU. Если они выполнены, подчиненное PMU сообщает обратно в главное PMU.

Способ содержит этап а) приема команды в контроллере, чтобы уменьшить количество энергии, подаваемой источником питания в линию связи, и этап с) уменьшения энергии, подаваемой в линию связи, после того, как любые незавершенные транзакции выполнены. Между ними может быть этап b) посылки инструкции из контроллера в обе интегральные схемы, чтобы не дать интегральным схемам инициировать новые транзакции.

Варианты осуществления могут содержать один или более из следующих признаков:

- команда является командой выключить питание линии связи,

- линия связи соответствует протоколу последовательного интерфейса схема-схема (следовательно, также применима к параллельным интерфейсам, так как они содержат последовательные соединения),

- линия связи является интерфейсом с малым временем задержки MIPI,

- по меньшей мере, одна из интегральных схем имеет межсоединение, питаемое источником питания межсоединения, которое используется только при обменах транзакциями между двумя интегральными схемами, а этап с) дополнительно содержит уменьшение энергии, подаваемой источником питания межсоединения, после того, как любые незавершенные транзакции выполнены,

- одна интегральная схема является главной интегральной схемой, а другая интегральная схема является подчиненной интегральной схемой,

- система содержит, по меньшей мере, один монитор (средство мониторинга), который может предоставлять сигнал, соответствующий числу незавершенных транзакций, причем способ дополнительно содержит этап между этапом b) и этапом с), на котором посылают сигнал из монитора в контроллер, когда число незавершенных транзакций достигает нуля.

Также предложена система, содержащая две интегральные схемы, источник питания, предназначенный для питания линии связи между двумя интегральными схемами, таким образом давая возможность обменов транзакциями между обеими интегральными схемами. Также предложен контроллер, предназначенный для управления интегральными схемами и источником питания. Контроллер приспособлен посылать инструкцию в обе интегральные схемы, чтобы не дать интегральным схемам инициировать новые транзакции, при приеме команды уменьшить количество энергии питания, подаваемой источником питания в линию связи, и уменьшить энергию, подаваемую в линию связи, если незавершенные транзакции выполнены.

Предпочтительные варианты осуществления содержат следующие признаки:

- контроллер приспособлен посылать инструкцию в обе интегральные схемы, чтобы не дать интегральным схемам инициировать новые транзакции при приеме команды выключить питание линии связи и выключить источник питания линии связи, после того, как любые незавершенные транзакции выполнены,

- контроллер приспособлен посылать инструкцию в обе интегральные схемы, чтобы не дать интегральным схемам инициировать новые транзакции при приеме команды выключить питание при приеме команды выключить питание линии связи

- контроллер приспособлен действовать как контроллер в меньшей мере одном из способов, как описано выше.

Дополнительные признаки и преимущества изобретения будут следовать из нижеследующего описания вариантов осуществления изобретения, приведенных в качестве неограничивающих примеров, со ссылкой на сопровождающие чертежи, перечисленные ниже в настоящей заявке.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

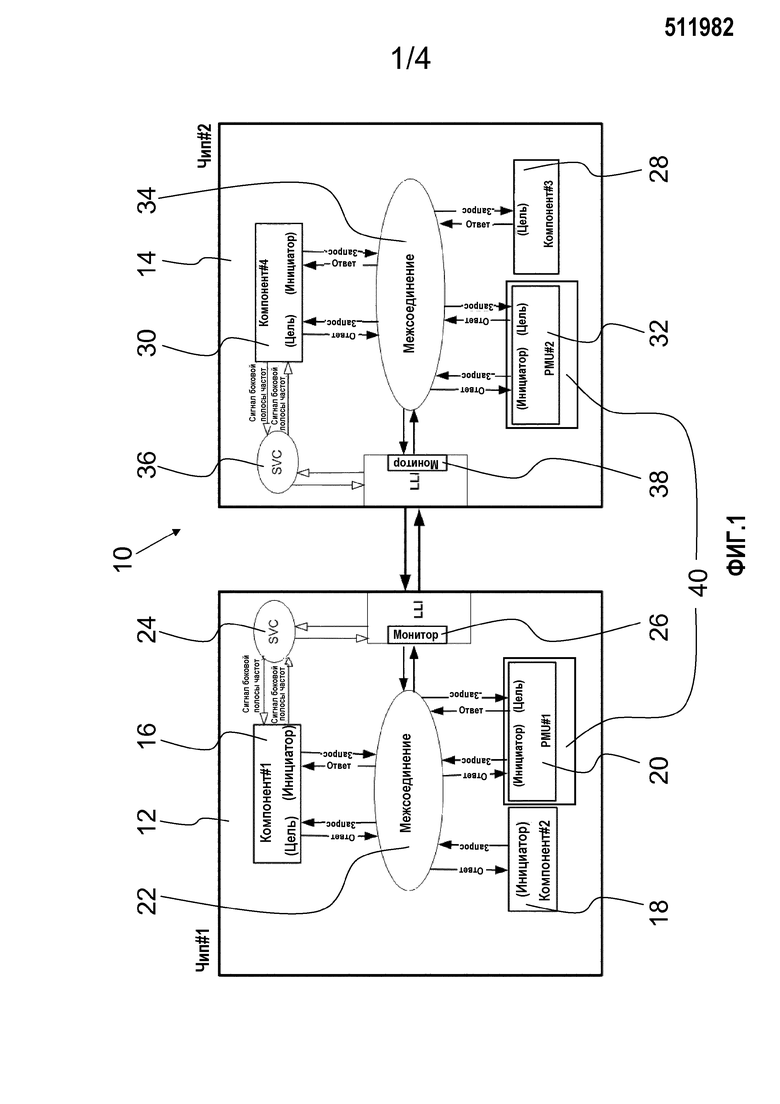

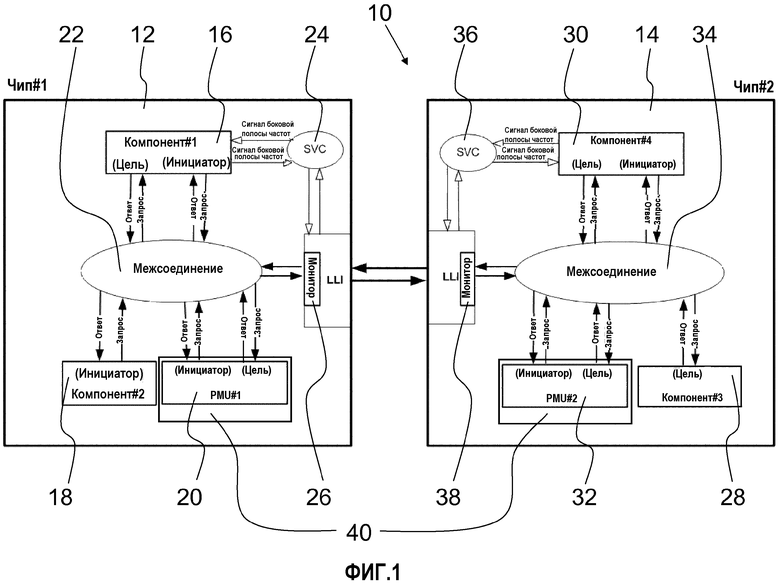

Фиг.1 изображает блок-схему примера системы, разделенной на две отдельные IC.

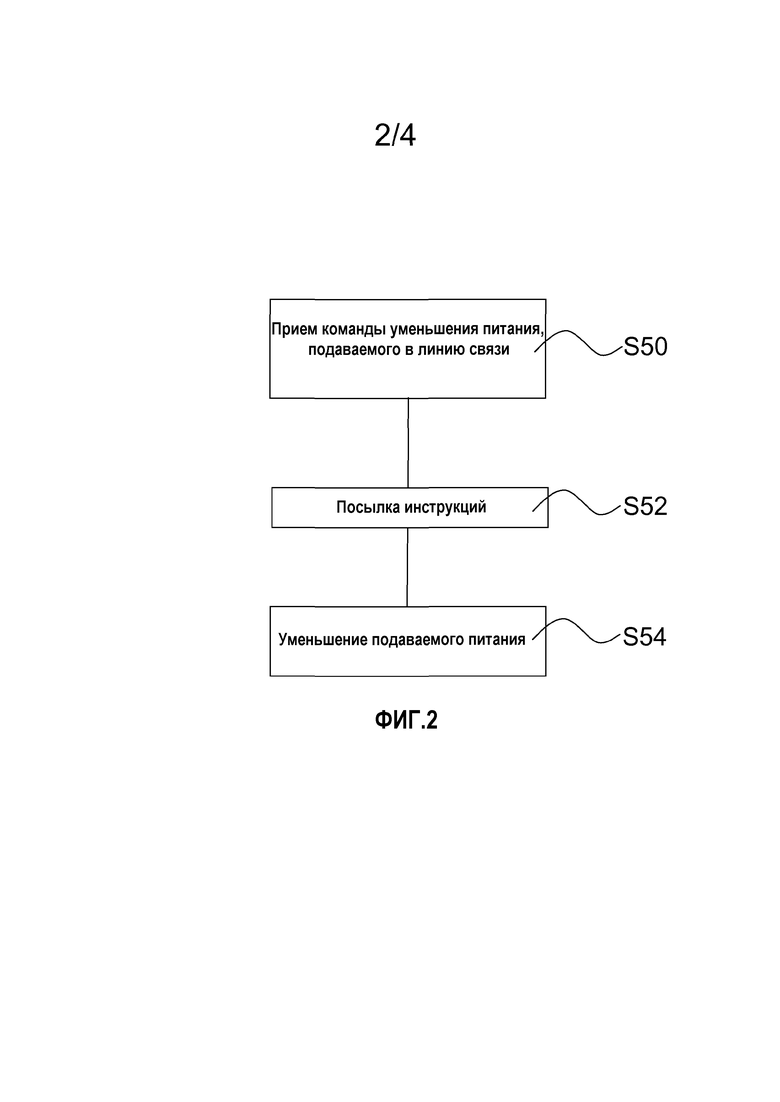

Фиг.2 изображает логическую блок-схему последовательности этапов способа управления обменами транзакциями между двумя IC в системе.

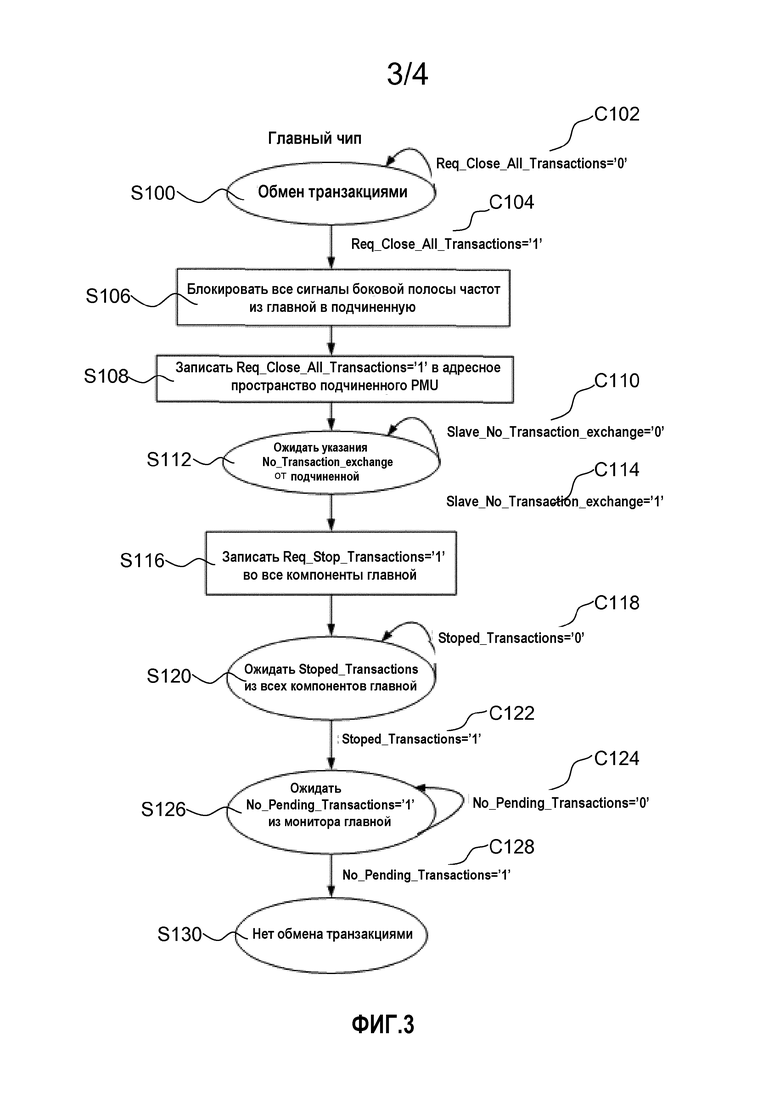

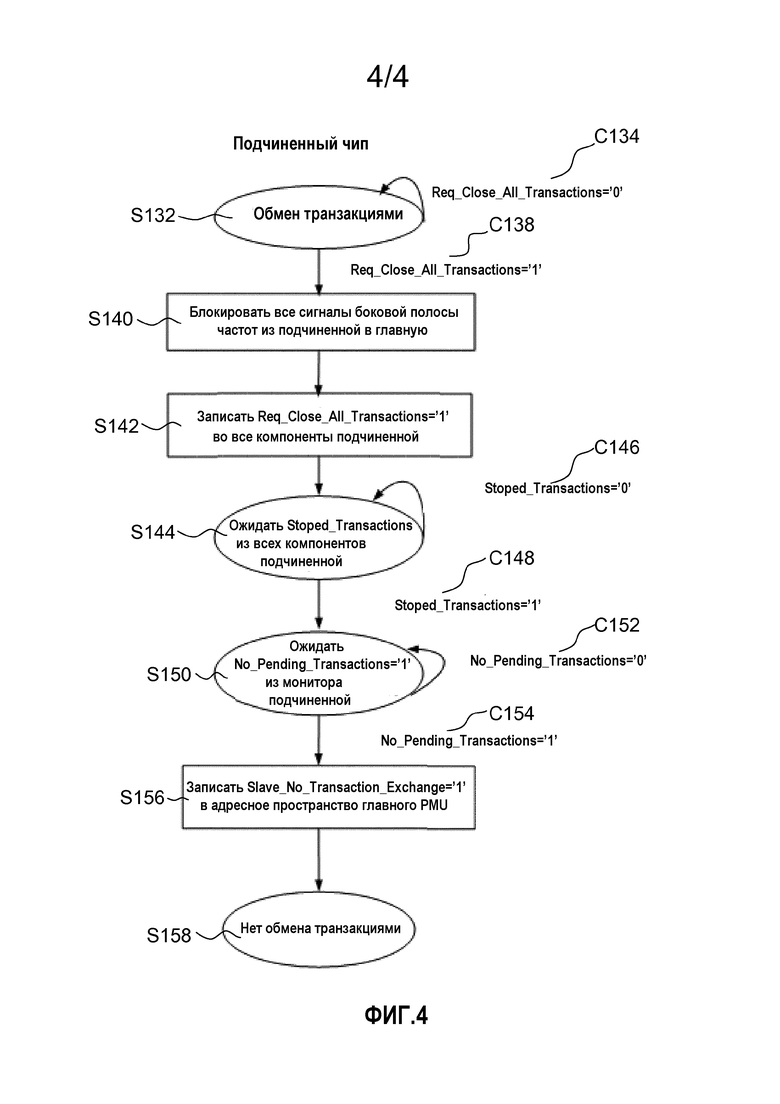

Фиг.3 и фиг.4 - логические блок-схемы последовательности этапов примера способа, используемого для того, чтобы надежно знать, что нет незавершенных транзакций, инициированных либо из IC, либо из другого элемента.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Настоящее изобретение связано с системой передачи данных между двумя IC и, более конкретно, со способом и схемой, чтобы иметь дело с надежным завершением обмена данными в такой системе. Хотя изобретение, более конкретно, описано для интерфейсов передачи данных с малым временем задержки, таких как LLI MIPI, следует понимать, что такое изобретение может быть использовано в других применениях.

В частности, предложен способ управления обменами транзакциями между двумя IC в системе. Фиг.1 является блок-схемой примера такой системы, разделенной на две отдельные IC. Система 10 содержит первую IC 12, которая является чипом#1, и вторую IC 14, которая является чипом#2. Каждая IC 12 и 14 содержит разные компоненты. Примерами компонентов являются CPU или любое аппаратное обеспечение (“физическое осуществление” или “интеллектуальная собственность”, также называемое с использованием его сокращения IP), такое как DMA. В примере по фиг.1 первая IC 12 содержит первый компонент 16 (компонент #1 на фиг.1), второй компонент 18 (компонент #2 на фиг.1), устройство 20 управления питанием (также называемое, согласно его сокращению, PMU), обозначенное PMU #1 на фиг.1, межсоединение 22, логический блок, который преобразует сигналы боковой полосы частот в служебные транзакции (также называемые, согласно их сокращению, SVC) 24, и монитор 26. Вторая IC 14 содержит третий компонент 28 (компонент #3 на фиг.1), четвертый компонент 30 (компонент #4 на фиг.1), устройство 32 управления питанием (обозначенное PMU #2 на фиг.1), межсоединение 34, SVC 35 и монитор 38. PMU 20 и 32 являются компонентами, которые обычно являются частью их соответственных межсоединений 22 и 34. Однако с целью иллюстрации они явно изображены на фиг.1. Разные компоненты будут дополнительно детализированы в дальнейшем.

Каждый компонент (четыре компонента 16, 18, 28 и 30 и PMU 20 и 32) может быть инициатором и/или целью транзакций. Ради иллюстрации в случае по фиг.1 два компонента 16 и 30 и PMU 20 и 32 являются, как инициаторами, так и целями транзакций, в то время как два компонента 18 и 28 являются только инициаторами транзакций.

Как объяснено ранее, транзакция может, например, содержать запрос считывания или записи данных, инициированный инициатором, в целевой компонент. Целевой компонент выполняет запрос и возвращает ответ считывания (данные считывания или ошибку) или ответ записи (успешный или ошибку). Как описано ранее и обсуждено опять ниже, транзакция также содержит ответ.

В соответствии с примером по фиг.1, стрелки с меткой “REQ” изображают маршрут запроса, а стрелки с обозначением “RES” изображают маршрут ответа. Транзакция инициируется инициатором через маршрут “REQ” в межсоединение 22 или 34, в соответствии с рассматриваемой IC 12 или 14. Межсоединение доставляет транзакцию в правильную цель. Эта доставка выполняется благодаря входному сигналу маршрута “REQ” и использованию того факта, что каждому компоненту IC 12 или 14 назначается память в каждом межсоединении 22 и 34. Цель выполняет считывание или записи, и результирующие ответ посылается из межсоединения через маршрут “RES”. Межсоединение 22 или 34 затем переносит этот ответ обратно инициатору, который инициировал транзакцию. В качестве основной иллюстрации, если второй компонент 18 инициирует запрос в первый компонент 16, запрос будет проходить через межсоединение 22. Кроме того, когда первый компонент 16 будет посылать свой ответ во второй компонент 18, ответ будет также проходить через межсоединение 22.

Система 10 также заключает в себе источник питания, предназначенный для питания линии связи между двумя IC 12 и 14, причем подача питания в линию связи дает возможность обменов транзакциями между двумя IC 12 и 14. (Этот источник питания или отдельный источник питания, конечно, требуется, для того, чтобы питать компоненты в IC). Более конкретно, это означает, что после подачи питания в линию связи транзакции могут выполняться между компонентом первой IC 12 и другим компонентом второй IC 14. Например, второй компонент 18 может посылать запрос в четвертый компонент 30, причем этот четвертый компонент 30 отвечает второму компоненту 18.

В соответствии с примером по фиг.1, две IC взаимно соединены с помощью протокола последовательного интерфейса чип-чип, такого как LLI MIPI. Однако следует заметить, что способ может применяться к любой системе, в которой используется концепция “расширения шины”, чтобы взаимно соединять две части системы. Иначе говоря, способ может быть осуществлен в системе, в которой имеются два взаимно соединенных кристалла. Кристаллы могут быть взаимно соединены с помощью любого способа, такого как LLI MIPI. Поскольку параллельный интерфейс состоит, по меньшей мере, частично, из последовательных интерфейсов, изобретение, конечно, применяется в равной степени также к параллельным интерфейсам.

В системе 10 межсоединение 22 и 34 в каждой IC 12 и 14 соединено с межсоединением 34 и 22 другой IC 14 и 12, соответственно, с помощью протокола “расширения шины” или ”туннеля межсоединения”, такого как LLI MIPI. Обмен данными между компонентами происходит в их соответственном протоколе межсоединения, таком как протоколы OCP, AMBA®, сеть на чипе (также называемом, согласно его сокращению, NoC), с использованием транзакций, которым назначается память, без какого либо вмешательства программного обеспечения. Таким образом, LLI является двунаправленной линией связи, в которой поддержка программного обеспечения требуется только для запуска линии связи, для обработки ошибок, для выключения питания линии связи и т.п., и никакое вмешательство программного обеспечения не требуется обеими компонентами, чтобы обмениваться транзакциями. В соответствии с примером по фиг.1, для каждой IC 12 или 14 межсоединение 22 и 34 представляет межсоединения на чипе, такие как OCP, AMBA®, а также могла бы требоваться логика адаптации межсоединения, чтобы адаптировать транзакции протокола межсоединений на чипе в транзакции LLI и наоборот. Протокол LLI обеспечивает классы трафика с малым временем задержки (также называемый, согласно его сокращению, LL) и лучший из возможного (также называемый, согласно ее сокращению, BE). Межсоединение является ответственным за назначение каждой транзакции в класс трафика LL или BE. Следует заметить, что класс трафика ВЕ является необязательным, но, если он поддерживается набором LLI, тогда класс трафика LL также должен поддерживаться. LLI также обеспечивает специальное множество транзакций, называемых “служебные транзакции”, которые используются, чтобы туннелировать сигналы боковой полосы частот, такие как прерывания, запросы DMA из одной IC в другую. Логика, которая гарантирует преобразование из сигналов боковой полосы частот в служебные транзакции и наоборот, является элементом SVC 24 и 36 на фиг.1. Служебные транзакции могут также использоваться, чтобы записывать и/или считывать из регистров в адресном пространстве LLI.

В системах, которые разделены на две отдельные IC, и, в честности, на отдельные секции, как система 10 на фиг.1, одна IC может вести себя как главная IC, в то время как другая IC является подчиненной IC. Например, первая IC 12 может быть главной IC, а вторая IC 14 подчиненной IC. Главная IC 12 является ответственной за управление подчиненной IC 14. Главная IC 12 также управляет назначением памяти всей системы, таким образом, чтобы компоненты в подчиненной IC 14 рассматривались, как если бы они были расположены в межсоединении 22 главной IC 12. Ролью главной IC 12 является также конфигурировать линию связи LLI. IP LLI взаимодействует как с межсоединением 22 главной IC 12, так и с межсоединением 34 подчиненной IC 14. Такие взаимодействия дают возможность передачи и приема “запросов” и ”ответов” из каждого межсоединения 22 и 34.

Система 10 также содержит контроллер 40, управляющий IC 12 и 14 и источником питания. Источник питания не представлен на фиг.1. Контроллер 40 содержит оба PMU 20 и 32. Фактически, оба PMU 20 и 32 обычно исполняют программное обеспечение, которое отвечает за управление питанием линии связи LLI под контролем из главного программного обеспечения системы, исполняющегося в CPU главной IC. Управление питанием линии связи может выполняться другим способом.

Мониторы 26 и 38 IC 12 и 14 на фиг.1 играют роль постоянного отслеживания каждой транзакции, которая была послана, и того, был ли принят ее ответ. Монитор 26 (или 38 IC 14) может, таким образом, быть приспособлен предоставлять сигнал, соответствующий числу незавершенных транзакций. Этот сигнал будет посылаться в контроллер 40, например, когда число незавершенных транзакций достигает нуля. Как описано ранее, контроллер 40 затем вызывает уменьшение питания, подаваемого в соответственные PMU 20 и 32. Следует понимать, что понятие “достигать”, в частности, заключает в себе значение “быть равным чему-либо”.

Способ, которым мониторы 26 получают сигнал, соответствующий числу незавершенных транзакций, может быть различным. Например, монитор 26 IC 12 будет постоянно отслеживать транзакции, которые были инициированы в межсоединении 22, и то, получила ли каждая из них ответ обратно из межсоединения 34, расположенного в IC 14. Каждый монитор может быть реализован как простой суммирующий/вычитающий счетчик. В таком варианте осуществления, счетчик увеличивается, когда посылается запрос транзакции, и уменьшается, когда принимается ответ транзакции.

Другие реализации, отличные от реализации по фиг.1, являются возможными. Например, хотя мониторы 26 изображены как часть IP LLI, они могут быть также реализованы вне LLI. Аналогично, контроллер 40 может быть вне IC 12 и 14.

Как изображено на фиг.2, которая иллюстрирует логическую блок-схему последовательности этапов способа управления обменами транзакциями между двумя IC 12 и 14 в системе 10, способ содержит этап S50 приема в контроллере 40 команды уменьшить количество энергии, подаваемой источником питания в линию связи.

Способ дополнительно содержит этап S52 посылки инструкции из контроллера 40 в обе IC 12 и 14, чтобы не дать IC 12 и 14 инициировать новые транзакции. Следует понимать, что такая посылка может быть непрямой. Фактически, в случае, когда обе IC находятся в отношении главной и подчиненной, контроллер 40 может посылать инструкции непосредственно в главную IC 12 и непрямо в подчиненную IC 14 через главную IC 12.

Способ дополнительно заключает в себе этап S54 уменьшения энергии, подаваемой в линию связи. Это уменьшение выполняется контроллером 40, после того как незавершенные транзакции выполнены. Как описано в другом месте, это является необязательным этапом, но изображено в настоящей заявке как иллюстративный вариант осуществления. Таким образом, такой способ является более надежным для компонентов IC 12 и 14. Фактически, такой способ дает возможность приводить пользователей линии связи в безопасное или известное состояние, до того как будет закрыта линия связи обмена данными. Таким образом, повышается безопасность компонента. Иначе говоря, способ гарантирует надежное закрытие линии связи.

С помощью такого способа, данными можно обмениваться даже после того, как контроллером 40 принят запрос уменьшить питание. Этот способ легко реализовать, поскольку никакие дополнительные входные и/или выходные контакты не требуются в корпусе, чтобы выполнять способ. Это дает в результате экономию затрат.

Кроме того, такой способ применяется к множеству систем, таких как системы, в которых IC являются одноранговыми, системы, в которых IC находятся в зависимости главной и подчиненной.

Когда на этапе S50 команда является командой выключить питание линии связи, вышеупомянутые эффекты являются даже более ощутимыми. Фактически в таком случае на этапе S54 источник питания обычно выключается.

Такой способ может также использоваться, чтобы выключать питание локального межсоединения IC, если никой из компонентов в этой IC не имеет данных для обмена. В этом случае локальное месоединение используется только при обменах транзакциями между двумя интегральными схемами. В такое локальное межсоединение IC питание подается источником питания межсоединения. Этот источник питания межсоединения является отдельным от источника питания, предназначенного для питания линии связи. Таким образом, на этапе S54 питание, подаваемое в межсоединение источником питания месоединения, может быть также уменьшено. Источник питания межсоединения может быть даже выключен.

Такой способ дает возможность уменьшать потребление энергии, подаваемой в систему 10.

Способ управления обменами транзакциями между двумя IC 12 и 14 в системе 10, как описано ранее, теперь будет описан в специфических случаях по фиг.3 и фиг.4, на которых одна IC является главной IC 12, в то время как другая IC является подчиненной IC 14. Фиг.3 и фиг.4 являются схематическими блок-схемами последовательности этапов примера способа, используемого для того, чтобы надежно знать, что не имеются незавершенные транзакции, инициированные либо из IC, либо другие. Как видно из вышесказанного, информация о наличии незавершенных транзакций может использоваться, чтобы выключать питание линии связи или приводить линию связи LLI в состояние малого энергопотребления, или любой другой функцией, которая должна знать, что линия связи является свободной.

Более конкретно, фиг.3 является иллюстрацией соответственных этапов способа, касающегося главной IC 12, в то время как фиг.4 иллюстрирует соответственные этапы способа, предназначенного для подчиненной IC 14. Для целей ясности, предыдущие и последующие этапы не изображены. Этапы соответствуют состоянию машины. Допускается, что такие этапы осуществляются в программном обеспечении, исполняющемся в контроллере обеих IC 12 и 14. В частности, они могут быть осуществлены в устройстве управления питанием (также называемом, согласно его сокращению, PMU) контроллера. Однако следует понимать, что могут быть использованы другие варианты осуществления. Например, такие этапы могут выполняться в любом другом компоненте или даже могут быть осуществлены в аппаратном обеспечении.

На фиг.3 способ начинается с этапа обмена транзакциями, обозначенного S100. Фактически, этот этап S100 состояния транзакции заключает в себе несколько этапов, которые выполняются главной IC 12, причем этапы не детализированы, так чтобы сохранить фигуру читаемой. На этом этапе S100 обмена транзакциями устанавливается (или запускается) линия связи LLI, устанавливается карта памяти системы, и компоненты как главной IC 12, так и подчиненной IC 14 обмениваются транзакциями. Транзакции назначаются в классы трафика либо LL, либо ВЕ, либо в оба класса трафика LLI. Кроме того, сигналы боковой полосы частот могут преобразовываться в служебные транзакции и передаваться в подчиненную IC 14 и, наоборот, из главной IC, т.е. преобразование сигналов боковой полосы частот главной IC в транзакции SVC и передача транзакций в другую IC, в данном случае подчиненную IC.

Способ остается на этапе S100 обмена транзакциями до тех пор, пока выполняется условие С102. Условие С102 соответствует тому факту, что сигнал Req_Close_All_Transactions (запрос закрытия всех транзакций) равен ‘0’. Сигнал Req_Close_All_Transactions может быть сигналом аппаратного обеспечения или прерыванием, если главная IC 12 записывает в регистр в PMU. Способ работает независимо от того, как осуществляются сигналы инициирующего события, и, следовательно, далее в настоящей заявке подчеркиваются только условия инициирующего события (а не их точное осуществление), чтобы переходить из одного состояния в другое.

Когда условие С102 не выполняется, это означает, что выполняется условие С104. Фактически, условие С104 соответствует тому факту, что сигнал Req_Close_All_Transactions равен ‘1’. Переход из выполненного состояния С102 в выполненное состояние С104 гарантируется контроллером 40, который переключает сигнал Req_Close_All_Transactions в ‘1’. В остальной части описания глагол ‘переключать’ следует понимать как изменение значения сигнала в 1. Когда условие С104 выполняется, в соответствии со способом логической блок-схемы по фиг.3, главная IC 12 выполняет этап S102 блокировки всех сигналов боковой полосы частот из главной IC 12 в подчиненную IC 14.

Способ также содержит этап S106, на котором главная IC 12 записывает в адресное пространство PMU подчиненной IC, чтобы переключить сигнал Req_Close_All_Transactions в подчиненной IC 14. Это возможно, так как для PMU подчиненной IC назначается память и, следовательно, PMU главной IC может непосредственно записывать в адресное пространство подчиненной IC с использованием транзакции LL или ВЕ. Служебные транзакции (которые могли бы видеться как принадлежащие трафику третьего класса в LLI) могут использоваться для того, чтобы записывать в адресное пространство сигнализации IP LLI подчиненной IC. Это пространство может фактически выдавать прерывание (сигнал Req_Close_All_Transactions) в подчиненное PMU. Ответы на служебные транзакции выдаются посредством IP LLI, и это является надежным благодаря механизмам управления потоком и повторной передачи LLI.

Способ также заключает в себе этап S112, на котором главная IC 12 ожидает указания “No_Transaction_Exchange” («Нет обмена транзакциями») от подчиненной и остается на этом этапе до тех пор, пока это указание не принято. Это гарантируется условием С118, которое соответствует тому факту, что сигнал “No_Transaction_Exchange” равен ‘0’.

На фиг.4 способ начинается с аналогичных этапов S132 и S140 для подчиненной IC 14 по сравнению с этапом S100 и S106, как ранее описано для главной IC 12. Единственным различием является то, что этап S140 ассоциирован с блокировкой сигналов боковой полосы частот из подчиненной IC 14 в главную IC 12. Кроме того, условия С134 и С138 являются также аналогичными, соответственно, условиям С102 и С104. Переход из выполненного условия С134 в выполненное условие С138 осуществляется, когда главная IC 12 находится на этапе S108.

Способ согласно логической блок-схеме по фиг.4 дополнительно содержит этап S142 записи в адресные пространства компонентов, которые используют линию связи LLI в подчиненной IC 14, чтобы переключить сигнал Req_Stop_Transactions (запрос остановы транзакций) в каждом компоненте. Для компонентов, которые не содержат программное обеспечение, данный сигнал может быть сигналом аппаратного обеспечения. В случае фиг.1 компоненты, имеющие отношение к этапу S142, являются третьим компонентом 28, четвертым компонентом 30 и PMU 32.

Затем подчиненная IC 14 переходит на этап S144. Этап S144 является этапом ожидания. Подчиненная IC 14 ожидает прекращения транзакций во всех подчиненных компонентах. Каждый подчиненный компонент после приема указания прекратить все транзакции предпринимает необходимые этапы, чтобы проверить, нет ли новых транзакций, которые должны быть инициированы, чтобы привести компонент в безопасное состояние, и, когда он определяет, что это имеет место, он подтвердит это с помощью переключения сигнала Stopped_Transactions (транзакции прекращены) (либо с помощью записи в специализированный бит регистра в PMU, либо с использованием сигнала аппаратного обеспечения). Подчиненные компоненты, которые не имеют функциональной возможности проверять, требуются ли еще транзакции, могут немедленно переключить этот сигнал, так как можно допустить, что такие компоненты не приведены в нестабильное состояние при закрытии линии связи LLI.

Подчиненная IC 14 остается на этапе S144 до тех пор, пока выполняется условие С146. Такое условие С146 соответствует тому факту, что сигнал stopped_transactions равен ‘0’. После того, как подчиненной IC 14 принято переключение сигнала “Stopped_Transactions” из всех компонентов, которые могут инициировать транзакции, сигнал stopped_transactions становится равным ‘1’. Таким образом, условие С148 становится выполненным, поскольку условие С148 соответствует тому факту, сто сигнал stopped_transactions становится равным ‘1’.

Затем подчиненная IC 14 выполняет этап S150 ожидания того, что больше нет незавершенных транзакций, из монитора 38 в подчиненной IC 14. Подчиненная IC остается на этапе S150 до тех пор, пока выполняется условие С152. В соответствии с примером по фиг.3, условие С152 соответствует тому факту, что сигнал No_Pending_Transaction (нет выполняющихся транзакций) равен ‘0’. Когда монитор 38 реализован внутри IP LLI, он может устанавливать атрибут No_Pending_Transaction в пространстве атрибутов управления и статуса в пространстве атрибутов/регистров подчиненного LLI. IP подчиненного LLI может генерировать прерывание в подчиненное PMU, когда этот конкретный атрибут установлен монитором 38. Это прерывание выдается после того, как подчиненное PMU запрашивает самый последний статус монитора 38, в то время как он остается на этапе S150. Это является одним из возможных способов, чтобы получить сигнал No_Pending_Transaction. Однако могут быть рассмотрены другие осуществления.

Если условие С152 больше не выполняется или не видится другим способом, условие С154 становится выполненным. Фактически условие С154 соответствует тому факту, что сигнал No_Pending_Transaction равен ‘1’. Затем подчиненная IC 14 выполняет этап S156 способа, в соответствии с логической блок-схемой по фиг.3. Этап S156 содержит запись, что бит регистра slave_No_Transaction_Exchange (нет обмена транзакциями на подчиненном устройстве) в адресном пространстве главного PMU равен ‘1’.

Затем подчиненная IC 14 переходит на этап S158, который обозначен как отсутствие обмена транзакциями. Несмотря на то, что транзакция, выполненная на этапе S156, будет принимать ответ, подчиненная IC 14 может сразу перейти на этап S158, поскольку целью такого этапа является убедиться в том, что все компоненты находятся в установившемся состоянии. Аналогично случаю этапа S108, на котором записывается в подчиненное адресное пространство, PMU подчиненной IC может записывать в адресное пространство главной IC с использованием транзакций LL или ВЕ. Таким образом, может быть выдано прерывание (инициирующий сигнал “Slave_No_Transaction_Exchange”).

После того как главная IC 12 принимает переключение сигнала slave_No_Transaction_Exchange, инициированное на этапе S156 подчиненной IC 14, сигнал “slave_No_Transaction_Exchange” переходит из ‘0’ в ’1’. Таким образом, вместо условия С110 становится выполненным условие С114 (которое соответствует сигналу “slave_No_Transaction_Exchange”, равному ‘1’).

Затем главное PMU выполняет этап S116 записи, что сигнал ‘Req_Stop_Transactions’ равен ‘1’, в адресное пространство всех компонентов, которые используют линию связи LLI в главной IC 12.

Затем главная IC 12 переходит на этап S120 ожидания, что значение ‘stopped_transactions’ равно ‘1’ для всех компонентов, которые используют линию связи LLI в главной IC 12. Это подразумевает, что главная IC 12 остается на этапе S120 до тех пор, пока выполняется условие С118 (значение ‘stopped_transactions’ равно ‘0’, по меньшей мере, для одного компонента). Другим способом выражения этого представления является то, что главная IC 12 остается на этапе S120 до тех пор, пока не выполнено условие С122 (значение ‘stopped_transactions’ равно ‘1’ для всех компонентов).

Каждый компонент IC 12 после приема указания прекратить все транзакции предпринимает необходимые этапы, чтобы проверить, должны ли быть инициированы новые транзакции, чтобы привести компонент в безопасное состояние. Когда компонент IC 12 определяет, что это имеет место, он подтверждает это с помощью переключения сигнала stopped_transactions. В этом специфическом контексте переключение может быть выполнено либо с помощью записи в специализированный бит регистра в PMU, либо с использованием сигнала аппаратного обеспечения. Компоненты IC 12, которые не имеют функциональной возможности проверять, требуются ли новые транзакции, может немедленно переключить сигнал ‘stopped_transactions’ в ‘1’. Фактически можно допустить, что такие компоненты не приводятся в нестабильное состояние при закрытии линии связи LLI.

После того как условие С122 выполнено, главная IC 12 переходит на этап S126 ожидания, что больше не имеются незавершенные транзакции, из монитора 26 в главной IC 12. Главная IC 12 остается на этапе S126 до тех пор, пока выполняется условие С124. В соответствии с примером по фиг.2, условие С124 соответствует тому факту, что сигнал No_Pending_Transaction равен ‘0’. Когда монитор 26 реализован внутри IP LLI, он может устанавливать атрибут No_Pending_Transaction в пространстве атрибутов управления и статуса в пространстве атрибутов/регистров главного LLI. IP главного LLI может генерировать прерывание в главное PMU, когда этот конкретный атрибут установлен монитором 26. Это прерывание выдается после того, как главное PMU запрашивает самый последний статус монитора 26, в то время как он остается на этапе S126. Это является одним из возможных способов, чтобы получить сигнал No_Pending_Transaction. Однако могут быть рассмотрены другие осуществления.

Если условие С152 больше не выполняется или не видится другим способом, условие С128 становится выполненным. Фактически условие С128 соответствует тому факту, что сигнал No_Pending_Transaction равен ‘1’. Затем главная IC 12 выполняет этап S130, который обозначен как отсутствие обмена транзакциями. На этом этапе главное PMU или его логический эквивалент уверен, что все компоненты в главной IC 12 и в подчиненной IC 14 находятся в безопасном и/или устойчивом состоянии.

Следовательно, на этом этапе питание линии связи LLI может быть выключено или приведено в состояние малого энергопотребления, какой-либо нестабильности в системе 10.

Следует заметить, что способ согласно логическим блок-схемам по фиг.3 и фиг.4 является только иллюстративным способом. В частности, специалист в данной области техники может адаптировать некоторые этапы или переупорядочить некоторые из этапов в способе, чтобы выполнить ту же самую задачу. Например, этап S106 блокировки сигналов боковой полосы частот из главной IC 12 в подчиненную IC 14 может быть выполнен после этапа S112, на котором главная IC получает событие, инициирующее изменение значения сигнала slave_no_transaction_exchange. Другой возможностью является, что главная IC 12 может сначала запросить все свои компоненты выполнить (= завершить) свои транзакции до запрашивания подчиненной IC 14 сделать то же самое на ее стороне. Кроме того, знание того, что компоненты подчиненной IC 14 не имеют транзакций для обмена, может служить в качестве предварительного указателя выключить питание межсоединения в IC.

В каждом варианте осуществления способ может быть выполнен в системе 10, содержащей две интегральные схемы 12 и 14, источник питания, предназначенный для питания линии связи между двумя интегральными схемами 12 и 14, таким образом давая возможность обменов транзакциями между обеими интегральными схемами 12 и 14, и контроллер 40, предназначенный для управления интегральными схемами и источником питания. Контроллер 40 адаптирован посылать инструкцию в обе интегральные схемы 12 и 14, чтобы не дать IC 12 и 14 инициировать новые транзакции, при приеме команды уменьшить количество энергии, подаваемой источником питания в линию связи, и уменьшить энергию, подаваемую источником питания в линию связи, после того как выполнены любые незавершенные транзакции. Как упомянуто, контроллер 40 мог бы присутствовать только в главной IC (из которой он может потом управлять PMU в подчиненной, фактически являясь виртуальным контроллером 40 в подчиненной IC, см. фиг.1).

Такой контроллер мог бы дополнительно быть адаптированным посылать инструкцию в обе интегральные схемы 12 и 14, чтобы не дать IC 12 и 14 инициировать новые транзакции при приеме команды выключить питание линии связи и выключить источник питания линии связи, если выполнены любые незавершенные транзакции.

Кроме того, в каждом варианте осуществления способ может быть выполнен на основе компьютерной программы, содержащей инструкции, предназначенные для выполнения способа. Программа является исполняемой в программируемом устройстве. Прикладная программа может быть осуществлена на высокоуровневом процедурном или объектно-ориентированном языке программирования, или на языке ассемблера, или на машинном языке, если требуется. В любом случае, язык может быть компилируемым или интерпретируемым языком. Программа может быть программной полной установки или программой обновления. В последнем случае программа является программой обновления, которая обновляет программируемое устройство, ранее запрограммированное выполнять части способа, в состояние, в котором устройство является подходящим для выполнения всего способа.

Программа может быть записана на носителе данных. Носитель данных может быть любой памятью, приспособленной для записи компьютерных инструкций. Таким образом, носитель данных может быть любым видом энергонезависимой памяти, включая, в качестве примера, устройства полупроводниковой памяти, такие как EPROM, EEPROM и устройства флэш-памяти, магнитные диски, такие как жесткие диски и сменные диски, магнитно-оптические диски и диски CD-ROM.

Изобретение было описано со ссылкой на предпочтительные варианты осуществления. Однако многие изменения являются возможными в рамках объема изобретения.

Группа изобретений относится к управлению обменами транзакциями между двумя интегральными схемами. Технический результат – создание технологии для приведения линии связи в состояние очень малого питания безопасным способом. Для этого предложен способ управления обменами транзакциями между двумя интегральными схемами (12, 14) в системе (10), содержащей: две интегральные схемы (12, 14), источник питания, предназначенный для питания линии связи между двумя интегральными схемами, таким образом давая возможность обменов транзакциями между обеими интегральными схемами (12, 14), контроллер (40), управляющий интегральными схемами (12, 14) и источником питания, причем способ содержит этапы: а) приема в контроллере (40) команды уменьшить количество энергии, подаваемой источником питания в линию связи, b) посылки инструкции из контроллера (40) в обе интегральные схемы (12, 14), чтобы не дать интегральным схемам (12, 14) инициировать новые транзакции, с) уменьшения энергии, подаваемой в линию связи, после того как любые незавершенные транзакции выполнены. 3 н. и 16 з.п. ф-лы, 4 ил.

1. Способ управления обменами транзакциями между двумя интегральными схемами (12, 14) в системе (10), содержащей:

две интегральные схемы (12, 14),

источник питания, предназначенный для питания линии связи между двумя интегральными схемами, таким образом обеспечивая возможность обменов транзакциями между обеими интегральными схемами (12, 14), и

контроллер (40), управляющий интегральными схемами (12, 14) и источником питания,

причем способ содержит этапы, на которых:

принимают команду в контроллере (40), причем команда запрашивает, чтобы линия связи была закрыта;

посылают инструкцию из контроллера в каждую из двух интегральных схем, причем инструкция предписывает каждой из двух интегральных схем прекратить инициирование запросов новых транзакций;

для каждой одной из двух интегральных схем, в ответ на обнаружение того, что одна из двух интегральных схем прекратила инициирование новых транзакций, обнаруживают, когда все незавершенные транзакции, инициированные одной из двух интегральных схем, выполнены; и

закрывают линию связи в ответ на обнаружение того, что все незавершенные транзакции обеих из двух интегральных схем выполнены.

2. Способ по п. 1, в котором упомянутая команда является командой выключить питание линии связи.

3. Способ по п. 1, в котором линия связи работает в соответствии с протоколом последовательного интерфейса схема-схема.

4. Способ по п. 1, в котором линия связи работает в соответствии с интерфейсом процессора промышленности мобильных устройств, MIPI, интерфейсом с малым временем задержки.

5. Способ по п. 1, в котором по меньшей мере одна из интегральных схем имеет межсоединение, в которое питание подается источником питания межсоединения, которое используется только при обменах транзакциями между двумя интегральными схемами, при этом этап, на котором закрывают линию связи, содержит этап, на котором уменьшают питание, подаваемое источником питания межсоединения, в ответ на обнаружение того, что все незавершенные транзакции обеих из двух интегральных схем выполнены.

6. Способ по п. 5, в котором при уменьшении питания, подаваемого источником питания межсоединения, выключают питание источника питания межсоединения.

7. Способ по п. 1, в котором одна из интегральных схем (12) является главной интегральной схемой, а другая одна из интегральных схем (14) является подчиненной интегральной схемой.

8. Способ по п. 1, в котором система (10) содержит по меньшей мере одно средство мониторинга (26), которое выполнено с возможностью предоставлять сигнал, соответствующий числу незавершенных транзакций, при этом этап, на котором обнаруживают, когда все незавершенные транзакции, инициированные одной из двух интегральных схем, выполнены, содержит этап, на котором посылают упомянутый сигнал из средства мониторинга (26) одной из двух интегральных схем в контроллер (40), когда число незавершенных транзакций достигает нуля.

9. Способ по п. 8, в котором средство мониторинга (26) содержит суммирующий/вычитающий счетчик, сконфигурированный с возможностью подсчета в одном из двух направлений в ответ на инициирование запроса транзакции и подсчета в другом из двух направлений в ответ на прием ответа на запрос транзакции.

10. Способ по п. 1, содержащий этапы, на которых:

по меньшей мере один компонент в по меньшей мере одной из двух интегральных схем (12, 14) выполняет:

прием из контроллера инструкции, которая предписывает каждой из двух интегральных схем прекратить инициирование запросов новых транзакций;

в ответ на принятую инструкцию, продолжение инициировать запросы новых транзакций только до тех пор, пока этот по меньшей мере один компонент не перешел в предварительно определенное безопасное состояние; и

в ответ на то, что упомянутый по меньшей мере один компонент перешел в предварительно определенное безопасное состояние, уведомление контроллера о том, что данный по меньшей мере один компонент прекратил инициирование новых транзакций.

11. Способ по п. 1, в котором упомянутая команда является командой уменьшить питание, подаваемое в линию связи.

12. Способ по п. 1, содержащий этап, на котором используют механизм прерывания, чтобы информировать контроллер о том, что все незавершенные транзакции, инициированные одной из двух интегральных схем, выполнены.

13. Система (10) для управления обменами транзакциями между двумя интегральными схемами, содержащая:

две интегральные схемы (12, 14);

источник питания, сконфигурированный подавать питание в линию связи между двумя интегральными схемами (12, 14), таким образом обеспечивая возможность обменов транзакциями между обеими из двух интегральных схем (12, 14),

контроллер (40), сконфигурированный для управления двумя интегральными схемами и источником питания;

причем контроллер (40) сконфигурирован отвечать на команду:

посылкой инструкции в каждую из двух интегральных схем (12, 14), причем инструкция предписывает каждой из двух интегральных схем прекратить инициирование запросов новых транзакций;

предписанием каждой одной из двух интегральных схем в ответ на обнаружение того, что эта одна из двух интегральных схем (12, 14) прекратила инициирование новых транзакций, обнаруживать, когда все незавершенные транзакции, инициированные этой одной из двух интегральных схем, выполнены; и

закрытием линии связи в ответ на обнаружение того, что все незавершенные транзакции обеих из двух интегральных схем выполнены,

причем упомянутая команда является командой, которая запрашивает, чтобы линия связи была закрыта.

14. Система по п. 13, в которой команда, которая запрашивает, чтобы линия связи была закрыта, является командой уменьшить питание линии связи, при этом контроллер (40) сконфигурирован выключать источник питания линии связи в ответ на обнаружение того, что все незавершенные транзакции обеих из двух интегральных схем (12, 14) выполнены.

15. Система по п. 13, содержащая:

по меньшей мере один компонент в по меньшей мере одной из двух интегральных схем, сконфигурированный для выполнения:

приема из контроллера инструкции, которая предписывает каждой из двух интегральных схем прекратить инициирование запросов новых транзакций;

в ответ на принятую команду, продолжения инициировать запросы новых транзакций только до тех пор, пока этот по меньшей мере один компонент не перешел в предварительно определенное безопасное состояние; и

в ответ на то, что упомянутый по меньшей мере один компонент перешел в предварительно определенное безопасное состояние, уведомления контроллера о том, что данный по меньшей мере один компонент прекратил инициирование новых транзакций.

16. Система по п. 13, в которой упомянутая команда является командой уменьшить питание, подаваемое в линию связи.

17. Система по п. 13, содержащая по меньшей мере одно средство мониторинга, сконфигурированное генерировать представление числа незавершенных транзакций и посылать сигнал в контроллер, когда число незавершенных транзакций достигает нуля,

причем средство мониторинга содержит суммирующий/вычитающий счетчик, сконфигурированный с возможностью подсчета в одном из двух направлений в ответ на инициирование запроса транзакции и подсчета в другом из двух направлений в ответ на прием ответа на запрос транзакции.

18. Система по п. 13, содержащая механизм прерывания, сконфигурированный для информирования контроллера о том, что все незавершенные транзакции, инициированные одной из двух интегральных схем, выполнены.

19. Долговременный машиночитаемый носитель информации, на котором сохранены инструкции, которые при их исполнении процессором предписывают процессору выполнять способ управления обменами транзакциями между двумя интегральными схемами в системе, содержащей:

две интегральные схемы,

источник питания, предназначенный для питания линии связи между двумя интегральными схемами, таким образом обеспечивая возможность обменов транзакциями между обеими интегральными схемами,

контроллер, управляющий интегральными схемами и источником питания,

причем способ содержит этапы, на которых:

принимают команду в контроллере, причем команда запрашивает, чтобы линия связи была закрыта;

посылают инструкцию из контроллера в каждую из двух интегральных схем, причем инструкция предписывает каждой из двух интегральных схем прекратить инициирование запросов новых транзакций;

для каждой одной из двух интегральных схем в ответ на обнаружение того, что одна из двух интегральных схем прекратила инициирование новых транзакций, обнаруживают, когда все незавершенные транзакции, инициированные одной из двух интегральных схем, выполнены; и

закрывают линию связи в ответ на обнаружение того, что все незавершенные транзакции обеих из двух интегральных схем выполнены.

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

2017-04-25—Публикация

2012-07-06—Подача