Техническое решение относится к измерительной технике, в частности к следящим АЦП многоразрядных приращений, и может быть использовано для непрерывного преобразования напряжения в цифровой код, например, для преобразователей сигналов сельсин-код, резольвер-код и магниточувствительных датчиков угла поворота и положения на основе магниторезистивных сенсоров и датчиков Холла.

Известно устройство информационного преобразования аналогового сигнала в цифровой код [1]. Устройство построено на лампах и содержит компаратор входного напряжения и напряжения ЦАП выходного кода реверсивного счетчика и тактовый генератор. В предлагаемом устройстве компаратор на тактовой частоте генератора вырабатывает сигналы инкрементирования или декрементирования реверсивного счетчика в зависимости от знака рассогласования напряжений на входе компаратора. Достоинством устройства является непрерывное отслеживание входного напряжения, недостатками - медленная реакция на быстро и существенно меняющийся входной сигнал, низкая помехозащищенность, а также дрожание младшего разряда кода даже при достижении режима слежения.

Известен следящий АЦП [2]. АЦП содержит операционный усилитель, на суммирующий вход которого подается входное напряжение, а на вычитающий - напряжение с ЦАП выходного кода реверсивного счетчика, разностное напряжение подается на интегратор, выход которого соединен с компаратором, который фиксирует знак и превышение напряжения на интеграторе заданного порога, а также формируют строб, по которому интегратор сбрасывается, а реверсивный счетчик инкрементируется или декрементируется в зависимости от знака рассогласования. Использование интегратора повышает помехозащищенность следящего АЦП, но не устраняет его недостаток - медленную реакцию на быстро и существенно меняющийся входной сигнал.

Известен асинхронный АЦП [3]. АЦП построен по схеме следящего АЦП и содержит вычитатель входного напряжения и напряжения ЦАП выходного кода реверсивного счетчика, компаратор разностного напряжения вычитателя и блок коррекции реверсивного счетчика. Когда срабатывает положительный или отрицательный порог компаратора, вырабатывается строб длительностью, достаточной для приращения или уменьшения реверсивного счетчика и установки напряжения на выходе ЦАП. АЦП предусматривает наличие нескольких компараторов соответственно с порогом срабатывания в два и более раз выше порога напряжения младшего разряда АЦП, тогда коррекция реверсивного счетчика осуществляется соответственно на два и более разрядов. Достоинством АЦП является непрерывное отслеживание входного напряжения, выполнение коррекции реверсивного счетчика только при превышении порога срабатывания компаратора (компараторов), более высокая скорость сходимости на быстро и существенно меняющийся входной сигнал, недостатком - низкая помехозащищенность, поскольку помеха уровнем выше порога срабатывания компаратора приводит к ложному изменению выходного кода.

Известен следящий АЦП с реверсивным счетчиком и дополнительным АЦП [4], выбранный в качестве прототипа. Следящий АЦП содержит последовательно соединенные реверсивный счетчик, ЦАП разрядов реверсивного счетчика, вычитатель входного напряжения и напряжения с ЦАП, дополнительный параллельный АЦП разностного напряжения с выхода вычитателя. Старшие разряды кода дополнительного АЦП определяют скорость приращения реверсивного счетчика, а младшие - дополняют разряды реверсивного счетчика, образуя в совокупности выходной код. Недостатками АЦП является низкая помехозащищенность, сложность реализации ЦАП высокой разрядности, сложность реализации параллельного АЦП, а также высокое потребление схемы.

Задачей технического решения является повышение разрядности и точности следящего АЦП, помехозащищенности, а также упрощение схемы АЦП.

Поставленная задача решается благодаря тому, что в следящем АЦП многоразрядных приращений, включающем в себя реверсивный счетчик, соединенный с ЦАП, вычитатель входного сигнала и выхода ЦАП, дополнительный АЦП разностного сигнала, старшие разряды выходного кода которого соединены со схемой приращения реверсивного счетчика, а младшие разряды образуют в совокупности с разрядами реверсивного счетчика выходной код следящего АЦП, предусмотрены следующие отличия, реверсивный счетчик разделен на несколько ступеней малой разрядности, каждая из которых содержит ЦАП, соединенный со ступенью реверсивного счетчика, выход которого соединен с делителем с коэффициентом деления, соответствующим разрядности предыдущих ступеней, выходы делителей соединены с вычитателем входного напряжения, выход которой соединен с дополнительным АЦП разностного сигнала, который имеет вид преобразователя напряжения в частоту и содержит интегратор, выход которого соединен с компаратором, выходы сигналов положительного или отрицательного порога срабатывания которого через элемент ИЛИ соединены со входом сброса интегратора, а также со счетчиком выходного сигнала тактового генератора эталонной частоты в полутактах частоты, регистром-защелкой счетчика и входом сброса младших разрядов выходного кода, выход регистра-защелки соединен с адресным входом ПЗУ, выход ПЗУ соединен с первым входом сумматора-вычитателя приращения реверсивного счетчика, второй вход которого соединен с младшими разрядами выходного кода и младшими разрядами реверсивного счетчика, управляющие входы сумматора-вычитателя соединены с выходами компаратора.

Между совокупностью существенных признаков заявленного технического решения и достигаемым техническим результатом существует причинно-следственная связь, а именно соединение ЦАП малой разрядности, к которым не предъявляются жесткие требования по точности соотношения параметров элементов, позволяет получить высокую разрядность выходного кода ЦАП, использование интегратора позволяет отфильтровать высокочастотные помехи входного сигнала, измерение длительности срабатывания компаратора на счетчике полутактов частоты генератора позволяет оценить величину напряжения рассогласования на входе интегратора и увеличивать или уменьшать значение реверсивного счетчика выходного кода в зависимости от знака рассогласования и его величины, что повышает сходимость и точность следящего АЦП, а также упрощает схему следящего АЦП и снижает ее потребление.

Техническое решение позволяет по сравнению с прототипом повысить помехозащищенность, разрядность и точность следящего АЦП, упростить его схему и снизить ее потребление.

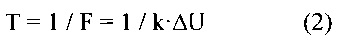

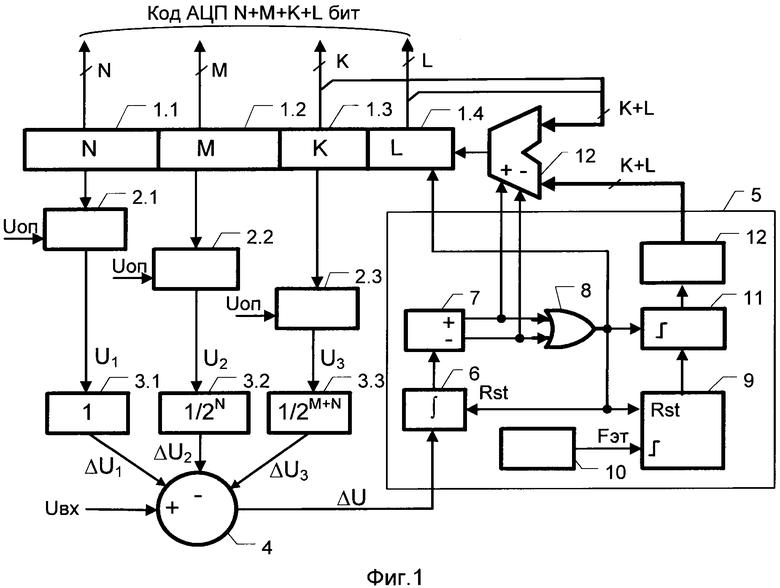

Техническая сущность предложенного технического решения поясняется чертежом, на котором фиг. 1 содержит структурную схему следящего АЦП многоразрядных приращений, фиг. 2 содержит пример схемы счета длительности временного интервала в полутактах, фиг. 3 содержит примеры временных диаграмм.

Структурная схема предложенного следящего АЦП многоразрядных приращений приведена на фиг. 1, где

1 - реверсивный счетчик;

2 - ЦАП;

3 - делитель;

4 - вычитатель;

5 - интегрирующий АЦП, который содержит

6 - интегратор;

7 - компаратор

8 - элемент ИЛИ;

9 - счетчик полутактов генератора эталонной частоты;

10 - генератор эталонной частоты;

11 - регистр-защелка;

12 - ПЗУ;

13 - сумматор-вычитатель.

Реверсивный счетчик 1 разбит на четыре ступени 1.1, 1.2, 1.3 и 1.4. Ступени, кроме последней 1.4, соединены с малоразрядными ЦАП 2.1, 2.2 и 2.3, на входы опорного напряжения которых подается одинаковое опорное напряжение. Выходы ЦАП 2.1, 2.2 и 2.3 соединены с делителями 3.1, 3.2 и 3.3, имеющими заданный весовой коэффициент. Напряжения с делителей подаются на вычитатель 4 входного напряжения. С выхода вычитателя 4 напряжение разностного сигнала подается на дополнительный АЦП разностного сигнала 5, который содержит интегратор 6, выход которого соединен с компаратором 7. При превышении отрицательного или положительного порога срабатывания компаратор 7 формирует сигналы знака рассогласования, которые объединяются на элементе ИЛИ 8. Выходной сигнал элемента 8 сбрасывает интегратор 7. Таким образом, на выходе элемента 8 формируется сигнал строба, период которого зависит от напряжения рассогласования. Длительность периода сигнала строба фиксируется счетчиком 9, который считает полутакты тактового генератора эталонной частоты 10 и сохраняется в регистре-защелке 11 по сигналу строба. При этом счетчик 9 сбрасывается. Значение регистра-защелки 11 подается на адресный вход ПЗУ 12, которое содержит таблицу кодов приращения реверсивного счетчика 1 в зависимости от длительности периода сигналов строба. В зависимости от знака напряжения рассогласования, поступающего от компаратора 6, выходной код приращения ПЗУ 9 складывается или вычитается из реверсивного счетчика 1 с помощью сумматора-вычитателя 13, перед этим младшая ступень 1.4 счетчика по переднему фронту строба сбрасывается. Шкала разрядов кода приращения и шкала разрядов ЦАП 2 перекрываются таким образом, что сумма весов старших разрядов кода приращения используется для коррекции разрядов реверсивного счетчика 1, подаваемых на ЦАП 2, а младшие разряды кодируют разностный сигнал, получаемый из-за того, что на ЦАП 2 подаются не все разряды выходного кода.

Разбиение реверсивного счетчика 1 на ступени и ступенчатое соединение ЦАП 2 позволяет использовать в следящем АЦП малоразрядные ЦАП, к которым не предъявляются жесткие требования по точности соотношения параметров элементов.

Для схемы следящего АЦП с 3-ступенчатыми счетчиком 1 и ЦАП 2 с разрядностями N, М и K, приведенной на фиг. 1, разностное напряжение вычитателя 4 определяется формулами

ΔU=Uвх-U1-U2/2N-U3/2N+M

U1=Uоп⋅(D1/2N)

U2=Uоп⋅(D2/2M)

U3=Uоп⋅(D3/2K),

где Uоп - опорное напряжение,

Uвх - входное напряжение,

D1, D2, D3 - коды на выходе счетчиков 1.1, 1.2 и 1.3 соответственно,

N, М, K - разрядности счетчиков 1.1, 1.2 и 1.3 соответственно.

Таким образом, цена младшего разряда преобразования составляет:

Ulow=Uоп/2(N+M+K)

Частота сигнала срабатывания компаратора 7 выходного сигнала интегратора 6 пропорциональна разностному напряжению на его входе:

Период сигнала строба на выходе схемы 8 обратно пропорционален частоте

Период сигнала строба измеряется в полутактах эталонной частоты на счетчике 9.

Код приращения реверсивного счетчика 1 вычисляется с помощью ПЗУ 12, которое содержит таблицу кодов приращения в зависимости от периода сигналов строба, измеренного в полутактах эталонной частоты в соответствии.

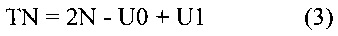

На фиг. 2 приведен пример структурной схемы счета длительности периода сигналов строба в полутактах. Схема содержит счетчик 9 счетных импульсов эталонной частоты, регистр-защелку 11, триггер 14 и триггер 15. Содержимое счетчика 9 по фронту строба переписывается в регистр-защелку 11, после этого счетчика 9 сбрасывается. Также по фронту строба содержимое триггера 14 переписывается в триггер 15, а в триггер 14 записывается логический уровень эталонной частоты.

Содержимое счетчика 9, сохраненное в регистре-защелке 11, и состояние триггеров 14, 15 позволяют оценить длительность периода поступления сигналов строба с точностью до полутакта эталонной частоты по формуле:

где N - содержимое регистра-защелки 9,

U0, U1 - состояние триггеров 14, 15.

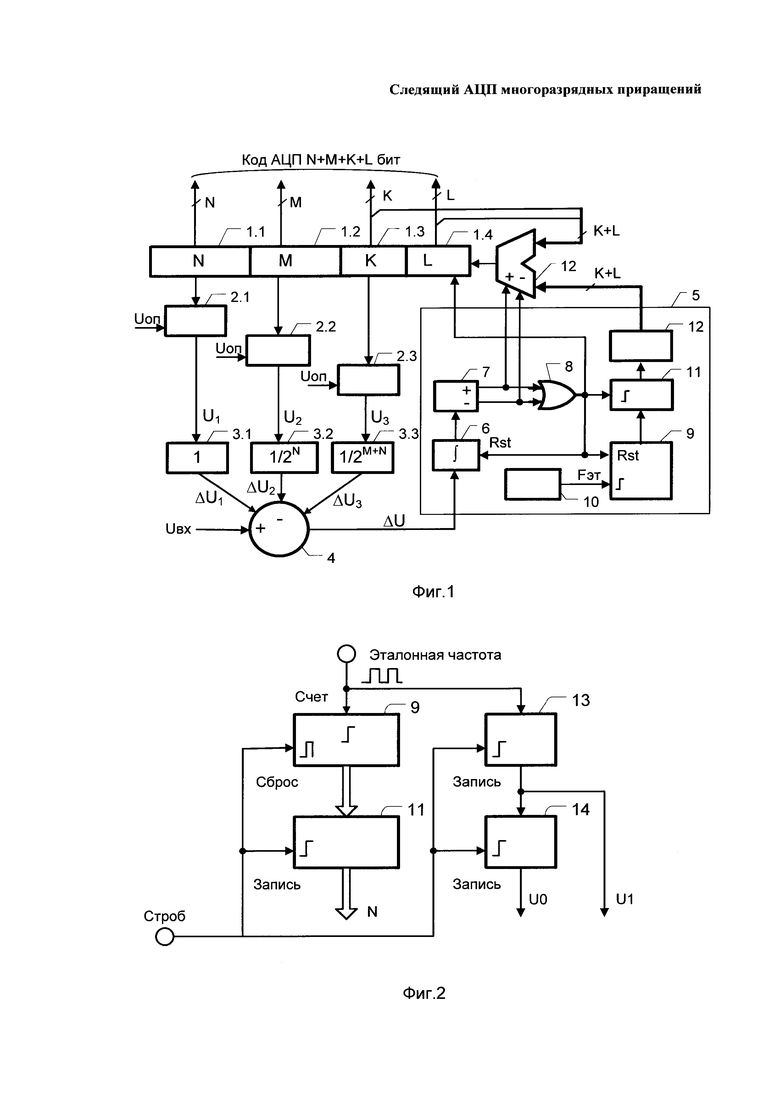

На фиг. 3 приведены временные диаграммы сигналов строба и эталонной частоты. На диаграмме приведены примеры поступления сигналов строба с периодом Тх, Tmin и Тmax. За это время на счетчик 9 поступает 5 счетных импульсов эталонной частоты, при этом уровень сигнала эталонной частоты в момент прихода стробов разный, поэтому число полутактов по формуле 3 составляет соответственно 10, 9 и 11 полутактов эталонной частоты в соответствии с формулой 3.

Параметры интегратора 6 и компаратора 7 выбираются такими, чтобы при разностном напряжении, равном Ulow, частота строба при заданной эталонной частоте давала выходной код, равный 2L. Тогда, четыре разряда счетчика полутактов 11 обеспечивают вычисление 4-разрядного кода приращения реверсивного счетчика 1, тем самым повышая скорость сходимости АЦП в 16 раз. Если разрядность счетчика полутактов 11 повысить, то дополнительные разряды можно использовать для оценки величины разностного напряжения, тем самым повысить точность следящего АЦП на несколько дополнительных разрядов.

Предложенное техническое решение позволяет повысить скорость сходимости следящего АЦП и его точность с малыми аппаратными затратами и низким потреблением.

Источники информации

1. Патент США 2989741.

2. Патент РФ 2045813.

3. Патент США 6850180.

4. Патент США 5014056 – прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЛЕДЯЩИЙ СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД | 2017 |

|

RU2659468C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2010 |

|

RU2441317C1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| УСТРОЙСТВО И СПОСОБ ПРЕОБРАЗОВАНИЯ АНАЛОГОВОГО СИГНАЛА В ЦИФРОВУЮ ФОРМУ, УСТРОЙСТВО И СПОСОБ ПРЕОБРАЗОВАНИЯ МНОЖЕСТВА ДВОИЧНО-КОДИРОВАННЫХ ЧИСЛОВЫХ ОТСЧЕТОВ СИГНАЛА В АНАЛОГОВЫЙ СИГНАЛ | 1994 |

|

RU2159505C2 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| Цифровой преобразователь тока компенсационного типа | 2017 |

|

RU2650844C1 |

Изобретение относится к измерительной технике, в частности к следящим АЦП многоразрядных приращений, и может быть использовано для непрерывного преобразования напряжения в цифровой код для преобразователей сигналов сельсин-код, резольвер-код и магниточувствительных датчиков угла поворота и положения на основе магниторезистивных сенсоров и датчиков Холла. Техническим результатом является повышение скорости сходимости следящего АЦП и повышение его точности. Устройство содержит реверсивный счетчик, который разделен на несколько ступеней малой разрядности, каждая из которых содержит ЦАП с заданной разрядностью, делители, вычитатель, сумматор-вычитатель, дополнительный АЦП, содержащий интегратор, компаратор, элемент ИЛИ, счетчик времени срабатывания компаратора в полутактах эталонной частоты и ПЗУ. 3 ил.

Следящий АЦП многоразрядных приращений, включающий в себя реверсивный счетчик, соединенный с ЦАП, вычитатель входного сигнала и выхода ЦАП, дополнительный АЦП разностного сигнала, вход которого соединен с выходом вычитателя, а старшие разряды выходного кода которого соединены со схемой приращения реверсивного счетчика, а младшие разряды которого образуют в совокупности с разрядами реверсивного счетчика выходной код следящего АЦП, отличающийся тем, что реверсивный счетчик разделен на несколько ступеней малой разрядности, каждая из которых содержит малоразрядный ЦАП, соединенный со ступенью реверсивного счетчика, выход которого соединен с делителем с коэффициентом деления, соответствующим разрядности предыдущих ступеней, выходы делителей соединены со схемой вычитателя входного напряжения, выход которой соединен с дополнительным АЦП разностного сигнала, который выполнен в виде преобразователя напряжения в частоту и содержит интегратор, выход которого соединен с компаратором, выходы сигналов положительного или отрицательного порога срабатывания которого через элемент ИЛИ соединены со входом сброса интегратора, а также со счетчиком выходного сигнала тактового генератора эталонной частоты в полутактах частоты, регистром-защелкой счетчика и входом сброса младших разрядов выходного кода, выход регистра-защелки соединен с адресным входом ПЗУ, выход ПЗУ соединен с первым входом сумматора-вычитателя приращения реверсивного счетчика, второй вход которого соединен с младшими разрядами выходного кода и младшими разрядами реверсивного счетчика, управляющие входы сумматора-вычитателя соединены с выходами компаратора.

| US 5014056 A, 07.05.1991 | |||

| US 6340943 B1, 22.01.2002 | |||

| СПОСОБ ПРОИЗВОДСТВА ТОЛСТОЛИСТОВОГО ШТРИПСА ДЛЯ МАГИСТРАЛЬНЫХ ТРУБ НА РЕВЕРСИВНОМ СТАНЕ | 2012 |

|

RU2490336C1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

| Следящий аналого-цифровой преобразователь | 1989 |

|

SU1661998A1 |

Авторы

Даты

2017-05-19—Публикация

2016-05-12—Подача