Область техники, к которой относится изобретение

Варианты осуществления, описанные здесь, относятся, в общем, к процессорам. В частности, варианты осуществления, описанные здесь, относятся, в общем, к установлению очередности исполнения инструкций в процессорах с изменением очередности исполнения инструкций.

Уровень техники

Многочисленные современные процессоры представляют собой процессоры с изменением очередности исполнения инструкций (ОоО), которые способны исполнять инструкции в очередности, которая отличается от очередности, в которой инструкции появляются в первоначальной программе программного обеспечения. Термин "очередность программы" часто используется по отношению к очередности исполнения инструкций в первоначальной программе программного обеспечения. Вместо обязательного исполнения инструкций с очередностью исполнения инструкций программы, ОоО-процессор может исполнять инструкции с очередностью, которая может зависеть от доступности входных данных, а также от потенциально различных других факторов. Посредством примера, возможны ситуации, когда некоторые младшие по значимости инструкции должны вводить данные из старших по значимости инструкций, в то время как другие младшие по значимости инструкции не должны вводить данные из любых старших по значимости инструкций.

Исполнение инструкций с изменением их очередности (ОоО) позволяет процессору незамедлительно исполнять инструкции, которые готовы к исполнению без задержки, связанной с ожиданием предыдущих инструкций, которые сами по себе могут быть не готовы к исполнению, так как они ожидают обработки данных. Очередность, с которой инструкции фактически исполняются в ОоО-процессоре, часто упоминается как очередность данных. Далее ОоО-процессор может переупорядочить результаты исполнения и/или состояние архитектуры и представить результаты исполнения и/или состояние архитектуры (например, для программного обеспечения, пользователя и т.д.) в виде первоначальной очередности программы вместо очередности данных, в которой были фактически исполнены инструкции. Преимущественно, такие ОоО-процессоры обычно имеют повышенную производительность и/или быстродействие, необходимую в части повышения использования каскадов конвейера или обработки временных слотов.

Однако одна сложная задача, связанная с ОоО-процессорами, в некоторых ситуациях состоит в том, что проблемы могут возникать тогда, когда ресурс, который должен быть доступен в очереди программы, доступен в очередности данных в результате изменения исполнения инструкций с изменением их очередности.

Краткое описание чертежей

Настоящее изобретение можно будет лучше понять со ссылкой на последующее описание и сопроводительные чертежи, которые используются для иллюстрации вариантов осуществления. На чертежах:

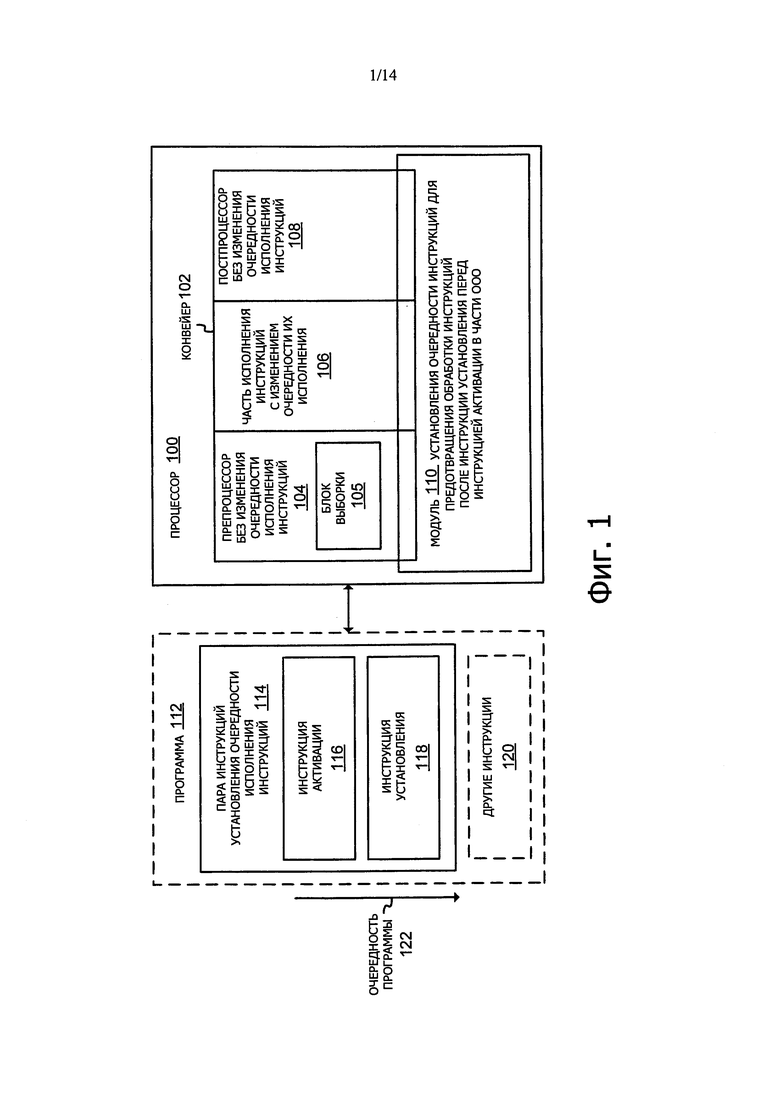

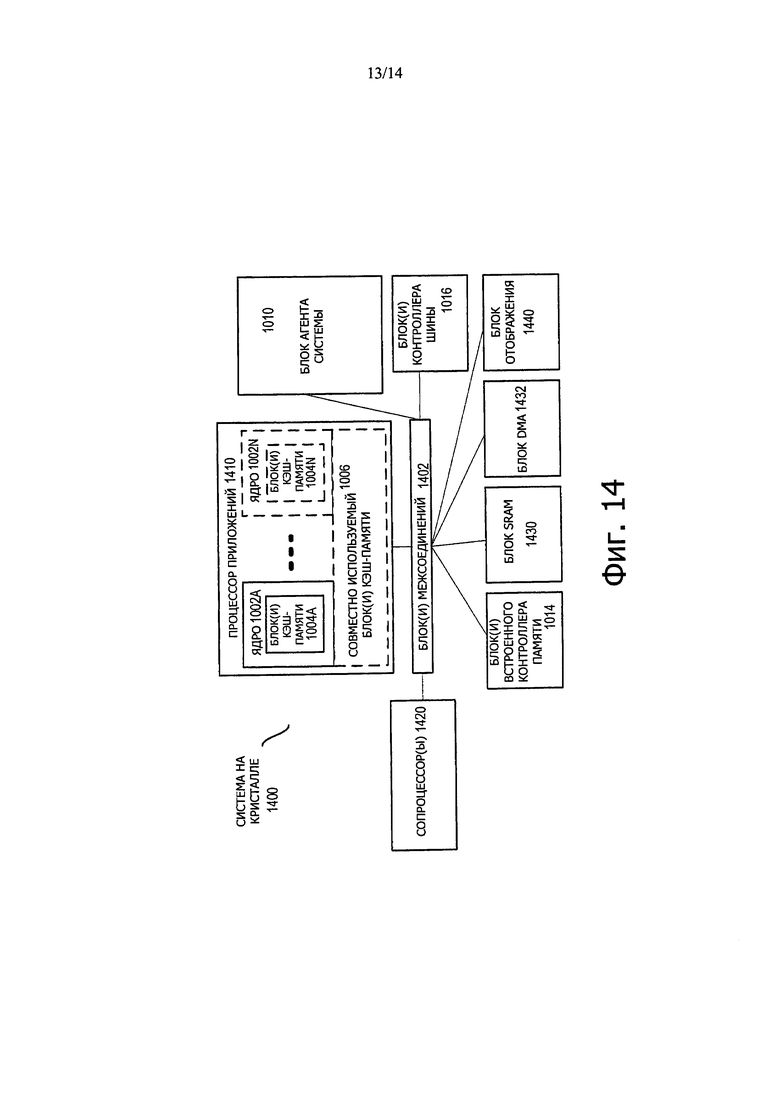

на фиг. 1 показана блок-схема варианта осуществления процессора, который выполнен с возможностью обработки или выполнения пары инструкций установления очередности исполнения инструкций;

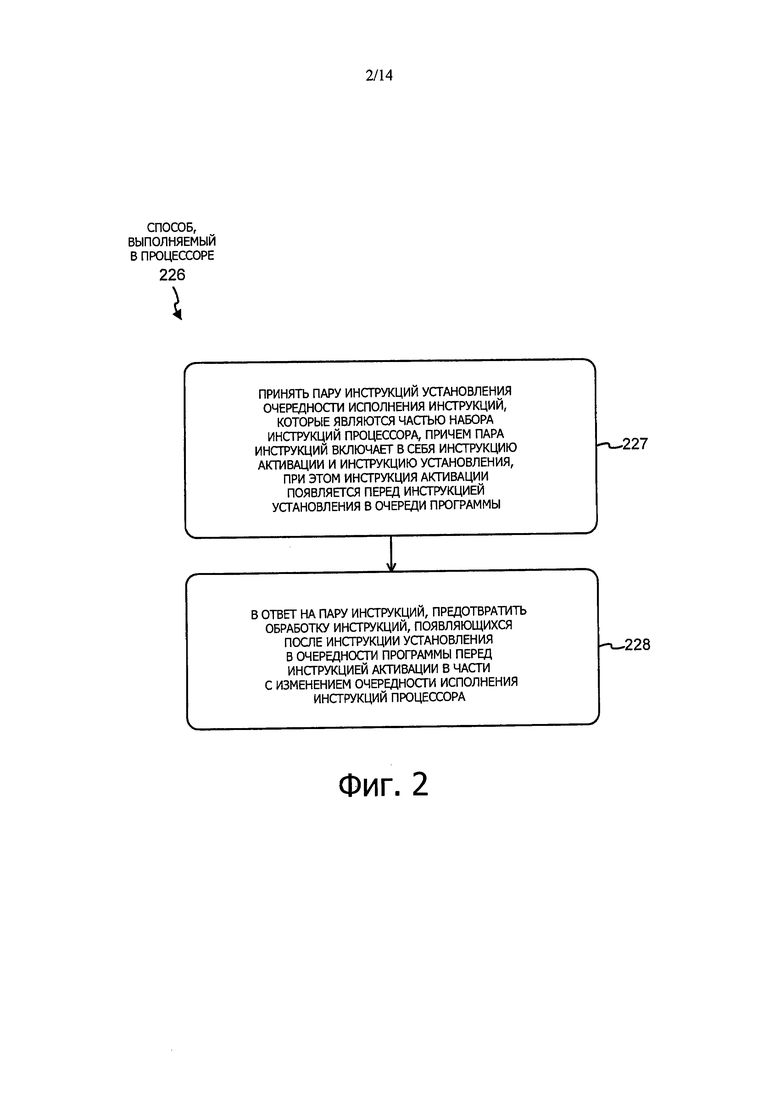

на фиг. 2 показана блок-схема последовательности операций варианта осуществления способа, который выполняется в процессоре для обработки или выполнения варианта осуществления пары инструкций установления очередности исполнения инструкций;

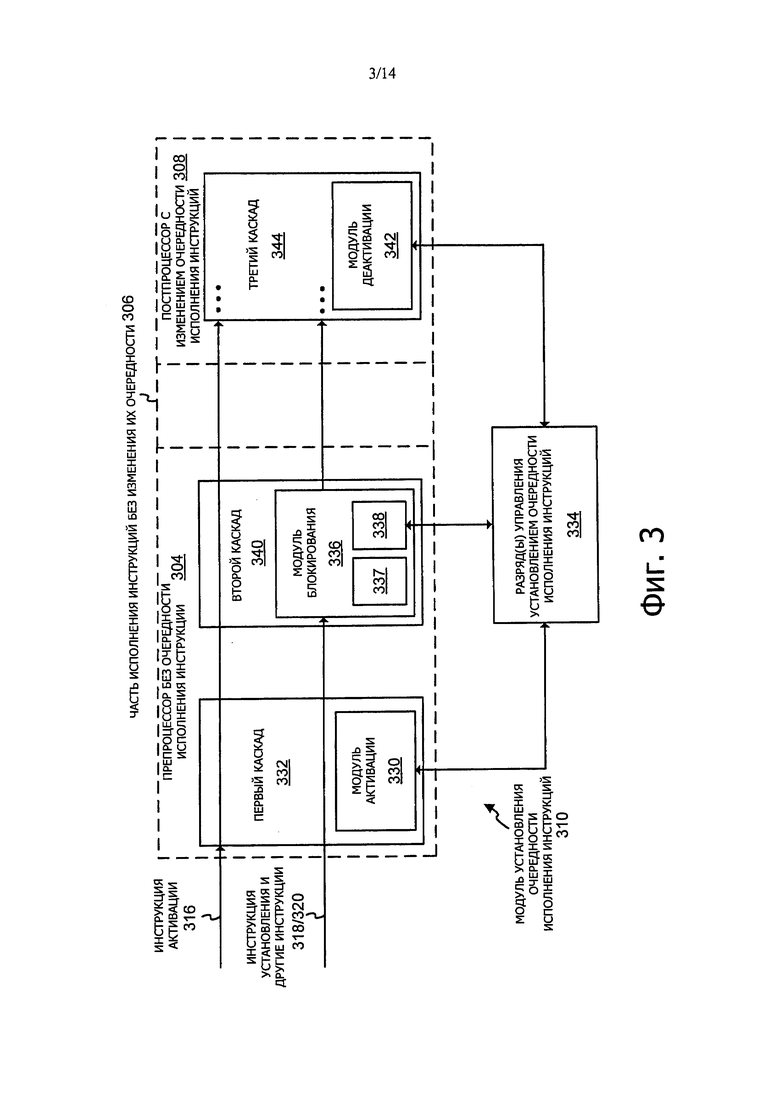

на фиг. 3 показана блок-схема первого примерного варианта осуществления подходящего модуля установления очередности исполнения инструкций;

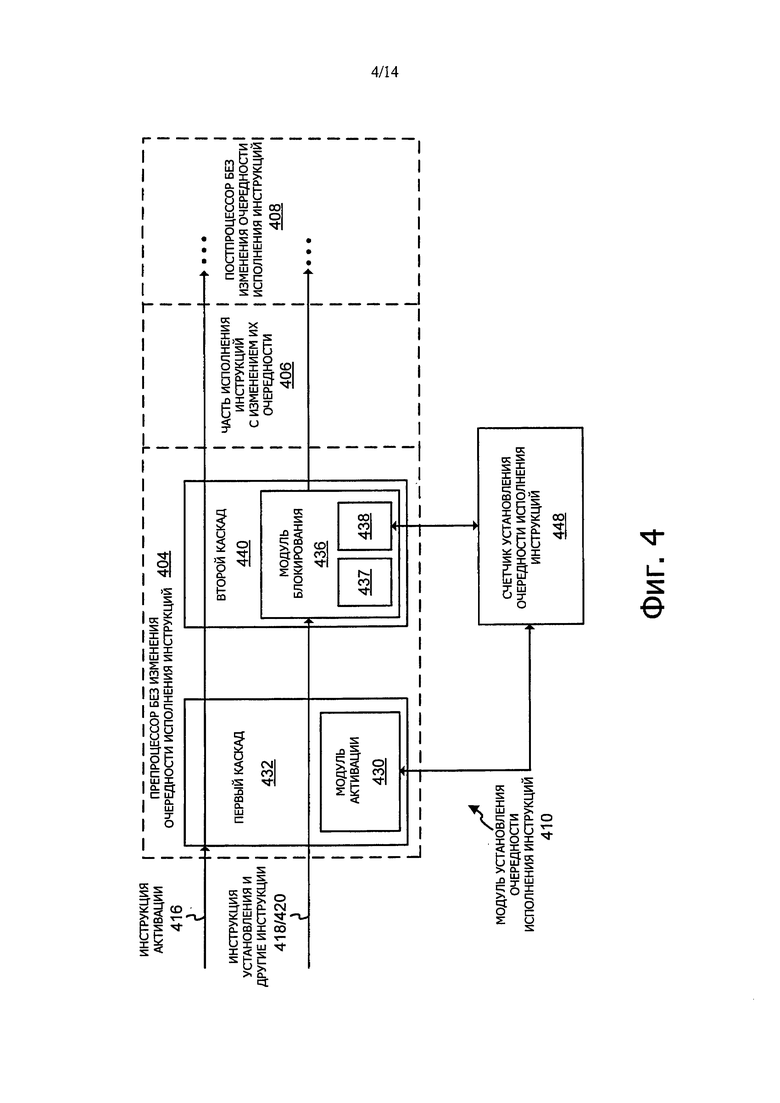

на фиг. 4 показана блок-схема второго примерного варианта осуществления подходящего модуля установления очередности исполнения инструкций;

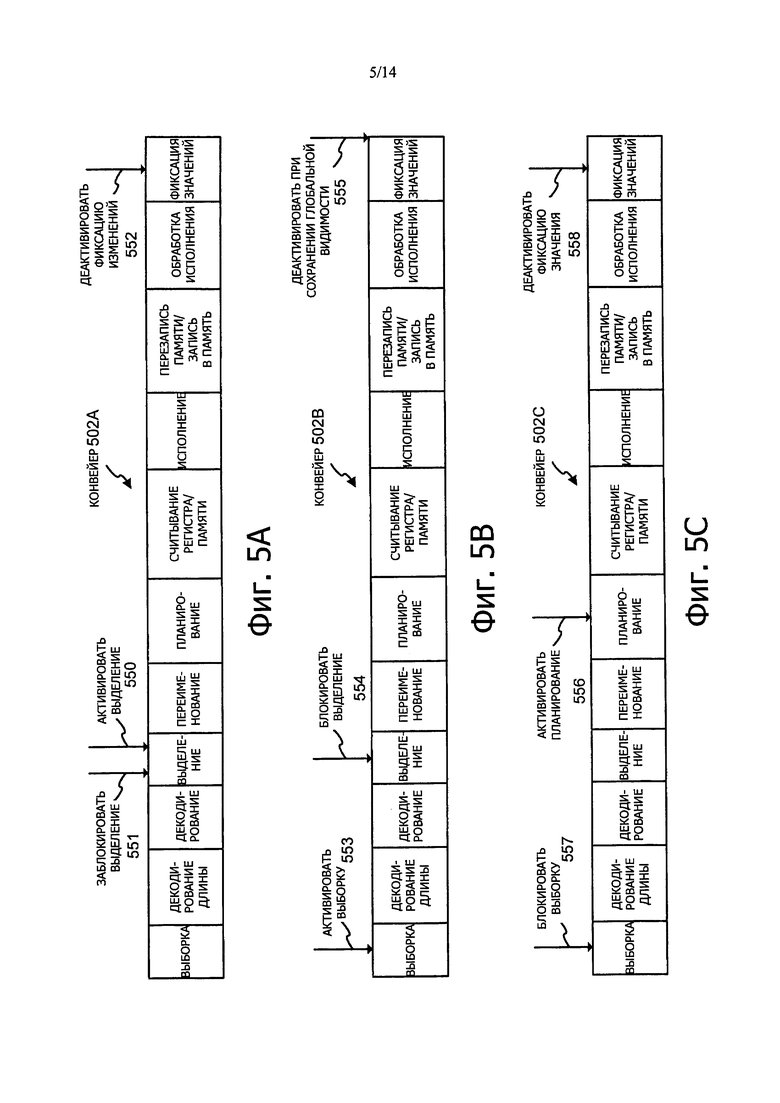

на фиг. 5А-С показаны блок-схемы, иллюстрирующие несколько вариантов осуществления подходящих каскадов конвейера для реализации активации, установления и деактивации очередности исполнения инструкций;

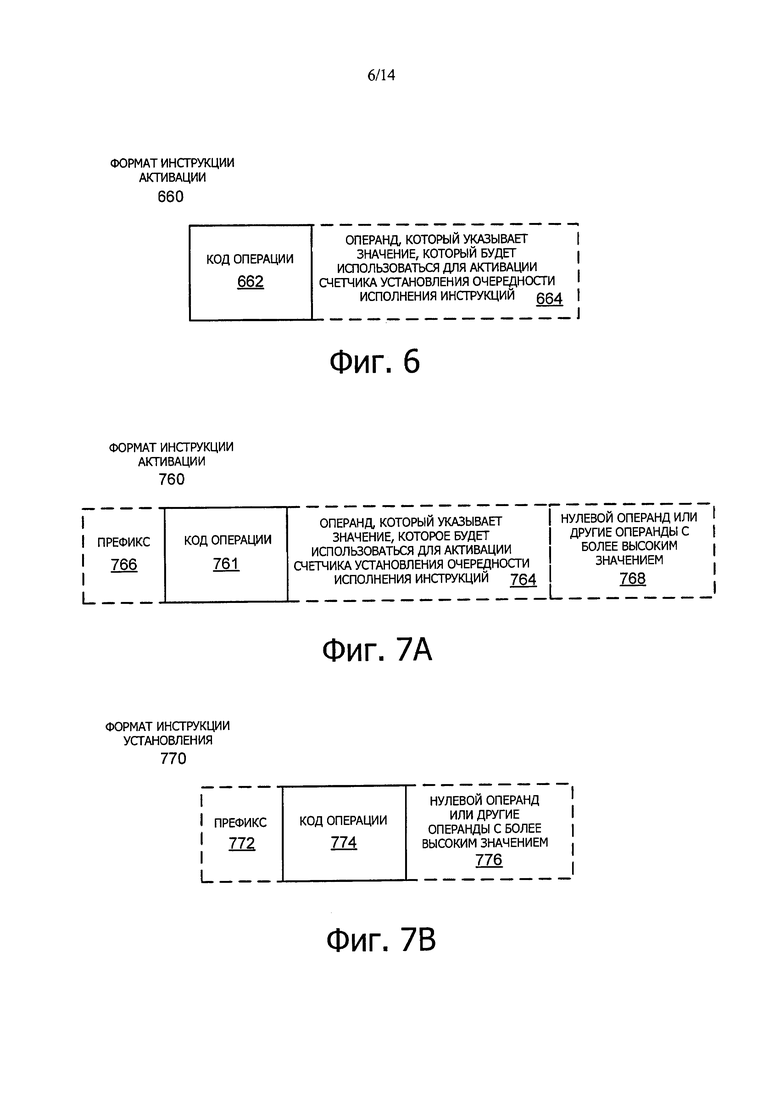

на фиг. 6 показана блок-схема первого варианта осуществления подходящего формата инструкции активации;

на фиг. 7А показана блок-схема второго варианта осуществления подходящего формата инструкции активации;

на фиг. 7В показана блок-схема варианта осуществления подходящего формата инструкции установления;

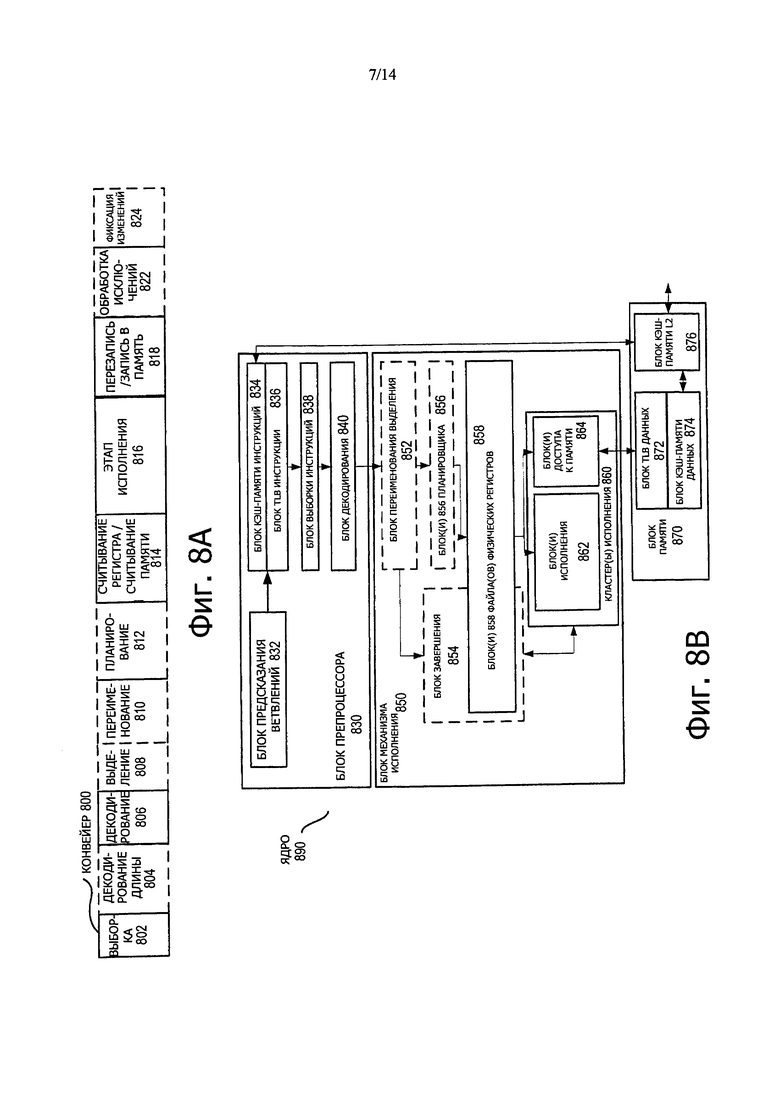

на фиг. 8А показана блок-схема, иллюстрирующая как примерный конвейер исполнения инструкций без изменения их очередности и примерное переименование регистров, так и конвейер с изменением очередности выдачи/исполнения инструкций согласно вариантам осуществления изобретения;

на фиг. 8В показана блок-схема, иллюстрирующая как примерный вариант осуществления ядра архитектуры исполнения инструкций без изменения их очередности и примерное переименование регистров, так и ядро архитектуры с изменением очередности выдачи/исполнения инструкций, которое будет включено в процессор, согласно вариантам осуществления изобретения;

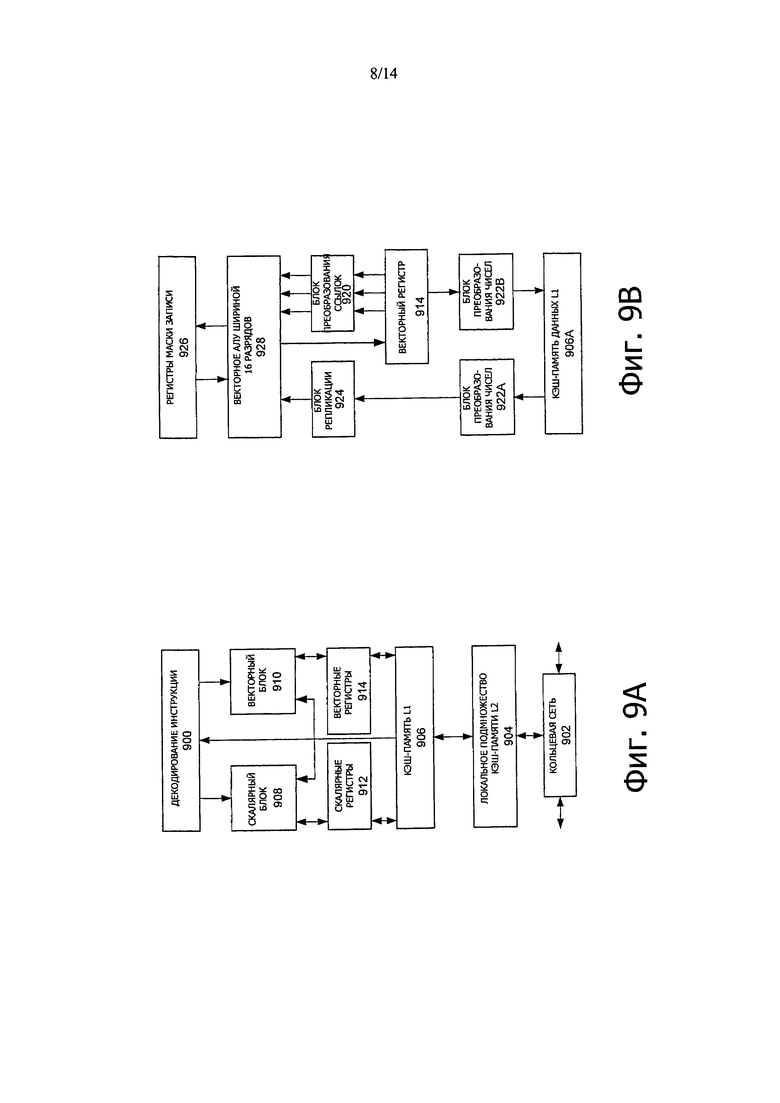

на фиг. 9А показана блок-схема одного ядра процессора наряду с его подсоединением к сети межсоединений на кристалле и с его локальным подмножеством кэш-памяти 2-го уровня (L2) согласно вариантам осуществления изобретения;

на фиг. 9В показан расширенный вид части ядра процессора (фиг. 9А) согласно вариантам осуществления изобретения;

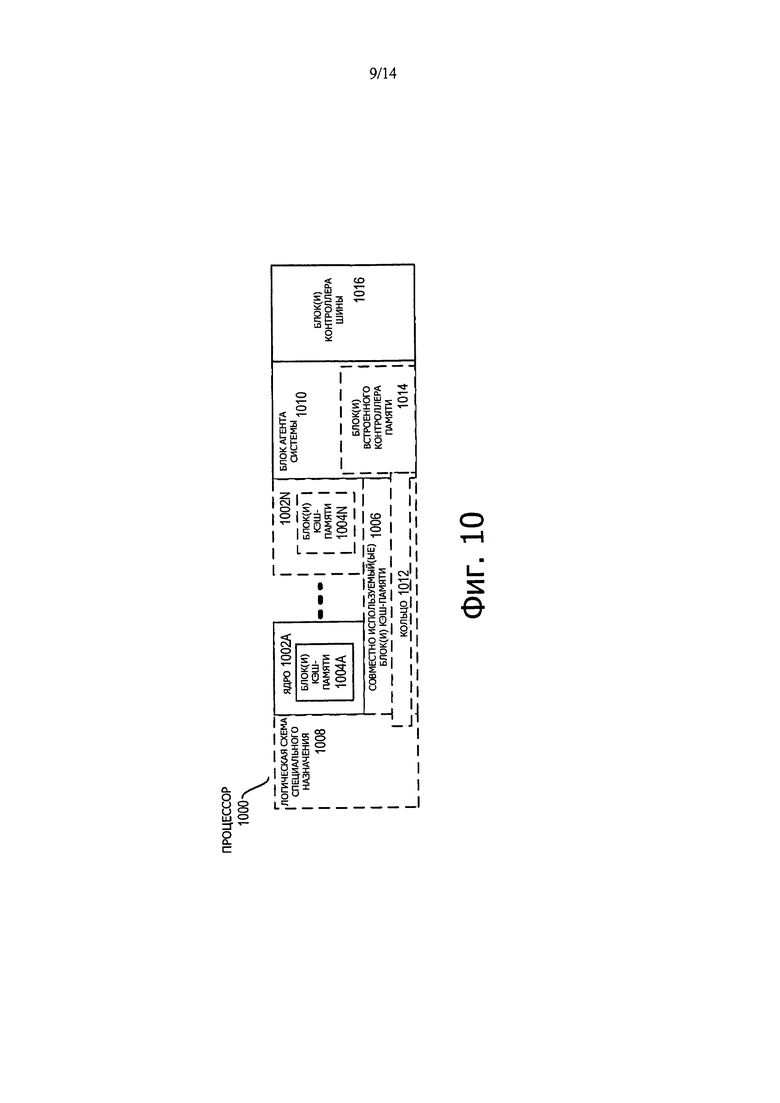

на фиг. 10 показана блок-схема процессора, который может иметь более одного ядро, может иметь встроенный контроллер памяти и может иметь встроенную графику согласно вариантам осуществления изобретения;

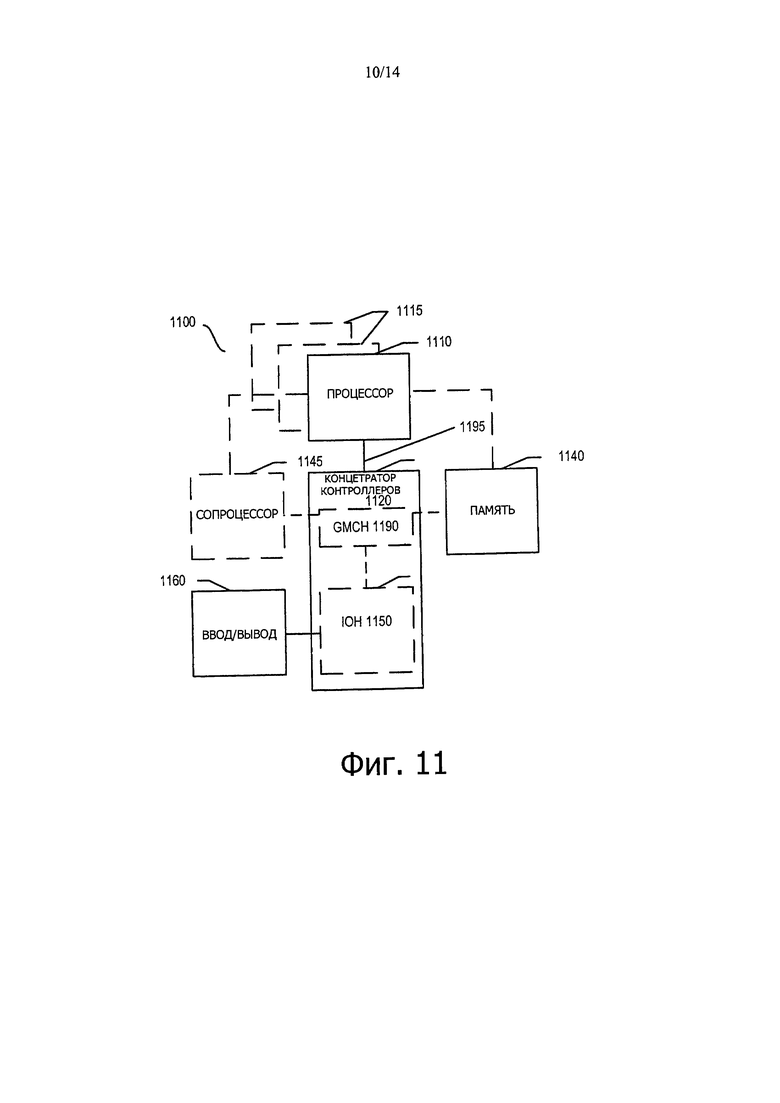

на фиг. 11 показана блок-схема системы в соответствии с одним вариантом осуществления настоящего изобретения;

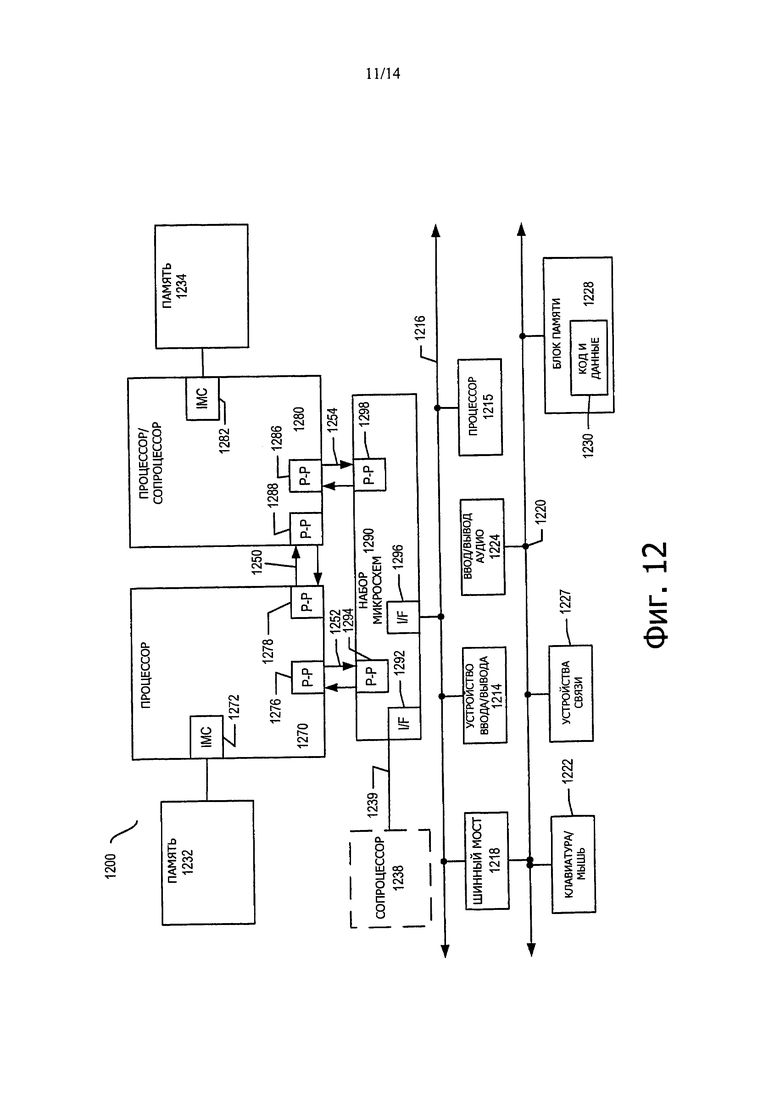

на фиг. 12 показана блок-схема первой более конкретной примерной системы в соответствии с вариантом осуществления настоящего изобретения;

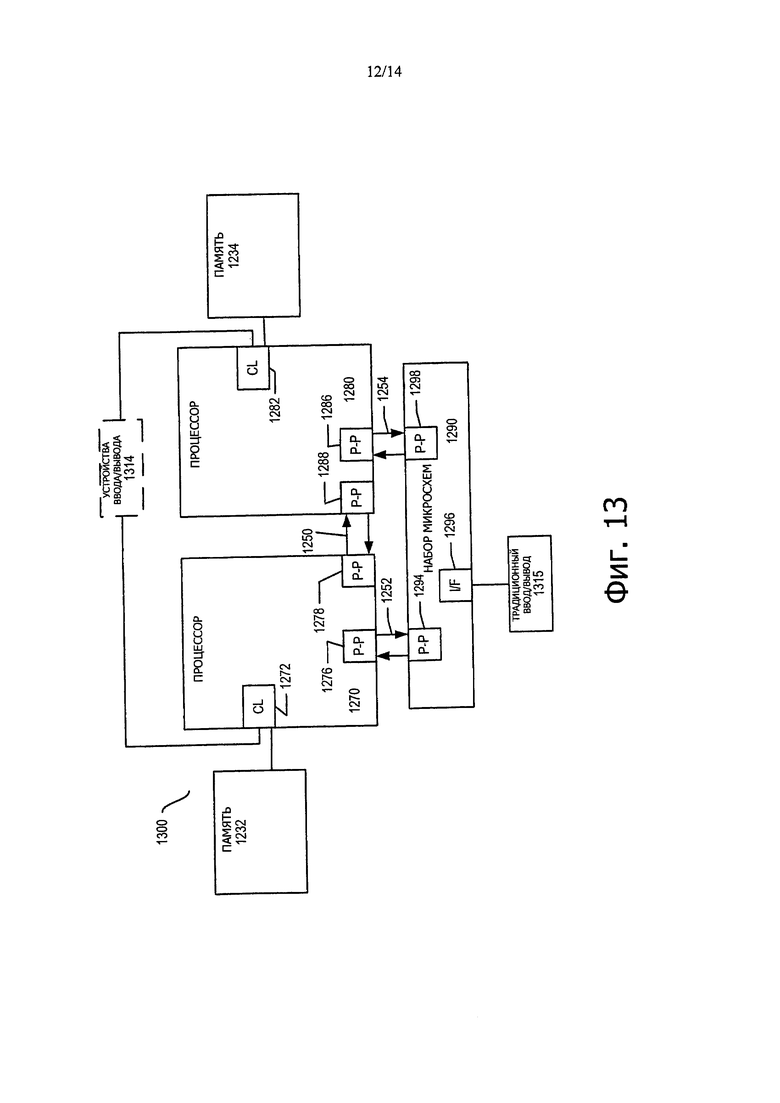

на фиг. 13 показана блок-схема второй более конкретной примерной системы в соответствии с вариантом осуществления настоящего изобретения;

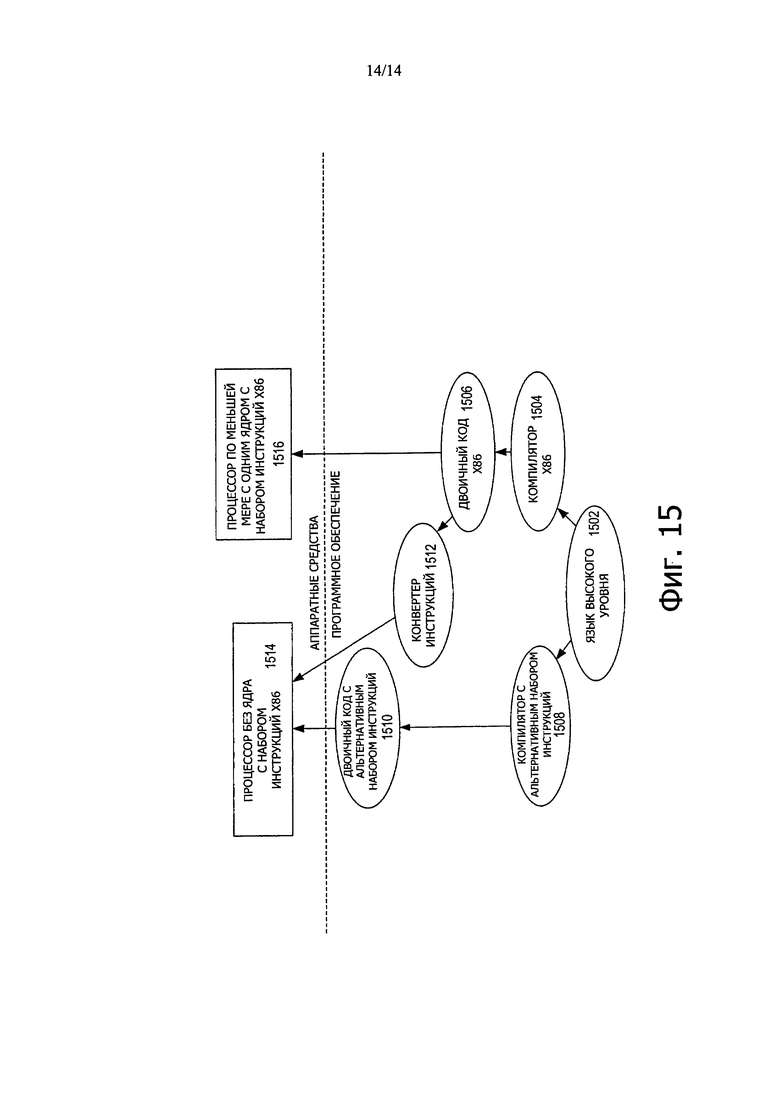

на фиг. 14 показана блок-схема SoC в соответствии с вариантом осуществления настоящего изобретения;

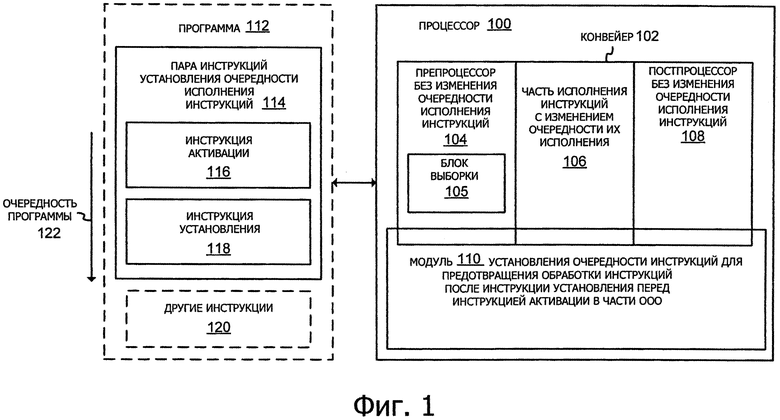

на фиг. 15 показана блок-схема, сопоставляющая использование программного конвертера инструкций для преобразования двоичных инструкций в наборе инструкций источника в двоичные инструкции в целевом наборе инструкций согласно вариантам осуществления изобретения.

Подробное описание изобретения

В данном документе раскрыты пары инструкций установления очередности исполнения инструкций, процессоры для обработки или выполнения пар инструкций, способы, выполняемые процессорами при обработке или выполнении пар инструкций, и системы, входящие в состав одного или более процессоров, для обработки или выполнения пар инструкций. В последующем описании изложены многочисленные конкретные детали (например, функциональные возможности конкретных инструкций, конфигурации процессоров, микроархитектурные детали, последовательности операций и т.д.). Однако варианты осуществления могут применяться на практике без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и технологии не были показаны подробно во избежание усложнения понимания описания.

На фиг. 1 показана блок-схема варианта осуществления процессора 100, который выполнен с возможностью обработки или выполнения пары инструкций 114 установления очередности исполнения инструкций. В некоторых вариантах осуществления процессор 100 может представлять собой процессор общего назначения (например, центральное процессорное устройство (CPU), или другой микропроцессор общего назначения, или процессор типа, который используется в настольном компьютере, ноутбуке, планшетном компьютере и в подобных компьютерах). Альтернативно, процессор может представлять собой процессор специального назначения. Примеры подходящих процессоров специального назначения включают в себя, но не ограничиваются ими, сетевые процессоры, коммуникационные процессоры, криптографические процессоры, графические процессоры, сопроцессоры, встроенные процессоры, процессоры цифровых сигналов (DSPS) и контроллеры (например, микроконтроллеры), и это всего лишь несколько примеров. Процессор может вполне представлять собой любой из различных процессоров с полным набором команд (CISC), различных процессоров с сокращенным набором инструкций (RISC), различных процессоров с очень длинным командным словом (VLrW), различных их гибридов и других типов процессоров.

Показана также программа 112. Посредством примера, программа может храниться в основной памяти или в другом подходящем запоминающем устройстве. Во время работы программа может запускаться, исполняться или иным образом выполняться процессором. Процессор может осуществлять выборку или иным образом принимать инструкции программы. В некоторых вариантах осуществления инструкции программы могут представлять собой часть набора инструкций процессора. Инструкции из набора инструкций могут представлять собой макроинструкции относительно высокого уровня, инструкции на языке ассемблера, инструкции на уровне машины или управляющие сигналы на уровне набора инструкций, который можно подать в процессор для исполнения в отличие от микроинструкций относительно низкого уровня, микроопераций или других инструкций или управляющих сигналов, декодируемых процессором из инструкций относительно более высокого уровня.

В некоторых вариантах осуществления процессор может представлять собой процессор 100 с изменением очередности исполнения инструкций (ОоО-процессор), который выполнен с возможностью исполнения инструкций с изменением очередности. ОоО-процессоры были обсуждены выше в разделе "Уровень техники". ОоО-процессор имеет ОоО-конвейер 102. Конвейер включает в себя препроцессор 104 без изменения очередности исполнения инструкций, часть 106 с изменением очередности исполнения инструкций и постпроцессор 108 без изменения очередности исполнения инструкций. Конкретные блоки или составные части этих фаз конвейера могут изменяться от реализации к реализации. В одном репрезентативном варианте осуществления препроцессор без изменения очередности исполнения инструкций может включать в себя блок или каскад выборки инструкций (например, блок 105 выборки), блок или каскад декодирования длины, блок или каскад декодирования, блок или каскад выделения, блок или каскад переименования. В одном репрезентативном варианте осуществления часть с изменением очередности исполнения инструкций может включать в себя блок или каскад планировщика (который иногда также упоминается как блок отправки или выдачи), регистровый(е) файл(ы) блоки и блок памяти или каскад считывания регистра/считывания памяти, исполнительный модуль(и) или каскад, блоки регистрового(ых) файла(ов) и блок памяти или каскад перезаписи/записи в память. В одном репрезентативном варианте осуществления постпроцессор без изменения очередности исполнения инструкций включает в себя каскад обработки исключений и блок или каскад завершения или фиксации изменений. Это является просто одним конкретным примером и следует понимать, что объем изобретения не ограничивается этим конкретным примером. В других вариантах осуществления можно использовать другие комбинации и конфигурации блоков и/или каскадов конвейера. В общем, для ОоО-процессоров применимы любые комбинации или конфигурация блока и/или каскадов конвейера, известных в технике.

Одна проблема ОоО-процессоров состоит в том, что иногда важно или по меньшей мере полезно поддерживать некоторые инструкции в первоначальной очередности программы даже в пределах ОоО-части 106 процессора. Посредством примера, может иметь случай, когда ячейка памяти, отображенное значение ввода-вывода или другой ресурс должны только обновляться или иным образом иметь доступ первоначальной очередности программы. Характерно, если ячейка памяти обновляется с очередностью данных вместо очередности программы, то может возникнуть ошибка (например, запись более старой/предыдущей инструкции можно обновить на запись более новой инструкции, исполняемой с изменением ее очередности около более старой/предыдущей инструкции). Такая ошибка может привести к тому, что значения будут отличаться и не соответствовать целям первоначальной программы. В более общем смысле это может иметь место в любых из всевозможных ситуаций, в которых может возникнуть некорректный или противоречивый результат или может возникнуть некоторая другая проблема, если инструкции исполняются с изменением очередности (ОоО) и/или с очередностью данных вместо исполнения инструкции без изменения очередности и/или в очереди программы.

Обращаясь снова к фиг. 1, программа включает в себя пару инструкций 114 установления очередности исполнения инструкций. Пара инструкций установления очередности исполнения инструкций включает в себя инструкцию активации 116 и инструкцию установления 118. В некоторых вариантах осуществления инструкцию активации можно выполнить с возможностью заставлять или приводить процессор к активации установления очередности исполнения инструкций, и инструкцию установления можно выполнить с возможностью заставлять или приводить процессор к установлению очередности инструкций. Программа также включает в себя другие инструкции 120. Увеличение очередности 122 программы показано стрелкой, направленной вниз. В иллюстрированном варианте осуществления первоначальная очередность 122 программы обозначает, что инструкция 116 активации появляется перед инструкцией 118 установления в очереди программы. Более того, другие инструкции 120 происходят после инструкции установления в очереди программы. При желании одну или более инструкций (не показано) можно опционально включить в очередность программы между инструкциями активации и установления.

Как показано на иллюстрации, процессор также включает в себя модуль 110 установления очередности исполнения инструкций. Модуль установления очередности исполнения инструкций можно реализовать в виде аппаратных средств (например, в виде интегральной схемы, транзисторов или других элементов схемы и т.д.), программно-аппаратных средств (например, в виде микрокода или других инструкций более низкого уровня, хранящихся в энергонезависимой памяти), программного обеспечения (например, в виде инструкций более высокого уровня, которые хранятся в памяти) или их комбинаций (например, в виде аппаратных средств, потенциально объединенных с одним или более программно-аппаратными средствами и/или программным обеспечением).

В некоторых вариантах осуществления модуль 110 установления очередности исполнения инструкций, в ответ на пару инструкций 114 установления очередности исполнения инструкций, можно выполнить с возможностью предотвращения обработки других инструкций 120, появляющихся после инструкции 118 установления в очередности 122 программы перед инструкцией 116 активации, в части 106 с изменением очередности исполнения инструкций из процессора 100. Пара инструкций может побудить или привести процессор к установлению ограничения исполнения инструкций на инструкции или операции, выданные перед и после пары инструкций. В некоторых вариантах осуществления инструкцию 116 активации можно выполнить с возможностью активации установления очередности исполнения инструкций в заданном каскаде конвейера, таком, например, как каскад препроцессора 104 без изменения очередности исполнения инструкций. В дальнейшем будут описаны и рассмотрены различные способы активации установления очередности исполнения инструкций. В некоторых вариантах осуществления инструкцию 118 установления можно выполнить с возможностью установления очередности исполнения инструкций в заданном каскаде конвейера, таком, например, как каскад препроцессора 104 без изменения очередности исполнения инструкций. Например, в некоторых вариантах осуществления инструкцию установления можно приостановить в очереди в заданном каскаде конвейера и тем самым предотвратить, а также предотвратить другие более новые инструкции 120, их прохождение через конвейер за пределами данного каскада конвейера. Иногда в более поздний момент времени установление очередности исполнения инструкций можно деактивировать, и затем инструкции установления и другие более новые инструкции могут продолжить прохождение по конвейеру. Преимущественно, это может оказать помощь при установлении очередности исполнения инструкций, например, которая может быть полезна для упорядочивания доступа к ячейкам памяти или другим ресурсам.

Как упоминалось ранее, в некоторых вариантах осуществления инструкции активации и установления могут представлять собой инструкции из набора инструкций процессора. Преимущественно, при использовании двух инструкций из набора инструкций (то есть инструкций уровня набора инструкций) нет никакой необходимости выполнять операции или функции, связанные с очередностью исполнения инструкций, в виде микрокода. В одном аспекте это может стать преимуществом для процессора RISC и/или процессора, который не выполнен с возможностью использования микрокода (например, микроинструкции или микрооперации) для выполнения пары инструкций 114 установления очередности исполнения инструкций (например, процессор может и не использовать микрокод или может использовать только микрокод только лимитированным или ограниченным образом, который не подходит для реализации пары инструкций установления очередности исполнения инструкций). Однако инструкции можно также опционально использовать в CISC и других типах процессоров, включая процессоры, которые позволяют опционально реализовать пару инструкций установления очередности исполнения инструкций в микрокоде. Более того, пара инструкций может позволить специалисту-практику (например, программисту) или программному обеспечению гибко управлять ячейками в программе или коде пары инструкций для достижения желаемой очередности исполнения инструкций.

В некоторых вариантах осуществления, в отличие от некоторых типов инструкций, таких как инструкции сравнения и обмена и т.п., которые затрагивают только одиночный семафор, мьютекс или совместно используемую количественную переменную, варианты осуществления пары инструкций установления очередности исполнения инструкций позволяют упорядочить доступ к многочисленным, с любым количеством, адресам памяти. В некоторых вариантах осуществления, в отличие от некоторых инструкций защиты памяти или барьера памяти, варианты осуществления пары инструкций установления очередности исполнения инструкций могут устанавливать очередность в многочисленных, многих или любого количества различных типов инструкций вместо инструкций только доступа к памяти (например, загрузки памяти, сохранения в память, загрузки памяти и сохранения в память и т.д.). Более того, инструкции защиты памяти обычно устанавливают только очередность доступа к памяти. Напротив, варианты осуществления инструкций, раскрытых в данном документе, могут устанавливать очередность доступа к памяти, а также устанавливать очередность для других аспектов, таких, например, как доступ к регистрам, арифметические операции и/или время обработки инструкций. В дополнение, варианты осуществления инструкций, раскрытые в данном документе, позволяют устанавливать очередность в других ситуациях, в которых инструкции защиты памяти обычно не позволяют устанавливать очередность. В качестве примера рассмотрим устройство ввода/вывода (I/O), которое имеет два местоположения: первое местоположение X и второе местоположение Y. Запись X может разрешить считывание Y. Инструкции защиты памяти могут поддерживать взаимодействие между Y, который появляется спустя некоторое время после X, но не наоборот.

Во избежание излишнего усложнения описания процессор описан и показан в упрощенном виде. Процессор может опционально включать в себя другие известные компоненты, которые обычно используются в процессорах. Примеры таких компонентов включают в себя, но не ограничиваются ими, блок предсказания ветвлений, кэш-память данных и инструкций, кэш-память второго или более высокого уровня, буферы предварительной выборки для трансляции данных и инструкций, буферы предварительной выборки, блок переименования регистра, блок планирования инструкций, блоки шинного интерфейса, блок завершения, другие компоненты, включенные в процессоры, и различные их комбинации. В процессорах существуют в прямом смысле многочисленные различные комбинации и конфигурации компонентов, и варианты осуществления не ограничиваются какой-либо конкретной комбинацией или конфигурацией. Варианты осуществления могут быть включены в процессоры, имеющие многочисленные ядра, логические процессоры или исполнительные блоки, по меньшей мере один из которых выполнен с возможностью обработки пары инструкций установления очередности исполнения инструкций так, как это раскрыто в данном документе.

На фиг. 2 показана блок-схема последовательности операций варианта осуществления способа 226, выполняемого в процессоре для обработки или для выполнения варианта осуществления пары инструкций установления очередности исполнения инструкций. В различных вариантах осуществления способ можно выполнить с помощью процессора общего назначения, процессора специального назначения или другого устройства для обработки инструкций или цифрового логического устройства. В некоторых вариантах осуществления операции и/или способ, показанный на фиг. 2, можно выполнить с помощью и/или внутри процессора, показанного на фиг. 1. Компоненты, признаки и специфические опциональные детали, описанные в данном документе для процессора (фиг. 1), также опционально применимы для операций и/или способа (фиг. 2). Альтернативно, операции и/или способ (фиг. 2) можно выполнить с помощью и/или внутри аналогичного или другого процессора. Более того, процессор (фиг. 1) может выполнять операции и/или способы, подобные, аналогичные или различные чем операции и/или способы, показанные на фиг. 2.

Способ включает в себя прием пары инструкций установления очередности исполнения инструкций на этапе 227. В различных аспектах пару инструкций можно принимать в процессоре или его части (например, в блоке выборки инструкций, кэш-памяти инструкций, декодере и т.д.). В различных аспектах инструкцию можно принимать из источника вне кристалла (например, из памяти, межсоединения вне кристалла и т.д.) или из источника на кристалле (например, из кэш-памяти инструкций). Пара инструкций установления очередности исполнения инструкций может представлять собой часть набора инструкций процессора. В некоторых вариантах осуществления пара инструкций установления очередности исполнения инструкций может включать в себя инструкцию активации и инструкции установления. Обычно инструкция активации может появляться перед инструкцией установления в очереди программы.

Способ включает в себя, в ответ на пару инструкций установления очередности исполнения инструкций, предотвращение обработки инструкций, появляющихся после инструкции установления в очереди программы перед инструкцией активации в части с изменением очередности исполнения инструкций процессора на этапе 228. В некоторых вариантах осуществления этот способ может включать в себя активацию установления очередности исполнения инструкций, в ответ на инструкцию активации, в первом каскаде конвейера процессора (например, в каскаде препроцессора без изменения очередности исполнения инструкций процессора). В некоторых вариантах осуществления после активации установления очередности исполнения инструкций способ может включать в себя установление очередности исполнения инструкций путем предотвращения продвижения инструкции установления и инструкций, появляющихся после инструкции установления в очереди программы за пределами второго каскада конвейера (например, каскада препроцессора без изменения очередности исполнения инструкций процессора). В некоторых вариантах осуществления инструкцию установления можно удерживать в очереди (например, во втором каскаде конвейера) и можно предотвратить продвижение инструкций после инструкции установления в очереди программы около инструкции установления. Некоторое время спустя установление очередности исполнения инструкций можно деактивировать, и затем инструкция установления и инструкции после инструкции установления могут продвигаться по конвейеру.

Способ был показан и описан в относительно простом формате, но операции можно опционально добавить и/или удалить из способа. Например, в других вариантах осуществления способ может опционально включать в себя выборку инструкций, декодирование инструкций, планирование инструкций (например, планирование изменения очередности исполнения инструкции активации), исполнение инструкций, выполнение микроархитектурных операций, связанных с исполнением инструкций (например, модификацию одного или более разрядов, программирование или активацию счетчика и т.д.), фиксацию изменений инструкций и т.д.

На фиг. 3 показана блок-схема первого примерного варианта осуществления подходящего модуля 310 установления очередности исполнения инструкций. В некоторых вариантах осуществления модуль 310 установления очередности исполнения инструкций может быть включен в процессор (фиг. 1) и/или можно использовать для выполнения операции(й) или способа (фиг. 2). Альтернативно, модуль 310 установления очередности исполнения инструкций может быть включен в аналогичный или другой процессор и/или можно использовать для выполнения аналогичных или различных операций или способов. Более того, процессор (фиг. 1) может включать в себя аналогичный или другой модуль установления очередности исполнения инструкций чем тот, который показан на фиг. 3, и/или операцию(и) или способ (фиг. 2) можно выполнить с помощью аналогичного или другого модуля установления очередности исполнения инструкций, чем тот, который показан на фиг. 3.

Модуль 310 установления очередности исполнения инструкций включает в себя модуль активации 330. Модуль активации выполнен с возможностью инициирования или активации установления очередности исполнения инструкций в ответ на инструкцию 316 активации в первом каскаде 332 конвейера процессора. Как показано, в некоторых вариантах осуществления первый каскад 332 может находиться внутри препроцессора 304 без изменения очередности исполнения инструкций, хотя объем настоящего изобретения не ограничивается этим. Посредством примера, подходящие примеры первого каскада внутри препроцессора без изменения очередности исполнения инструкций включают в себя, но не ограничиваются ими, каскад выборки, каскад декодирования и каскад выделения или различные места, расположенные между ними. Альтернативно, другие каскады в препроцессоре без изменения очередности исполнения инструкций или другой участок процессора можно использовать опционально. Например, первый каскад может представлять собой каскад исполнения, каскад планирования или другой каскад. В некоторых вариантах осуществления активация может находиться в препроцессоре без изменения очередности исполнения инструкций, и деактивация может находиться в препроцессоре без изменения очередности исполнения инструкций секции с изменением очередности исполнения инструкций или постпроцессоре без изменения очередности исполнения инструкций. Если каскады конвейера, которые используются непосредственно инструкциями активации и установления, не гарантируют достаточного порядка во избежание сценария зависания (например, если инструкции активации и установления выдаются с очередностью таким образом, что возникает проблема), то в процессор можно включить некоторый другой механизм для обеспечения гарантии достаточного порядка во избежание таких сценариев зависания.

В этом первом примерном варианте осуществления активация установления очередности исполнения инструкций происходит с помощью одного или более разрядов 334 управления установлением очередности исполнения инструкций. Как показано, модуль активации может быть связан с одним или более разрядами 334 управления. В некоторых вариантах осуществления модуль активации можно выполнить с возможностью модификации или изменения одного или более разрядов 334 управления из первого состояния (например, начального двоичного значения) во второе другое состояние (например, другое двоичное значение) для активизации установления очередности исполнения инструкций. В качестве одного конкретного примера, модуль активации можно выполнить с возможностью установки единственного бита на двоичную единицу для активации установления очередности исполнения инструкций, тогда как одиночный разряд можно иным образом заменить на двоичный нуль при деактивации такого установления очередности исполнения инструкций.

Модуль 310 установления очередности исполнения инструкций также включает в себя модуль 336 блокирования. Модуль блокирования выполнен с возможностью, в ответ на инструкции активации и установлении при установлении очередности исполнения инструкций, установления очередности исполнения инструкций. В некоторых вариантах осуществления модуль блокирования можно выполнить с возможностью блокирования или предотвращения продвижения инструкции установления и других инструкций, возникающих после инструкции установления в очереди программы, за пределами второго каскада 340 конвейера. Как показано, в некоторых вариантах осуществления, второй каскад может находиться в отдельном каскаде, чем модуль активации, и модуль блокирования может быть соединен с модулем активации. В других вариантах осуществления второй каскад и/или модуль блокирования может находиться в том же самом каскаде, как и модуль активации. Посредством примера подходящие каскады для модуля блокирования включают в себя, но не ограничиваются ими, каскад выборки, каскад декодирования, каскад выделения, каскад планирования, каскад исполнения и различные места между ними. Альтернативно, можно опционально использовать и другие каскады.

Как показано, в этом первом примерном варианте осуществления модуль блокирования может включать в себя логическую схему 338 проверки разряда управления, связанную с разрядами управления. Логическая схема проверки разряда управления и/или модуль блокирования можно выполнить с возможностью считывания или осуществления доступа к разрядам управления для определения того, активируется или нет в текущий момент времени установление очередности исполнения инструкций. Как дополнительно показано, в этом первом примерном варианте осуществления модуль блокирования может включать в себя логическую схему 337 удержания инструкции (например, очередь, многопоточный ресурс, который совместно используется инструкциями из двух или более потоков и т.д.), которая выполнена с возможностью удержания инструкции установления. В некоторых вариантах осуществления, когда это определено, что установление очередности исполнения инструкций активирована, логическую схему удержания инструкции и/или модуль блокирования можно выполнить с возможностью удержания инструкции установления во втором каскаде 340 и предотвращения продвижения других инструкций после инструкции установления в очереди программы около инструкции установления и/или продвижения за пределы второго каскада. Конвейерное исполнение для потока, имеющего инструкции активации и установления и инструкции после инструкций установления, можно, по существу, приостановить или сделать паузу в течение периода времени. Во время этого периода времени инструкции из других потоков можно опционально поместить в конвейер, чтобы воспользоваться преимуществами неиспользованных слотов или каскадов конвейера.

В этом первом примерном варианте осуществления модуль 310 установления очередности исполнения инструкций может также включать в себя модуль 342 деактивации. В некоторых вариантах осуществления модуль деактивации можно выполнить с возможностью деактивации установления очередности исполнения инструкций, в ответ на инструкцию 316 активации, в третьем каскаде 344 конвейера. Как показано, в некоторых вариантах осуществления, модуль деактивации может быть связан с одним или более разрядами управления установлением очередности исполнения инструкций 334. В некоторых вариантах осуществления модуль деактивации может изменять или модифицировать разряды 334 управления из второго состояния, которое используется для индикации активации, в другое состояние (например, первое состояние), которое используется для индикации деактивации. Как показано, в некоторых вариантах осуществления, третий каскад может находиться внутри постпроцессора 308 без изменения очередности исполнения инструкций, хотя объем изобретения не ограничивается этим. Посредством примера, подходящие места в постпроцессоре без изменения очередности исполнения инструкций включают в себя, но не ограничиваются ими, каскад фиксации изменений, место после фиксации изменений, где сохранение является глобально видимым и известно для появления, но еще фактически не появилось, место после фиксации изменений, где сохранение фактически появилось, и различные места между ними. Альтернативно, можно опционально использовать другие места или каскады в конвейере процессора. После деактивации инструкция установления и другие последующие инструкции в очереди программы могут иметь возможность проходить дальше или продвигаться по конвейеру. В качестве другой опции, в некоторых вариантах осуществления инструкцию установления можно обработать после этого как неоперацию (NOP) во втором каскаде или в последующем каскаде.

На фиг. 4 показана блок-схема второго примерного варианта осуществления подходящего модуля 410 установления очередности исполнения инструкций. В некоторых вариантах осуществления модуль 410 установления очередности исполнения инструкций можно включить в процессор (фиг. 1) и/или можно использовать для выполнения операции(й) или способа (фиг. 2). Альтернативно, модуль 410 установления очередности исполнения инструкций можно включить в аналогичный или другой процессор и/или можно использовать для выполнения аналогичных или других операций или способов. Более того, процессор (фиг. 1) может включать в себя аналогичный или другой модуль установления очередности исполнения инструкций, например, показанный на фиг. 4, и/или операцию(и) или способ (фиг. 2) можно выполнить с помощью аналогичного или другого модуля установления очередности исполнения инструкций, например, который показан на фиг. 4.

Модуль 410 установления очередности исполнения инструкций включает в себя модуль 430 активации. Модуль активации выполнен с возможностью инициирования или активации установления очередности исполнения инструкций в ответ на инструкцию 416 активации в первом каскаде 432 конвейера процессора. Как показано, в некоторых вариантах осуществления первый каскад 432 может находиться в пределах препроцессора 404 без изменения очередности исполнения инструкций, хотя объем изобретения этим не ограничивается. Посредством примера подходящие примеры первого каскада, которые находятся в пределах препроцессора без изменения очередности исполнения инструкций, включают в себя, но не ограничиваются ими, каскад выборки, каскад декодирования и каскад выделения или различные места между ними. Альтернативно, можно использовать и другие каскады в препроцессоре без изменения очередности исполнения инструкций или другой части процессора. Например, первый каскад может представлять собой каскад исполнения, каскад планирования или другой каскад.

В этом втором варианте осуществления активация установления очередности исполнения инструкций выполняется посредством счетчика 448 установления очередности исполнения инструкций. Как показано, модуль 430 активации может быть соединен со счетчиком 448. В некоторых вариантах осуществления модуль активации можно выполнить с возможностью активации или инициирования счетчика для запуска подсчета до заданного или предварительно определенного значения для того, чтобы активировать установление очередности исполнения инструкций. Посредством примера счетчик может осуществлять отсчет от начального значения (например, нуля) до заданного или предварительного определенного значения остановки (например, нуля). В некоторых вариантах осуществления заданное или предварительно определенное значение может быть фиксированным или постоянным для инструкции активации (например, фиксированным для кода операции инструкции активации без возможности точного определения или изменения инструкцией активации, определяемым на основании декодирования декодером кода операции и т.д.). В других вариантах осуществления инструкция активации может иметь операнд для точного определения явным образом значения, которое будет использоваться для счетчика, или указания иным образом значения, которое будет использоваться для счетчика (например, может иметь один или более разрядов для выбора из числа предварительно определенных значений). Преимущественно, это дает возможность программисту или программному обеспечению запрограммировать счетчик со значением, допускающим изменение, которое подходит для конкретной реализации.

Модуль 410 установления очередности исполнения инструкций также включает в себя модуль 436 блокирования. Модуль блокирования выполнен с возможностью, в ответ на инструкции активации и установления при активации установления очередности исполнения инструкций, установления очередности исполнения инструкций. В некоторых вариантах осуществления модуль блокирования можно выполнить с возможностью блокирования или предотвращения продвижения инструкции установления и других инструкций, появляющихся после инструкции установления в очереди программы, за пределами второго каскада 440 конвейера. Как показано, в некоторых вариантах осуществления второй каскад может находиться в другом каскаде, чем модуль активации, и модуль блокирования может быть соединен с модулем активации. В других вариантах осуществления второй каскад и/или модуль блокирования может находиться в том же самом каскаде, как и модуль активации. Посредством примера подходящие каскады для модуля блокирования включают в себя, но не ограничиваются ими, каскад выборки, каскад декодирования, каскад выделения, каскад планирования, каскад исполнения и различные места между ними. Альтернативно, можно опционально использовать и другие каскады.

Как показано, в этом втором варианте осуществления модуль блокирования может включать в себя логическую схему 438 проверки счетчика, которая соединена со счетчиком 448. Логическая схема проверки счетчика и/или модуль блокирования может быть выполнен с возможностью считывания, проверки или доступа к счетчику для определения того, активировано ли в настоящее время установление очередности исполнения инструкций. Альтернативно, счетчик можно выполнить с возможностью оповещения модуля блокирования для указания того, активировано ли в настоящее время установление очередности исполнения инструкций. Как дополнительно показано, в этом первом примерном варианте осуществления модуль блокирования может включать в себя логическую схему 437 удержания инструкции (например, очередь, многопоточный ресурс, который совместно используется инструкциями из двух или более потоков, и т.д.), которая выполнена с возможностью удержания инструкции установления. В некоторых вариантах осуществления, когда определено, что установление очередности исполнения инструкций активировано, логическую схему удержания инструкции и/или модуль блокирования можно выполнить с возможностью удержания инструкции установления во втором каскаде 440 и предотвращения продвижения других инструкций после инструкции установления в очереди программы около инструкции установления и/или перемещения за пределы второго каскада.

В этом втором варианте осуществления установление очередности исполнения инструкций может деактивироваться автоматически после отсчета счета до заданного или предварительно определенного значения. После деактивации инструкция установления и другие последующие инструкции могут иметь возможность проходить дальше или продвигаться по конвейеру (например, через часть 406 с изменением очередности исполнения инструкций и постпроцессор 408 без изменения очередности исполнения инструкций). В качестве другой опции, в некоторых вариантах осуществления инструкцию установления можно после этого опционально рассматривать в качестве неоперации (только для указанных целей) во втором каскаде или последующем каскаде конвейера.

На фиг. 5А-С показаны блок-схемы, иллюстрирующие несколько вариантов осуществления подходящих каскадов конвейера для реализации активации, установления и деактивации очередности исполнения инструкций. На этих схемах каскады конвейера, показанные слева направо, включают в себя выборку, декодирование длины, декодирование, выделение (alloc), переименование, планирование, считывание регистра/памяти, исполнение, перезапись/запись в память, дескриптор исключения и фиксацию изменений. Эти конкретные каскады конвейера не требуются. В общем должны подходить и другие каскады конвейера, известные в технике.

Фиг. 5А иллюстрирует вариант осуществления конвейера 502А, где активация 550 упорядочивания инструкций находится в каскаде выделения, установление или блокирование 551 упорядочивания инструкций находится также в каскаде выделения, и деактивации 552 упорядочивания инструкций находится в каскаде фиксации изменений. Фиг. 5В иллюстрирует вариант осуществления конвейера 502В, где активация 553 упорядочивания инструкций находится в каскаде выборки, установление или блокирование 554 упорядочивания инструкций находится в каскаде выделения, и деактивация 555 упорядочивания инструкций находится в каскаде фиксации изменений в точке, где в целом видно то, что сохраняется. Фиг. 5С иллюстрирует вариант осуществления конвейера 502С, где активация 556 упорядочивания инструкций находится в каскаде планирования, установление или блокирование 557 упорядочивания инструкций находится в каскаде выборки и деактивация 558 упорядочивания инструкций находится в каскаде фиксации изменений. Следует понимать, что все это представляет собой несколько иллюстративных вариантов осуществления. Специалистам в данной области техники и тем, кто имеет выгоду от настоящего раскрытия, будет понятно, что альтернативно можно использовать различные другие каскады конвейера и/или комбинации каскадов.

На фиг. 6 показана блок-схема первого варианта осуществления подходящего формата 660 инструкции активации. Формат инструкции активации включает в себя код операции или опкод 662. Код операции может представлять собой множество разрядов или один или более полей, которые выполнены с возможностью идентификации инструкции и/или выполняемой операции. В некоторых вариантах осуществления формат инструкции активации может также опционально включать в себя один или более операндов 664 для точного определения или иным образом указания значения, которое будет использоваться для активации счетчика установления очередности исполнения инструкций. Один или более операндов могут включать в себя одно или более полей или разрядов. В некоторых вариантах осуществления один или более операндов могут явным образом точно определять или иным образом указывать на значение непосредственно внутри инструкции. Например, непосредственный операнд (например, 4-разрядный или 8-разрядный непосредственный операнд) позволяют явным образом точно определить значение или выбрать одно из многочисленных предварительно определенных значений. В некоторых вариантах осуществления значение может представлять собой число тактовых циклов для счета, хотя объем изобретения не ограничивается этим. В других вариантах осуществления один или более операндов могут указывать один или более регистров или другие ячейки памяти, которые используются для хранения значения. В других вариантах осуществления регистр или другая ячейка памяти, имеющая значение, может быть неявно определенной для инструкции вместо того, чтобы быть точно определенной.

На фиг. 7А показана блок-схема второго варианта осуществления подходящего формата 760 инструкции активации. В некоторых вариантах осуществления формат инструкции активации может опционально включать в себя префикс 766 для указания того, что инструкция является инструкцией активации для активации установления очередности исполнения инструкций. Формат инструкции активации также включает в себя код операции или опкод 761. В некоторых вариантах осуществления код операции позволяет идентифицировать то, что инструкция и/или операция, которая будет выполняться, отличается от активации установления очередности исполнения инструкций, которая является функцией префикса. Скорее всего, посредством примера, код операции показывает арифметическую операцию, логическую операцию, доступ к памяти или другой тип инструкции/операции (например, упакованную операцию умножения, операцию логического сдвига и т.д.). В некоторых вариантах осуществления префикс можно добавить к всевозможным типам арифметических операций, логических операций, доступа к памяти или других инструкций и/или кодов операций для того, чтобы добавить функциональные возможности активации очередности исполнения инструкций и сделать инструкции двойного назначения. В некоторых вариантах осуществления формат инструкции активации может также опционально включать в себя один или более операндов 764 для точного определения или иным образом указания значения, которое будет использоваться для активации счетчика установления очередности исполнения инструкций. Различные опции, ранее описанные для фиг. 6, также подходят для этого варианта осуществления. В некоторых вариантах осуществления, например, в зависимости от конкретного кода операции, формат инструкции активации может опционально включать в себя нулевые или с большим значением другие операнды 768 для реализации функциональных возможностей и/или операции, связанной с кодом операции.

На фиг. 7В показана блок-схема варианта осуществления подходящего формата 770 инструкции установления. В некоторых вариантах осуществления формат инструкции установления может опционально включать в себя префикс 772 для указания того, что инструкция является инструкцией установления для установления очередности исполнения инструкций. Формат инструкции установления также включает в себя код операции или опкод 774. В некоторых вариантах осуществления код операции позволяет идентифицировать то, что инструкция и/или операция, которая будет выполняться, отличается от установления очередности исполнения инструкций, которая является функцией префикса. Скорее всего, посредством примера, код операции может показывать арифметическую операцию, логическую операцию, доступ к памяти или другой тип инструкции/операции. В некоторых вариантах осуществления префикс можно добавлять к всевозможным типам арифметических операций, логических операций, доступа к памяти или к другим инструкциям и/или кодам операций для того, чтобы добавить функциональные возможности установления очередности исполнения инструкций и сделать инструкции двойного назначения. В некоторых вариантах осуществления, например, в зависимости от конкретного кода операции, формат инструкции установления может опционально включать в себя нулевые или с более высоким значением другие операнды 776 для реализации функциональных возможностей и/или операции, связанной с кодом операции.

Следует понимать, что форматы, показанные на фиг. 6 и фиг. 7А-В, являются всего лишь несколькими примерами подходящих форматов. Другие подходящие форматы инструкции можно опционально добавить в дополнительным операнды, поля и т.д. Более того, не требуется иллюстрированный порядок/размещение полей, а скорее всего можно опционально переупорядочить, разбить на части многочисленные поля, поля можно объединить и т.д. Дополнительно, поля не должны включать в себя непрерывные последовательности разрядов, а скорее всего могут включать в себя прерывистые или разделенные разряды.

Примерные архитектуры ядер, процессоры и архитектуры компьютеров

Ядра процессора можно реализовать различным образом для различных целей и в различных процессорах. Например, реализации таких ядер могут включать в себя: 1) ядро исполнения инструкций без изменения их очередности общего назначения, предназначенное для вычислений общего назначения; 2) высокопроизводительное ядро с изменением очередности исполнения инструкций общего назначения, предназначенное для вычислений общего назначения; 3) ядро специального назначения, предназначенное в основном для графики и/или научных вычислений (требующих высокой производительности). Реализации различных процессоров могут включать в себя: 1) ЦПУ, включающее в себя одно или более ядер с изменением очередности исполнения инструкций общего назначения, предназначенных для вычислений общего назначения и/или одно или более ядер без изменения очередности исполнения инструкций, предназначенных для вычисления общего назначения; и 2) сопроцессор, включающий в себя одно или более ядер специального назначения, предназначенных в основном для графики и/или научных (производственных) вычислений. Такие различные процессоры приводят к различным архитектурам компьютерных систем, которые могут включать в себя: 1) сопроцессор на отдельном кристалле относительно ЦПУ; 2) сопроцессор на отдельном кристалле в одном и том же корпусе, как и ЦПУ; 3) сопроцессор на одинаковом кристалле, как и ЦПУ (в этом случае, такой сопроцессор иногда упоминается как логическая схема специального назначения, такая как встроенная графика и/или логическая схема для научных вычислений (требующих высокой производительности), или как ядра специального назначения); и 4) система на кристалле, которая может включать в себя на том же самом кристалле описанное ЦПУ (иногда упоминается как ядро(а) приложений или процессор(ы) приложений), вышеописанный сопроцессор и дополнительные функциональные возможности. Примерная архитектура ядер описана ниже после описания примерных процессоров и архитектур компьютеров.

Примерные архитектуры ядер

Блок-схема ядра исполнения инструкций с и без изменения их очередности

На фиг. 8А показана блок-схема, иллюстрирующая как примерный конвейер исполнения инструкций без изменения их очередности и примерное переименование регистров, так и конвейер с изменением очередности выдачи/исполнения инструкций согласно вариантам осуществления изобретения. На фиг. 8В показана блок-схема, иллюстрирующая как примерный вариант осуществления ядра архитектуры исполнения инструкций без изменения их очередности и примерное переименование регистров, так и ядро архитектуры с изменением очередности выдачи/исполнения инструкций, которое будет включено в процессор согласно вариантам осуществления изобретения. Прямоугольники, показанные сплошной линией на фиг. 8А-В, иллюстрируют конвейер исполнения инструкций без изменения их очередности и ядро с изменением очередности исполнения инструкций, при этом опциональное добавленные прямоугольники, показанные пунктирной линией, иллюстрируют переименование регистров, конвейер с изменением очередности выдачи/исполнения инструкций и ядро. Учитывая, что аспект, связанный с исполнением инструкций без изменения их очередности, представляет собой подмножество аспектов, связанных с исполнением инструкций с изменением их очередности, ниже будет описан аспект, связанный с исполнением инструкций с изменением их очередности.

На фиг. 8А конвейер 800 процессора включает в себя этап 802 выборки, этап 804 декодирования длины, этап 806 декодирования, этап 808 выделения, этап 810 переименования, этап 812 планирования (также известный как этап отправки или выдачи), этап 814 считывания регистра/памяти, этап 816 исполнения, этап 818 записи/перезаписи памяти, этап 822 обработки исключений и этап 824 фиксации изменений.

На фиг. 8В показано ядро 890 процессора, включающее в себя блок 830 препроцессора, соединенный с исполнительным блоком 850, и они оба соединены с блоком 870 памяти. Ядро 890 может представлять собой ядро с сокращенным набором инструкций (RISC), ядро с полным набором инструкций (CISC), ядро с очень длинным словом инструкции (VLIW) или гибридный или альтернативный тип ядра. В качестве еще одной опции, ядро 890 может представлять собой ядро специального назначения, такое, например, как ядро сети или связи, механизм сжатия, ядро сопроцессора, ядро блока обработки компьютерной графики общего назначения (GPGPU), ядро графики и т.п.

Блок 830 препроцессора включает в себя блок 832 предсказания ветвлений, соединенный с блоком 834 кэш-памяти инструкций, который соединен с буфером 836 быстрого преобразования адреса инструкции (TLB), который соединен с блоком 838 выборки инструкций, который соединен с блоком 840 декодирования. Блок 840 декодирования (или декодер) может декодировать инструкции и вырабатывать в виде выходного сигнала одну или более микроопераций, точки входа в микрокод, микроинструкции, другие инструкции или другие сигналы управления, из которых декодируют, или которые иным образом отражают, или из которых получаются первоначальные инструкции. Блок 840 декодирования можно реализовать с использованием всевозможных механизмов. Примеры подходящих механизмов включают в себя, но не ограничиваются ими, таблицы поиска, аппаратные реализации, программируемые логические матрицы (PLA), постоянные запоминающие устройства (ROM) микрокода и т.д. В одном варианте осуществления ядро 890 включают в себя ROM микрокода или другой носитель, который хранит микрокод для некоторых макроинструкций (например, в блоке 840 декодирования или иным образом внутри блока 830 препроцессора). Блок 840 декодирования соединен с блоком 852 переименования/выделения в исполнительном блоке 850.

Исполнительный блок 850 включает в себя блок 852 переименования/выделения, соединенный с блоком 854 завершения, и набор из одного или более блоков 856 планировщика. Блок(и) 856 планировщика представляет(ют) собой любое число различных планировщиков, включая станции резервирования, центральное окно инструкции и т.д. Блок(и) 856 планировщика соединены с блоком(ами) 858 файла(ов) физических регистров. Каждый из блоков 858 файла(ов) физических регистров представляет собой один или более файлов физических регистров, некоторые из которых хранят один или более различных типов данных, такие как скалярное целое число, скалярная плавающая точка, упаковало целое число, упакованная плавающая точка, векторное целое число, векторная плавающая точка, статус (например, указатель инструкции, который представляет собой адрес следующей инструкции, которая будет исполнена), и т.д. В одном варианте осуществления блок(и) 858 файла(ов) физических регистров содержит блок векторных регистров, блок регистров маски записи и блок скалярных регистров. Блоки регистров могут предусматривать архитектурные векторные регистры, векторные регистры маски и регистры общего назначения. Блок(и) 858 файла(ов) физических регистров перекрывается(ются) блоком 854 завершения для иллюстрации различных способов, которыми можно реализовать переименование регистров и исполнение инструкций с изменением их очередности (например, использование буфера(ов) переупорядочения и файла(ов) регистров завершения; использование будущего(их) файл(ов), буфера(ов) истории и файла(ов) регистров завершения; использование карт регистров и группы регистров и т.д.). Блок 854 завершения и блок(и) 858 файла(ов) физических регистров соединены с кластером(ами) 860 исполнения. Кластер(ы) 860 исполнения включает в себя набор из одного или более блоков 862 исполнения и набор из одного или более блоков 864 доступа к памяти. Блоки 862 исполнения могут выполнять различные операции (например, сдвиг, сложение, вычитание, умножение) и над различными типами данных (например, над скалярной плавающей точкой, упакованным целым числом, упакованной плавающей точкой, векторным целым числом, векторной плавающей точкой). Хотя некоторые варианты осуществления могут включать в себя ряд блоков исполнения, выделенных для специфических функций или набора функций, другие варианты осуществления могут включать в себя только один блок исполнения или многочисленные блоки исполнения, которые все вместе выполняют все функции. Блок(и) 856 планировщика, блок(и) 858 файла(ов) физических регистров и кластер(ы) 860 исполнения по возможности показаны как многочисленные, и так как некоторые варианты осуществления предусматривают создание отдельных конвейеров для некоторых типов данных/операций (например, конвейер для скалярных целых чисел, конвейер для скалярной плавающей точки/упакованного целого числа плавающей точки/упакованной плавающей точки/векторного целого числа/векторной плавающей точки и/или конвейер доступа к памяти, каждый из которых имеет свой собственный блок 856 планировщика, блок файла(ов) физических регистров и/или кластер исполнения - и в случае отдельного конвейера доступа к памяти реализованы некоторые варианты осуществления, в которых только кластер исполнения этого конвейера имеет(ют) блок(и) доступа к памяти 864), следует также понимать, что в тех случаях, когда используются отдельные конвейеры, один или более из этих конвейеров может изменять очередность выдачи/исполнения инструкций, а остальные не могут изменять их очередность.

Набор блоков 864 доступа к памяти соединен с блоком 870 памяти, который включает в себя блок 872 TLB данных, соединенный с блоком 874 кэш-памяти данных, соединенным с блоком 876 кэш-памяти уровня 2 (L2). В одном примерном варианте осуществления блоки 864 доступа к памяти могут включать в себя блок загрузки, блок адреса хранения и блок данных хранения, каждый из которых соединен с блоком 872 TLB данных в блоке 870 памяти. Блок 834 кэш-памяти инструкций опционально соединен с блоком 876 кэш-памяти уровня 2 (L2) в блоке 870 памяти. Блок 876 кэш-памяти L2 соединен с одним или более другими уровнями кэш-памяти и, в конечном счете, с основной памятью.

Посредством примера, при примерном переименовании регистра архитектура ядра с изменением очередности выдачи/исполнения инструкций позволяет реализовать конвейер 800 следующим образом: 1) блок 838 выборки инструкций выполняет этапы 802 и 804 выборки и декодирования длины; 2) блок 840 декодирования выполняет этап 806 декодирования; 3) блок 852 переименования/выделения выполняет этап 808 выделения и этап 810 переименования; 4) блок(и) 856 планировщика выполняет этап 812 планирования; 5) блок(и) 858 файла(ов) физических регистров и блок 870 памяти выполняет этап 814 считывания регистра/считывания памяти; кластер 860 исполнения выполняет этап 816 исполнения; 6) блок 870 памяти и блок(и) 858 файла(ов) физических регистров выполняет этап 818 перезаписи/записи в память; 7) различные блоки могут быть включены в этап 822 обработки исполнения и 8) блок 854 завершения и блок(и) 858 файла(ов) физических регистров выполняет(ют) этап 824 фиксации изменений.

Ядро 890 позволяет поддерживать один или более наборов инструкций (например, набор инструкций х86 (с некоторыми расширениями, которые были добавлены с помощью более новых версий); набор инструкций MIPS от MIPS Technologies of Sunnyvale, CA; набор инструкций ARM (с опциональными дополнительными расширениями, такими как NEON) от ARM Holdings of Sunnyvale, CA), включая в себя инструкцию(и), описанную(ые) в данном документе. В одном варианте осуществления ядро 890 включают в себя логику для поддержки расширения набора инструкций для упакованных данных (например, AVX1, AVX2), тем самым позволяя выполнять операции, которые используются многими мультимедийными приложениями, с использованием упакованных данных.

Следует понимать, что ядро может поддерживать многопоточность (исполняя два или более параллельных наборов операций или потоков), и ее можно выполнить множеством способов, включающих в себя многопоточность с квантованием по времени, одновременную многопоточность (где одно физическое ядро предусматривает логическое ядро для каждого из потоков, причем физическое ядро одновременно выполняет многопоточность данных) или их комбинации (например, выборку с квантованием по времени, и декодирование и одновременную многопоточную обработку данных, соответственно, как, например, в технологии Intel®Hyperthreading).

Хотя переименование регистров описано в контексте с изменением очередности исполнения инструкций, следует понимать, что переименование регистров можно использовать в архитектуре без изменения очередности исполнения инструкций. Хотя иллюстрированный вариант осуществления процессора также включает в себя отдельные блоки 834/874 кэш-памяти данных и инструкций и совместно используемый блок 876 кэш-памяти L2, альтернативные варианты осуществления могут иметь единственную внутреннюю кэш-память для обеих инструкций и данных, таких, например, как внутренняя кэш-память Уровня 1 (L1) или многочисленные уровни внутренней кэш-памяти. В некоторых вариантах осуществления система может включать в себя комбинацию из внутренней кэш-памяти и внешней кэш-памяти, которая является внешней по отношению к ядру и/или процессору. В качестве альтернативы, каждая из кэш-памяти может быть внешней по отношению к ядру и/или процессору.

Конкретная примерная архитектура ядра исполнения инструкций без изменения их очередности

Фиг. 9А-В иллюстрируют блок-схему более конкретной примерной архитектуры ядра исполнения инструкций без изменения их очередности, причем ядро будет иметь один из нескольких логических блоков (в том числе другие ядра того же самого типа и/или различных типов) в кристалле. Логические блоки поддерживают связь через широкополосную сеть межсоединений (например, кольцевую сеть) с некоторой логикой с фиксированной функцией, интерфейсы ввода-вывода памяти и другую необходимую логику ввода/вывода в зависимости от приложения.

На фиг. 9А показана блок-схема однопроцессорного ядра наряду с его подсоединением к накристальной сети 902 межсоединений и с его локальным подмножеством 904 кэш-памяти Уровня 2 (L2), согласно вариантам осуществления изобретения. В одном варианте осуществления декодер 900 инструкций поддерживает набор инструкций х86 с расширением набора инструкций для упакованных данных. Кэш-память 906 L1 позволяет обеспечить доступам с малой задержкой к кэш-памяти в скалярном и векторном блоках. Хотя в одном варианте осуществления (для упрощения конструкций) скалярный блок 908 и векторный блок 910 используют отдельные наборы регистров (соответственно, скалярные регистры 912, и векторные регистры 914) и данные, передаваемые между ними, записываются в память и затем повторно считываются в/из кэш-памяти 906 уровня 1 (L1), альтернативные варианты осуществления изобретения могут использовать различные подходы (например, использовать один набор регистров или включать в себя канал связи, который позволяет обмениваться данными между двумя файлами регистров без записи и повторного считывания).

Локальное подмножество 904 кэш-памяти L2 является частью глобальной кэш-памяти L2, которое разделено на отдельные локальные подмножества, по одному на ядро процессора. Каждое ядро процессора имеет путь прямого доступа к своему собственному локальному подмножеству 904 кэш-памяти L2. Данные, считанные ядром процессора, сохраняются в своем подмножестве 904 кэш-памяти L2, и к ним можно получить быстрый доступ параллельно с другими ядрами процессора, которые имеют доступ к своим собственным локальным подмножествам кэш-памяти L2. Данные, считанные ядром процессора, сохраняются в своем собственном подмножестве 904 кэш-памяти L2 и, при необходимости, заполняются из других подмножеств. Кольцевая сеть обеспечивает связность для совместно используемых данных. Кольцевая сеть является двунаправленной, позволяя агентам, таким как ядра процессора, кэш-память L2 и другие логические блоки, поддерживать связь друг с другом в пределах чипа. Каждый кольцевой канал передачи данных имеет ширину 1012 разрядов в каждом направлении.

На фиг. 9В показан расширенный вид части ядра процессора (фиг. 9А) согласно вариантам осуществления изобретения. На фиг. 9В показана часть кэш-память 906А данных L1 кэш-памяти 904 L1, а также более подробный вид, относящийся к векторному блоку 910 и векторным регистрам 914. В частности, векторный блок 910 представляет собой блок векторной обработки с шириной 16 разрядов (VPU) (смотри АЛУ 928 с шириной 16 разрядов), который исполняет одну или более инструкций для целых чисел, чисел с плавающей точкой с одинарной точностью и чисел с плавающей точкой двойной точности. VPU поддерживает свизлинг входов регистра с помощью блока 920 преобразования ссылок, преобразование чисел с помощью блоков 922А-В преобразования чисел и репликацию с помощью блока 924 репликации на входе памяти. Регистры 926 маски записи обеспечивают предсказание результирующих записей векторов.

Процессор с встроенным контроллером памяти и графикой

На фиг. 10 показана блок-схема процессора 1000, который может иметь больше одного ядра, может иметь встроенный контроллер памяти и может иметь встроенную графику согласно вариантам осуществления изобретения. Прямоугольники, показанные на фиг. 10 сплошной линией, иллюстрируют процессор 1000 с одним ядром 1002А, системный агент 1010, набор из одного или более блоков 1016 контроллера шины, в то время как опциональное добавление с прямоугольниками, показанными штриховыми линиями, иллюстрирует альтернативный процессор 1000 с многочисленными ядрами 1002A-N, набор из одного или более встроенных блоков 1014 контроллера памяти в блоке 1010 системного агента и логическую схему 1008 специального назначения.

Таким образом, различные реализации процессора 1000 могут включать в себя: 1) ЦПУ с логической схемой 1008 специального назначения, которая представляет собой встроенную графику и/или логическую схему для научных вычислений (требующих высокой производительности) (которая может включать в себя одно или более ядер), и ядра 1002A-N, которые представляют собой одно или более ядер общего назначения (например, ядра без изменения очередности исполнения инструкций общего назначения, ядра с изменением очередности исполнения инструкций общего назначения и их комбинации); 2) сопроцессор с ядрами 1002A-N, который представляет собой большое количество ядер специального назначения, предназначенных в основном для графики и/или научных вычислений (требующих высокой производительности), и 3) сопроцессор с ядрами 1002A-N, который представляет собой большое количество ядер без изменения очередности исполнения инструкций. Таким образом, процессор 1000 может представлять собой процессор общего назначения, сопроцессор или процессор специального назначения, такой, например, как сетевой или связной процессор, механизм сжатия, графический процессор, GPGPU (блок обработки компьютерной графики общего назначения), высокопроизводительный сопроцессор с многочисленными встроенными ядрами (MIC) (включающий в себя 30 или более ядер), встроенный процессор или т.п. Процессор можно реализовать на одном или более чипах. Процессор 1000 может быть частью и/или можно реализовать на одной или более подложках с использованием любого числа технологий обработки, таких, например, как BiCMOS, CMOS или NMOS.

Иерархия памяти включает в себя один или более уровней кэш-памяти внутри ядер, набор или один или более совместно используемых блоков 1006 кэш-памяти и внешнюю память (не показано), соединенную с набором блоков 1014 контроллера со встроенной памятью. Набор совместно используемых блоков 1006 кэш-памяти может включать в себя один или более кэш-памяти среднего уровня, таких как уровня 2 (L2), уровня 3 (L3), уровня 4 (L4) или других уровней кэш-памяти, кэш-память последнего уровня (LLC) и/или их комбинации. Хотя в одном варианте осуществления блок 1012 межсоединений, основанных на кольце, осуществляет межсоединение логической схемы 1008 со встроенной графикой, набор совместно используемых блоков 1006 кэш-памяти и блок 1010 системного агента/блок(и) 1014 контроллера со встроенной памятью, альтернативные варианты осуществления позволяют использовать любое количество хорошо известных технологий для межсоединения таких блоков. В одном варианте осуществления между одним или более блоками 1006 кэш-памяти и ядрами 1002A-N поддерживается связность.

В некоторых вариантах осуществления один или более ядер 1002A-N выполнены с возможностью многопоточной обработки данных. Системный агент 1010 включает в себя эти компоненты, координирующие и приводящие в действие ядра 1002A-N. Блок 1010 системного агента может включать в себя, например, блок управления мощностью (PCU) и блок отображения. PCU может включать в себя логическую схему и компоненты, необходимые для регулировки состояния мощности ядер 1002A-N и логической схемы 1008 со встроенной графикой. Блок отображения предназначен для возбуждения одного или более дисплеев, соединенных внешним образом.

Ядра 1002A-N могут быть однородными или неоднородными с точки зрения набора инструкций архитектуры; то есть два или более ядер 1002A-N можно выполнить с возможностью исполнения одного и того же набора инструкций, в то время как другие можно выполнить с возможностью исполнения только подмножества из этого набора инструкций или другого набора инструкций.

Примерные архитектуры компьютеров

На фиг. 11-14 представлены блок-схемы примерных архитектур компьютеров. Подходят также и другие конструкции и конфигурации, которые известны в технике, для портативных персональных компьютеров типа "лэптоп", настольных персональных компьютеров, карманных компьютеров, персональных цифровых помощников, инженерных рабочих станций, серверов, сетевых устройств, сетевых концентраторов, переключателей, встроенных процессоров, процессоров цифровых сигналов (DSP), графических устройств, видеоигровых устройств, телевизионных приставок, микроконтроллеров, сотовых телефонов, портативных мультимедийных плееров, переносных устройств и различных других электронных устройств. В общем, подходит огромное множество систем или электронных устройств, способных к объединению процессора и/или другой исполнительной логической схемы, как раскрыто в данном документе.

Обратимся теперь к фиг. 11, на которой показана блок-схема системы 1100 в соответствии с одним вариантом установления настоящего изобретения. Система 1100 может включать в себя один или более процессоров 1110, 1115, которые соединены с концентратором 1120 контроллеров. В одном варианте осуществления концентратор 1120 контроллеров включает в себя концентратор контроллеров памяти графических данных (GMCH) 1190 и концентратор ввода/вывода (IOH) 1150 (который может располагаться на отдельном чипе); GMCH 1190 включает в себя память и графические контроллеры, к которым подсоединена память 1140 и сопроцессор 1145; IOH 1150 подсоединяет устройства 1160 ввода/вывода (I/O) к GMCH 1190. В качестве альтернативы, память и графические контроллеры по одному или все вместе интегрированы внутри процессора (как описано в данном документе), память 1140 и сопроцессор 1145 соединены непосредственно с процессором 1110, и концентратор 1120 контроллеров в виде одного чипа соединен с IOH 1150.

Опциональный тип дополнительных процессоров 1115 обозначен на фиг. 11 пунктирными линиями. Каждый процессор 1110, 1115 может включать в себя одно или более процессорных ядер, описанных в данном документе, и может представлять собой некоторую версию процессора 1000.

Память 1140 может представлять собой, например, динамическое запоминающее устройство (DRAM), память на фазовых переходах (РСМ) или их комбинацию. Согласно по меньшей мере одному варианту установления концентратор 1120 контроллеров поддерживает связь с процессором(ами) 1110, 1115 через многоточечную шину, такую как системная шина (FSB), интерфейс "точка-точка", такой как межсоединение QuickPath (QPI) или аналогичное соединение 1195.

В одном варианте осуществления сопроцессор 1145 представляет собой процессор специального назначения, такой, например, как высокопроизводительный процессор MIC, сетевой или связной процессор, механизм сжатия, графический процессор, GPGPU, встроенный процессор или т.п. В одном варианте осуществления концентратор 1120 контроллеров может включать в себя встроенный графический ускоритель.

Существует множество различий между физическими ресурсами 1110, 1115 с точки зрения спектра метрик эксплуатационных характеристик, включающих в себя архитектурные, микроархитектурные, тепловые характеристики, характеристики потребляемой мощности и т.п.

В одном варианте осуществления процессор 1110 исполняет инструкции, которые управляют операциями обработки данных общего типа. Встроенные внутри инструкции могут представлять собой инструкции сопроцессора. Процессор 1110 распознает эти инструкции сопроцессора в виде типа, который должен исполнять присоединенный сопроцессор 1145. Соответственно, процессор 1110 подает эти инструкции сопроцессора (или сигналы управления, представляющие собой инструкции сопроцессора) по шине сопроцессора или другому межсоединению в сопроцессор 1145. Сопроцессор(ы) 1145 принимает(ют) и исполняет(ют) принятые инструкции сопроцессора.

Обратимся теперь к фиг. 12, на которой показана блок-схема первой более конкретной примерной системы 1200 в соответствии с вариантом установления настоящего изобретения. Как показано на фиг. 12, многопроцессорная система 1200 представляет собой систему двухточечных межсоединений и включает в себя первый процессор 1270 и второй процессор 1280, соединенный через двухточечное межсоединение 1250. Каждый из процессоров 1270 и 1280 может представлять собой некоторую версию процессора 1000. В одном варианте осуществления изобретения процессоры 1270 и 1280 представляют собой, соответственно, процессоры 1110 и 1115, тогда как сопроцессор 1238 представляет собой сопроцессор 1145. В другом варианте осуществления процессоры 1270 и 1280 представляют собой, соответственно, сопроцессор 1145 процессора 1110.

Процессоры 1270 и 1280 показаны как включающие в себя блоки 1272 и 1282 контроллеров со встроенной памяти (IMC), соответственно. Процессор 1270 также включает в себя в качестве части двухточечных (Р-Р) интерфейсов 1276 и 1278 своих блоков контроллера шины; аналогичным образом второй процессор 1280 включает в себя Р-Р интерфейсы 1286 и 1288. Процессоры 1270, 1280 могут осуществлять обмен информацией через двухточечный (Р-Р) интерфейс 1250 с использованием схем 1278, 1288 Р-Р интерфейса. Как показано на фиг. 12, IMC 1272 и 1282 подсоединяют процессоры к соответствующей памяти, а именно к памяти 1232 и памяти 1234, которые могут представлять собой части основной памяти, локально присоединенной к соответствующим процессорам.

Процессоры 1270, 1280 могут по отдельности осуществлять обмен информацией с набором 1290 микросхем через отдельные Р-Р интерфейсы 1252, 1254 с использованием схем 1276, 1294, 1286, 1298 двухточечных интерфейсов. Набор 1290 микросхем может опционально осуществлять обмен информацией с сопроцессором 1238 через высокопроизводительный интерфейс 1239. В одном варианте осуществления сопроцессор 1238 представляет собой процессор специального назначения, такой, например, как высокопроизводительный процессор MIC, сетевой или связной процессор, механизм сжатия, графический процессор, GPGPU, встроенный процессор или т.п.

Совместно используемая кэш-память (не показана) может быть включена в процессор или за пределами обоих процессоров, еще соединенных с процессорами через Р-Р межсоединение таким образом, чтобы информацию о локальной кэш-памяти каждого или обоих процессоров можно было сохранить в совместно используемой кэш-памяти, если процессор находится в режиме малого электропотребления.

Набор 1290 микросхем может быть соединен с первой шиной 1216 через интерфейс 1296. В одном варианте осуществления первая шина 1216 может представлять собой шину межсоединения периферийных компонентов (PCI) или шину, такую как шина PCI Express, или другую шину межсоединения I/O третьего поколения, хотя объем настоящего изобретения не ограничивается этим.

Как показано на фиг. 12, различные устройства 1214 I/O могут быть связаны с первой шиной 1216 наряду с межшинным мостом 1 218, который соединяет первую шину 1216 со второй шиной 1220. В одном варианте осуществления один или более дополнительных процессоров 1215, таких как сопроцессоры, высокопроизводительные процессоры MIC, ускорители GPGPU (такие, например, как графические ускорители или блоки обработки цифровых сигналов (DSP)), программируемые вентильные матрицы, или любой другой процессор соединены с первой шиной 1216. В одном варианте осуществления вторая шина 1220 может представлять собой шину с малым числом выводов (LPC).

Различные устройства могут быть соединены со второй шиной 1220, в том числе, например, с клавиатурой и/или мышью 1222, устройствами 1227 связи или блоком 1228 памяти, таким как накопитель на дисках или другое устройство массовой памяти, которое может включать в себя инструкции/код и данные 1230 согласно одному варианту установления. Кроме того, блок 1224 ввода-вывода аудио может быть соединен со второй шиной 1220. Следует отметить, что возможны и другие архитектуры. Например, вместо двухточечной архитектуры, показанной на фиг. 12, в системе может быть реализована многоточечная шина или другая такая архитектура.

Обратимся теперь к фиг. 13, на которой показана блок-схема второй более конкретной примерной системы 1300 в соответствии с вариантом установления настоящего изобретения. Одинаковые элементы, показанные на фиг. 12 и 13, обозначены одинаковыми ссылочными позициями, и некоторые аспекты, показанные на фиг. 12, были опущены на фиг. 13 во избежание излишнего усложнения других аспектов, показанных на фиг. 13.

На фиг. 13 показаны процессоры 1270, 1280, которые могут включать в себя встроенную память и I/O управляющую логическую схему ("CL") 1272 и 1282, соответственно. Таким образом, CL 1272, 1282 включают в себя блоки контроллера со встроенной памятью и включают в себя I/O управляющую логическую схему. На фиг. 13 показано, что не только память 1232, 1234 соединена с CL 1272, 1282, но также, что устройства 1314 I/O также соединены с управляющей логической схемой 1272, 1282. Унаследованные устройства I/O 1315 подсоединяются к набору 1290 микросхем.

Обратимся теперь к фиг. 14, на которой показана блок-схема SoC 1400 в соответствии с вариантом установления настоящего изобретения. Аналогичные элементы, показанные на фиг. 10, обозначены одинаковыми ссылочными позициями. Кроме того, прямоугольники, показанные пунктирными линиями, имеют дополнительные признаки на более продвинутых SoC. На фиг. 14 блок(и) 1402 межсоединений подсоединен к: процессору 1410 приложений, который включает в себя набор из одного или более ядер 202A-N, и блок(и) 1006 совместно используемой кэш-памяти; блоку 1010 системного агента; блоку(ам) 1016 контроллера шины; блоку(ам) 1014 контроллера со встроенной памятью; набору или одному или более сопроцессорам 1420, которые могут включать в себя встроенную графическую логическую схему, процессор для обработки изображений, процессор дли обработки аудио и видеопроцессор; блоку 1430 статического оперативного запоминающего устройства (SRAM); блоку 1432 прямого доступа к памяти (DMA) и блоку 1440 отображения для подсоединения к одному или более внешним дисплеям. В одном варианте осуществления сопроцессор(ы) 1420 включает в себя процессор специального назначения, такой, например, как сетевой или связной процессор, механизм сжатия, GPGPU, высокопроизводительный процессор MIC, встроенный процессор и т.п.

Варианты механизмов, раскрытые в данном документе, можно реализовать в виде аппаратных средств, программного обеспечения, программно-аппаратных средств или комбинации таких методов реализации. Варианты осуществления изобретения можно реализовать в виде компьютерных программ или программного кода, исполняемого на программируемых системах, содержащих по меньшей мере один процессор, систему памяти (включающей в себя энергозависимую и энергонезависимую память и/или элементы памяти), по меньшей мере одно устройство ввода и по меньшей мере одно устройство вывода.

Код программы, такой как код 1230, иллюстрированный на фиг. 12, можно применить к входным инструкциям для того, чтобы выполнить функции, описанные в данном документе, и выработать выходную информацию. Выходную информацию можно применить известным способом к одному или более устройствам вывода. В целях этого приложения, система обработки включает в себя любую систему, которая имеет процессор, такой, например, как процессор цифровых сигналов (DSP), микроконтроллер, специализированная интегральная схема (ASIC) или микропроцессор.