Уровень техники

Современные микропроцессоры сформированы из различных каскадов, которые принимают инструкции, выполняют инструкции и предоставляют результаты инструкций. Множество современных архитектур основаны на воплощении, выполняемом не по порядку (OOO, ВНП), в котором инструкции могут быть выполнены не по порядку, и результаты затем фиксируют в архитектурном состоянии процессора, выполняющего инструкции по порядку.

Для реализации такой операции, выполняемой не по порядку, конвейер процессора может быть сегментирован на различные этапы. При окончании обработки инструкций на таких этапах может быть включен этап окончания инструкции для подтверждения того, что результаты выполнения являются действительными, не являются умозрительными или основанными на неправильных данных, и что при этом не возникли какие-либо ошибки или исключения. В архитектурах множества процессоров, в каждом цикле окончания инструкции вся логика окончания инструкции работает так, что все ассоциированные данные считывают из всех ассоциированных массивов, и для каждой инструкции запускают полную логику окончания инструкции. Все эти действия направлены на получение гарантированного сигнала, и выполнение операций, связанных с окончанием инструкции, которые включают в себя расчет события и установление приоритетов.

Однако в большинстве циклов не происходят каких-либо событий, и поэтому нет необходимости рассчитывать эти события. При этом происходит существенное потребление энергии, которая не требуется для правильной работы.

Краткое описание чертежей

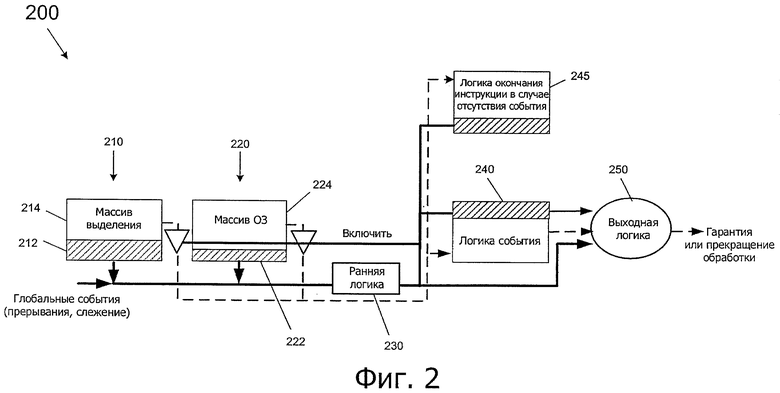

На фиг.1 показана блок-схема процессора в соответствии с одним вариантом воплощения настоящего изобретения.

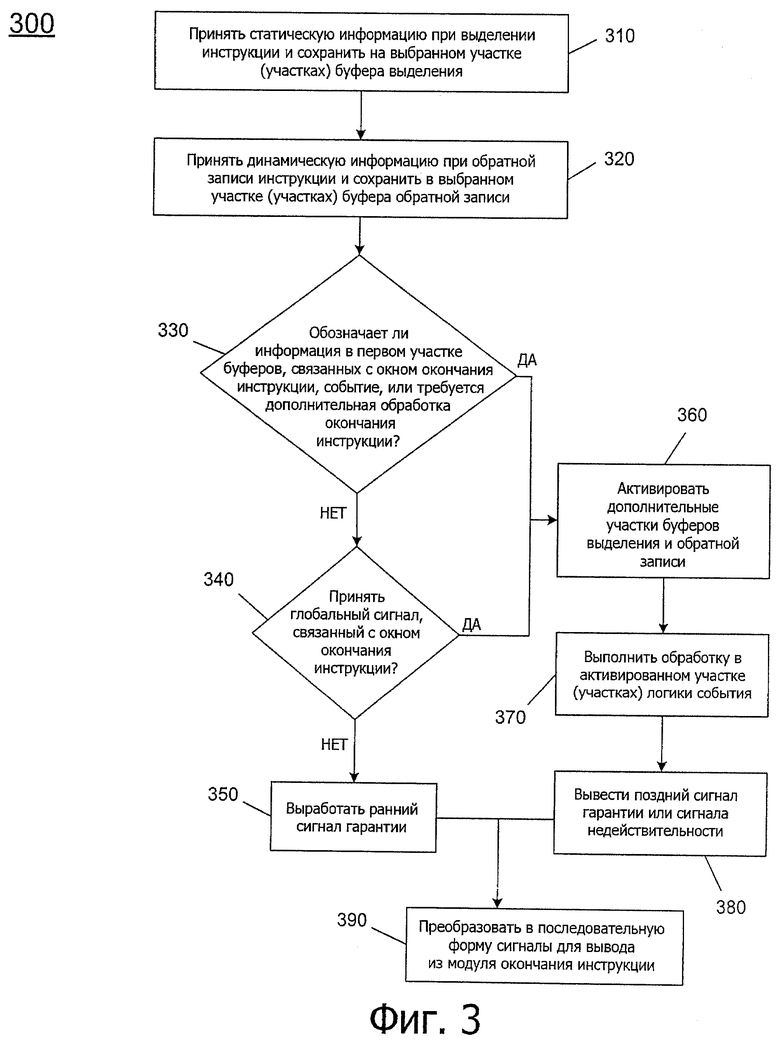

На фиг.2 показана блок-схема логики окончания инструкции в соответствии с одним вариантом воплощения настоящего изобретения.

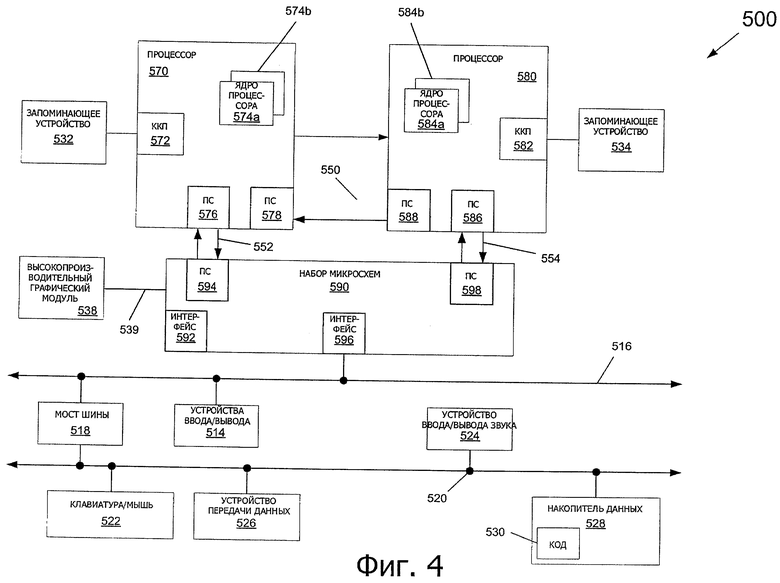

На фиг.3 показана блок-схема способа в соответствии с вариантом воплощения настоящего изобретения.

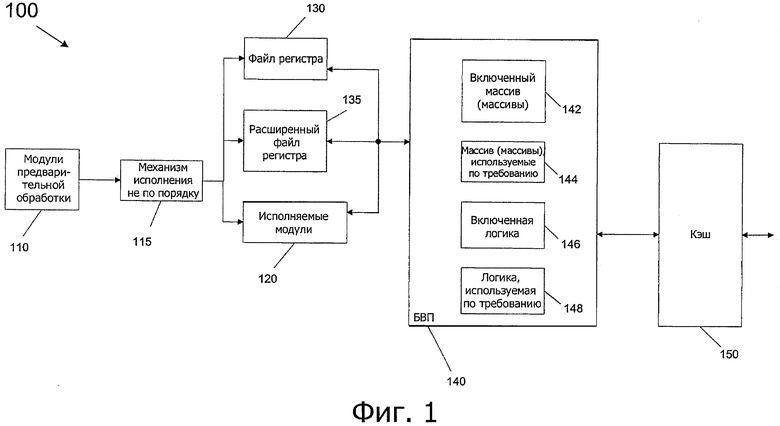

На фиг.4 показана блок-схема системы в соответствии с вариантом воплощения настоящего изобретения.

Подробное описание изобретения

В различных вариантах воплощения логикой окончания инструкции процессора можно управлять для обеспечения работы с учетом потребляемой энергии в результате разделения на части различных ресурсов окончания инструкции таким образом, что только минимальное количество этих ресурсов будет получать энергию в течение значительных частей операции. При этом различные массивы, буферы и так далее, и логические схемы могут быть разделены так, чтобы они соответствовали такой работе. В то время как варианты воплощения, описанные здесь, представлены в контексте буфера восстановления последовательности (ROB, БВП), объем настоящего изобретения не ограничивается этим, и варианты воплощения можно использовать с различной логикой окончания инструкции, которая может присутствовать в данном процессоре.

Для обеспечения преимуществ, связанных с сохранением энергии, части таких массивов и логических схем, связанных с нормальными действиями при окончании инструкции, которые должны выполняться в каждом окне окончания инструкции, могут быть относительно малыми, так, чтобы потреблялась минимальная энергия. В отличие от этого, для относительно редких случаев, в которых требуется воплощать дополнительные расчеты, связанные с различными событиями, при окончании инструкций, могут получать питание более крупные массивы и логические схемы. Таким образом, требуемые операции могут быть выполнены в соответствии с необходимостью, в то время как для большей части операций окончания инструкций, питание должна получать только минимальная часть логической схемы окончания инструкций. Хотя здесь, в общем, описано окончание инструкций для инструкции, следует понимать, что в различных вариантах воплощения инструкции могут называться как, так называемые, микрооперации (µop), в которых одиночная инструкция на уровне пользователя, например, макрокоманда может быть разбита на множество µор.

БВП выполняет управление, относящееся к окончанию инструкций, такое как обработка исключения, расчет указателя инструкции (например, EIP/UIP), расчет монитора рабочих характеристик (PMON, МОНРХ) и обновление регистра. Кроме детектирования ошибок, БВП выполняет другие нормальные задачи, относящиеся к выполнению окончания инструкции, когда ошибки не детектированы, и которые выполняют при окончании инструкции. Эти задачи включают в себя операции, выполняемые после действительного окончания инструкции, например записи новых выведенных промежуточных значений в регистры, которые не были переименованы, расчет битов состояния и обновление новых значений (таких, как биты разбиения данных, исключения команд и регистра состояния, исключения точности и так далее) и мониторы обновления рабочих характеристик. Схема вывода окончания инструкции с учетом потребляемой мощности, в соответствии с вариантом воплощения настоящего изобретения, позволяет избирательно управлять различными блоками, потребляющими много энергии в БВП, только когда это необходимо, на основе, по меньшей мере, частично, статической и динамической информации, получаемой, как на основании внешних, так и на основании внутренних показателей (относительно БВП).

Другими словами, задачи основного потока разработки при нормальном окончании инструкции, которые отбирают минимальное количество энергии, могут быть обработаны отдельными частями массивов и логических схем, оставляя редкие случаи, такие как обработка событий (например, ошибки, ловушки, исключения, прерывания), для обработки с более полными наборами частей таких массивов и логических схем, только когда это необходимо. Таким образом, специальные режимы, такие как МОНРХ, которые должны работать в среде с полными рабочими характеристиками, могут нормально работать, когда это необходимо, и обеспечивается экономия энергии, когда они не активны. Варианты воплощения, таким образом, могут обеспечивать большую ширину окончания инструкции, при частом выполнении непрерываемого окончания инструкций, путем уменьшения объема расчетов для реализации окончания инструкций.

Рассмотрим теперь фиг.1, на которой показана блок-схема процессора в соответствии с одним вариантом воплощения настоящего изобретения. Как показано на фиг.1, процессор 100 может представлять собой многоэтапный конвейерный процессор, выполняющий инструкции не по порядку. Процессор 100 показан в относительно упрощенном виде на фиг.1 для иллюстрации различных элементов, используемых совместно с операциями окончания инструкций с учетом потребляемой энергии, как будет описано ниже.

Как показано на фиг.1, процессор 100 включает в себя модули 110 предварительной обработки, которые можно использовать для выборки макрокоманд, предназначенных для выполнения, и подготовки их для последующего использования в процессоре. Например, модуль 110 предварительной обработки может включать в себя блок предварительной выборки инструкций, декодер инструкций и кэш отслеживания, вместе с накопителем микрокода, а также с накопителем µор. Блок предварительной выборки инструкций может выбирать макрокоманды из памяти и подавать их в декодер инструкций для декодирования их на примитивы, то есть µoр для выполнения процессором. Кэш отслеживания может принимать декодированные µор и собирать из них упорядоченные программные последовательности для сохранения в хранилище макрокода. Однако в случае сложных макрокоманд хранилище микрокода может предоставлять µop, необходимые для выполнения операции. Конечно, дополнительные компоненты и элементы могут быть воплощены в модулях 110 предварительной обработки.

Между модулями 110 предварительной обработки и исполнительными модулями 120 расположен механизм 115 ВНП, который можно использовать для приема микроинструкций и подготовки их к выполнению. Более конкретно, механизм 115 ВНП может включать в себя различные буферы для изменения порядка потока микроинструкций и выделения различных ресурсов, необходимых для исполнения, а также для обеспечения переименования логических регистров на ячейки памяти в пределах различных файлов регистров, например, в файле 130 регистра и в расширенном файле 135 регистра. Файл 130 регистра может включать в себя отдельные файлы регистра для операций с целыми числами и операций с плавающей запятой. Расширенный файл 135 регистра может обеспечивать место для сохранения модулей размером вектор, например, 256 или 512 бит на регистр.

Различные ресурсы могут присутствовать в исполнительных модулях 120, включающих в себя, например, различные логические модули, работающие с целыми числами, с плавающей запятой и типа "один поток команд - много потоков данных" (SIMD, ОКМД), среди других специализированных аппаратных средств. Результаты могут быть предоставлены в логическую схему окончания инструкции, а именно, в буфер 140 восстановления последовательности (БВП), который может работать с учетом потребляемой энергии. Более конкретно, БВП 140 включает в себя различные массивы и логические схемы для приема информации, связанной с выполняемыми инструкциями. БВП 140 затем проверяет эту информацию для определения, можно ли правомерно закончить инструкции и передать полученные в результате данные в архитектурное состояние процессора, или произошло одно или больше исключений, которые не позволяют правильно закончить инструкции. Конечно, БВП 140 может обрабатывать другие операции, связанные с окончанием инструкций, например, различные события и расчеты, описанные здесь.

Как показано на фиг.1, БВП 140 может включать в себя различные массивы, включающие в себя один или больше разрешенных массивов 142 и один или больше массивов 144, используемых по требованию. Разрешенные массивы могут всегда получать питание и могут включать в себя минимальное количество информации, связанной с инструкциями. Как будет подробно описано ниже, в одном конкретном варианте воплощения отдельные отделы массива выделения и массив обратной записи (WB, ОЗ), могут соответствовать разрешенному массиву 144. Аналогично, массив 144 по требованию может представлять части таких массивов, которые включают в себя дополнительную информацию, связанную с µop, и которые могут получать питание, только если это необходимо для обработки событий, связанных с данной инструкцией. Как, кроме того, показано на фиг.1, БВП 140 дополнительно включает в себя разрешенную логику 146. Такая разрешенная логика может быть всегда активной и может использоваться для обработки операций окончания нормальных инструкций. В отличие от этого, логика 148, выполняемая по требованию, может быть включена только, если это требуется для обработки событий, выходящих за пределы нормального окончания инструкций, таких как обработка ошибок, прерываний, ошибочных результатов прогнозирования разветвлений, отслеживание рабочих характеристик и обновление, и т.д. Как показано на фиг.1, БВП 140 соединен с кэш 150, который в одном варианте воплощения может представлять собой кэш низкого уровня (например, кэш L1), хотя объем настоящего изобретения не ограничивается этим. Кроме того, исполнительные модули 120 могут быть непосредственно соединены с кэш 150. Из кэш 150 может происходить обмен данными с кэш более высокого уровня, системным запоминающим устройством и т.д. Хотя в варианте воплощения, показанном на фиг.1, показан такой высокий уровень, следует понимать, что объем настоящего изобретения не ограничивается этим.

В ходе общей работы БВП определяет, требуются ли для µор в окне окончания инструкции считывание специфичного участка массивов БВП, или требуется включить специфические логические схемы (в случае, когда специфические ресурсы потребляют много энергии, и выполняют операции, выходящие за пределы нормального окончания инструкции). Такое определение может быть статически детектировано заранее во время выделения, или может детектироваться динамически по ОЗ. Например, если не детектированы никакие статические события (во время выделения) или динамические события (во время обратной записи (ОЗ)) нет необходимости активировать логические схемы события. Кроме того, если набор МОНРХ не активен, тогда это состояние можно детектировать статически по выделению, и данные, связанные с расчетом МОНРХ, не должны быть считаны во время окончания инструкции, и при этом не требуется, чтобы логическая схема, которая рассчитывает значения МОНРХ, была включена.

Если только специфичные операции не будут идентифицированы и специально включены, БВП обычно фокусируется на действиях основного потока обработки при нормальном окончании инструкции. Такая схема с учетом потребляемой энергии обычно обеспечивает работу только логики, необходимой для окончания не содержащих события и нормальных µор, и отключает питание всех других логических схем до тех пор, пока не будет идентифицирована потребность в них.

Для обеспечения БВП с учетом потребляемой энергии, в вариантах воплощения различные ресурсы, такие как массивы, могут быть разделены на два блока: один, который считывают при каждом окончании инструкции, и другой, который считывают только по требованию (например, для операции МОНРХ, прерываний, ошибок и т.д.). Затем логика для идентификации каждой части каждого массива будет считана для каждого типа возможностей (например, только событие, только МОНРХ и т.д.), которая может использоваться для включения питания соответствующего ресурса. Кроме того, логика окончания инструкции может быть разделена таким образом, что каждая часть будет включена по отдельности, когда выполняют окончание такого типа, который ассоциирован с этим видом операций.

В нормальном случае, когда спекулятивное событие не детектируют, сигнал гарантии для окна окончания инструкции, который обозначает, что µор могут быть обоснованно закончены без ошибки или исключений, может быть немедленно активным, когда µор готовы к действительному окончанию инструкции, и при этом не требуется выполнение каких-либо расчетов с использованием логики ошибок. Поэтому такое управление может быть реализовано быстрее, например, на один или больше циклов, и, таким образом, может называться ранним сигналом гарантии. Однако, когда детектируют спекулятивное событие, раннюю гарантию не формируют в это время и вместо этого формируют (поздний) сигнал гарантии, или уничтожения или недействительный сигнал для обозначения, что µор не могут быть обоснованно закончены с помощью логики, включаемой по требованию.

На фиг.2 показана блок-схема логики окончания инструкции в соответствии с одним вариантом воплощения настоящего изобретения. Как показано на фиг.2, модуль 200 окончания инструкции, который может соответствовать БВП, может иметь различные ресурсы, которые разделены на множество отделов, где первый отдел может всегда быть включен для выполнения операций во время каждого окна окончания инструкции, и второй отдел может включаться только периодически в соответствии с необходимостью, для обработки окончания инструкций, имеющих различные события, связанные с ними. Как показано на фиг.2, модуль 200 окончания инструкций включает в себя массив 210 выделения. Массив 210 выделения может принимать входящую информацию, связанную с µор при их выделении. Хотя объем настоящего изобретения не ограничен в этом отношении, такая информация может соответствовать статической информации, ассоциированной с µор, такой как тип операций (операций ответвления, загрузки, сохранения, с плавающей запятой (FP, ПЗ) или с целыми числами), или тип исключения, связанный с µop. Как показано в фиг.2, массив 210 выделения может быть разделен на первый отдел 212, который может быть выполнен так, чтобы он всегда был активным, и второй отдел 214, который включают только в соответствии с необходимостью (то есть по требованию). Как показано, относительный размер первого отдела 212 может быть намного меньшим, чем у второго отдела 214. Таким образом, часть, всегда получающая питание, может быть выполнена относительно небольшой, что уменьшает потребление энергии. С этой целью, только минимальное количество информации для каждой µор может быть сохранено в первом отделе 212. Например, может быть сохранен один бит для каждой µор, который обозначает, присутствует ли дополнительная информация µор во втором отделе 214. Таким образом, если µор представляет собой µор, которая может быть нормально закончена без какого-либо типа обработки события, ассоциированный бит в первом отделе 212 может представлять собой бит в первом состоянии (например, логического нуля), в то время как во втором состоянии (например, логической 1), он означает, что дополнительная информация, связанная с µор, присутствует во втором отделе 214.

Аналогично, массив 220 обратной записи (ОЗ) может быть соединен для получения информации при обратной записи, связанной с µор. Таким образом, после выполнения заданной µор в исполнительном модуле, различная информация результата, включающая в себя рассчитанные значения, а также флаги состояния, или другая такая информация, включающая в себя информацию ошибки или другое исключение, может быть предоставлена в массив 220 ОЗ. Как показано на фиг.2, массив 220 ОЗ также разделен на две части, а именно, на первый отдел 222 и второй отдел 224. Эти отделы могут сохранять информацию таким же образом, как описано выше в отношении массива 210 выделения.

Также на фиг.2 показано, что ранняя логика 230 может быть подключена к обоим массивам 210 и 220 и может принимать из них сигналы включения. Как дополнительно показано на фиг.2, ранняя логика 230 может быть подключена для приема информации о глобальном событии из других частей процессора. Хотя объем настоящего изобретения не ограничивается в этом отношении, такие глобальные события могут соответствовать прерываниям, слежению или другим таким событиям. Ранняя логика 230 может быть выполнена с возможностью приема этой информации и определения, может ли быть сгенерирован ранний сигнал гарантии. Таким образом, если никакие глобальные события, связанные с окном окончания инструкции не будут приняты, и значения из включенных первых отделов массивов 210 и 220 обозначают, что информация, связанная с µор окна окончания не присутствует во вторых отделах, это означает, что отсутствуют события для обработки, и может быть выполнено нормальное окончание инструкции. В соответствии с этим, ранняя логика 230 генерирует ранний сигнал гарантии, который как будет дополнительно описано ниже, выводят в логику 250 вывода. Таким образом, ранняя логика 230, по существу, действует как логика "ИЛИ".

Если вместо этого любые из этих различных входных данных в раннюю логику 230 обозначают, что ранний сигнал гарантии не может быть сгенерирован, вторые отделы массивов 210 и 220 могут быть активированы так, что информация, соответствующая окну окончания инструкции из этих массивов, может быть передана в логику 240 события, которая, в общем, относится к логике для выполнения операций, относящихся к окончанию инструкций.

Логика 240 события, таким образом, может быть включена, когда ранний сигнал гарантии не может быть сгенерирован так, что обеспечивается возможность выполнения обработки события, связанного с окном окончания инструкции. Кроме того, на основе информации, присутствующей во втором отделе, логика 245 окончания инструкции, не связанного с событием, может быть включена для выполнения операций, относящихся к окончанию инструкций, таких как обновление указателя инструкции, из-за ошибочно спрогнозированного ответвления, или показатель МОНРХ, принятый после выделения или окончания инструкций. Хотя это не показано для простоты иллюстрации в варианте воплощения, представленном на фиг.2, следует понимать, что в различных вариантах воплощения логика 240 события сама может быть разделена на различные участки таким образом, что может быть активирована только минимальная часть такой логики, предназначенная для обработки заданного типа окончания инструкции или обработки события. Таким образом, когда информация обозначает необходимость в определенной части логики 240 события, используемой для обработки события, только эта часть логики 240 может быть включена.

Логика 240 события может генерировать выход, который представляют в выходную логику 250. Этот выход может соответствовать сигналу гарантии, если расчет обозначает, что окно окончания инструкции является действительным. Следует отметить, что этот сигнал гарантии можно рассматривать как поздний сигнал гарантии, который генерируют через один или больше циклов после раннего сигнала гарантии, который может быть сгенерирован в ранней логике 230. Если на основе расчетов, выполненных в логике 240 события, определяют, что окно окончания инструкции не может быть обоснованно выключено, например, из-за ошибки, прерывания, неверного прогнозирования или так далее, вместо этого может быть передан сигнал неправильного выполнения или сигнал прекращения выполнения инструкции в выходную логику 250, и окончание инструкции может обрабатываться другой логикой, которая будет работать в программном порядке, но может работать с другой скоростью, чем исходная скорость (то есть окончание одной µор на период тактовой частоты по сравнению с окончанием четырех µор на период тактовой частоты при использовании нормальной скорости окончания инструкции).

Выходная логика 250, которая может представлять собой конечный автомат (FSM, КА), может, таким образом, принимать эти различные сигналы из ранней логики 230 и логики 240 событий. Выходная логика 250 может действовать для перевода в последовательную форму этих различных сигналов таким образом, чтобы они поступали из выходной логики 250 в порядке программы. Таким образом, вместо выполнения инструкций не по порядку, выходная логика 250 может обеспечивать, что ранний сигнал гарантии, который может быть принят на один или больше циклов раньше, чем сигнал гарантии или сигнал неправильного выполнения из логики 240 события, для более раннего окна окончания инструкции, не будет выработан до такого сигнала. Другими словами, выходная логика 250 выводит сигналы для каждого окна окончания инструкций по порядку, независимо от того, поступают ли такие сигналы из ранней логики 230 или логики 240 события.

В различных вариантах выполнения выходная логика 250 может быть соединена с различными другими ресурсами процессора, такими как логика управления и т.д., что обеспечивает действительное связывание результатов исполнения с архитектурным состоянием процессора, если генерируется сигнал гарантии, и представляет соответствующую ошибку для другой обработки исключения, включающую в себя потенциальную очистку различных ресурсов процессора, если вместо этого будет сгенерирован недействительный сигнал.

Таким образом, как показано на фиг.2, различные массивы разделены на первые отделы, которые всегда считывают, и вторые отделы, которые считывают избирательно. Аналогично, логика модуля 200 окончания инструкции также может быть разделена на логику, которая всегда активна и используется для определения, произошло ли событие, связанное с окном окончания инструкции, и если так, какая дополнительная логика окончания инструкции должна быть включена. Хотя данное конкретное воплощение представлено в варианте воплощения, показанном на фиг.2, объем настоящего изобретения не ограничивается этим.

Таким образом, для краткого описания, работы, во время выделения ресурсов статическая информация, определяющая, какой отдел требуется считать, может быть рассчитана и сохранена в массиве 210 выделения и, более конкретно, в первом отделе 212. Аналогичную работу выполняют для информации ОЗ, которая может быть сохранена в массиве 220 ОЗ, и, более конкретно, в первом отделе 222. Затем во время окончания инструкции ранняя логика 230 считывает информацию и принимает решение, в отношении того, какой массив требуется считать, и какую логику требуется включить. Кроме того, ранняя логика 230 также может проверять внешние события, такие как прерывания или слежение для определения, требуется ли включить другой массив или логику. В случае, если будет идентифицирована задача, которую требуется выполнить, и для нее требуется дополнительная информация из одного из массивов, который не был считан, тогда определенную часть выделенных ресурсов или массивов ОЗ считывают, и дополнительную логику включают для выполнения этой задачи.

Рассмотрим теперь фиг.3, на которой показана блок-схема последовательности операций способа в соответствии с вариантом воплощения настоящего изобретения. Как показано на фиг.3, способ 300 можно использовать для окончания инструкций с учетом потребления энергии. Способ 300 может начинаться после приема статической информации при выделении инструкций и сохранения такой информации на выбранных участках буфера выделения (блок 310). Например, как описано выше, если такая статическая информация обозначает, что маловероятно возникновение ошибки или исключения, индикатор, такой как один бит, может быть установлен в меньшем первом участке буфера выделения для обозначения, что дополнительная информация, связанная с инструкцией, не присутствует во втором участке буфера выделения. Если вместо этого статическая информация означает, что дополнительная обработка, вероятно, потребуется при окончании инструкции, то есть из-за ошибки, отслеживания рабочих характеристик или по другой причине, индикатор может быть установлен так, что он будет обозначать, что дополнительная информация присутствует во втором отделе. Аналогичные операции могут возникать в отношении динамической информации, принятой при обратном считывании инструкций и которые сохраняют в аналогично устроенном буфере обратного считывания (блок 320).

Так же, на фиг.3, в ромбе 330 может выполняться определение (во время окончания инструкции), обозначает ли информация в первых участках буферов, связанных с данным окном окончания инструкции, что необходима дополнительная обработка окончания инструкции или события. Таким образом, на основе состояния соответствующих индикаторов в первом участке, может быть определено, может ли потребоваться такая обработка окончания инструкции (например, обновление указателя прерываний или отслеживание рабочих характеристик) или обработка события, например различные расчеты, обработка ошибки или прерывания и так далее. Если нет, управление переходит к ромбу 340, где может быть определено, был ли принят глобальный сигнал, который ассоциирован с окном окончания инструкции. Как описано выше, такой глобальный сигнал может соответствовать прерыванию, слежению или другим глобальным событиям. Если такой сигнал не был принят, ранняя логика, например, может вырабатывать ранний сигнал гарантии (блок 350).

Так же на фиг.3, если вместо этого будет определено, что требуется дополнительная обработка окончания инструкции или обработка события или был принят глобальный сигнал, управление переходит либо из ромба 330, или 340 в блок 360, где могут быть активированы дополнительные участки выделения и буферов обратной записи. Управление затем переходит в блок 370, где такая обработка может быть выполнена в одном или больше активированных участках логики события. Как описано выше, на основе представленной дополнительной информации различная логика окончания инструкции или логика события может быть включена для выполнения различных расчетов или другой обработки, для определения, может ли быть сгенерирован поздний сигнал гарантии. В соответствии с этим, выход логики события может представлять собой поздний сигнал гарантии или сигнал недействительности (например, прекращение обработки) (блок 380).

Кроме того, показано на фиг.3, как из блока 350, так и из блока 380, управление переходит в блок 390, где различные сигналы могут быть преобразованы в последовательную форму для вывода из модуля окончания инструкции. Таким образом, для поддержания последовательности окон окончания инструкции ранний сигнал гарантии, сгенерированный для более позднего окна окончания инструкции, не будет передан перед сигналом поздней гарантии или сигналом недействительности, связанным с более ранним окном окончания инструкции. Хотя в варианте воплощения, описанном со ссылкой на фиг.3, был представлен конкретный вариант выполнения, объем настоящего изобретения не ограничивается этим.

Например, если определяют, что специальная обработка требуется при прекращении инструкции, прекращаемые µор могут быть обработаны по-другому, чем обычно. Предположим, что 8 µор обычно прекращают работу в случае, когда отсутствует какое-либо событие. Когда событие детектируют в окне окончания инструкции, работа каждой µор может быть вместо этого, отдельно прекращена таким образом, что только один набор логики события потребуется для одной µop. Это может дополнительно позволит уменьшить потребление энергии и даже повысит рабочие характеристики, если окончание инструкции будет выполнено быстро. Однако операция прекращения инструкции после того, как будет принято решение активировать определенную логику, может осуществляться с другой скоростью, чем исходная скорость.

Один пример события, которое больше не требуется, может представлять собой бит закрепления в памяти, который установлен. При этом нет необходимости устанавливать его снова, и, таким образом, не требуется включать логику события, для выполнения такой дублирующей установки. Другой такой случай представляет суммирование ранних сигналов для достаточно ранней идентификации работы без ошибок таким образом, что операция, связанная с ней, не будет выполнена. Например, операция с плавающей запятой (ПЗ), может быть заявлена безопасной достаточно рано таким образом, что не потребуется обработка исключения с использованием определенной логики. В случаях, когда для обработки МОНРХ и сохранения состояния сопроцессора БВП считывает массивы данных, которые он содержит, выполняет задачи, связанные с операцией, но он не выполняет проверку ошибок и не активирует логику, связанную с ней, в случае, если не была детектирована ошибка.

Варианты воплощения могут быть выполнены во множестве различных типов системы. На фиг.4 представлена блок-схема системы в соответствии с вариантом воплощения настоящего изобретения. Как показано на фиг.4, система 500 микропроцессора представляет собой систему со сквозной передачей данных, и включает в себя первый процессор 570 и второй процессор 580, соединенные через взаимное соединение 550 с прямой передачей данных. Как показано на фиг.4, каждый из процессоров 570 и 580 может представлять собой многоядерные процессоры, включающие в себя первое и второе ядра процессора (то есть ядра 574а и 574b процессора и ядра 584а и 584b процессора). Каждое ядро процессора может включать в себя такую логику, как показано на фиг.1 и 2, для обеспечения окончания инструкции с учетом потребления энергии в соответствии вариантом воплощения настоящего изобретения.

Так же, как показано на фиг.4, первый процессор 570 дополнительно включает в себя концентратор 572 контроллера памяти (МСН, ККП), и интерфейсы 576 и 578 с прямой связью (Р-Р, ПС). Аналогично, второй процессор 580 включает в себя ККП 582 и интерфейсы 586 и 588 ПС. Как показано на фиг.4, ККП 572 и 582 соединяют процессоры с соответствующими запоминающими устройствами, а именно, запоминающим устройством 532 и запоминающим устройством 534, которые могут представлять собой части основного запоминающего устройства (например, динамического оперативного запоминающего устройства (DRAM, ДОЗУ)), которое локально соединено с соответствующими процессорами. Первый процессор 570 и второй процессор 580 могут быть соединены с набором 590 микросхем через взаимные соединения 552 и 554 Р-Р соответственно. Как показано на фиг.4, набор 590 микросхем включает в себя интерфейсы 594 и 598 ПС.

Кроме того, набор 590 микросхем включает в себя интерфейс 592 для подключения набора 590 микросхем к высокопроизводительному графическому механизму 538. В свою очередь, набор 590 микросхем может быть соединен с первой шиной 516 через интерфейс 596. Как показано на фиг.4, различные устройства 514 входа/выхода могут быть соединены с первой шиной 516 вместе с мостом 518 шины, который соединяет первую шину 516 со второй шиной 520. Различные устройства могут быть соединены со второй шиной 520, включая в себя, например, клавиатуру/мышь 522, устройство 526 передачи данных и модуль 528 накопителя данных, например привод диска или другое устройство - носитель данных большого объема, которое может включать в себя код 530, в одном варианте воплощения. Кроме того, вход/выход 524 аудиоданных может быть соединен со второй шиной 520.

Варианты воплощения могут быть выполнены в виде кода и могут быть сохранены на носителе данных, в котором сохранены инструкции, которые можно использовать для программирования системы, для выполнения этих инструкций. Носитель данных может включать в себя, но не ограничивается этим, любой тип диска, включающего в себя гибкие диски, оптические диски, постоянные запоминающие устройства на компакт-диске (CD-ROM, КД-ПЗУ), перезаписываемые компакт-диски (CD-RW, КД-ПЗ) и магнитооптические диски, полупроводниковые устройства, такие как постоянные запоминающие устройства (ПЗУ ROM), оперативные запоминающие устройства (ОЗУ, RAM), такие как динамические оперативные запоминающие устройства (DRAM), статические запоминающие устройства (SRAM), стираемые программируемые постоянные запоминающие устройства (EEPROM), запоминающее устройство типа флэш, электрически стираемые программируемые постоянные запоминающие устройства (СППЗУ), магнитные или оптические карты, или любые другие типы носителей, пригодные для сохранения электронных инструкций.

Хотя настоящее изобретение было описано в отношении ограниченного количества вариантов воплощения, для специалистов в данной области будут понятны различные модификации и их варианты. При этом предполагается, что приложенная формула изобретения охватывает все такие модификации и варианты, которые попадают в пределы истинной сущности и объема настоящего изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕОГРАНИЧЕННАЯ ТРАНЗАКЦИОННАЯ ПАМЯТЬ С ГАРАНТИЯМИ ПРОДВИЖЕНИЯ ПРИ ПЕРЕСЫЛКЕ, ИСПОЛЬЗУЯ АППАРАТНУЮ ГЛОБАЛЬНУЮ БЛОКИРОВКУ | 2014 |

|

RU2597506C2 |

| ПРЕДСТАВЛЕНИЕ ФИЛЬТРАЦИИ НАБЛЮДЕНИЯ, АССОЦИИРОВАННОЙ С БУФЕРОМ ДАННЫХ | 2013 |

|

RU2608000C2 |

| СИСТЕМЫ И СПОСОБЫ ОТСЛЕЖИВАНИЯ ФЛАГА В ОПЕРАЦИЯХ УСТРАНЕНИЯ ПЕРЕМЕЩЕНИЯ | 2014 |

|

RU2628156C2 |

| СИНХРОНИЗАЦИЯ ОБРАБОТКИ ПРЕРЫВАНИЯ ДЛЯ УМЕНЬШЕНИЯ ПОТРЕБЛЕНИЯ ЭНЕРГИИ | 2014 |

|

RU2651238C2 |

| ОПРЕДЕЛЕНИЕ ПРОФИЛЯ ПУТИ, ИСПОЛЬЗУЯ КОМБИНАЦИЮ АППАРАТНЫХ И ПРОГРАММНЫХ СРЕДСТВ | 2013 |

|

RU2614583C2 |

| АВТОНОМНЫЙ ДЕТЕКТОРНЫЙ МОДУЛЬ КАК СТРОИТЕЛЬНЫЙ БЛОК ДЛЯ МАСШТАБИРУЕМЫХ СИСТЕМ PET И SPECT | 2009 |

|

RU2536792C2 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ИДЕНТИФИКАЦИИ ИНСТРУКЦИЙ ДЛЯ УДАЛЕНИЯ В МНОГОПОТОЧНОМ ПРОЦЕССОРЕ С ИЗМЕНЕНИЕМ ПОСЛЕДОВАТЕЛЬНОСТИ | 2013 |

|

RU2644528C2 |

| ПРЕДОСТАВЛЕНИЕ ВЫБРАННЫХ ОТПРАВИТЕЛЕМ ЭЛЕМЕНТОВ ЗВУКА УЧАСТНИКАМ РАЗГОВОРА | 2008 |

|

RU2493597C2 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ДОСТУПА К ПАМЯТИ В КЛАСТЕРНОЙ МАШИНЕ ШИРОКОГО ИСПОЛНЕНИЯ | 2013 |

|

RU2662394C2 |

| УПРАВЛЕНИЕ ПАМЯТЬЮ ДЛЯ ВЫСОКОСКОРОСТНОГО УПРАВЛЕНИЯ ДОСТУПОМ К СРЕДЕ | 2007 |

|

RU2419226C2 |

Изобретение относится к способу, устройству и системе управления логикой окончания инструкций. Техническим результатом является уменьшение потребляемой энергии. Способ содержит: прием статической информации, связанной с инструкцией, при выделении инструкции, и сохранение участка статической информации в первом участке буфера выделения, и сохранение второго участка статической информации во втором участке буфера выделения, если статическая информация обозначает событие, которое должно быть выполнено во время окончания инструкции; выработку раннего сигнала гарантии во время окончания инструкции для инструкции, если статическая информация, связанная с инструкцией, не присутствует во втором участке буфера выделения; и в противном случае включение питания второго участка буфера выделения, для обеспечения доступа ко второму участку статической информации, в котором если выработан ранний сигнал гарантии, выключают второй участок буфера выделения, для уменьшения потребляемой энергии во время нормальных действий при окончании инструкции. 3 н. и 17 з.п. ф-лы, 4 ил.

1. Устройство для управления логикой окончания инструкции, содержащее: модуль окончания инструкции, предназначенный для окончания инструкций после выполнения, модуль окончания инструкции включает в себя:

первый массив, предназначенный для приема первой информации при выделении инструкций, первый массив разделен на первый участок, который считывают в каждом окне окончания инструкции, и второй участок, считываемый по требованию;

второй массив, предназначенный для приема второй информации после выполнения инструкций, причем второй массив разделен на первый участок, который считывают в каждом окне окончания инструкции, и второй участок, который считывают по требованию; и

логика, выполняемая по требованию, предназначенная для расчета события, связанного с исполняемой инструкцией, если информация, связанная с исполняемой инструкцией, сохранена во втором участке первого массива или второго массива, при этом в противном случае логика, выполняемая по требованию, выключена,

в котором второй участок первого и второго массивов должен быть выключен для уменьшения потребляемой энергии модуля окончания инструкции во время нормальных действий при окончании инструкции, если только не будет активна логика, вырабатывающая требование.

2. Устройство по п.1, в котором логика, выполняемая по требованию, предназначена для генерирования сигнала гарантии для исполняемой инструкции, если расчеты показывают, что исполняемая инструкция не имеет ошибок, и для генерирования сигнала недействительности, если была обозначена ошибка.

3. Устройство по п.2, дополнительно содержащее раннюю логику, соединенную с выходами первого и второго массивов и предназначенную для вывода раннего сигнала гарантии для первой исполняемой инструкции на основе информации в первом участке первого и второго массивов.

4. Устройство по п.3, в котором ранняя логика дополнительно подключена для получения глобальной информации о событии и активации логики, исполняемой по требованию в ответ на нее.

5. Устройство по п.3, дополнительно содержащее выходную логику, соединенную с логикой, исполняемой по требованию, и ранней логикой, для преобразования в последовательную форму сигнала ранней гарантии и сигнала гарантии или сигнала недействительности.

6. Устройство по п.4, в котором ранняя логика предназначена для активации второго участка первого массива на основе состояния индикатора, соответствующего окну окончания инструкции, присутствующему в первом участке первого массива.

7. Устройство по п.1, в котором первый массив содержит массив выделения и второй массив содержит массив с обратной записью.

8. Устройство по п.7, в котором второй участок первого и второго массивов должен быть выключен, если только не будет активна логика, вырабатывающая требование.

9. Способ управления логикой окончания инструкции, содержащий: принимают статическую информацию, связанную с инструкцией, при выделении инструкции и сохраняют, по меньшей мере, первый участок статической информации в первом участке буфера выделения и сохраняют второй участок статической информации во втором участке буфера выделения, если статическая информация обозначает событие, которое должно быть выполнено во время окончания инструкции;

вырабатывают ранний сигнал гарантии во время окончания инструкции для инструкции, если статическая информация, связанная с инструкцией, не присутствует во втором участке буфера выделения; и

в противном случае включают питание второго участка буфера выделения для обеспечения доступа ко второму участку статической информации, в котором, если выработан ранний сигнал гарантии, выключают второй участок буфера выделения для уменьшения потребляемой энергии во время нормальных действий при окончании инструкции.

10. Способ по п.9, дополнительно содержащий: выполняют обработку события в логике события, которую включают, если не был выработан ранний сигнал гарантии.

11. Способ по п.10, дополнительно содержащий: генерируют поздний сигнал гарантии или сигнал недействительности в логике события на основе результата обработки события.

12. Способ по п.11, дополнительно содержащий: преобразуют в последовательную форму для выхода из модуля окончания инструкции ранний сигнал гарантии, связанный с первой инструкцией, и поздний сигнал гарантии или сигнал недействительности, ассоциированный со второй инструкцией, причем вторая инструкция следует раньше в порядке программы, чем первая инструкция.

13. Способ по п.9, дополнительно содержащий: принимают динамическую информацию, связанную с инструкцией, при обратной записи инструкции, и сохраняют, по меньшей мере, первую часть динамической информации в первом участке буфера обратной записи, и сохраняют вторую часть динамической информации во втором участке буфера обратной записи, если динамическая информация обозначает событие, которое выполняется во время окончания инструкции.

14. Способ по п.13, дополнительно содержащий: определяют на основе, по меньшей мере, части первого участка статической информации и первого участка динамической информации, следует ли выполнить обработку события для окончания инструкции, и выполняют обработку события во время окончания инструкции, в котором окончание инструкции должно происходить с разной скоростью, когда требуется выполнить обработку события, чем тогда, когда не требуется выполнить обработку события.

15. Система для управления логикой окончания инструкции, содержащая:

процессор, предназначенный для выполнения инструкций не по порядку (ВНП), процессор включает в себя множество исполнительных модулей и модуль окончания инструкции, соединенный с множеством исполнительных модулей, в котором модуль окончания инструкции включает в себя:

буфер выделения, предназначенный для приема первой информации при выделении инструкций, буфер выделения разделен на первый участок, считываемый в каждом окне окончания инструкции, и второй участок, который считывают по требованию;

буфер обратной записи, предназначенный для приема второй информации после выполнения инструкций, причем буфер обратной записи разделен на первый участок, который считывают в каждом окне окончания инструкции, и второй участок, который считывают по требованию;

первую логику, соединенную с выходами буфера выделения и буфера обратной записи и с выходом сигнала ранней гарантии для первой исполняемой инструкции, если вторая информация, связанная с первой исполняемой инструкцией, отсутствует во второй части буфера выделения или в буфере обратной записи, при этом, если выработан ранний сигнал гарантии, выключается вторая часть буфера выделения и вторая часть буфера обратной записи для уменьшения потребляемой энергии модуля окончания инструкции во время нормальных действий при окончании инструкции; и

вторую логику, соединенную с выходами буфера выделения и буфера обратной записи и с выходом позднего сигнала гарантии или сигнала недействительности для второй исполняемой инструкции, если вторая информация, связанная со второй исполняемой инструкцией, присутствует во втором участке буфера выделения или буфера обратной записи, при этом, если выработан ранний сигнал гарантии, вторая логика выключается для уменьшения потребляемой энергии модуля окончания инструкции; и

динамическое оперативное запоминающее устройство (DRAM), соединенное с процессором.

16. Система по п.15, в которой первая логика предназначена для приема сигнала глобального события и активации второй логики во время окончания третьей исполняемой инструкции, которая отвечает на сигнал глобального события.

17. Система по п.15, дополнительно содержащая третью логику, соединенную с первой логикой и второй логикой, и которая комбинирует выходы первой логики и второй логики.

18. Система по п.17, в которой третья логика предназначена для преобразования в последовательную форму выхода из модуля окончания инструкции позднего сигнала гарантии или сигнала недействительности до раннего сигнала гарантии, в котором вторая исполняемая инструкция выполняется раньше в порядке программы, чем первая исполняемая инструкция.

19. Система по п.15, в которой первые участки буфера выделения и буфера обратной записи должны быть включены во время каждого окна окончания инструкции и второй участок буфера выделения должен быть включен во время окна окончания инструкции, только если информация, связанная с окном окончания инструкции, сохранена во втором участке буфера выделения.

20. Система по п.15, в которой первая логика предназначена для вывода раннего сигнала гарантии и вторая логика не включена во время окна окончания инструкции, в котором бит закрепления в памяти установлен перед окном окончания инструкции и его не требуется устанавливать с помощью модуля окончания инструкции.

| RU 97106771 А, 27.05.1999 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2011-08-27—Публикация

2009-06-26—Подача