Изобретение относится к автоматике и вычислительной технике и может найти применение при построении распределенных систем программного управления и многопроцессорных систем широкого класса.

Известна микроконтроллерная сеть, содержащая M*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры сети, М - число строк, каждый модуль которой включает блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки, группу блоков управления синхронизацией, каждый из которых содержит триггер наличия соседа слева, триггер наличия соседа снизу, группу элементов НЕ, группу элементов И, с первого по пятый элементы ИЛИ, первый и второй элементы И, коммутатор, триггер и триггер разрешения запуска (патент РФ №2280887, МПК8 G05B 19/18, G06F 9/28; заявл. 15.02.2005, опубл. 27.07.2006. Бюл. №21).

Недостатком указанной сети является большое число межмодульных линий связи, что ограничивает область ее применения.

Наиболее близкой к предлагаемому логическому мультиконтроллеру с распределенным параллельно-конвейерным барьерным синхронизатором по технической сущности является микроконтроллерная сеть, содержащая М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры сети, М - число строк, каждый модуль которой включает блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки, группу блоков модулей управления синхронизацией, мультиплексор каналов синхронизации, регистр конфигурации, первый и второй мультиплексоры, дешифратор каналов синхронизации, генератор сигналов управления синхронизацией, первую и вторую группы элементов И (патент РФ №2336553 МПК9 G06F 9/28, G06F 15/173, G06F 1/10; заявл. 17.04.2007, опубл. 20.10.2008. Бюл. №29).

Недостатком данной сети является невысокая скорость выполнения барьерной синхронизации (и, как следствие, недостаточное ее быстродействие при реализации параллельных алгоритмов управления) из-за последовательного характера активизации групп блоков модулей управления синхронизацией (групп барьеров).

Технической задачей заявляемого изобретения является повышение скорости выполнения барьерной синхронизации участков параллельных программ, выполняющихся в различных модулях логического мультиконтроллера (контроллерах), за счет совмещения во времени фазы формирования признаков завершения параллельных участков в одной группе барьеров и запуска ожидающих завершения контроллеров в другой.

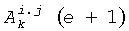

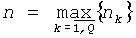

Техническая задача решается тем, что в каждый модуль логического мультиконтроллера с распределенным параллельно-конвейерным барьерным синхронизатором, содержащего М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры, М - число строк, включающий блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, блок элементов ИЛИ, первый и второй одновибраторы, первый элемент задержки, первую и вторую группы элементов И, группу из р блоков управления синхронизацией (где  n - максимальное число вершин синхронизации в реализуемых программах, m - количество барьерных блоков в одном блоке управления синхронизацией, - операция округления вверх), причем вход кода операции модуля соединен со вторым информационным входом коммутатора адреса, выход которого подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока памяти программ, выход которого соединен с информационным входом регистра команд, выход метки конца программы которого соединен с управляющими входами коммутатора адреса, выходы кода логического условия и модифицируемого разряда адреса регистра команд подключены к адресному и второму информационному входам мультиплексора логических условий соответственно, первый информационный вход которого соединен со входом логических условий модуля, первый вход блока синхронизации соединен со входом пуска модуля, выход немодифицируемой части адреса регистра команд в объединении с выходом мультиплексора логических условий подключены к первому входу блока элементов ИЛИ и к информационному входу буферного регистра, выход которого соединен со вторым входом блока элементов ИЛИ, выход которого соединен с первым информационным входом коммутатора адреса, выход микроопераций регистра команд подключен к выходу микроопераций модуля, вход вектора соответствия модуля соединен с информационным входом регистра вектора соответствия, групповые выходы с первого по р-й которого соединены со вторыми входами блоков управления синхронизацией с первого по р-й соответственно, первый выход номера вершины синхронизации регистра команд соединен со входом первого дешифратора номера вершины синхронизации, групповые выходы с первого по р-й которого соединены с третьими входами блоков управления синхронизацией с первого по р-й соответственно, второй выход номера вершины синхронизации регистра команд соединен со входом второго дешифратора номера вершины синхронизации, групповые выходы с первого по р-й которого соединены с девятыми входами блоков управления синхронизацией с первого по р-й соответственно, выход первого элемента ИЛИ соединен со входом синхронизации буферного регистра и со входом первого одновибратора, выход которого подключен ко входу сброса регистра команд и ко второму входу блока синхронизации, первый выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен ко входу синхронизации регистра адреса, выход метки конца участка регистра команд соединен со входом второго одновибратора, выход которого соединен с третьим входом блока синхронизации, второй выход которого подключен ко входу сброса буферного регистра и ко второму входу третьего элемента ИЛИ, вход настройки модуля соединен со вторым входом второго элемента ИЛИ, со входом синхронизации регистра вектора соответствия, а также со входом первого элемента задержки, выход которого подключен к первому входу третьего элемента ИЛИ, выход которого подключен ко входу синхронизации регистра команд, первая группа входов модуля с первого по m-й соединена с первыми входами первой группы элементов И с первого по m-й соответственно, вторая группа входов модуля с первого по m-й соединена со вторыми входами первой группы элементов И с первого по m-й соответственно, третья группа входов модуля с первого по m-й соединена с первыми входами второй группы элементов И с первого по m-й соответственно, четвертая группа входов модуля с первого по m-й соединена со вторыми входами второй группы элементов И с первого по m-й соответственно, выходы первой группы элементов И с первого по m-й соединены с первыми входами блоков управления синхронизацией с первого по р-й, выходы второй группы элементов И с первого по m-й соединены с восьмыми входами блоков управления синхронизацией с первого по р-й, дополнительно введены триггер конфигурации, элемент И, триггер, второй и третий элементы задержки, первый и второй счетчики номера активной группы, первый и второй дешифраторы номера активной группы, четвертый и пятый элементы ИЛИ, первая и вторая группы элементов ИЛИ, причем первый и второй входы модуля соединены с информационным входом и входом синхронизации триггера конфигурации соответственно, прямой выход которого соединен с шестыми входами блоков управления синхронизацией с первого по р-й и с первым входом элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, третий вход модуля соединен со вторым входом элемента И, со входами инкремента первого и второго счетчиков номера активной группы, с пятыми входами блоков управления синхронизацией с первого по р-й, а также является первым выходом модуля, четвертый вход модуля соединен со вторым входом четвертого элемента ИЛИ, выход которого соединен с входом установки триггера, прямой выход которого соединен с первым входом пятого элемента ИЛИ и через второй элемент задержки подключен ко входу сброса триггера, пятый вход модуля соединен со вторым входом пятого элемента ИЛИ, выход которого соединен со входом третьего элемента задержки, выход которого является вторым выходом модуля, шестой вход модуля соединен с информационным входом первого счетчика номера активной группы, выход которого соединен со входом первого дешифратора номера активной группы, выходы с первого по р-й которого соединены с четвертыми входами блоков управления синхронизацией с первого по р-й соответственно, седьмой вход модуля соединен с входом синхронизации первого счетчика номера активной группы, восьмой вход модуля соединен с информационным входом второго счетчика номера активной группы, выход которого соединен со входом второго дешифратора номера активной группы, выходы с первого по р-й которого соединены с седьмыми входами блоков управления синхронизацией с первого по р-й соответственно, девятый вход модуля соединен с входом синхронизации второго счетчика номера активной группы, первые групповые выходы блоков управления синхронизацией с первого по р-й соединены соответственно с первого по р-й входами с первого по m-й элементов первой группы элементов ИЛИ соответственно, вторые групповые выходы блоков управления синхронизацией с первого по р-й соединены соответственно с первого по р-й входами с первого по m-й элементов второй группы элементов ИЛИ соответственно, третьи групповые выходы блоков управления синхронизацией с первого по р-й соединены с групповыми входами первого элемента ИЛИ с первого по р-й соответственно, выходы первой группы элементов ИЛИ с первого по m-й являются выходами первой группы выходов модуля с первого по m-й соответственно, а выходы второй группы элементов ИЛИ с первого по m-й являются выходами второй группы выходов модуля с первого по m-й соответственно.

n - максимальное число вершин синхронизации в реализуемых программах, m - количество барьерных блоков в одном блоке управления синхронизацией, - операция округления вверх), причем вход кода операции модуля соединен со вторым информационным входом коммутатора адреса, выход которого подключен к информационному входу регистра адреса, выход которого подключен к адресному входу блока памяти программ, выход которого соединен с информационным входом регистра команд, выход метки конца программы которого соединен с управляющими входами коммутатора адреса, выходы кода логического условия и модифицируемого разряда адреса регистра команд подключены к адресному и второму информационному входам мультиплексора логических условий соответственно, первый информационный вход которого соединен со входом логических условий модуля, первый вход блока синхронизации соединен со входом пуска модуля, выход немодифицируемой части адреса регистра команд в объединении с выходом мультиплексора логических условий подключены к первому входу блока элементов ИЛИ и к информационному входу буферного регистра, выход которого соединен со вторым входом блока элементов ИЛИ, выход которого соединен с первым информационным входом коммутатора адреса, выход микроопераций регистра команд подключен к выходу микроопераций модуля, вход вектора соответствия модуля соединен с информационным входом регистра вектора соответствия, групповые выходы с первого по р-й которого соединены со вторыми входами блоков управления синхронизацией с первого по р-й соответственно, первый выход номера вершины синхронизации регистра команд соединен со входом первого дешифратора номера вершины синхронизации, групповые выходы с первого по р-й которого соединены с третьими входами блоков управления синхронизацией с первого по р-й соответственно, второй выход номера вершины синхронизации регистра команд соединен со входом второго дешифратора номера вершины синхронизации, групповые выходы с первого по р-й которого соединены с девятыми входами блоков управления синхронизацией с первого по р-й соответственно, выход первого элемента ИЛИ соединен со входом синхронизации буферного регистра и со входом первого одновибратора, выход которого подключен ко входу сброса регистра команд и ко второму входу блока синхронизации, первый выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен ко входу синхронизации регистра адреса, выход метки конца участка регистра команд соединен со входом второго одновибратора, выход которого соединен с третьим входом блока синхронизации, второй выход которого подключен ко входу сброса буферного регистра и ко второму входу третьего элемента ИЛИ, вход настройки модуля соединен со вторым входом второго элемента ИЛИ, со входом синхронизации регистра вектора соответствия, а также со входом первого элемента задержки, выход которого подключен к первому входу третьего элемента ИЛИ, выход которого подключен ко входу синхронизации регистра команд, первая группа входов модуля с первого по m-й соединена с первыми входами первой группы элементов И с первого по m-й соответственно, вторая группа входов модуля с первого по m-й соединена со вторыми входами первой группы элементов И с первого по m-й соответственно, третья группа входов модуля с первого по m-й соединена с первыми входами второй группы элементов И с первого по m-й соответственно, четвертая группа входов модуля с первого по m-й соединена со вторыми входами второй группы элементов И с первого по m-й соответственно, выходы первой группы элементов И с первого по m-й соединены с первыми входами блоков управления синхронизацией с первого по р-й, выходы второй группы элементов И с первого по m-й соединены с восьмыми входами блоков управления синхронизацией с первого по р-й, дополнительно введены триггер конфигурации, элемент И, триггер, второй и третий элементы задержки, первый и второй счетчики номера активной группы, первый и второй дешифраторы номера активной группы, четвертый и пятый элементы ИЛИ, первая и вторая группы элементов ИЛИ, причем первый и второй входы модуля соединены с информационным входом и входом синхронизации триггера конфигурации соответственно, прямой выход которого соединен с шестыми входами блоков управления синхронизацией с первого по р-й и с первым входом элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, третий вход модуля соединен со вторым входом элемента И, со входами инкремента первого и второго счетчиков номера активной группы, с пятыми входами блоков управления синхронизацией с первого по р-й, а также является первым выходом модуля, четвертый вход модуля соединен со вторым входом четвертого элемента ИЛИ, выход которого соединен с входом установки триггера, прямой выход которого соединен с первым входом пятого элемента ИЛИ и через второй элемент задержки подключен ко входу сброса триггера, пятый вход модуля соединен со вторым входом пятого элемента ИЛИ, выход которого соединен со входом третьего элемента задержки, выход которого является вторым выходом модуля, шестой вход модуля соединен с информационным входом первого счетчика номера активной группы, выход которого соединен со входом первого дешифратора номера активной группы, выходы с первого по р-й которого соединены с четвертыми входами блоков управления синхронизацией с первого по р-й соответственно, седьмой вход модуля соединен с входом синхронизации первого счетчика номера активной группы, восьмой вход модуля соединен с информационным входом второго счетчика номера активной группы, выход которого соединен со входом второго дешифратора номера активной группы, выходы с первого по р-й которого соединены с седьмыми входами блоков управления синхронизацией с первого по р-й соответственно, девятый вход модуля соединен с входом синхронизации второго счетчика номера активной группы, первые групповые выходы блоков управления синхронизацией с первого по р-й соединены соответственно с первого по р-й входами с первого по m-й элементов первой группы элементов ИЛИ соответственно, вторые групповые выходы блоков управления синхронизацией с первого по р-й соединены соответственно с первого по р-й входами с первого по m-й элементов второй группы элементов ИЛИ соответственно, третьи групповые выходы блоков управления синхронизацией с первого по р-й соединены с групповыми входами первого элемента ИЛИ с первого по р-й соответственно, выходы первой группы элементов ИЛИ с первого по m-й являются выходами первой группы выходов модуля с первого по m-й соответственно, а выходы второй группы элементов ИЛИ с первого по m-й являются выходами второй группы выходов модуля с первого по m-й соответственно.

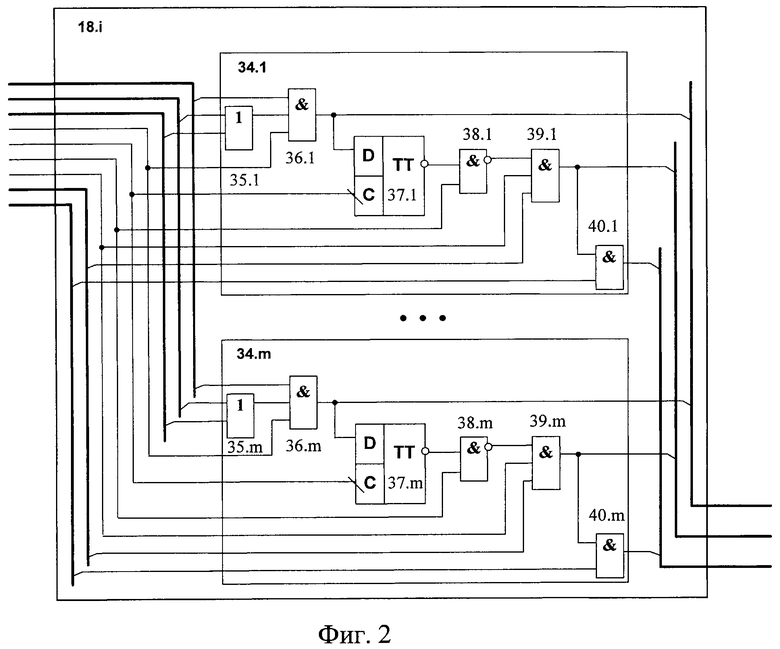

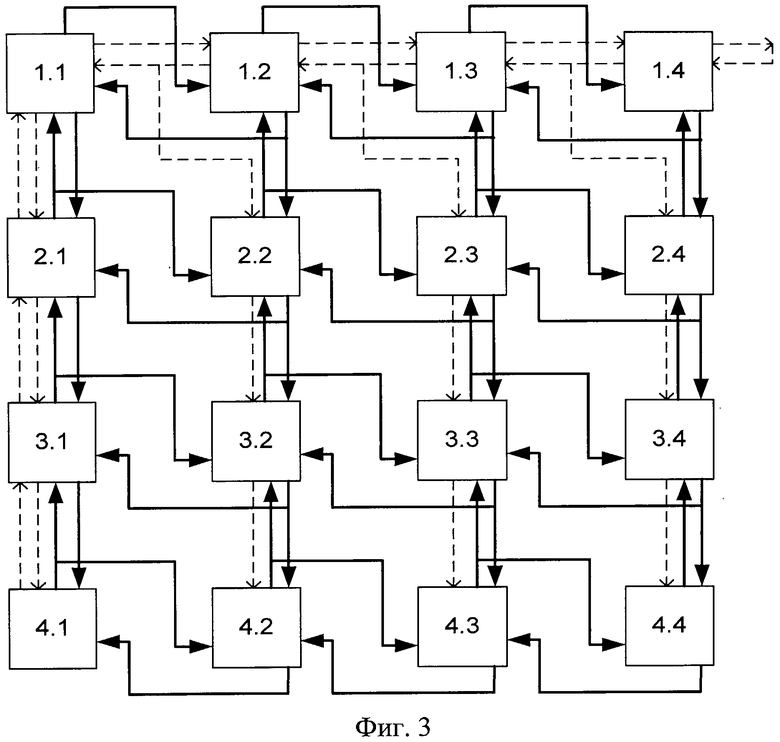

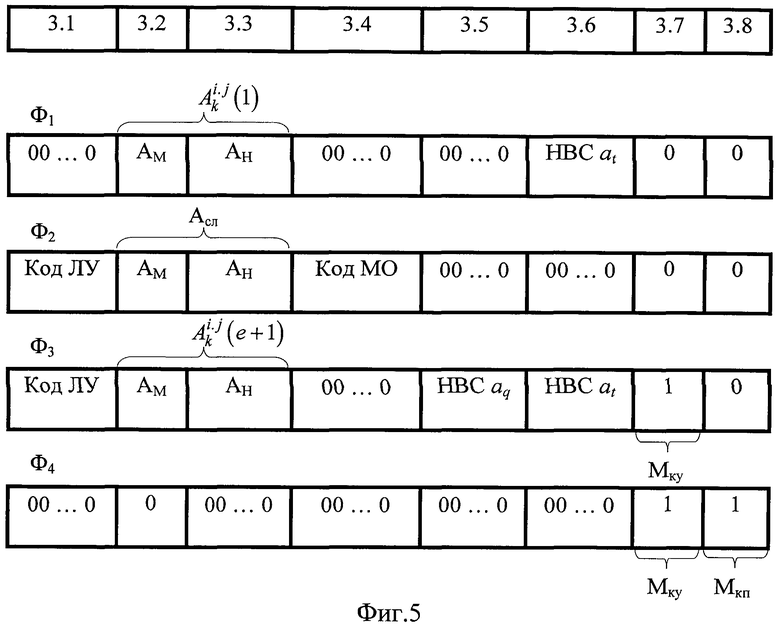

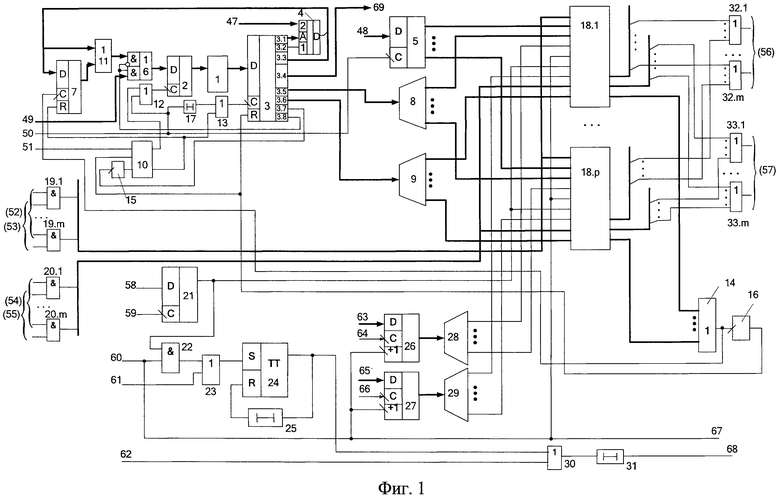

Сущность изобретения поясняется чертежами, где на фиг.1 представлена функциональная схема модуля логического мультиконтроллера с распределенным параллельно-конвейерным барьерным синхронизатором, на фиг.2 изображена функциональная схема блока управления синхронизацией, на фиг.3 дана структурная схема мультиконтроллера на примере конфигурации 4×4, причем пунктирными линиями показаны связи для передачи сигналов управления, а сплошными - связи для передачи признаков завершения параллельных участков и запуска модулей мультиконтроллера, на фиг.4 изображена функциональная схема блока синхронизации, на фиг.5 приведены форматы (микро)команд, реализуемые модулем мультиконтроллера, на фиг.6 представлен иллюстративный пример, поясняющий принципы реализации параллельных алгоритмов (программ) в логическом мультиконтроллере.

Модуль логического мультиконтроллера с распределенным параллельно-конвейерным барьерным синхронизатором (фиг.1) включает блок 1 памяти программ, регистр 2 адреса, регистр 3 команд, мультиплексор 4 логических условий, регистр 5 вектора соответствия, коммутатор 6 адреса, буферный регистр 7, первый 8 и второй 9 дешифраторы номера вершины синхронизации, блок 10 синхронизации, блок элементов ИЛИ 11, первый 14, второй 12, третий 13, четвертый 23 и пятый 30 элементы ИЛИ, первый 16 и второй 15 одновибраторы, первый 17, второй 25 и третий 31 элементы задержки, группу 18.1-18.p блоков управления синхронизацией, первую 19.1-19.m и вторую 20.1-20.m группы элементов И, триггер 21 конфигурации, элемент И 22, триггер 24, первый 26 и второй 27 счетчики номера активной группы, первый 28 и второй 29 дешифраторы номера активной группы, первую 32.1-32.m и вторую 33.1-33.m группы элементов ИЛИ, причем вход 49 кода операции модуля соединен со вторым информационным входом коммутатора 6 адреса, выход которого подключен к информационному входу регистра 2 адреса, выход которого подключен к адресному входу блока 1 памяти программ, выход которого соединен с информационным входом регистра 3 команд, выход 3.8 метки конца программы которого соединен с управляющими входами коммутатора 6 адреса, выходы 3.1 кода логического условия и 3.2 модифицируемого разряда адреса регистра 3 команд подключены к адресному и второму информационному входам мультиплексора 4 логических условий соответственно, первый информационный вход которого соединен со входом 47 логических условий модуля, первый вход блока 10 синхронизации соединен со входом 51 пуска модуля, выход 3.3 немодифицируемой части адреса регистра 3 команд в объединении с выходом мультиплексора 4 логических условий подключены к первому входу блока 11 элементов ИЛИ и к информационному входу буферного регистра 7, выход которого соединен со вторым входом блока 11 элементов ИЛИ, выход которого соединен с первым информационным входом коммутатора 6 адреса, выход 3.4 микроопераций регистра 3 команд подключен к выходу 69 микроопераций модуля, вход 48 вектора соответствия модуля соединен с информационным входом регистра 5 вектора соответствия, групповые выходы с первого по р-й которого соединены со вторыми входами блоков 18.1-18.p управления синхронизацией соответственно, первый выход 3.5 номера вершины синхронизации регистра 3 команд соединен со входом дешифратора 8 номера вершины синхронизации, групповые выходы с первого по р-й которого соединены с третьими входами блоков 18.1-18.p управления синхронизацией соответственно, второй выход 3.6 номера вершины синхронизации регистра 3 команд соединен со входом дешифратора 9 номера вершины синхронизации, групповые выходы с первого по р-й которого соединены с девятыми входами блоков 18.1-18.p управления синхронизацией соответственно, выход элемента ИЛИ 14 соединен со входом синхронизации буферного регистра 7 и со входом одновибратора 16, выход которого подключен ко входу сброса регистра 3 команд и ко второму входу блока 10 синхронизации, первый выход которого соединен с первым входом элемента ИЛИ 12, выход которого подключен ко входу синхронизации регистра 2 адреса, выход 3.7 метки конца участка регистра 3 команд соединен со входом одновибратора 15, выход которого соединен с третьим входом блока 10 синхронизации, второй выход которого подключен ко входу сброса буферного регистра 7 и ко второму входу элемента ИЛИ 13, вход 50 настройки модуля соединен со вторым входом элемента ИЛИ 12, со входом синхронизации регистра 5 вектора соответствия, а также со входом элемента 17 задержки, выход которого подключен к первому входу элемента ИЛИ 13, выход которого подключен ко входу синхронизации регистра 3 команд, входы 52.1-52.m модуля соединены с первыми входами элементов И 19.1-19.m соответственно, входы 53.1-53.m модуля соединены со вторыми входами элементов И 19.1-19.m соответственно, входы 54.1-54.m модуля соединены с первыми входами элементов И 20.1-20.m соответственно, входы 55.1-55.m модуля соединены со вторыми входами элементов И 20.1-20.m соответственно, выходы элементов И 19.1-19.m соединены с первыми входами блоков 18.1-18.p управления синхронизацией, выходы элементов И 20.1-20.m соединены с восьмыми входами блоков 18.1-18.p управления синхронизацией, первый 58 и второй 59 входы модуля соединены с информационным входом и входом синхронизации триггера 21 конфигурации соответственно, прямой выход которого соединен с шестыми входами блоков 18.1-18.p управления синхронизацией и с первым входом элемента И 22, выход которого соединен с первым входом элемента ИЛИ 23, третий вход 60 модуля соединен со вторым входом элемента И 22, со входами инкремента счетчиков 26 и 27 номера активной группы, с пятыми входами блоков 18.1-18.p управления синхронизацией, а также является первым выходом 67 модуля, четвертый вход 61 модуля соединен со вторым входом элемента ИЛИ 23, выход которого соединен с входом установки триггера 24, прямой выход которого соединен с первым входом элемента ИЛИ 30 и через элемент 25 задержки подключен ко входу сброса триггера 24, пятый вход 62 модуля соединен со вторым входом элемента ИЛИ 30, выход которого соединен со входом элемента 31 задержки, выход которого является вторым выходом 68 модуля, шестой вход 63 модуля соединен с информационным входом счетчика 26 номера активной группы, выход которого соединен со входом дешифратора 28 номера активной группы, выходы с первого по р-й которого соединены с четвертыми входами блоков 18.1-18.р управления синхронизацией соответственно, седьмой вход 64 модуля соединен с входом синхронизации счетчика 26 номера активной группы, восьмой вход 65 модуля соединен с информационным входом счетчика 27 номера активной группы, выход которого соединен со входом дешифратора 29 номера активной группы, выходы с первого по р-й которого соединены с седьмыми входами блоков 18.1-18.p управления синхронизацией соответственно, девятый вход 66 модуля соединен с входом синхронизации счетчика 29 номера активной группы, первые групповые выходы блоков 18.1-18.p управления синхронизацией соединены соответственно с первого по р-й входами элементов ИЛИ 32.1-32.m соответственно, вторые групповые выходы блоков 18.1-18.p управления синхронизацией соединены соответственно с первого по р-й входами элементов ИЛИ 33.1-33.m соответственно, третьи групповые выходы блоков 18.1-18.р управления синхронизацией соединены с групповыми входами элемента ИЛИ 14 с первого по р-й соответственно, выходы элементов ИЛИ 32.1-32.m являются выходами 56.1-56.m модуля соответственно, а выходы элементов ИЛИ 33.1-33.m являются выходами 57.1-57.m модуля соответственно.

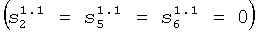

Блок 18.i управления синхронизацией (фиг.2),  , содержит барьерные блоки 34.1-34.m, причем с первого по m-й разряды первого, второго, третьего, восьмого и девятого входов блока управления синхронизацией соединены с первым, вторым, третьим, восьмым и девятым входами барьерных блоков 34.1-34.m соответственно, четвертый, пятый, шестой и седьмой входы блока управления синхронизацией соединены соответственно с четвертым, пятым, шестым и седьмым входами барьерных блоков 34.1-34.m, первый, второй и третий выходы барьерных блоков 34.1-34.m соединены с первого по m-й разрядами первого, второго и третьего групповых выходов блока управления синхронизацией соответственно.

, содержит барьерные блоки 34.1-34.m, причем с первого по m-й разряды первого, второго, третьего, восьмого и девятого входов блока управления синхронизацией соединены с первым, вторым, третьим, восьмым и девятым входами барьерных блоков 34.1-34.m соответственно, четвертый, пятый, шестой и седьмой входы блока управления синхронизацией соединены соответственно с четвертым, пятым, шестым и седьмым входами барьерных блоков 34.1-34.m, первый, второй и третий выходы барьерных блоков 34.1-34.m соединены с первого по m-й разрядами первого, второго и третьего групповых выходов блока управления синхронизацией соответственно.

Барьерный блок 34.j,  , каждого блока управления синхронизацией (фиг.2) содержит элемент ИЛИ 35, первый 36, второй 39 и третий 40 элементы И, триггер 37, элемент И-НЕ 38, причем первый вход барьерного блока подключен к первому входу элемента И 36, второй вход которого соединен с выходом элемента ИЛИ 35, первый и второй входы которого являются вторым и третьим входами барьерного блока соответственно, четвертый вход которого подключен к третьему входу элемента И 36, выход которого соединен с информационным входом триггера 37 признака завершения барьера, а также является первым выходом барьерного блока, пятый вход которого подключен к входу синхронизации триггера 37 признака завершения барьера, инверсный выход которого соединен с первым входом элемента И-НЕ 38, второй вход которого является шестым входом барьерного блока, а выход подключен к первому входу элемента И 39, выход которого является вторым выходом барьерного блока, седьмой и восьмой входы которого соединены со вторым и третьим входами элемента И 39 соответственно, выход которого подключен к первому входу элемента И 40, второй вход и выход которого являются девятым входом и третьим выходом барьерного блока соответственно.

, каждого блока управления синхронизацией (фиг.2) содержит элемент ИЛИ 35, первый 36, второй 39 и третий 40 элементы И, триггер 37, элемент И-НЕ 38, причем первый вход барьерного блока подключен к первому входу элемента И 36, второй вход которого соединен с выходом элемента ИЛИ 35, первый и второй входы которого являются вторым и третьим входами барьерного блока соответственно, четвертый вход которого подключен к третьему входу элемента И 36, выход которого соединен с информационным входом триггера 37 признака завершения барьера, а также является первым выходом барьерного блока, пятый вход которого подключен к входу синхронизации триггера 37 признака завершения барьера, инверсный выход которого соединен с первым входом элемента И-НЕ 38, второй вход которого является шестым входом барьерного блока, а выход подключен к первому входу элемента И 39, выход которого является вторым выходом барьерного блока, седьмой и восьмой входы которого соединены со вторым и третьим входами элемента И 39 соответственно, выход которого подключен к первому входу элемента И 40, второй вход и выход которого являются девятым входом и третьим выходом барьерного блока соответственно.

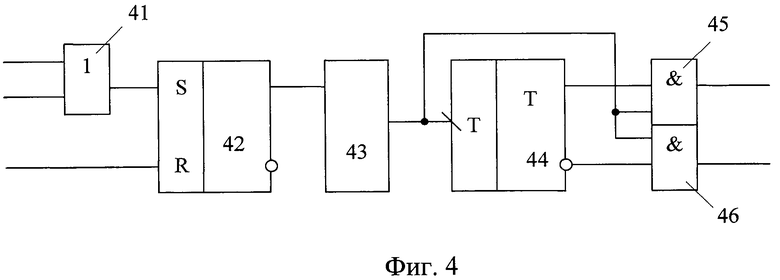

Схема блока 10 синхронизации (фиг.4) не отличается от прототипа.

Общие особенности функциональной организации предлагаемого логического мультиконтроллера с распределенным параллельно-конвейерным барьерным синхронизатором состоят в следующем.

Логический мультиконтроллер (ЛМК) формируется из множества однотипных модулей (контроллеров), объединенных в матричную структуру (фиг.3). Каждый модуль ЛМК содержит перепрограммируемую память программ и имеет множество входных и выходных каналов, предназначенных для подключения к другим аналогичным модулям и обмена управляющей информацией. Модули идентифицируются условными номерами вида i.j, где i и j имеют смысл соответственно номера строки и номера столбца матричной структуры, на пересечении которых находится данный модуль, «.» - символ конкатенации (в дальнейшем модуль с номером i.j именуется также как (i.j)-й модуль или модуль mi,j).

Мультиконтроллер служит для управления сложными объектами, поведение которых описывается комплексом программ и предполагает параллельное протекание и взаимодействие множества процессов. Комплекс программ, реализуемый мультиконтроллером, разбивается на множество параллельных и последовательных участков (ветвей), которые распределяются между различными модулями. Каждый модуль реализует некоторое подмножество участков.

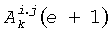

В процессе выполнения участков программ модули ЛМК обрабатывают команды двух типов: операционные и коммуникационные. Операционные команды (эти команды имеют формат Ф2, см. фиг.5) обеспечивают выдачу управляющих воздействий на объект управления и инициируют исполнение требуемых микроопераций. Коммуникационные команды (формат Ф3, см. фиг.5) служат для организации взаимодействия и координации различных модулей, включая запуск участков, закрепленных за другими модулями (межмодульную передачу управления), и барьерную синхронизацию.

Как и в прототипе, в рассматриваемом ЛМК межмодульная передача управления в явном виде (т.е. с обменом адресами перехода) отсутствует, фактически выполняется только процедура барьерной синхронизации. При этом запуск участков программ, реализуемых различными модулями, происходит при выполнении соответствующих условий синхронизации. Например, при запуске участков, непосредственно следующих за множеством других (параллельных) участков, является завершение всех участков данного множества (условие достижения барьера). При запуске участков, следующих за единственным участком, в качестве условия выступает завершение этого единственного участка.

Для задания момента активизации некоторого участка  (где e - порядковый номер данного участка для (i.j)-го модуля, k - номер программы) этому участку ставится в соответствие номер непосредственно предшествующей ему вершины синхронизации (далее в описании - барьера) a

t; если активизируемому участку непосредственно предшествует единственный участок программы, то барьер a

t считается фиктивным. Запуск участка

(где e - порядковый номер данного участка для (i.j)-го модуля, k - номер программы) этому участку ставится в соответствие номер непосредственно предшествующей ему вершины синхронизации (далее в описании - барьера) a

t; если активизируемому участку непосредственно предшествует единственный участок программы, то барьер a

t считается фиктивным. Запуск участка  происходит после выполнения барьера a

t, т.е. как только завершаются все непосредственно предшествующие ему участки программы.

происходит после выполнения барьера a

t, т.е. как только завершаются все непосредственно предшествующие ему участки программы.

Как и в прототипе, в предлагаемом ЛМК адреса приема управления формируются непосредственно модулями, реализующими запускаемые участки (модулями - приемниками управления), в результате самонастройки. Адрес  начала следующего ((е+1)-го) участка, выполняемого (i.j)-м модулем, указывается в заключительной команде предшествующего (е-го) участка программы. Для задания адресов начальных участков модулей

начала следующего ((е+1)-го) участка, выполняемого (i.j)-м модулем, указывается в заключительной команде предшествующего (е-го) участка программы. Для задания адресов начальных участков модулей  используются команды настройки формата Ф1 (фиг.5), где «НВС» означает «номер вершины синхронизации», т.е. номер барьера. За каждым модулем ЛМК закрепляется Q таких команд, Q - число программ, реализуемых мультиконтроллером (число программ в реализуемом комплексе). Каждая из Q команд настройки определяет адрес

используются команды настройки формата Ф1 (фиг.5), где «НВС» означает «номер вершины синхронизации», т.е. номер барьера. За каждым модулем ЛМК закрепляется Q таких команд, Q - число программ, реализуемых мультиконтроллером (число программ в реализуемом комплексе). Каждая из Q команд настройки определяет адрес  первой команды, выполняемой (i.j)-м модулем при реализации k-й программы, т.е. адрес начального участка (i.j)-го модуля. Отметим, что если (i.j)-й модуль не участвует в процессе выполнения k-й программы, то команда Ф1 полностью состоит из нулей. Команды настройки Ф1 размещаются в блоке 1 памяти программ (фиг.1) по начальным адресам от 1 до Q включительно. Команда настройки, а следовательно, и реализуемая программа однозначно задается адресом при обращении к блоку 1.

первой команды, выполняемой (i.j)-м модулем при реализации k-й программы, т.е. адрес начального участка (i.j)-го модуля. Отметим, что если (i.j)-й модуль не участвует в процессе выполнения k-й программы, то команда Ф1 полностью состоит из нулей. Команды настройки Ф1 размещаются в блоке 1 памяти программ (фиг.1) по начальным адресам от 1 до Q включительно. Команда настройки, а следовательно, и реализуемая программа однозначно задается адресом при обращении к блоку 1.

Процесс синхронизации параллельных участков в предлагаемом ЛМК осуществляется на основе распространения и опроса сигналов завершения множества параллельных участков. Каждый такой сигнал распространяется в отдельном канале (слое) синхронизации, который соответствует одному барьеру. Слой синхронизации представляет собой совокупность элементов (барьерных блоков) различных модулей ЛМК и соответствующих связей, обеспечивающих протекание процесса синхронизации определенного множества параллельных участков.

Как и в прототипе, в рассматриваемом ЛМК слои синхронизации разбиты на группы. Однако, в отличие от прототипа, в котором в один момент времени может работать только одна группа слоев, внутри которой сигналы синхронизации различных барьеров распространяются независимо и параллельно, в предлагаемом техническом решении в один момент времени активны две группы слоев. Смена групп происходит циклически.

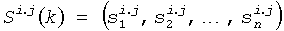

Для обеспечения синхронизации произвольных множеств параллельных участков за каждым модулем ЛМК закрепляется вектор, задающий соответствие между множеством барьеров программы и данным модулем. (i.j)-му модулю мультиконтроллера,  ,

,  , в общем случае соответствует Q различных векторов, каждый из которых отвечает определенной программе. Вектор соответствия для (i.j)-го модуля и k-й программы имеет вид

, в общем случае соответствует Q различных векторов, каждый из которых отвечает определенной программе. Вектор соответствия для (i.j)-го модуля и k-й программы имеет вид

,

,

где  , nk - число барьеров в k-й программе.

, nk - число барьеров в k-й программе.

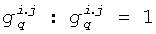

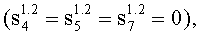

Значение компоненты вектора Si.j(k) определяется следующим образом:  , если за (i.j)-м модулем ЛМК закреплен некоторый участок программы, завершающийся q-м барьером;

, если за (i.j)-м модулем ЛМК закреплен некоторый участок программы, завершающийся q-м барьером;  , если (i.j)-й модуль ЛМК не реализует ни одного участка, завершающегося q-м барьером, или q-й барьер отсутствует в k-й программе (что возможно при nk<q).

, если (i.j)-й модуль ЛМК не реализует ни одного участка, завершающегося q-м барьером, или q-й барьер отсутствует в k-й программе (что возможно при nk<q).

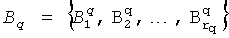

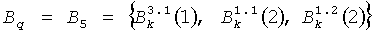

Синхронизация множества участков  , завершающихся q-м барьером, осуществляется на основе распространения сигнала dq завершения множества участков в q-м слое синхронизации. Сигнал dq формируется (1.N)-м (правым верхним) модулем ЛМК (см. фиг.3). В исходном состоянии dq=0 (параллельные участки не завершены) и, следовательно,

, завершающихся q-м барьером, осуществляется на основе распространения сигнала dq завершения множества участков в q-м слое синхронизации. Сигнал dq формируется (1.N)-м (правым верхним) модулем ЛМК (см. фиг.3). В исходном состоянии dq=0 (параллельные участки не завершены) и, следовательно,  .

.

Процесс барьерной синхронизации включает две фазы: формирование признака завершения синхронизируемых участков и передачу этого признака всем модулям ЛМК.

Первая из указанных фаз начинается с формирования номера активной группы слоев uq, в которой находится q-й слой синхронизации. Таким образом, происходит включение группы слоев uq и выполнение синхронизации соответствующих множеств параллельных участков. После этого единичный сигнал  распространяется от (1.N)-го модуля вниз и влево через все модули ЛМК ко всем крайним левым и крайним нижним модулям вплоть до (М.1)-го модуля ЛМК (см. фиг.3).

распространяется от (1.N)-го модуля вниз и влево через все модули ЛМК ко всем крайним левым и крайним нижним модулям вплоть до (М.1)-го модуля ЛМК (см. фиг.3).

Распространение сигнала  через (i.j)-й модуль ЛМК происходит следующим образом. Если

через (i.j)-й модуль ЛМК происходит следующим образом. Если  , то появление единичных сигналов

, то появление единичных сигналов  на верхнем и правом входах (i.j)-го модуля обусловливает формирование единичного сигнала

на верхнем и правом входах (i.j)-го модуля обусловливает формирование единичного сигнала  на его выходе. Если

на его выходе. Если  , то формирование единичного сигнала

, то формирование единичного сигнала  на выходе (i.j)-го модуля происходит только при условии завершения участка

на выходе (i.j)-го модуля происходит только при условии завершения участка  сходящегося к q-му барьеру и реализуемого (i.j)-м модулем ЛМК.

сходящегося к q-му барьеру и реализуемого (i.j)-м модулем ЛМК.

Состояние участка  определяется значением сигнала - признака

определяется значением сигнала - признака  , если участок

, если участок  завершен;

завершен;  в противном случае. В случае если участок

в противном случае. В случае если участок  не завершен, на выходе (i.j)-го модуля устанавливается нулевой сигнал. Данный сигнал формирует нулевые сигналы на выходах всех модулей ЛМК, расположенных не выше и не правее (i.j)-го модуля. На входе (М.1)-го (левого нижнего) модуля (см. фиг.3), соответственно, также будет нулевой сигнал. Как только происходит завершение участка

не завершен, на выходе (i.j)-го модуля устанавливается нулевой сигнал. Данный сигнал формирует нулевые сигналы на выходах всех модулей ЛМК, расположенных не выше и не правее (i.j)-го модуля. На входе (М.1)-го (левого нижнего) модуля (см. фиг.3), соответственно, также будет нулевой сигнал. Как только происходит завершение участка  , единичный сигнал

, единичный сигнал  передается на выход (i.j)-го модуля и поступает в (i+1.j)-й и (i.j-1)-й модули.

передается на выход (i.j)-го модуля и поступает в (i+1.j)-й и (i.j-1)-й модули.

После завершения всех параллельных участков множества Bq единичный сигнал  пройдет на входы (М.1)-го модуля ЛМК и с помощью импульса управления зафиксируется в этом модуле. На выходе (М.1)-го модуля ЛМК, таким образом, будет сформирован сигнал dq=1, сообщающий об окончании синхронизируемых параллельных участков. На этом первая фаза синхронизации завершается.

пройдет на входы (М.1)-го модуля ЛМК и с помощью импульса управления зафиксируется в этом модуле. На выходе (М.1)-го модуля ЛМК, таким образом, будет сформирован сигнал dq=1, сообщающий об окончании синхронизируемых параллельных участков. На этом первая фаза синхронизации завершается.

Вторая фаза синхронизации начинается с переключения всех модулей ЛМК на группу слоев uq, в которой находится q-й слой синхронизации, и появления на выходе (М.1)-го модуля единичного сигнала dq. Этот сигнал распространяется (фиг.3) от (М.1)-го модуля вверх и вправо через ЛМК ко всем крайним правым и крайним верхним модулям до модуля с номером (1.N). В процессе распространения сигнала происходит запуск модулей ЛМК, ожидающих завершения параллельных участков множества Bq. Вторая фаза и процесс синхронизации параллельных участков в целом завершаются после появления нулевого сигнала на выходе (1.N)-го модуля и переключения на следующую группу слоев синхронизации.

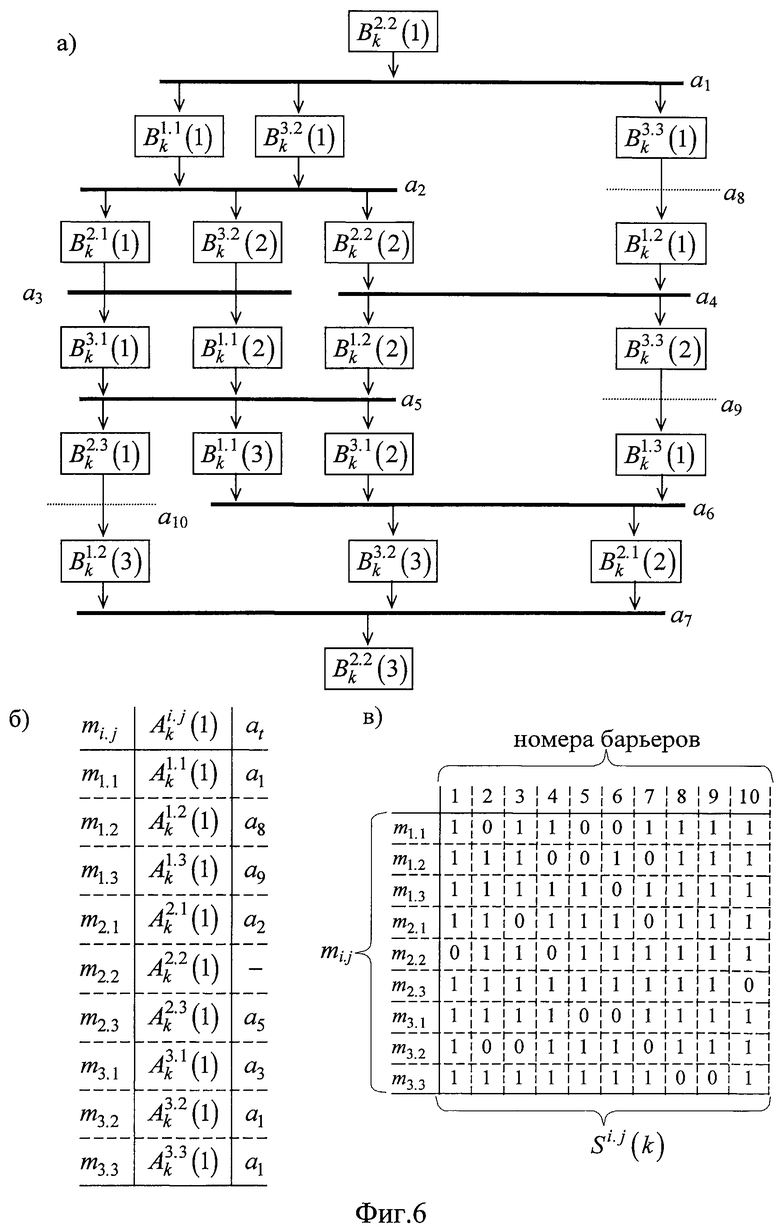

Принципы организации межмодульной передачи управления и синхронизации параллельных участков в предлагаемом ЛМК поясняются примером реализации параллельного алгоритма логического управления, представленного на фиг.6а. Алгоритм включает 20 параллельных и последовательных участков  , принадлежность которых определенному модулю задается верхним индексом i.j. В рассматриваемый алгоритм входят барьеры а

1, а

2,…, а

10; барьеры а

8, а

9, a

10 (показанные пунктиром) являются фиктивными, поскольку им соответствуют переходы между отдельными участками. Пары барьеров а

2 и а

8, а

3 и а

4, а

5 и а

9, a

10 и а

6 являются параллельными и синхронизируются независимо. ЛМК, реализующий данный алгоритм, имеет вид матрицы с конфигурацией 3×3 модуля.

, принадлежность которых определенному модулю задается верхним индексом i.j. В рассматриваемый алгоритм входят барьеры а

1, а

2,…, а

10; барьеры а

8, а

9, a

10 (показанные пунктиром) являются фиктивными, поскольку им соответствуют переходы между отдельными участками. Пары барьеров а

2 и а

8, а

3 и а

4, а

5 и а

9, a

10 и а

6 являются параллельными и синхронизируются независимо. ЛМК, реализующий данный алгоритм, имеет вид матрицы с конфигурацией 3×3 модуля.

Таблица настройки модулей, определяющая адреса начальных участков  , а также номера барьеров a

t, после достижения которых должен быть обеспечен запуск соответствующих модулей, представлены на фиг.6б. В соответствии с данной таблицей запуск модулей m1.1, m3.2 и m3.3 происходит после выполнения барьера а

1, т.е. после завершения участка

, а также номера барьеров a

t, после достижения которых должен быть обеспечен запуск соответствующих модулей, представлены на фиг.6б. В соответствии с данной таблицей запуск модулей m1.1, m3.2 и m3.3 происходит после выполнения барьера а

1, т.е. после завершения участка  , запуск модуля m1.2 осуществляется после достижения барьера а

8, т.е. после завершения участка

, запуск модуля m1.2 осуществляется после достижения барьера а

8, т.е. после завершения участка  , и т.д. Модуль m2,2 активизируется непосредственно в момент запуска ЛМК независимо от состояния других модулей, поскольку реализует начальный последовательный участок алгоритма

, и т.д. Модуль m2,2 активизируется непосредственно в момент запуска ЛМК независимо от состояния других модулей, поскольку реализует начальный последовательный участок алгоритма  .

.

Таблица векторов соответствия для рассматриваемого алгоритма показана на фиг.6в. Согласно данной таблице модуль m1.1 реализует участки, завершающиеся в барьерах а

2, а

5 и a

6

, модуль m1,2 - участки, сходящиеся в барьерах а

4, а

5 и a

7

, модуль m1,2 - участки, сходящиеся в барьерах а

4, а

5 и a

7  и т.д.

и т.д.

Более подробно процессы синхронизации и запуска параллельных участков описываются далее при рассмотрении функционирования ЛМК.

Назначение элементов и блоков модуля логического мультиконтроллера (фиг.1) с 1 по 17 не отличается от прототипа.

Назначение остальных элементов и блоков сводится к следующему.

Блок 18.i управления синхронизацией,  , служит для группировки однотипных барьерных блоков 34.j (фиг.2),

, служит для группировки однотипных барьерных блоков 34.j (фиг.2),  , и организационно является ячейкой i-й группы слоев синхронизации (группы барьеров).

, и организационно является ячейкой i-й группы слоев синхронизации (группы барьеров).

Группа элементов И 19.1-19.m (фиг.1) служит для организации распространения сигналов опроса состояния множеств параллельных участков от соседних модулей, расположенных сверху и справа от текущего.

Группа элементов И 20.1-20.m предназначена для организации распространения сигналов запуска модулей, ожидающих завершения соответствующих множеств параллельных участков, от соседних модулей слева и снизу от текущего.

Триггер 21 конфигурации служит для хранения признака (флага) позиции модуля (его значение равно «1» только для нижнего левого, т.е. (M.1)-го модуля).

Элемент И 22, элементы ИЛИ 23, 30, триггер 24, элементы задержки 25 и 31 предназначены для формирования сигнала управления переключением групп слоев синхронизации (блоков управления синхронизацией).

Счетчики 26, 27 номера активной группы служат для перебора групп слоев синхронизации (блоков управления синхронизацией), в которых в данный момент происходят формирование признака синхронизации и запуск ожидающих модулей ЛМК соответственно.

Дешифраторы 28, 29 номера активной группы предназначены для активизации групп слоев синхронизации (блоков управления синхронизацией) в зависимости от значения счетчиков 26, 27.

Группа элементов ИЛИ 32.1-32.m служит для формирования и выдачи сигнала синхронизации влево и вниз от текущего модуля.

Группа элементов ИЛИ 33.1-33.m предназначена для передачи сигнала завершения барьера вправо и вверх от текущего модуля.

Барьерный блок 34.i,  , предназначен для управления прохождением сигналов завершения множества параллельных участков и активизации модулей ЛМК для одного из барьеров (организационно этот блок является ячейкой одного слоя управления синхронизацией).

, предназначен для управления прохождением сигналов завершения множества параллельных участков и активизации модулей ЛМК для одного из барьеров (организационно этот блок является ячейкой одного слоя управления синхронизацией).

Назначение элементов барьерного блока 34.i (фиг.2),  , состоит в следующем.

, состоит в следующем.

Элемент ИЛИ 35.i совместно с элементом И 36.i управляют распространением сигнала опроса состояния барьера в зависимости от состояния текущего модуля ЛМК.

Триггер 37.i служит для фиксации и хранения текущего значения признака завершения соответствующего барьера.

Элемент И-НЕ 38.i разрешает/запрещает считывание значения из триггера 37.i в зависимости от расположения модуля ЛМК в структуре мультиконтроллера.

Элемент И 39.i управляет распространением сигнала запуска модулей ЛМК, ожидающих завершения соответствующего множества параллельных участков.

Элемент И 40.i предназначен для формирования сигнала запуска для текущего модуля ЛМК.

Рассмотрим процесс функционирования ЛМК подробно.

Первоначально элементы памяти (регистры, триггеры и счетчики) всех модулей ЛМК находятся в состоянии логического нуля. Исключение составляет только регистр 3, на выходе 3.8 которого находится единичный уровень сигнала, и триггер 44 блока 10 синхронизации (фиг.4). На входах 52 модулей (i.N),  , входах 53 модулей (1.i),

, входах 53 модулей (1.i),  , входах 54 модулей (i.1),

, входах 54 модулей (i.1),  , входах 55 модулей (M.i),

, входах 55 модулей (M.i),  , (фиг.1, 3) также установлены сигналы высокого уровня. Исходя из указанного состояния элементов памяти блоки 10 синхронизации всех модулей выключены, коммутаторы 6 настроены на прием информации с входов 49, а на всех выходах модулей находятся сигналы логического нуля. Цепи приведения элементов памяти модуля в исходное состояние для упрощения на фиг.1, 2 условно не показаны.

, (фиг.1, 3) также установлены сигналы высокого уровня. Исходя из указанного состояния элементов памяти блоки 10 синхронизации всех модулей выключены, коммутаторы 6 настроены на прием информации с входов 49, а на всех выходах модулей находятся сигналы логического нуля. Цепи приведения элементов памяти модуля в исходное состояние для упрощения на фиг.1, 2 условно не показаны.

Перед началом работы происходит конфигурирование ЛМК. Для этого через вход 58 (М.1)-го (нижнего левого) модуля (фиг.1, 3) на информационный вход триггера 21 передается единичный сигнал и фиксируется в нем по заднему фронту импульса, пришедшего с входа 59 (М.1)-го модуля. Единичное значение в триггере 21 указывает, что данный модуль является в структуре ЛМК нижним левым. В триггерах 21 остальных модулей остается нулевое значение. Одновременно во всех модулях происходит запись кода «0…01» в счетчики 27. Для этого код «0…01» подается на входы 65 модулей, а на входы 66 модулей подается импульс, который фиксирует указанный код в счетчиках 27. В счетчиках 26 всех модулей при этом сохраняется нулевое значение. На этом процесс конфигурирования ЛМК заканчивается.

По завершении конфигурирования начинается настройка модулей ЛМК на выполнение требуемой (k-й) программы. Настройка (i.j)-го модуля на выполнение k-й программы сводится к установлению адреса первой выполняемой команды  , а также к определению номера барьера a

t, после достижения которого должен осуществляться запуск этого модуля.

, а также к определению номера барьера a

t, после достижения которого должен осуществляться запуск этого модуля.

Настройка (i.j)-го модуля начинается с подачи на его вход 49 (фиг.1) кода операции. Код операции (КОП), представляющий собой код номера выполняемой программы (k), через коммутатор 6 передается на информационный вход регистра 2. Одновременно на вход 50 (i.j)-го модуля подается импульс настройки. Указанный импульс через элемент ИЛИ 12 поступает на вход синхронизации регистра 2 и задним фронтом фиксирует КОП в данном регистре. Далее КОП с выхода регистра 2 подается на адресный вход блока 1 и формирует на его выходе команду настройки формата Ф1 (фиг.5), соответствующую k-й программе.

В то же самое время импульс настройки через элемент 17 задержки и элемент ИЛИ 13 (фиг.1) передается на вход синхронизации регистра 3 и задним фронтом производит запись считанной из блока 1 команды в регистр 3. После фиксации команды на выходах 3.2 и 3.3 регистра 3 образуется адрес  , а на выходе 3.6 формируется код номера (t) барьера (НВС) a

t. На остальных выходах регистра 3 устанавливается нулевой уровень сигнала. Отметим, что для модуля ЛМК, реализующего начальный участок k-й программы, задание кода НВС не требуется, поскольку этот модуль активизируется непосредственно в момент запуска мультиконтроллера независимо от условий синхронизации. Поэтому на выходе 3.6 регистра 3 (фиг.1, 3) рассматриваемого модуля устанавливается нулевой код.

, а на выходе 3.6 формируется код номера (t) барьера (НВС) a

t. На остальных выходах регистра 3 устанавливается нулевой уровень сигнала. Отметим, что для модуля ЛМК, реализующего начальный участок k-й программы, задание кода НВС не требуется, поскольку этот модуль активизируется непосредственно в момент запуска мультиконтроллера независимо от условий синхронизации. Поэтому на выходе 3.6 регистра 3 (фиг.1, 3) рассматриваемого модуля устанавливается нулевой код.

Нулевой сигнал с выхода 3.8 регистра 3 перенастраивает коммутатор 6 на прием информации с выхода блока элементов ИЛИ 11. Поскольку на выходе 3.1 регистра 3 присутствует нулевой код (проверка логических условий в ходе настройки не производится), адрес  без изменений передается через блок элементов ИЛИ 11. Далее этот адрес проходит через коммутатор 6 и устанавливается на информационном входе регистра 2.

без изменений передается через блок элементов ИЛИ 11. Далее этот адрес проходит через коммутатор 6 и устанавливается на информационном входе регистра 2.

Одновременно производится запись в регистр 5 значения вектора соответствия Si.j(k) (устанавливается соответствие между (i.j)-м модулем и множеством барьеров k-й программы). Вектор Si.j(k) подается на вход 48 модуля и по заднему фронту импульса настройки с входа 50 модуля заносится в регистр 5.

Параллельно с описанными действиями код номера барьера a t с выхода 3.6 регистра 3 подается на вход дешифратора 9. В результате на t-м выходе дешифратора 9 появляется единичный сигнал. Этот сигнал проходит в блок 18.ut управления синхронизацией, отвечающий за синхронизацию t-го барьера, и далее поступает в барьерный блок 34.c(ut) (фиг.2), непосредственно обеспечивающий синхронизацию t-го барьера, где с(ut) - порядковый номер барьерного блока внутри блока 18.ut управления синхронизацией. В барьерном блоке 34.с(ut) данный единичный сигнал открывает элемент И 40.c(ut), тем самым обеспечивая возможность последующего опроса уровня сигнала на выходе элемента И 39.c(ut), соответствующего состоянию t-го барьера.

На этом процесс настройки (i.j)-го модуля на выполнение k-й программы завершается. Аналогичным образом протекает настройка остальных модулей ЛМК, причем настройка различных модулей выполняется параллельно. На входы 49 всех модулей подается один и тот же КОП; однако векторы соответствия для разных модулей в общем случае различны. В результате настройки для каждого модуля определяется момент его запуска при выполнении мультиконтроллером k-й программы, задается соответствующий адрес первой команды и, кроме того, устанавливается подмножество барьеров k-й программы, в которых завершаются участки, реализуемые модулем.

После завершения настройки осуществляется запуск ЛМК. Для запуска ЛМК на вход 51 одного из его модулей, а именно модуля, реализующего начальный участок k-й программы, подается импульс пуска (фиг.1). Допустим, что указанный модуль имеет номер (i.j) (в примере на фиг.6 это модуль m2.2). Импульс пуска со входа 51 (i.j)-го модуля передается на первый вход блока 10 синхронизации. Далее этот импульс проходит (фиг.4) через элемент ИЛИ 41, воздействует на вход установки триггера 42 и переводит этот триггер в единичное состояние. Единичный сигнал с прямого выхода триггера 42 поступает на вход генератора 43 и разрешает формирование на его выходе последовательности импульсов.

Первый импульс с выхода генератора 43 проходит через элемент И 45 на первый выход блока синхронизации (элемент 45 открыт единичным сигналом с прямого выхода триггера 44). По заднему фронту этого же импульса триггер 44 переключается в нулевое состояние. В результате происходит блокировка элемента И 45 и открытие элемента И 46. Второй импульс с выхода генератора 43 через открытый элемент 46 проходит на второй выход блока синхронизации. Задний фронт данного импульса вновь возвращает триггер 44 в исходное (единичное) состояние. Третий импульс снова проходит на первый выход блока синхронизации, а четвертый импульс - на второй выход и т.д. Таким образом, на выходах блока 10 синхронизации начинается генерация двух сдвинутых друг относительно друга последовательностей импульсов синхронизации t1 и t2.

Первый импульс t1 с первого выхода блока 10 синхронизации (фиг.1) через элемент ИЛИ 12 проходит на вход синхронизации регистра 2 и фиксирует в данном регистре адрес  , поступающий с выхода коммутатора 6. Адрес

, поступающий с выхода коммутатора 6. Адрес  с выхода регистра 2 поступает на адресный вход блока 1 и формирует на его выходе первую команду k-й программы.

с выхода регистра 2 поступает на адресный вход блока 1 и формирует на его выходе первую команду k-й программы.

Первый импульс t2 со второго выхода блока 10 синхронизации проходит через элемент ИЛИ 13 и, поступая затем на вход синхронизации регистра 3, записывает в этот регистр команду, считанную из блока 1. Одновременно этот же импульс подается на вход сброса буферного регистра 7 и подтверждает его нулевое состояние. Таким образом, (i.j)-й модуль и ЛМК в целом начинают исполнение k-й программы.

Дальнейшее функционирование ЛМК будем рассматривать в предположении, что (i.j)-й модуль выполняет некоторый (в общем случае не начальный) участок k-й программы, например участок  , завершающийся барьером a

q. Кроме того, будем считать, что одновременно с (i.j)-м модулем могут функционировать и некоторые другие модули ЛМК (остальные модули находятся в пассивном состоянии или в состоянии ожидания).

, завершающийся барьером a

q. Кроме того, будем считать, что одновременно с (i.j)-м модулем могут функционировать и некоторые другие модули ЛМК (остальные модули находятся в пассивном состоянии или в состоянии ожидания).

Как и в прототипе, в процессе выполнения участка  (i.j)-й модуль может обрабатывать команды форматов Ф2, Ф3 или Ф4 (фиг.5). Обработка команды формата Ф2 соответствует режиму собственно выполнения участка программы (режим А), команда Ф3 определяет режим завершения участка программы и перехода в состояние ожидания запуска (режим В), а команда Ф4 задает режим завершения программы в целом (режим С). Рассмотрим работу модуля в каждом из названных режимов.

(i.j)-й модуль может обрабатывать команды форматов Ф2, Ф3 или Ф4 (фиг.5). Обработка команды формата Ф2 соответствует режиму собственно выполнения участка программы (режим А), команда Ф3 определяет режим завершения участка программы и перехода в состояние ожидания запуска (режим В), а команда Ф4 задает режим завершения программы в целом (режим С). Рассмотрим работу модуля в каждом из названных режимов.

Режим А. Записанная в регистр 3 команда имеет формат Ф2 (фиг.5). В этом случае на выходе 3.4 регистра 3 (фиг.1) формируется код микроопераций (МО), на выходах 3.2 и 3.3 образуется адрес следующей команды Асл (на выходе 3.3 - немодифицируемая часть, а на выходе 3.2 - модифицируемый разряд адреса следующей команды, изменяемый в точках ветвления программ), на выходе 3.1 устанавливается код опрашиваемого логического условия (ЛУ), а на выходах 3.5-3.8 появляются сигналы логического нуля.

Код МО с выхода 3.4 регистра 3 передается на выход 69 модуля и, поступая далее на вход объекта управления, инициирует выполнение требуемых микроопераций. Нулевые сигналы с выходов 3.5 и 3.6 регистра 3 воздействуют на входы дешифраторов 8 и 9 соответственно и формируют на всех их выходах нулевые сигналы. Нулевой сигнал с выхода 3.8 регистра 3 поступает на управляющие входы коммутатора 6 и настраивает его на прием адреса следующей команды с выхода блока элементов ИЛИ 11.

Одновременно с описанными действиями происходит формирование исполнительного адреса следующей команды. Указанный адрес образуется из адреса следующей команды Асл путем замещения его модифицируемого (младшего) разряда значением опрашиваемого ЛУ. Новое значение младшего разряда формируется на выходе мультиплексора 4. Процесс формирования этого значения протекает следующим образом. Модифицируемый разряд (AM) адреса Асл с выхода 3.2 регистра 3 подается на первый информационный вход мультиплексора 4, а код ЛУ с выхода 3.1 поступает на адресный вход мультиплексора 4. Если код ЛУ отличен от нулевого, то на выход мультиплексора 4 передается значение соответствующего ЛУ с входа 47 модуля. Если же код ЛУ нулевой, то на выход мультиплексора 4 поступает значение АМ с выхода 3.2 регистра 3. Значение с выхода мультиплексора 4 в объединении с немодифицируемой (старшей) частью адреса следующей команды (АН) с выхода 3.3 регистра 3 образует исполнительный адрес следующей команды  .

.

Адрес  через блок элементов ИЛИ 11 и открытый коммутатор 6 проходит на информационный вход регистра 2. Очередной импульс синхронизации t1 с первого выхода блока 10 синхронизации фиксирует адрес

через блок элементов ИЛИ 11 и открытый коммутатор 6 проходит на информационный вход регистра 2. Очередной импульс синхронизации t1 с первого выхода блока 10 синхронизации фиксирует адрес  в регистре 2. Адрес

в регистре 2. Адрес  с выхода регистра 2 поступает на адресный вход блока 1 и обеспечивает считывание из блока 1 очередной команды k-й программы. Следующий импульс t2 со второго выхода блока 10 синхронизации через элемент ИЛИ 13 подается на вход синхронизации регистра 3 и записывает в этот регистр считанную команду.

с выхода регистра 2 поступает на адресный вход блока 1 и обеспечивает считывание из блока 1 очередной команды k-й программы. Следующий импульс t2 со второго выхода блока 10 синхронизации через элемент ИЛИ 13 подается на вход синхронизации регистра 3 и записывает в этот регистр считанную команду.

На этом работа (i.j)-го модуля в режиме А заканчивается. Считанная команда снова может иметь формат Ф2 либо может быть командой формата Ф3 или Ф4.

Режим B. Записанная в регистр 3 команда имеет формат Ф3 (фиг.5). В этом случае (i.j)-й модуль завершает выполнение некоторого участка  , производит самонастройку на реализацию очередного участка k-й программы и переходит в состояние ожидания. В ходе самонастройки (i.j)-й модуль устанавливает адрес

, производит самонастройку на реализацию очередного участка k-й программы и переходит в состояние ожидания. В ходе самонастройки (i.j)-й модуль устанавливает адрес  начала очередного ((е+1)-го) участка

начала очередного ((е+1)-го) участка  (здесь е - порядковый номер участка

(здесь е - порядковый номер участка  для (i.j)-го модуля) и фиксирует номер (t) барьера a

t (после достижения которого должен осуществляться запуск (i.j)-го модуля).

для (i.j)-го модуля) и фиксирует номер (t) барьера a

t (после достижения которого должен осуществляться запуск (i.j)-го модуля).

На выходе 3.7 регистра 3 появляется единичная метка конца участка программы (Мку), индицирующая формат считанной команды, на выходах 3.2 и 3.3 регистра 3 формируется адрес  , на выходе 3.1 образуется код ЛУ, а на выходах 3.4 и 3.8 устанавливаются сигналы логического нуля. В то же время на выходах 3.5 и 3.6 регистра 3 формируются коды номеров барьеров: на выходе 3.5 - номер (q) барьера a

q, завершающего выполненный модулем участок

, на выходе 3.1 образуется код ЛУ, а на выходах 3.4 и 3.8 устанавливаются сигналы логического нуля. В то же время на выходах 3.5 и 3.6 регистра 3 формируются коды номеров барьеров: на выходе 3.5 - номер (q) барьера a

q, завершающего выполненный модулем участок  ; на выходе 3.6 - номер (t) барьера a

t, определяющего момент очередного запуска (i.j)-го модуля (допустимым является случай, когда t=q).

; на выходе 3.6 - номер (t) барьера a

t, определяющего момент очередного запуска (i.j)-го модуля (допустимым является случай, когда t=q).

В примере на фиг.6 после выполнения участка  на выходе 3.5 регистра 3 модуля m2.2 будет сформирован номер барьера а

1, на выходе 3.6 будет установлен номер барьера а

2, за которым следует очередной участок

на выходе 3.5 регистра 3 модуля m2.2 будет сформирован номер барьера а

1, на выходе 3.6 будет установлен номер барьера а

2, за которым следует очередной участок  , выполняемый модулем m2.2. Адрес начала этого участка

, выполняемый модулем m2.2. Адрес начала этого участка  будет зафиксирован на выходах 3.2 и 3.3 регистра 3. После завершения участка

будет зафиксирован на выходах 3.2 и 3.3 регистра 3. После завершения участка  на выходе 3.5 регистра 3 модуля m2.2 будет установлен НВС a

4, а на выходе 3.6 - НВС a

7, за которой следует очередной участок модуля m2.2 - участок

на выходе 3.5 регистра 3 модуля m2.2 будет установлен НВС a

4, а на выходе 3.6 - НВС a

7, за которой следует очередной участок модуля m2.2 - участок  Аналогичным образом происходит самонастройка других модулей.

Аналогичным образом происходит самонастройка других модулей.

Код номера барьера a

q с выхода 3.5 регистра 3 поступает на вход дешифратора 8 и возбуждает единичный сигнал  - признак завершения участка

- признак завершения участка  - на его q-м выходе (организационно q-й выход дешифратора 8 входит в его uq-й групповой, m-разрядный выход, подключенный к блоку 18.uq управления синхронизацией). Единичный сигнал

- на его q-м выходе (организационно q-й выход дешифратора 8 входит в его uq-й групповой, m-разрядный выход, подключенный к блоку 18.uq управления синхронизацией). Единичный сигнал  поступает в блок 18.uq и далее в барьерный блок 34.c(uq) (фиг.2), проходя затем через элемент ИЛИ 35.c(uq) (на втором входе элемента 35.c(uq) присутствует сигнал

поступает в блок 18.uq и далее в барьерный блок 34.c(uq) (фиг.2), проходя затем через элемент ИЛИ 35.c(uq) (на втором входе элемента 35.c(uq) присутствует сигнал  с q-го выхода регистра 5). Далее единичный сигнал

с q-го выхода регистра 5). Далее единичный сигнал  поступает на второй вход элемента И 36.c(uq) и тем самым индицирует окончание участка

поступает на второй вход элемента И 36.c(uq) и тем самым индицирует окончание участка  . В свою очередь, код НВС a

t с выхода 3.6 регистра 3 (фиг.1) подается на вход дешифратора 9 и возбуждает сигнал логической единицы на его t-м выходе (организационно t-й выход дешифратора 9 входит в его ut-й групповой, m-разрядный выход, подключенный к блоку 18.ut управления синхронизацией). Единичный сигнал с t-го выхода дешифратора 9 поступает в барьерный блок 34.с(ut) (фиг.2) на второй вход элемента И 40.с(ut), обеспечивая возможность последующего запуска (i.j)-го модуля при завершении участков, сходящихся в барьере a

t.

. В свою очередь, код НВС a

t с выхода 3.6 регистра 3 (фиг.1) подается на вход дешифратора 9 и возбуждает сигнал логической единицы на его t-м выходе (организационно t-й выход дешифратора 9 входит в его ut-й групповой, m-разрядный выход, подключенный к блоку 18.ut управления синхронизацией). Единичный сигнал с t-го выхода дешифратора 9 поступает в барьерный блок 34.с(ut) (фиг.2) на второй вход элемента И 40.с(ut), обеспечивая возможность последующего запуска (i.j)-го модуля при завершении участков, сходящихся в барьере a

t.

В то же время нулевой сигнал с выхода 3.8 регистра 3 (фиг.1) настраивает коммутатор 6 на прием информации с выхода блока элементов ИЛИ 11, а положительный перепад уровня сигнала, возникающий на выходе 3.7 регистра 3, воздействует на одновибратор 15 и формирует на его выходе импульс. Данный импульс поступает на третий вход блока 10 синхронизации и, проходя затем на вход сброса триггера 42 (фиг.4), переключает этот триггер в состояние логического нуля. Нулевой сигнал с прямого выхода триггера 42 выключает генератор 43 и тем самым приостанавливает процесс формирования импульсов синхронизации t1 и t2 на выходах блока 10 синхронизации. Таким образом, процесс считывания команд из блока 1 временно прекращается (модуль переходит в состояние ожидания).

Одновременно с описанными действиями происходит формирование исполнительного адреса следующей команды (адреса, с которого произойдет фактический запуск (i.j)-го модуля после достижения t-го барьера). Указанный адрес образуется из адреса  путем модификации его младшего разряда (AM) значением логического условия с входа 47 модуля (фиг.1). Процесс формирования исполнительного адреса протекает так же как и при работе модуля в режиме А (см. выше). Полученный исполнительный адрес (обозначим его как

путем модификации его младшего разряда (AM) значением логического условия с входа 47 модуля (фиг.1). Процесс формирования исполнительного адреса протекает так же как и при работе модуля в режиме А (см. выше). Полученный исполнительный адрес (обозначим его как  *) поступает на информационный вход буферного регистра 7, а также через блок элементов ИЛИ 11 и коммутатор 6 проходит на информационный вход регистра 2.

*) поступает на информационный вход буферного регистра 7, а также через блок элементов ИЛИ 11 и коммутатор 6 проходит на информационный вход регистра 2.

На этом работа модуля в режиме В заканчивается. Аналогичным образом происходит завершение других участков k-й программы, в том числе и участков  , z≠f, сходящихся в q-м барьере.

, z≠f, сходящихся в q-м барьере.

Рассмотрим работу ЛМК в режиме синхронизации множества параллельных участков, а также процесс запуска модулей при синхронизации. Для определенности будем рассматривать конкретное множество участков, например множество участков  , сходящихся в барьере a

q. Будем считать, что участки

, сходящихся в барьере a

q. Будем считать, что участки  распределены между модулями ЛМК произвольным образом.

распределены между модулями ЛМК произвольным образом.

Процесс синхронизации базируется на конвейерном переключении групп слоев синхронизации, соответствующих различным группам барьеров. В общих чертах этот процесс уже рассматривался выше при обсуждении особенностей заявляемого решения. Ниже дается его детальное представление со ссылками на фиг.1-3.

Переключение групп слоев синхронизации начинается с подачи единичного импульса на вход 61 (М.1)-го модуля ЛМК. Этот импульс проходит через элемент ИЛИ 23 и устанавливает триггер 24 в единичное состояние. Затем единичный сигнал с прямого выхода триггера 24 проходит через элемент ИЛИ 30 и элемент 31 задержки на выход 68 (М.1)-го модуля, откуда далее поступает на вход 62 модуля (М-1.1) (т.е. вверх, см. фиг.1, 3). С входа 62 (М-1.1)-го модуля единичный сигнал, опять же через элемент ИЛИ 30 и элемент 31 задержки, поступает на вход 62 модуля (М-2.1) (снова вверх) и т.д. Таким образом сигнал управления проходит через модули ЛМК до модуля (1,1), а затем движется вправо вдоль строки матрицы и достигает (1.N)-го (верхнего правого) модуля (см. пунктирные стрелки на фиг.3). Параллельно с этим единичный сигнал с выхода триггера 24 модуля (М.1) через элемент 25 задержки поступает на вход сброса триггера 24 и устанавливает его в нулевое состояние.

Единичный сигнал управления, достигнув модуля (1.N), поступает с выхода 68 на вход 60 этого же модуля (см. пунктирные стрелки на фиг.3) и распространяется без задержки через все модули ЛМК влево вдоль верхней строки и вниз по всем столбцам, инкрементируя при этом задним фронтом значения счетчиков 26 и 27 всех модулей. Таким образом, значения этих счетчиков увеличиваются и указывают на следующую группу барьеров. Одновременно этот же сигнал управления задним фронтом фиксирует текущие значения признаков синхронизации в триггерах 37 барьерных блоков 34.i всех модулей. Достигнув (М.1)-го модуля, единичный сигнал, через элемент И 22 (он открыт единичным сигналом с прямого выхода триггера 21) и элемент ИЛИ 23, снова устанавливает триггер 24 в единичное состояние, что приводит к генерации нового сигнала управления, который будет распространяться в ЛМК аналогичным образом и переключать модули на очередную группу слоев.

Длительность задержки 25 определяет длительность единичного сигнала управления и составляет порядка 10-20 задержек двухходового логического элемента выбранной элементной базы (эквивалентного вентиля). Длительность задержки 31 равна времени прохождения сигнала синхронизации через элемент И 36 (фиг.2) и элемент ИЛИ 32.i (фиг.1). Таким образом, время прохождения сигнала управления через модуль устанавливается равным времени передачи модулем признака завершения параллельных участков. Это обеспечивает возможность динамического изменения периода переключения групп барьерных модулей в зависимости от числа модулей ЛМК без необходимости внесения схемных изменений.

Теперь более подробно остановимся на самом процессе барьерной синхронизации.

Синхронизация q-го барьера начинается с появления значения uq на выходе счетчика 26 всех модулей ЛМК, что означает переключение на uq-ю группу слоев синхронизации (группу барьеров). При этом начинается первая фаза синхронизации - формирование признака dq окончания участков множества Bq (в исходном состоянии, т.е. до начала выполнения k-й программы, все сигналы  будут нулевыми, поскольку в каждом множестве

будут нулевыми, поскольку в каждом множестве  имеется хотя бы один не завершенный участок). Значение uq с выхода счетчика 26 поступает на вход дешифратора 28, формирует сигнал высокого уровня на его uq-м выходе и тем самым разрешает прохождение сигнала

имеется хотя бы один не завершенный участок). Значение uq с выхода счетчика 26 поступает на вход дешифратора 28, формирует сигнал высокого уровня на его uq-м выходе и тем самым разрешает прохождение сигнала  через элемент И 36.c(uq).

через элемент И 36.c(uq).

Формирование признака  завершения параллельных участков начинается с (1.N)-го модуля.

завершения параллельных участков начинается с (1.N)-го модуля.

Если  , т.е. (1.N)-й модуль не реализует участков из множества Bq (и, соответственно, не должен оказывать влияние на процесс синхронизации), то на выходе элемента ИЛИ 35.c(uq) (фиг.2) образуется единичный сигнал. Этот сигнал поступает на второй вход элемента И 36.с(uq). На третьем входе данного элемента также находится единичный сигнал с соответствующего выхода дешифратора 28. Таким образом, уровень сигнала на выходе элемента И 36.c(uq) зависит исключительно от сигнала с выхода элемента И 19.c(uq) (фиг.1). Поскольку на входах 52.c(uq) и 53.c(uq) (1.N)-го модуля ЛМК всегда присутствует единичный уровень сигнала (см. исходное состояние), на выходе элемента И 36.с(uq) (фиг.2) формируется единичный сигнал

, т.е. (1.N)-й модуль не реализует участков из множества Bq (и, соответственно, не должен оказывать влияние на процесс синхронизации), то на выходе элемента ИЛИ 35.c(uq) (фиг.2) образуется единичный сигнал. Этот сигнал поступает на второй вход элемента И 36.с(uq). На третьем входе данного элемента также находится единичный сигнал с соответствующего выхода дешифратора 28. Таким образом, уровень сигнала на выходе элемента И 36.c(uq) зависит исключительно от сигнала с выхода элемента И 19.c(uq) (фиг.1). Поскольку на входах 52.c(uq) и 53.c(uq) (1.N)-го модуля ЛМК всегда присутствует единичный уровень сигнала (см. исходное состояние), на выходе элемента И 36.с(uq) (фиг.2) формируется единичный сигнал  .

.

Если для (1.N)-го модуля ЛМК  , т.е. за (1.N)-м модулем закреплен некоторый участок

, т.е. за (1.N)-м модулем закреплен некоторый участок  множества Bq, то прохождение признака

множества Bq, то прохождение признака  через элемент И 36.c(uq) зависит исключительно от значения

через элемент И 36.c(uq) зависит исключительно от значения  на q-м выходе дешифратора 8. Если участок

на q-м выходе дешифратора 8. Если участок  завершен, то

завершен, то  и на выходе элемента ИЛИ 35.c(uq) появляется единичный сигнал. Соответственно, единичный сигнал будет и на выходе элемента И 36.c(uq). В случае если участок

и на выходе элемента ИЛИ 35.c(uq) появляется единичный сигнал. Соответственно, единичный сигнал будет и на выходе элемента И 36.c(uq). В случае если участок  не завершен, то

не завершен, то  и на выходе элемента ИЛИ 35.c(uq) поддерживается нулевой сигнал. Этот сигнал блокирует элемент И 36.с(uq) и формирует на его выходе нулевой сигнал (передача сигнала

и на выходе элемента ИЛИ 35.c(uq) поддерживается нулевой сигнал. Этот сигнал блокирует элемент И 36.с(uq) и формирует на его выходе нулевой сигнал (передача сигнала  через элемент И 36.c(uq) заблокирована). Нулевой сигнал на выходе элемента И 36.c(uq) сохраняется до тех пор, пока не будет завершен участок

через элемент И 36.c(uq) заблокирована). Нулевой сигнал на выходе элемента И 36.c(uq) сохраняется до тех пор, пока не будет завершен участок  .

.

Единичный сигнал  с выхода элемента И 36.c(uq) через элемент ИЛИ 32.c(uq) (фиг.1) поступает на выход 56.c(uq) (1.N)-го модуля ЛМК. Далее сигнал

с выхода элемента И 36.c(uq) через элемент ИЛИ 32.c(uq) (фиг.1) поступает на выход 56.c(uq) (1.N)-го модуля ЛМК. Далее сигнал  распространяется через остальные модули ЛМК. Сигнал

распространяется через остальные модули ЛМК. Сигнал  с выхода 56.c(uq) (1.N)-го модуля поступает на входы 52.c(uq) и 53.c(uq) модулей (2.N) и (1.N-1) соответственно (фиг.1, 3). С этих входов сигнал проходит через элементы И 19.c(uq) модулей (2.N) и (1.N-1) и поступает на первый вход элементов И 36.c(uq) (фиг.2). На третьем входе элементов И 36.с(uq) этих модулей также установлена единица. Значение на втором входе элементов И 36.c(uq) определяются так же как и в случае с модулем (1.N) (см. выше). Таким же образом сигнал

с выхода 56.c(uq) (1.N)-го модуля поступает на входы 52.c(uq) и 53.c(uq) модулей (2.N) и (1.N-1) соответственно (фиг.1, 3). С этих входов сигнал проходит через элементы И 19.c(uq) модулей (2.N) и (1.N-1) и поступает на первый вход элементов И 36.c(uq) (фиг.2). На третьем входе элементов И 36.с(uq) этих модулей также установлена единица. Значение на втором входе элементов И 36.c(uq) определяются так же как и в случае с модулем (1.N) (см. выше). Таким же образом сигнал  с выходов 56.c(uq) модулей (2.N) и (1.N-1) распространится по ЛМК вниз и влево (фиг.3), вплоть до модуля с номером (М.1).

с выходов 56.c(uq) модулей (2.N) и (1.N-1) распространится по ЛМК вниз и влево (фиг.3), вплоть до модуля с номером (М.1).

Если на момент переключения ЛМК на uq-ю группу барьеров все модули ЛМК, участвующие в q-м барьере, уже завершили свои участки программы  , то через определенное время на выходе элемента И 19.c(uq) (М.1)-го модуля установится единичный сигнал. Далее, пройдя через элемент И 36.c(uq) (фиг.2), по заднему фронту сигнала управления с входа 60 (М.1)-го модуля ЛМК единичный сигнал запишется в триггер 37.c(uq). Это будет означать, что первая фаза синхронизации для q-го барьера завершена. Параллельные участки программы выполнены, признак dq сформирован, и можно запускать модули ЛМК, ожидающие завершения q-го барьера.

, то через определенное время на выходе элемента И 19.c(uq) (М.1)-го модуля установится единичный сигнал. Далее, пройдя через элемент И 36.c(uq) (фиг.2), по заднему фронту сигнала управления с входа 60 (М.1)-го модуля ЛМК единичный сигнал запишется в триггер 37.c(uq). Это будет означать, что первая фаза синхронизации для q-го барьера завершена. Параллельные участки программы выполнены, признак dq сформирован, и можно запускать модули ЛМК, ожидающие завершения q-го барьера.

Одновременно с фиксацией сигнала в триггере 37.c(uq) (М.1)-го модуля сигнал управления инкрементирует счетчик 27 (фиг.1) во всех модулях ЛМК, после чего на выходе счетчика 27 установится значение uq. Значение uq с выхода счетчика 27 (i.j)-го модуля поступает на дешифратор 29 и инициирует появление на его uq-м выходе единичного сигнала. Данная единица разрешает прохождение сигнала запуска через элемент И 39.c(uq) (фиг.2). Для q-го барьера начнется вторая фаза синхронизации.