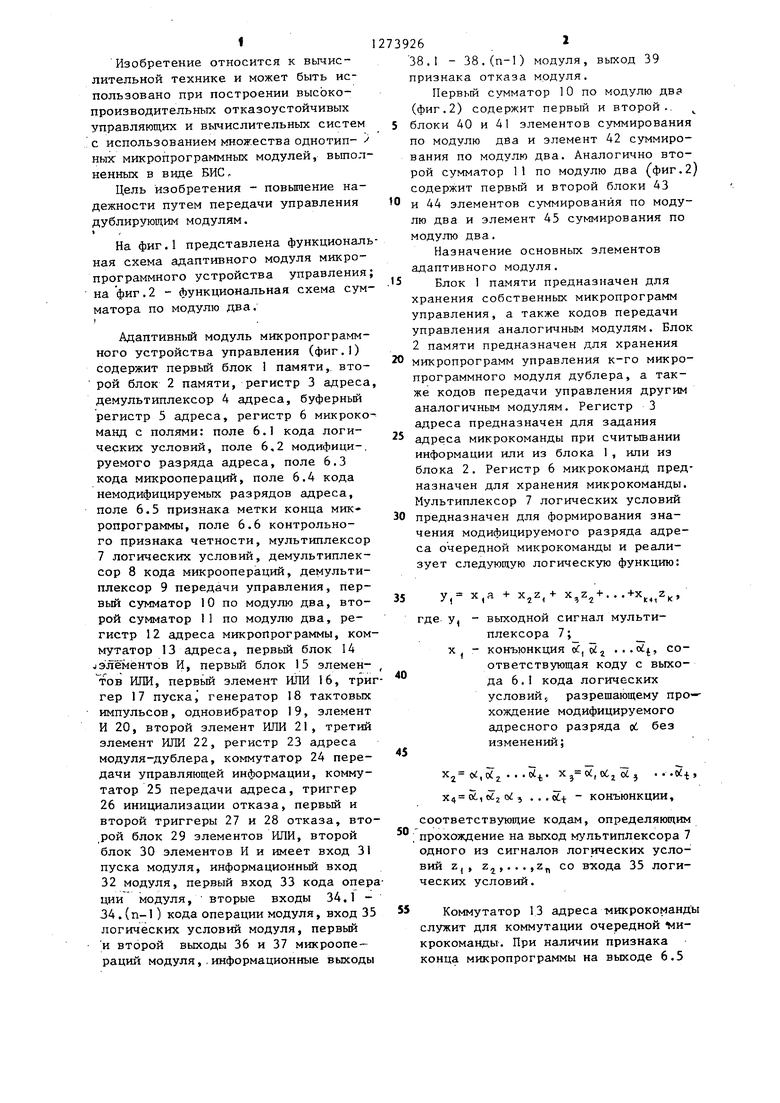

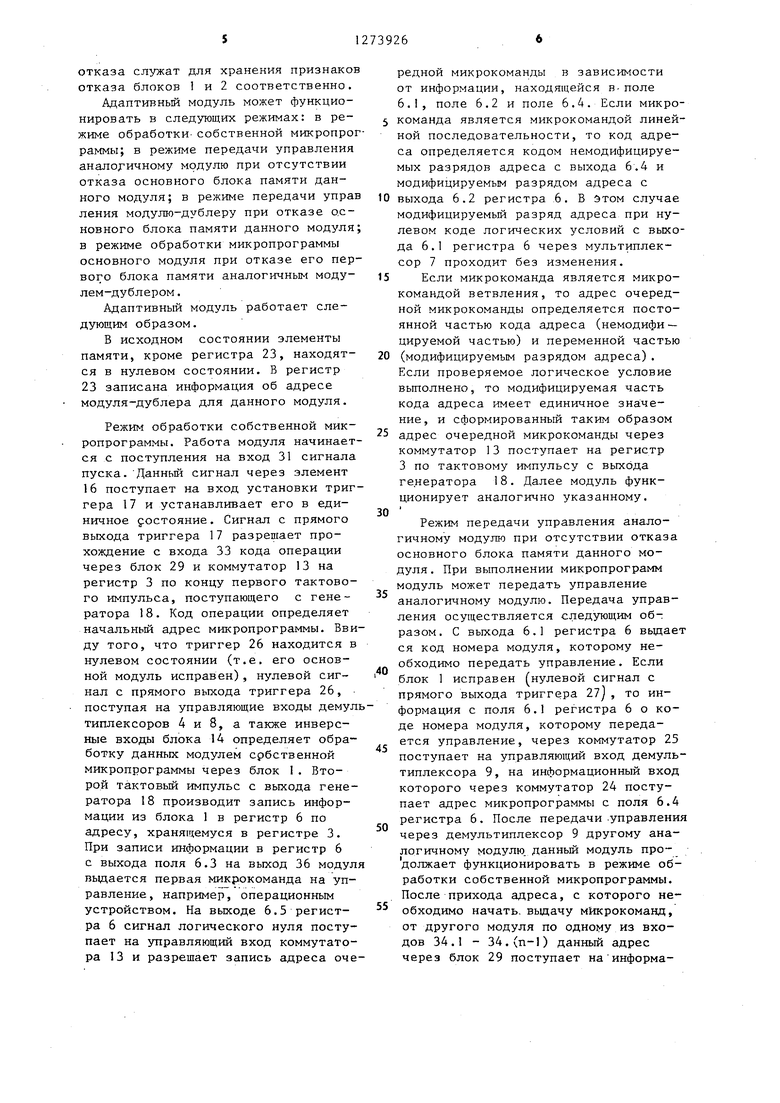

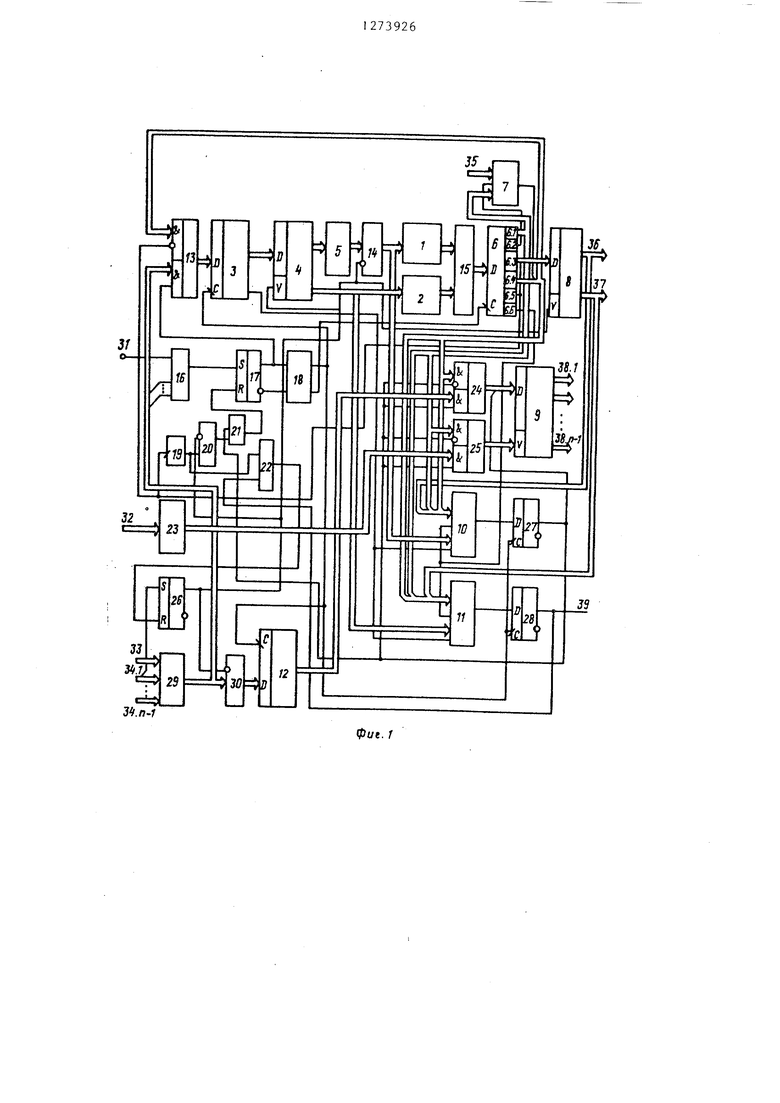

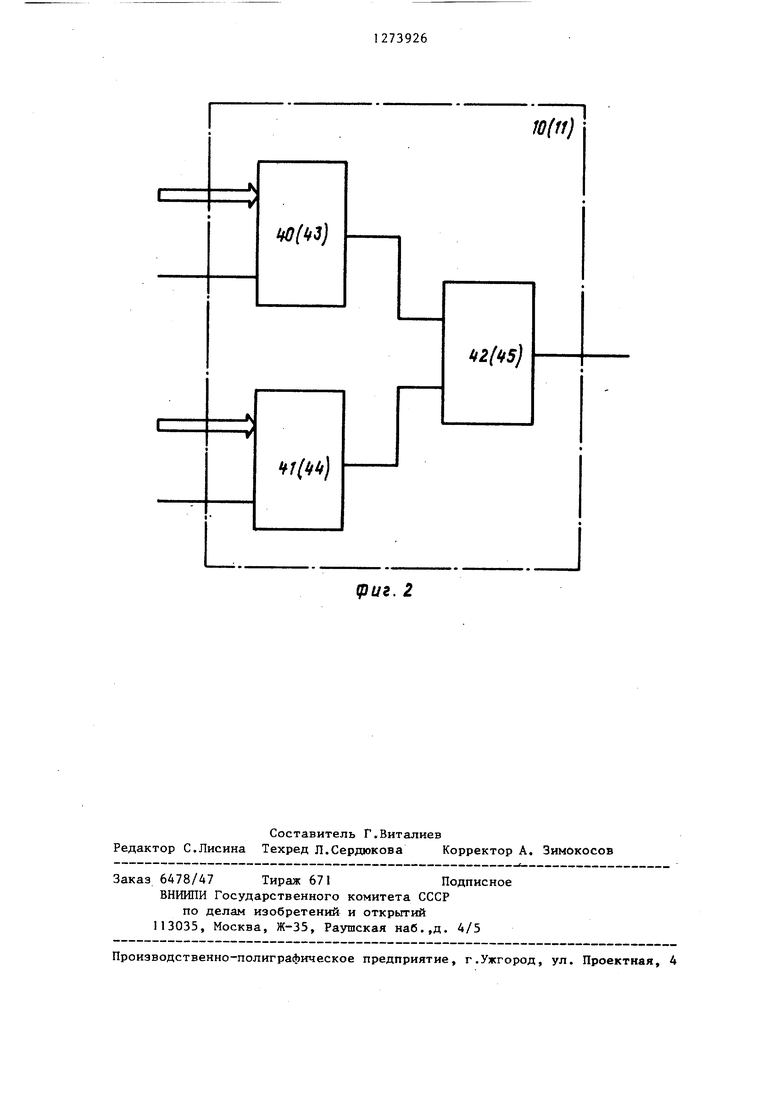

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных отказоустойчивых управляющих и вычислительных систем с использованием множества однотипньпс микропрограммных модулей, вьшол ненньк в виде ВИС. Цель изобретения - повышение надежности путем передачи управления дублирующим модулям. На фиг.1 представлена функциональ ная схема адаптивного модуля микропрограммного устройства управления на фиг.2 - функциональная схема сум матора по модулю два. Адаптивный модуль микропрограммного устройства управления (фиг.1) содержит первый блок 1 памяти, второй блок 2 памяти, регистр 3 адреса демультиплексор 4 адреса, буферный регистр 5 адреса, регистр 6 микроко манд с полями: поле 6.1 кода логических условий, поле 6,2 модифици-. руемого разряда адреса, поле 6.3 кода микроопераций, поле 6.4 кода немодифицируемых разрядов адреса, поле 6.5 признака метки конца микропрограммы, поле 6.6 контрольного признака четности, мультиплексор 7 логических условий, демультиплексор 8 кода микроопераций, демультиплексор 9 передачи управления, первьй сумматор 10 по модулю два, второй сумматор 11 по модулю два, регистр 12 адреса микропрограммы, ком мутатор 13 адреса, первый блок 1Д з лё ментов И, первый блок 15 элементов ИЛИ, первый элемент ИЛИ 16, три гер 17 пускаj генератор 18 тактовых импульсов, одновибратор 19, элемент И 20, второй элемент ИЛИ 21, третий элемент ИЛИ 22, регистр 23 адреса модуля-дублера, коммутатор 24 передачи управляющей информации, коммутатор 25 передачи адреса, триггер 26 инициализации отказа, первый и второй триггеры 27 и 28 отказа, вто ,рой блок 29 элементов ИЛИ, второй блок 30 элементов И и имеет вход 31 пуска модуля, информационный вход 32 модуля, первый вход 33 кода опер ции модуля, вторые входы 34.1 34.(п-1 ) кода операции модуля, вход 35 логических условий модуля, первый и второй выходы 36 и 37 микроопераций модуля,,информационные выходы 262 38.1 - 38.(п-1) модуля, выход 39 признака отказа модуля. Первый сумматор 10 по модулю два (фиг.2) содержит первый и второй.. блоки 40 и 41 элементов суммирования по модулю два и элемент 42 суммирования по модулю два. Аналогично второй сумматор 11 по модулю два {фиг.2) содержит первый и второй блоки 43 и 44 элементов суммирования по модулю два и элемент 45 суммирования по модулю два, Назначение основных элементов адаптивного модуля. Блок 1 памяти предназначен для хранения собственных: микропрограмм управления, а также кодов передачи управления аналогичньм модулям. Блок 2 памяти предназначен для хранения микропрограмм управления к-го микропрограммного модуля дублера, а также кодов передачи управления другим аналогичным модулям. Регистр 3 адреса предназначен для задания адреса микрокоманды при считьшании информации или из блока 1, или из блока 2. Регистр 6 микрокоманд предназначен для хранения микрокоманды. Мультиплексор 7 логических условий предназначен для формирования значения модифицируемого разряда адреса очередной микрокоманды и реализует следующую логическую функцию: У, х,а + х,г,+ x,z + . . .+x,z, где у, - выходной сигнал мультиплексора 7; Х| - конъюнкция 5, 52 . . ., соответствующая коду с выхода 6 . I кода логических условий; разрешающему про-хождение модифицируемого адресного разряда jd без изменений; Х2 Ы,о(г . . .Ы. (,oC.j oij ... Х4 . . . O6i - КОНЬЮНКЦИИ, соответствующие кодам, определяющим прохождение на выход мультиплексора 7 одного из сигналов логических условий Z, , Zj,...,z со входа 35 логических условий. Коммутатор 13 адреса микрокоманды служит для коммутации очередной микрокоманды. Лри наличии признака конца микропрограммы на выходе 6.5

3

регистра 6 очередной адрес микрокоманды коммутируется или с входа 33 кода операции, или с входа 34.134.(п-1) от других аналогичных модулей. При отсутствии признака конца микропрограммы адрес очередной микрокоманды коммутируется в зависимости от хода выполнения микропрограммы. Демультиплексор 4 предназначен для изменения направления передачи адресов микрокоманд, в зависимости от режима функционирования модуля. В режиме обработки собственной микропрограммы выборка микрокоманд производится из блока I, в режиме обработки микропрограммы основного модуля (в случае отказа его собственного блока l) выборка микрокоманд производится из блока 2. Регистр 5 служит для хранения адреса микрокоманды, с которой продолжается вьшолнение собственной микропрограммы после завершения выполнения микропрограммы основного модуля (если его собственный блок 1 отказал) через блок 2 данного модуля-дублера.

Блок 14 элементов И служит для разрешения продолжения выполнения собственной микропрограммы после того, как обработка микропрограммы отказавшего основного модуля через блок 2 данного модуля завершена. Блок 15 элементов ИЛИ предназначен для сборки микрокоманд в зависимости от режима функционирования модуля. .Демультиплексор 8 служит для разделения выдачи кодов микроопераций в зависимости от обрабатьшаемой в данный момент микропрограммы (или собственной, или отказавшего основного модуля). Элемент ИЛИ 16 предназначен для сборки сигналов для инициации работы модуля.

Триггер 17 пуска служит для запуска генератора 18, включение которого происходит по сигналу пуска или с входа 31, или при поступлении информации от аналоговых модулей с входа 34.1 - З4.(п-1),или при поступлении кода операции на вход 33 модуля. Генератор 18 тактовых импуль сов служит для синхронизации работы модуля. На его выходах формируются первый и второй тактовые импульсы. Блок 29 элементов ИЛИ предназначен для сборки кода операции с входа 33 и кодов адресов с входов 34.1 -,

2739264

34.(п-1) с последующей передачей через коммутатор 13 адреса на регистр 3. Одновибратор 19 предназначен для формирования импульса по 5 окончании микропрограммы (команды), что характеризуется появлением признака конец команды на выходе поля 6.5 регистра 6. Элемент ИЛИ 21 и элемент И 20 служат для формирования

О сигнала на прекращение работы модуля. Элемент ИЛИ 22 служит для сборки сигналов на обнуление триггера 26 или после завершения обработки микропрограммы, или после отказа блока 2 при

5 обработке микропрограммы от основного модуля.

Регистр 23 адреса модуля-дублера .(для данного модуля) предназначен для хранения информации адреса того модуля, в котором имеется блок 2 с .набором микропрограмм, идентичным набору микропрограмм блока I данного модуля, т.е. регистр 23 хранит информацию о том, куда необходимо передать код операции, если блок I данного модуля отказал. Регистр 12 предназначен для хранения информации об адресе микропрограммы и выдачи ее аналогичному модулю-дублеру (содержащему набор микропрограмм

блока 1 данного модуля в случае отказа блока 1 данного модуля. Триггер 26 отказа предназначен для инициализации отказа блока 1 основного 35 модуля, микропрограмма которого обрабатывается через блок 2 данного модуля-дублера. Блок 30 элементов И служит для разрешения записи адреса микропрограммы в регистр 12, если 0 основной модуль находится в работоспособном состоянии. Коммутатор 24 предназначен для коммутации управ- ляющей информации (адреса микрокоманды) в зависимости от режима рабо5 ты модуля при передаче информации в другой аналогичный модуль. Коммутатор 25 служит для коммутации адреса передачи управления (т.е. адреса модуля, которому необходимо пере0 дать информацию) в зависимости от режима функционирования модуля. Демультиплексор 9 предназначен для передачи управления другому аналогичному модулю по выходам 38.1 5 З8.(п-) модуля. Сумматор 10 служит для обнаружения отказа блока I. Сумматор 11 служит для обнаружения . отказа блока 2. Триггеры 27 и 28

отказа служат для хранения признако отказа блоков 1 и 2 соответственно.

Адаптивньй модуль может функционировать в следующих режимах: в режиме обработки- собственной микропрораммы; в режиме передачи управления аналогичному модулю при отсутствии отказа основного блока памяти данного модуля; в режиме передачи упра ления модулю-дублеру при отказе о,сновного блока памяти данного модуля в режиме обработки микропрограммы основного модуля при отказе его первого блока памяти аналогичным модулем-дублером.

Адаптивный модуль работает следующим образом.

В исходном состоянии элементы памяти, кроме регистра 23, находятся в нулевом состоянии. В регистр 23 записана информация об адресе модуля-дублера для данного модуля.

Режим обработки собственной микропрограммы. Работа модуля начинается с поступления на вход 31 сигнала пуска. Данньп сигнал через элемент 16 поступает на вход установки триггера 17 и устанавливает его в единичное достояние. Сигнал с прямого выхода триггера 17 разрешает прохождение с входа 33 кода операции через блок 29 и коммутатор 13 на регистр 3 по концу первого тактового импульса, поступающего с генератора 18. Код операции определяет начальный адрес микропрограммы. Ввиду того, что триггер 26 находится в нулевом состоянии (т.е. его основной модуль исправен), нулевой сигнал с прямого выхода триггера 26, поступая на управляющие входы демултиплексоров 4 и 8, а также инверсные входы блока 14 определяет обработку данных модулем србственной микропрограммы через блок I. Второй тактовьй импульс с выхода генератора 18 производит запись информации из блока 1 в регистр 6 по адресу, хранящемуся в регистре 3. При записи информации в регистр 6 с выхода поля 6.3 на выход 36 модул выдается первая микрокоманда на управление, например, операционным устройством. На выходе 6.5 регистра 6 сигнал логического нуля поступает на управляющий вход коммутатора 13 и разрешает запись адреса очередной микрокоманды в зависимости от информации, находящейся в-поле 6.1, поле 6.2 и поле 6.4. Если микрокоманда является микрокомандой линейной последовательности, то код адреса определяется кодом немодифицируемых разрядов адреса с выхода 6.4 и модифицируемым разрядом адреса с выхода 6.2 регистра ,6. В этом случае модифицируемый разряд адреса при нулевом коде логических условий с выхода 6.1 регистра 6 через мультиплексор 7 проходит без изменения.

Если микрокоманда является микрокомандой ветвления, то адрес очередной микрокоманды определяется постоянной частью кода адреса (немодифи - цируемой частью) и переменной частью (модифицируемым разрядом адреса). Если проверяемое логическое условие вьшолнено, то модифицируемая часть кода адреса имеет единичное зна чение, и сформированный таким образом адрес очередной микрокоманды через коммутатор 13 поступает на регистр 3 по тактовому импульсу с выхода генератора 18. Далее модуль функционирует аналогично указанному.

Режим передачи управления аналогичному модулю при отсутствии отказа основного блока памяти данного модуля . При выполнении микропрограмм модуль может передать управление аналогичному модулю. Передача управления осуществляется следующим образом. С выхода 6.1 регистра 6 вьщае ся код номера модуля, которому необходимо передать управление. Если блок 1 исправен (нулевой сигнал с прямого выхода триггера 27J , то информация с поля 6.1 регистра 6 о коде номера модуля, которому передается управление, через коммутатор 25 поступает на управляющий вход демультиплексора 9, на информационный вход которого через коммутатор 24 поступает адрес микропрограммы с поля 6.4 регистра 6. После передачи .управлени через демультиплексор 9 другому аналогичному модулю, данный модуль продолжает функционировать в режиме обработки собственной микропрограммы. После прихода адреса, с которого необходимо начать, выдачу микрокоманд, от другого модуля по ОДНОМУ из входов 34.1 - 34.(п-1) данный адрес через блок 29 поступает наинформационньм вход коммутатора 13 и на элемент 16. На выходе элемента 16 появляется сигнал, которьйперебрасывает триггер 17 в единичное состо ние и тем самым запускает генератор 18. Первым тактовым импульсом с. выхода генератора 18, поступающим н синхровход регистра 3, информация через коммутатор 13 заносится в регистр 3. По этому адресу происходит считывание информации из блока 1 , Далее модуль работает аналогично указанному. Режим передачи управления модулю дублеру при отказе основного блока памяти данного модуля, По мере вьща чи информации модулем происходит ее контроль в сумматорах 10 (контролирует блок 1) и 11 (контролирует блок 2) (фиг.2). При этом происходи контроль как адресной, так и операционной информации и при искажении одного из кодов или несоответствии адреса выбранной микрокоманде сумма тор 10 (п) формирует сигнал отказа соответствующего блока памяти. Этот сигнал с приходом тактового импульса на синхровход соответствующего триггера 27 или 28 перебрасьгоает данный триггер р единичное состояние. При отказе блока 1 единичный сигнал с прямого выхода триггера 2 через элемент 21 обнуляет триггер 17, а также производит перекоммутацию и передачу управления определен ному модулю-дублеру, адрес которого хранится в регистре 23, а код опера ции, при выполнении которой произошел отказ, хранится в регистре 12. Управляющая информация с регистров и 12 через коммутаторы 24 и 25, а также сигнал отказа с триггера 27 поступает на демуЛьтиплексор 9, который производит передачу кода опер ции (адреса невыполненной в данном модуле микропрограммы) определенном модулю-дублеру. После отказа блока 1 данный модуль способен выполнять функции модуля-дублера по отношению к определенному модулю устройства, т.е. в блоке 2 данного модуля храни ся набор микропрограмм, идентичный Чнабору микропрограмм блока 1 за ранее определенного модуля устрой ства. Режим обработки микропрограммы основного модуля при отказе его пер вого блока памяти аналогичным модулем-дублером. В этом режиме от отказавшего модуля, например, на вход 34.1 поступает управляющая информация, по которой триггер 26 устанавливается в единичное состояние, запрещая тем самым через блок 30 запись прмчедшего кода операции в регистр 12 в нем продолжает храниться информация об адресе текущей микропрограммы данного модуля). Единичный сигнал с прямого выхода триггера 26, поступая на управляющие входы демультиплексоров 4 и 8, а также на инверсные входы блока 14 организует хранение текущей микрокоманды в регистре 5 и определяет обработку данным модулем пришедшего кода операции через блок 2 и выдачу операционных микрокоманд на выход 37 модуля. Если при вьшолнении микропрограммы отказ блока 2 не происходит, то после окончания обработки микропрограммы с выхода поля 6.5 регистра 6 единичный сигнал через одновибратор 19 и элемент 22 обнуляет триггер 26 и выполнение прерванной микропрограммы через блок 1 продолжается. При обнаружении отказа блока 2 единичный сигнал с прямого выхода триггера 28 через элемент 22 также обнуляет триггер 26, продолжая тем самым выполнение прерванной микропрограммы, а на выходе 39 модуля появляется единичньй сигнал, говорящий о том, что произошел такой отказ блока 1 основного модуля и блока 2 данного модуля-дублера, что определенньй набор микропрограмм этих двух блоков памяти выполниться не сможет (полный отказ данного набора микропрограмм). Если вьтолнение собственной микропрограммы в данном модуле не прерьшалось обращениями к блоку 2 со стороны основного модуля, то . после окончания микропрограммы сигнал с выхода поля 6.5 регистра 6 обнуляет триггер 17 через элемент 20, так как триггер 28 находился в нулевом состоянии. Если он был в единичном состоянии (был запрос к блоку 2), то по окончании микропрограммы запроса триггер 17 не обнуляется (так как на инверсном входе элемента 20 присутствует единичный сигнал) и модуль продолжает вьтолнение собственной микропрограммы через блок 1 аналогично указанному. о б р е т е Формула Адаптивный модуль микропрограммного устройства управления, содержащий два блока памяти, коммутатор адреса, регистр микрокоманд, мульти плексор логических условий, триггер пуска, генератор тактовых импульсов два блока элементов И, блок элементов ИЛИ, элемент И, три элемента ИЛИ и одновибратор, причем выход первого блока элементов И соединен адресным входом первого блока памяти, выход поля логических условий, ВЫХОД.модифицируемого разряда адреса и выход немодифицируемьгх разрядов адреса регистра микрокоманд подключены соответственно к управляющему входу и первому информацион ному входу мультиплексора логических условий и немодифицируемым разрядам первого информационного входа коммутатора адреса, вькод мультипле сора логических условий соединен с модифицируемым разрядом первого информационного входа коммутатора адр са, вход пуска модуля подключен к , первому входу первого элемента ИЛИ, выход которого соединен с входом ус тановки триггера пуска, прямой выход триггера пуска подключен к вход запуска генератора тактовых импульсов, первый выход которого соединен с синхровходом регистра адреса, выход коммутатора адреса подключен к информационному входу регистра адре са, вход логических условий модуля соединен с вторым информационным вх дом мультиплексора логических условий, второй выход генератора тактовых импульсов подключен к синхровходу регистра микрокоманд, отли чающийся тем, что, с целью повышения надежности путем передачи управления дублирующим модулям, он содержит буферный регистр адреса регистр адреса микропрограммы, регистр адреса модуля-дублера, демуль типлексор адреса, демультиплексор кода микроопераций, демультиплексор передачи управления, коммутатор передачи адреса, коммутатор передачи управляющей информации, триггер инициализации отказа, два триггера отказа, два сумматора по модулю два второй блок элементов ИЛИ, причем выход первого блока памяти соединен с первым входом первого блока эле16 ментов ИЛИ, выход которого подключен к информационному входу регистра микрокоманд, выход кода микроопераций регистра микрокоманд соединен с информационным входом демультиплексора кода микроопераций, первый выход которого подключен к первому выходу микроопераций модуля и первому входу первого сумматора по модулю два, второй выход демультиплексора кода микроопераций соединен с вторым выходом микроопераций модуля и первым входом второго сумматора по модулю два, выход логических условий регистра микрокоманд, выход немодифицируемых разрядов адреса регистра микрокоманд и вькод мультиплексора логических условий подключены к первым входам первого и второго сумматоров по модулю два, вькод контрольного признака четности регистра микрокоманд соединен с вторыми входами первого и второго сумматоров по модулю два, первый вход кода операции модуля подключен к первому входу второго блока элементов ИЛИ, остальные п-1 входов которого (п - число модулей микропрограммного устройства управления) соединены с одноименными входами второй группы входов кода оперягщи модуля, i-й вход (i 1, п-1)-й группы вторых входов кода операции модуля подключен к входу установки триггера инициализации отказа, единичный выход которого соединен с инверсным входом элемента И, инверсными входами первого и второго блоков элементов И, управляющими входами демультиплексора адреса и демультиплексора кода микроопераций, выход второго блока эле- : ментов ИЛИ подключен к второму входу первого элемента ИЛИ, второму информационному входу коммутатора адреса и прямому входу второго блока элементов И, выход которого соединен с информационным входом регистра адреса микропрограммы, выход регистра адреса микропрограммы подключен к первому информационному входу коммутатора передачи управляющей информации, выход которого соединен с информационным входом демультиплексора передачи управления, п -1 выходов которого являются информационными выходами модуля, вькрд немодифицируемых разрядов адреса регистра микрокоманд и выход мультиплексора логических уелоПВИЙ подключены к второму информационному входу коммутатора передачи управляющей информации, единичный выход триггера пуска соединен с пря мым управляющим входом коммутатора адреса, выход регистра адреса подключен к информационному входу демультиплексора адреса, первьй выход которого соединен с входом буферного регистра адреса, выход буфе ного регистра адреса подключен к пр мому входу первого блока элементов И, выход которого соединен с третьим входом первого сумматора по моду лю два, выход первого сумматора по модулю два подключен к информационному входу первого триггера отказа, единичный выход которого соединен с информационным входом демульТиплексора передачи управления, пря мыми и инверсными управляющими вход ми коммутатора передачи адреса и коммутатора передачи управляющей информации и первым входом второго элемента ИЛИ, выход которого подключен к входу сброса триггера пуска, выход признака конца микропрограммы регистра микрокоманд соединен с информационным входом демультипле сора кода микроопераций, инверсным управляющим входом коммутатора адре са и входом одновибратора, выход которого подключен к первому входу третьего элемента ИЛИ и прямому входу элемента И, выход элемента И 6 соединен с вторым входом второго элемента ИЛИ, первый выход генератора тактовых импульсов подключен к синхровходу регистра адреса микропрограммы и синхровходам первого и второго триггеров отказа, едини 1ный выход второго триггера отказа соединен с выходом признака отказа модуля и вторым входом третьего элемента ИЛИ, выход которого подключен к входу сброса триггера инициализации отказа, выход второго сумматора по модулю два соединен с информационным входом второго триггера отказа, второй выход демультиплексора адреса подключен к третьему входу второго сумматора по модулю два и адресному входу второго блока памяти, выход которого соединен с вторым входом первого йтока элементов ИЛИ, выход контрольного признака четности регистра адреса подключен к четвертым входам первого и второго сумматоров по модулю два, информационный вход модуля соединен с входом регистра адреса модуля-дублера, выход которого подключен к первому информационному входу коммутатора передачи адреса, второй информационный вход которого соединен с выходом кода логических условий регистра микрокоманд, а выход коммутатора передачи адреса подключен к управляющему входу демультиплексора передачи управления.

Ю(11)

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Распределенная система для программного управления с мажоритированием | 1990 |

|

SU1727112A1 |

| Микропрограммный модуль | 1984 |

|

SU1193675A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

Изобретениэ относится к вычислительной технике и может быть использовано при построении высокопроизводительных отказоустойчивых управляющих и вычислительных систем с использованием множества однотипных микро,программных модулей, выполненных в виде БИС. Целью изобретения является повышение надежности путем передачи управления дублирующим модулям. С этой целью в адаптивный модуль содержащий два блока памяти, коммутатор адреса, регистр микрокоманд, мультиплексор логических условий, триггер пуска, генератор тактовых импульсов, два блока элементов И, блок элементов ИЛИ, элемент И, три элемента ИЛИ и одновибратор, введены буферный регистр адреса, регистр адреса микропрограммы, регистр адреса модуля-дублера, демультиплексор адреса, демультиплексор кода микроопераций, демультиплексор передачи управления, коммутатор передачи с адреса, коммутатор передачи управляющей информации, триггер инициали(Л зации отказа, два триггера отказа, два сумматора по модулю два, второй блок элементов ИЛИ. 2 ил.

ffO()

v//«4)

I

ff2(5)

,.J

ipue. 2

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1984-09-13—Подача