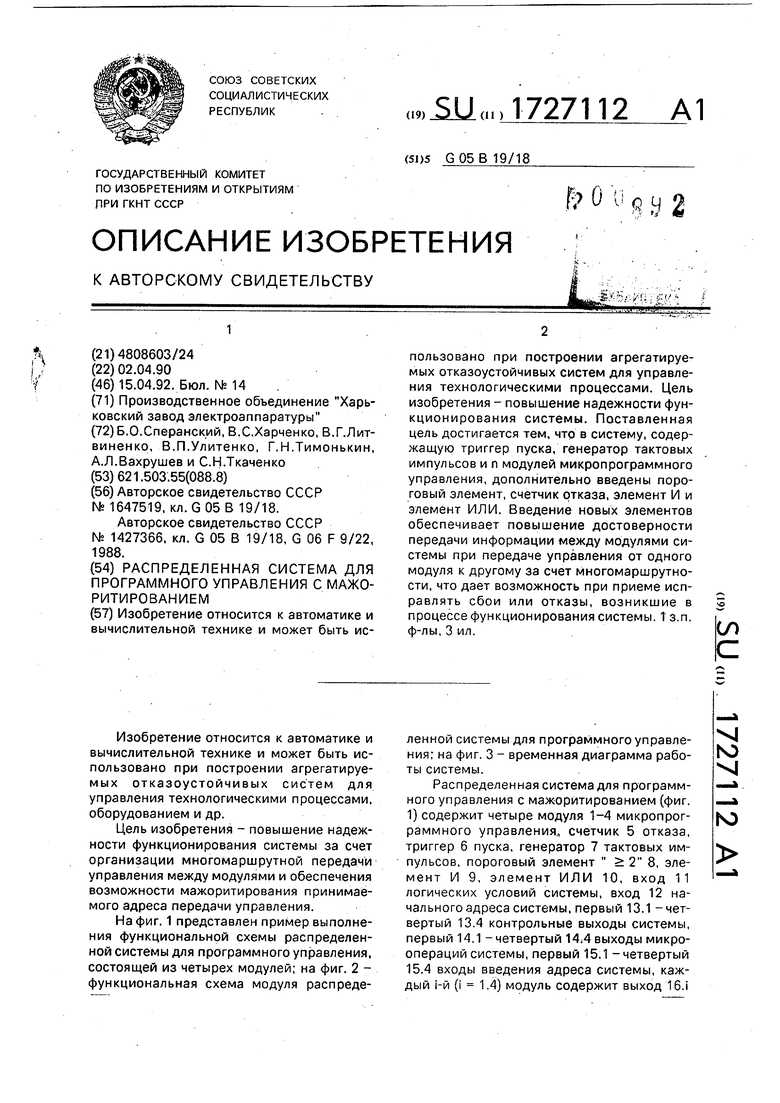

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении агрегатируе- мых отказоустойчивых систем для управления технологическими процессами, оборудованием и др.

Цель изобретения - повышение надежности функционирования системы за счет организации многомаршрутной передачи управления между модулями и обеспечения возможности мажоритирования принимаемого адреса передачи управления.

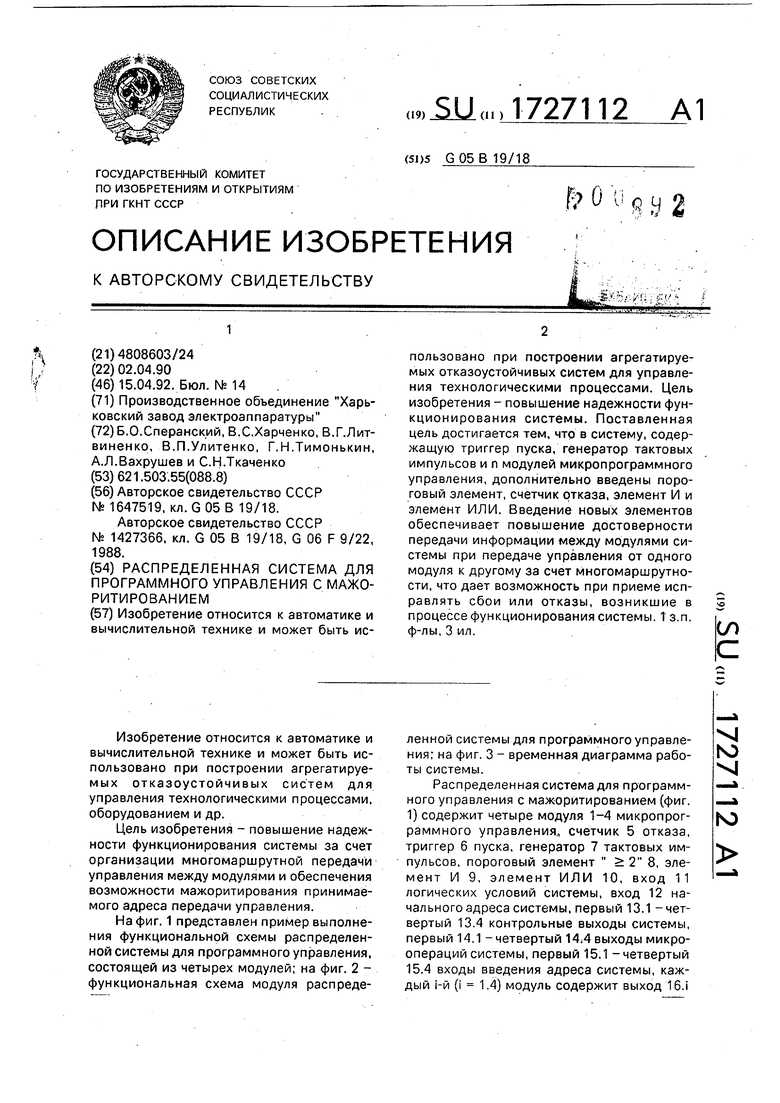

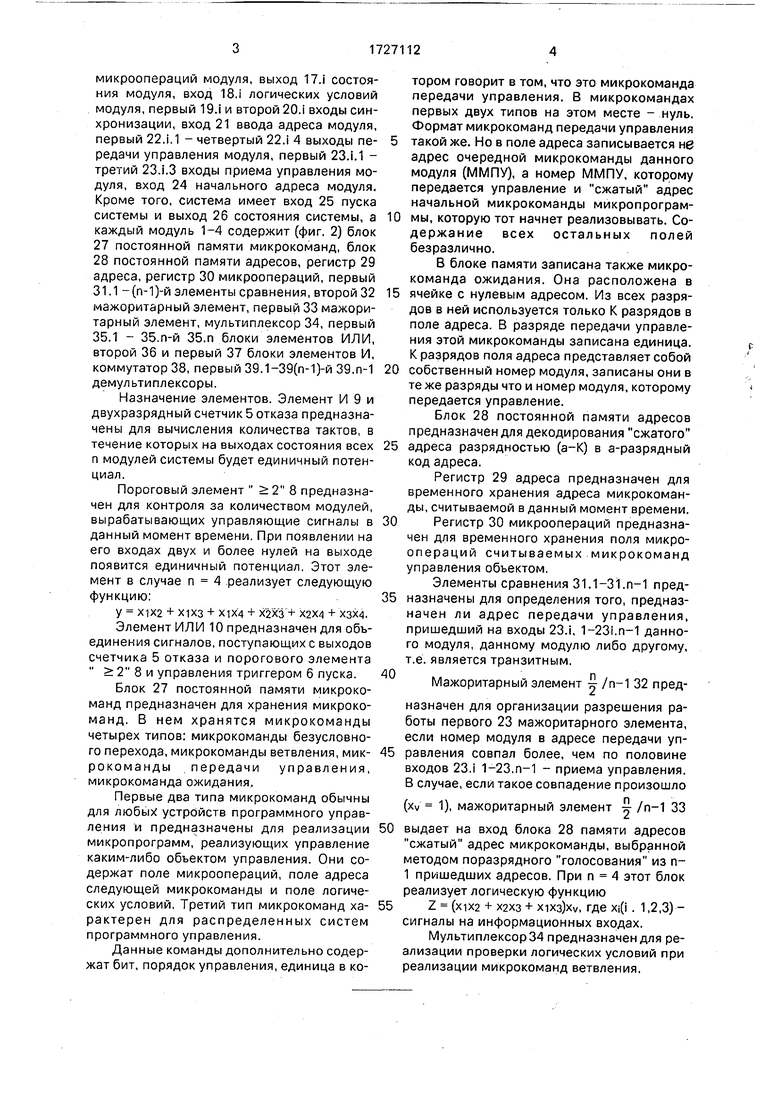

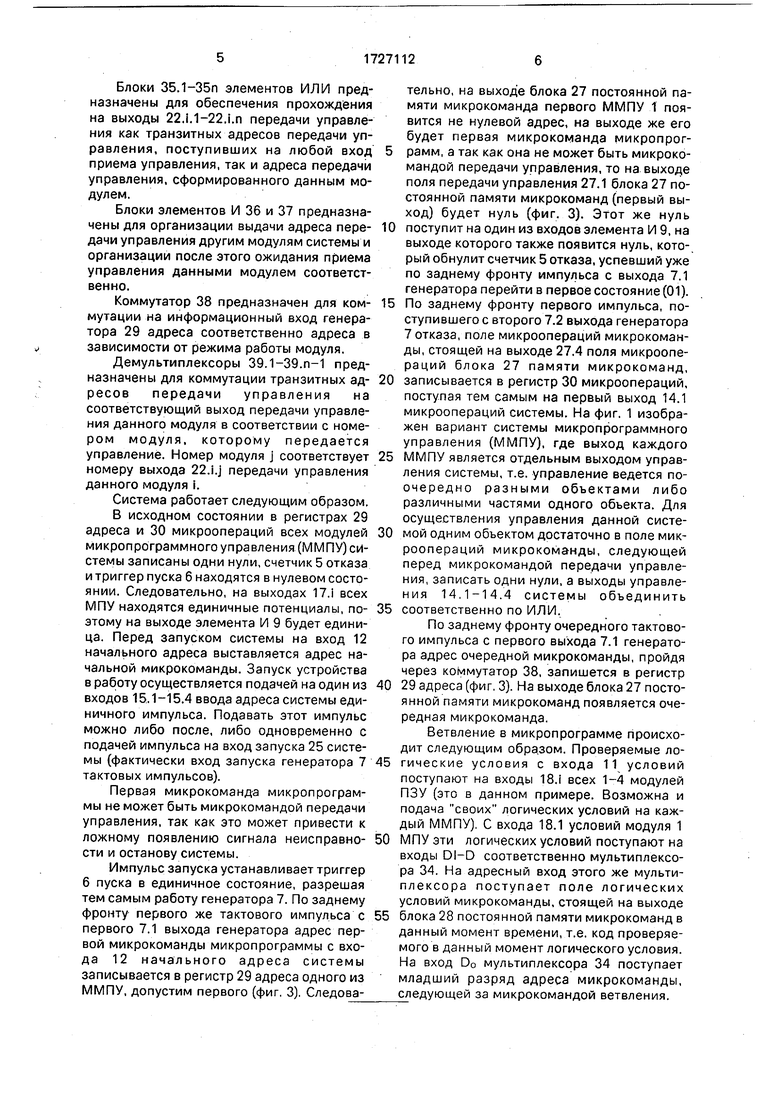

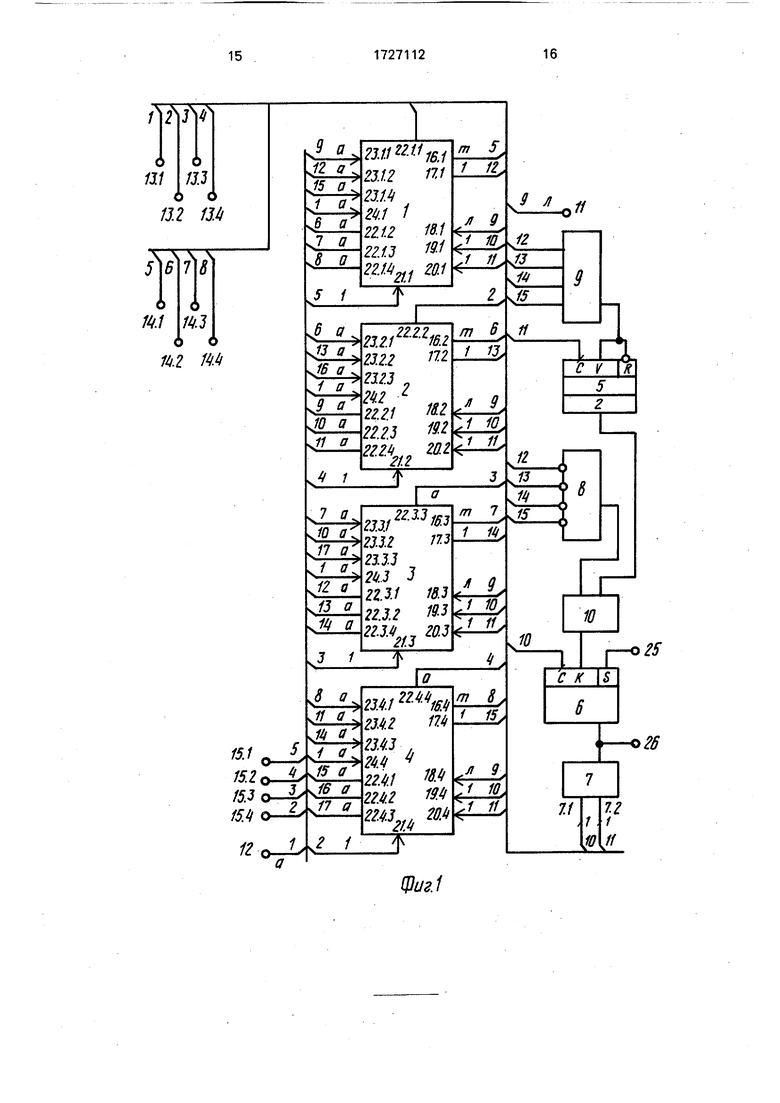

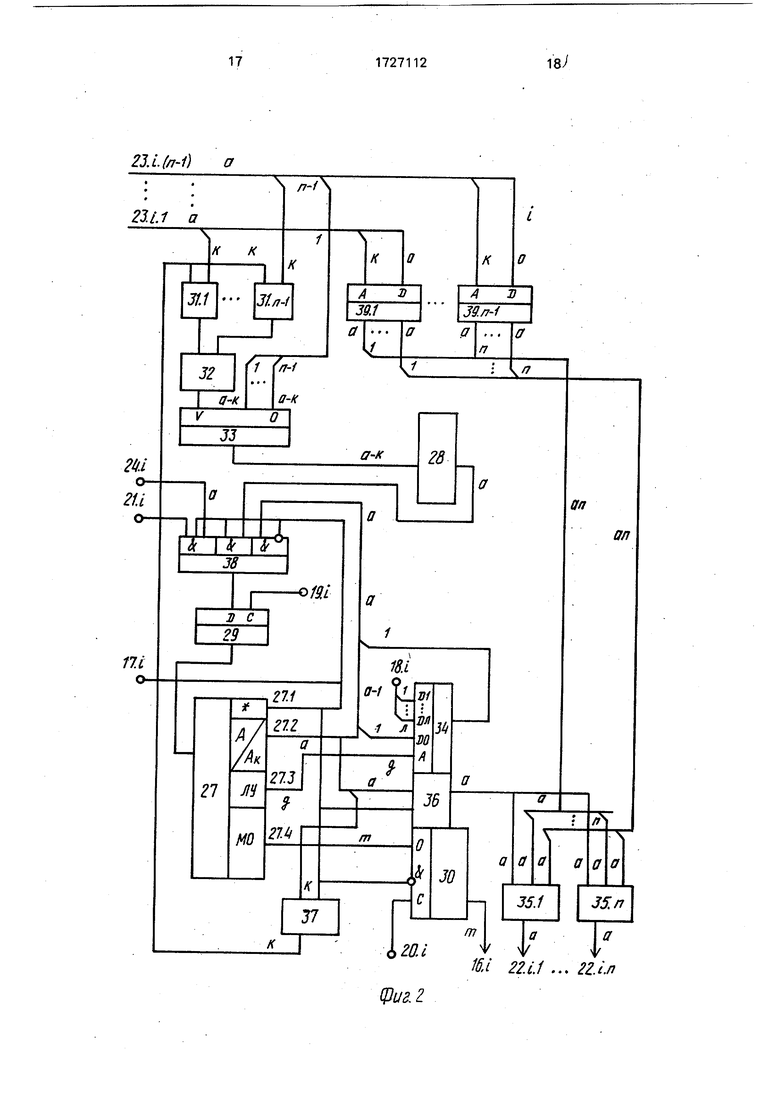

На фиг. 1 представлен пример выполнения функциональной схемы распределенной системы для программного управления, состоящей из четырех модулей; на фиг. 2 - функциональная схема модуля распределенной системы для программного управления; на фиг. 3 - временная диаграмма работы системы.

Распределенная система для программного управления с мажоритированием (фиг. 1) содержит четыре модуля 1-4 микропрограммного управления., счетчик 5 отказа, триггер 6 пуска, генератор 7 тактовых импульсов, пороговый элемент 2 8, элемент И 9, элемент ИЛИ 10, вход 11 логических условий системы, вход 12 начального адреса системы, первый 13.1 - четвертый 13.4 контрольные выходы системы, первый 14.1 -четвертый 14,4 выходы микроопераций системы, первый 15.1 -четвертый 15.4 входы введения адреса системы, каждый i-й (i 1.4) модуль содержит выход 16.i

vi

ND VI

hO

микроопераций модуля, выход 17.i состояния модуля, вход 18.1 логических условий модуля, первый 19.1 и второй 20.i входы синхронизации, вход 21 ввода адреса модуля, первый 22.И - четвертый 22.i 4 выходы передачи управления модуля, первый 23.1.1 - третий 23.I.3 входы приема управления модуля, вход 24 начального адреса модуля. Кроме того, система имеет вход 25 пуска системы и выход 26 состояния системы, а каждый модуль 1-4 содержит (фиг. 2) блок

27постоянной памяти микрокоманд, блок

28постоянной памяти адресов, регистр 29 адреса, регистр 30 микроопераций, первый 31.1 -(п-1)-й элементы сравнения, второй 32 мажоритарный элемент, первый 33 мажоритарный элемент, мультиплексор 34, первый 35.1 - З5.п-й 35.п блоки элементов ИЛИ, второй 36 и первый 37 блоки элементов И, коммутатор 38, первый 39.1-39(п-1)-й ЗЭ.п-1 демультиплексоры.

Назначение элементов. Элемент И 9 и двухразрядный счетчик 5 отказа предназначены для вычисления количества тактов, в течение которых на выходах состояния всех п модулей системы будет единичный потенциал.

Пороговый элемент 2 8 предназначен для контроля за количеством модулей, вырабатывающих управляющие сигналы в данный момент времени. При появлении на его входах двух и более нулей на выходе появится единичный потенциал. Этот элемент в случае п 4 реализует следующую функцию:

У Х1Х2 + Х1ХЗ + Х1Х4 + Х2Х4 + ХЗХ4.

Элемент ИЛИ 10 предназначен для объединения сигналов, поступающих с выходов счетчика 5 отказа и порогового элемента 2 8 и управления триггером 6 пуска.

Блок 27 постоянной памяти микрокоманд предназначен для хранения микрокоманд. В нем хранятся микрокоманды четырех типов: микрокоманды безусловного перехода, микрокоманды ветвления, мик- рокоманды передачи управления, микрокоманда ожидания.

Первые два типа микрокоманд обычны для любых устройств программного управления и предназначены для реализации микропрограмм, реализующих управление каким-либо объектом управления. Они содержат поле микроопераций, поле адреса следующей микрокоманды и поле логических условий. Третий тип микрокоманд характерен для распределенных систем программного управления.

Данные команды дополнительно содержат бит, порядок управления, единица в котором говорит в том, что это микрокоманда передачи управления. В микрокомандах первых двух типов на этом месте - нуль. Формат микрокоманд передачи управления 5 такой же. Но в поле адреса записывается не адрес очередной микрокоманды данного модуля (ММПУ), а номер ММПУ, которому передается управление и сжатый адрес начальной микрокоманды микропрограм0 мы, которую тот начнет реализовывать. Содержание всех остальных полей безразлично.

В блоке памяти записана также микрокоманда ожидания. Она расположена в

5 ячейке с нулевым адресом. Из всех разрядов в ней используется только К разрядов в поле адреса. В разряде передачи управления этой микрокоманды записана единица. К разрядов поля адреса представляет собой

0 собственный номер модуля, записаны они в те же разряды что и номер модуля, которому передается управление.

Блок 28 постоянной памяти адресов предназначен для декодирования сжатого

5 адреса разрядностью (а-К) в а-разрядный код адреса.

Регистр 29 адреса предназначен для временного хранения адреса микрокоманды, считываемой в данный момент времени.

0 Регистр 30 микроопераций предназначен для временного хранения поля микроопераций считываемых микрокоманд управления объектом.

Элементы сравнения 31.1-31.n-1 пред5 назначены для определения того, предназначен ли адрес передачи управления, пришедший на входы 23.i, 1-23I.п-1 данного модуля, данному модулю либо другому, т.е. является транзитным.

Мажоритарный элемент -5- /п-1 32 предназначен для организации разрешения работы первого 23 мажоритарного элемента, если номер модуля в адресе передачи уп- 5 равления совпал более, чем по половине входов 23.i 1-23.п-1 - приема управления. В случае, если такое совпадение произошло

(xv 1), мажоритарный элемент - /п-1 33

0 выдает на вход блока 28 памяти адресов сжатый адрес микрокоманды, выбранной методом поразрядного голосования из п- 1 пришедших адресов. При п 4 этот блок реализует логическую функцию

5 Z (xix2 + Х2хз + xixsjxv, где xi(i. 1,2,3) - сигналы на информационных входах.

Мультиплексор 34 предназначен для реализации проверки логических условий при реализации микрокоманд ветвления.

Блоки 35.1-35п элементов ИЛИ предназначены для обеспечения прохождения на выходы 22.i.1-22.i.n передачи управления как транзитных адресов передачи управления, поступивших на любой вход приема управления, так и адреса передачи управления, сформированного данным модулем.

Блоки элементов И 36 и 37 предназначены для организации выдачи адреса пере- дачи управления другим модулям системы и организации после этого ожидания приема управления данными модулем соответственно.

Коммутатор 38 предназначен для ком- мутации на информационный вход генератора 29 адреса соответственно адреса в зависимости от режима работы модуля.

Демультиплексоры 39.1-39.n-1 предназначены для коммутации транзитных ад- ресов передачи управления на соответствующий выход передачи управления данного модуля в соответствии с номером модуля, которому передается управление. Номер модуля j соответствует номеру выхода 22J.J передачи управления данного модуля i.

Система работает следующим образом.

В исходном состоянии в регистрах 29 адреса и 30 микроопераций всех модулей микропрограммного управления (ММПУ) системы записаны одни нули, счетчик 5 отказа и триггер пуска 6 находятся в нулевом состоянии. Следовательно, на выходах 17.i всех МПУ находятся единичные потенциалы, по- этому на выходе элемента И 9 будет единица. Перед запуском системы на вход 12 начального адреса выставляется адрес начальной микрокоманды. Запуск устройства в работу осуществляется подачей на один из входов 15,1-15.4 ввода адреса системы единичного импульса. Подавать этот импульс можно либо после, либо одновременно с подачей импульса на вход запуска 25 системы (фактически вход запуска генератора 7 тактовых импульсов).

Первая микрокоманда микропрограммы не может быть микрокомандой передачи управления, так как это может привести к ложному появлению сигнала неисправно- сти и останову системы.

Импульс запуска устанавливает триггер 6 пуска в единичное состояние, разрешая тем самым работу генератора 7. По заднему фронту первого же тактового импульса с первого 7.1 выхода генератора адрес первой микрокоманды микропрограммы с входа 12 начального адреса системы записывается в регистр 29 адреса одного из ММПУ, допустим первого (фиг. 3). Следовательно, на выходе блока 27 постоянной памяти микрокоманда первого ММПУ 1 появится не нулевой адрес, на выходе же его будет первая микрокоманда микропрограмм, а так как она не может быть микрокомандой передачи управления, то на выходе поля передачи управления 27.1 блока 27 постоянной памяти микрокоманд (первый выход) будет нуль (фиг. 3). Этот же нуль поступит на один из входов элемента И 9, на выходе которого также появится нуль, который обнулит счетчик 5 отказа, успевший уже по заднему фронту импульса с выхода 7.1 генератора перейти в первое состояние (01). По заднему фронту первого импульса, поступившего с второго 7.2 выхода генератора 7 отказа, поле микроопераций микрокоманды, стоящей на выходе 27.4 поля микроопераций блока 27 памяти микрокоманд, записывается в регистр 30 микроопераций, поступая тем самым на первый выход 14.1 микроопераций системы. На фиг. 1 изображен вариант системы микропрограммного управления (ММПУ), где выход каждого ММПУ является отдельным выходом управления системы, т.е. управление ведется поочередно разными объектами либо различными частями одного обьекта. Для осуществления управления данной системой одним объектом достаточно в поле микроопераций микрокоманды, следующей перед микрокомандой передачи управления, записать одни нули, а выходы управления 14.1-14.4 системы объединить соответственно по ИЛИ.

По заднему фронту очередного тактового импульса с первого выхода 7.1 генератора адрес очередной микрокоманды, пройдя через коммутатор 38, запишется в регистр 29 адреса (фиг. 3). На выходе блока 27 постоянной памяти микрокоманд появляется очередная микрокоманда.

Ветвление в микропрограмме происходит следующим обра.зом. Проверяемые логические условия с входа 11 условий поступают на входы 18.1 всех 1-4 модулей ПЗУ (это в данном примере. Возможна и подача своих логических условий на каждый ММПУ), С входа 18.1 условий модуля 1 МПУ эти логических условий поступают на входы DI-D соответственно мультиплексора 34. На адресный вход этого же мультиплексора поступает поле логических условий микрокоманды, стоящей на выходе блока 28 постоянной памяти микрокоманд в данный момент времени, т.е. код проверяемого в данный момент логического условия. На вход Do мультиплексора 34 поступает младший разряд адреса микрокоманды, следующей за микрокомандой ветвления.

Поле логических условий у команд безусловного перехода содержит одни нули. Следовательно, при выполнении таких команд младший разряд адреса очередной микрокоманды, пройдя через мультиплек- 5 сор и коммутатор 30, поступает на вход младшего разряда регистра 29 адреса без изменений. В микрокоманде же ветвления в поле логических условий находится двоичный код проверяемого логического условия 10 у, поступающего на соответствующий вход Оу мультиплексора 34. Следовательно, величина поля логических условий г определяется из соотношения:

г 1д2(.+ 1)Г,15

где г - количество разрядов поля условий;

. - количество проверяемых логических условий.

Таким образом, в зависимости от того, каким был младший разряд поля адреса в 20 микрокоманде ветвления, возможны следуг ющие переходы. В случае, если этот разряд равен нулю, то переход будет либо к микрокоманде с таким же адресом, либо с адресом на единицу большим, соответственно, в 25 случае равенства проверяемого логического условия нулю либо единице. В случае же равенства этого разряда единице ситуация аналогична с той лищь разницей, что переход будет к микрокоманде с адресом на еди- 30 ницу меньшим в случае, когда проверяемое логическое условие равно нулю.

Каждый из модулей, если он находится в активном состоянии, работает по описанному алгоритму,35

Рассмотрим, как происходит передача правления от одного ММПУ к другому. Пусть первый 1 ММПУ передает управление второму модулю 2. По очередному (в данном примере четвертому) тактовому импульсу, 40 поступившему с первого 7.1 выхода генераора 7, в регистр 29 пуска адреса первого 1 модуля ММПУ записался адрес микрокоманды, передающей управление другому модулю. В этом случае на первом выходе 45 27.1 блока 27 постоянной памяти микрокоманд появятся нуль (фиг. 3). Поле адреса выход 27.2) будет теперь содержать не адрес очередной микрокоманды выполняемой икропрограммы, а адрес модуля, которому 50 передается управление(К разрядов) и сжаый адрес начальной микрокоманды микропрограммы, которую начнет выполнять ММПУ берущий управление. Назовем его дресом передачи управления.55

Величина К определяется исходя из коичества модулей в системе

К ЧдаМ,

где а - означает округление числа а до ближайшего большого целого.

Содержание поля микроопераций и логических условий безразлично.

Как только на выходе блока 27 постоянных памяти микрокоманд появилась такая команда, адрес передачи управления через теперь открытый элемент И 36 поступает на все п выходов передачи управления первого ММПУ 1, а следовательно, и на первые входы 23.1.1 приема управления всех остальных ММПУ системы. Запись содержимого поля микроопераций в регистр 30 в модуле 1 ММПУ не происходит, на инверсном управляющем входе - единица.

Под сжатым начальным адресом будем понимать следующее. Блок 27 постоянной памяти микрокоманд любого ММПУ может содержать N микрокоманд. Одна среди них - это начальная микрокоманда микропрограммы, реализуемой данным ММПУ. Таких команд может быть несколько, в случае, если модуль может активизироваться несколько раз (допустим М) за полный цикл управления. Но в любом случае М « N, следовательно, передавать весь адрес нецелесообразно-большая избыточность, ведь

а lg2N ,

но М « N, следовательно, для передачи М адресов не требуется такого количества разрядов, можно обойтись меньшим, для чего необходимо передавать адрес в закодированном виде. При приеме такого кода происходит декодирование адреса до исходного состояния с помощью блока 28 памяти адресов.

Адрес передачи управления, состоящий из сжатого адреса начальной микрокоманды и адреса модуля, которому передается управление, поступает на первые выходы 23.1.1 всех остальных модулей 2-4 системы. Допустим, управление передается второму 2 ММПУ. В данном модуле на входе блока 27 памяти микрокоманд стоит нулевой адрес, который в каждом такте вновь записывается с выхода блока 27 памяти адресов в регистр 29 адреса через коммутатор 38. Этот нулевой адрес записан в ячейку с нулевым адресом блока 28 постоянной памяти адресов во всех ММПУ. Так как на выходе мажоритарного элемента 32 нуль, то и на выходе мажоритарного элемента 33 также находятся одни нули. Модуль находится в ожидании приема управления. С приходом на вход 23.2.1 второго модуля 2 МПУ адреса передачи управления ничего не изменяется, так как совпадение адреса модуля, который должен взять управление с собственным адресом второго ММПУ 2, который поступает на входы элементов сравнения 31.131.П-1 через открытый элемент И 37 с выхода 27.2 блока постоянной памяти 27 микрокоманд (К разрядов), произошло только в одном (первом) 31.1 элементе сравнения. Но адрес передачи управления с выходов первого ММПУ 1 поступил на входы 23.3.1 - и 23.4.1 третьего и четвертого ММПУ соответственно. В этих модулях совпадение соб- ственных адресов, стоящих на входах элементов сравнения 31.1-31.n-1, произойти не может. Но этот адрес передачи управления поступает еще и на вход данных демультиплексоров 31.1-39.п всех трех ММПУ 2-4, а на адресный вход этих демультиплексоров поступает адрес модуля, которому передается управление. Демультиплексоры коммутируют адрес передачи управления на соответствующий, в данном примере второй, выход передачи управления (22.2.2, 22.3.2, 22.4.2 соответственно во втором, третьем и четвертом ММПУ). Но второй выход 22.3.2 передачи управления третьего 3 ММПУ соединен с вторым входом 23.2.2 приема управления второго 2 ММПУ (см. фиг. 1), в свою очередь, второй выход 22.4.2 передачи управления четвертого 4 ММПУ соединен с третьим входом 23.2.3 приема управления второго ММПУ 2. Таким образом, на все три входа 23.2.1-23.2.3 входа приема управления второго модуля 2 поступает адрес передачи управления от первого 1 ММПУ, Возможна реализация проверки исправности линий связи между ММПУ и маскирования отказов (сбоев) путем использования метода голосования по большинству.

Итак, на всех трех входах приема управления второго ММПУ находятся теперь одинаковые данные. Следовательно, на выходах всех п-1 элементов сравнения 31.1-31.() данного ММПУ появятся единицы. Три единицы поступают на входы мажоритарного элемента 32, на его выходе - единица, открывающая мажоритарный элемент 33, на входы которого поступают сжатые адреса (К разрядов) с входов 23.2.1-23.2.3 приема управления. С выхода мажоритарного элемента 33 сжатый адрес поступает на вход блока 28 постоянной памяти адресов, где он преобразуется в нормальной а-разрядный адрес начальной микрокоманды. Этот начальный адрес через коммутатор 38 поступает на информационный вход регистра 29 адреса, куда и записывается по очередному тактовому импульсу с первого 7.1 выхода генератора 7. Как только на выходе блока 27 постоянной памяти микрокоманд второго ММПУ 2 появится начальная микрокоманда, на первом 27.1 выходе этого блока установится нулевой потенциал, который подключит с помощью коммутатора 38 выход 27.2 поля адреса блока 27 постоянной памяти микрокоманд к входу регистра 29 адреса, отключив при этом от

него выход блока 28 постоянной памяти адресов. Модуль 2 перешел в активный режим. В это же время в модуле 1 по заднему фронту того же (пятого) импульса с первого 7.1 выхода генератора 7 в регистр адреса с

0 выхода блока 28 постоянной памяти адресов, который подключен теперь к информа-. ционному входу регистра 29 адреса, запишутся одни нули, так как на входе блока

28адресов стоит нулевая комбинация, по- 5 ступающая с выхода закрытого можаритарного элемента 33. Открытым этот элемент быть не может, так как ни в одном из элементов сравнения 31.1-31.гНпроизойти совпадения не может, ведь на один из вхо0 дов всех элементов сравнения поступает адрес второго модуля 2, а на вторые- нули, так как на входы передачи управления 23.1.1- 23.1.п-1 ничего, кроме нулей, не поступает. Адрес модуля нулевым быть не может. Как

5 только нулевой адрес запишется в регистр

29адреса в первом ММПУ 1, на выходе 27.2 блока 27 постоянной памяти микрокоманд появится очередная (нулевая) микрокоманда. Единица на выходе 27.1 сохранится, а

0 вот в поле адреса, вернее в той его части, где записан код модуля-, которому передается управление, будет теперь записан код собственного модуля, т.е. первого. Этот код поступает на входы элементов сравнения

5 31.1.-31.п-1. Модуль перешел в режим ожидания приема управления. Далее система работает аналогично описанному.

Кроме того, в системе предусмотрен контроль за ее функционированием. Прин0 цип контроля основан на следующем. В системе не может быть более одного одновременно работающего модуля, но в то же время, не может быть и такого состояния, при котором не работает ни один модуль. В

5 оба эти состояния система может перейти как в результате аппаратных отказов (сбоев) в самих ММПУ, так и в результате отказов, а что более вероятно сбоев, возникающих в результате каких-либо помех в линиях связи

0 между ММПУ. Именно с целью маскирования последних и введено (п-1)-кратное резервирование линий связи. Итак, состояние, при котором одновременно работает более, чем один ММПУ, контролиру5 ется с помощью порогового элемента 8. На его входы (и х п) с выходов 17.1 состояния всех ММПУ поступают сигналы, говорящие о том, в каком из двух состояний, активном или ожидания, находятся модули. Фактически на входы порогового элемента 8 поступают сигналы с выходов 27.1 блоков 27 постоянной памяти микрокоманд всех ММПУ. Если на инверсных входах порогового элемента 8 (см. фиг. 1) появятся хотя бы два нуля, на его выходе появится единица, кото- рая через элемент ИЛИ 10 поступит на К- вход триггера 6 пуска. По заднему фронту первого же импульса, поступившего с первого выхода 7.1 генератора 7, триггер 6 пуска перейдет в нулевое состояние, остановив тем самым генератор 7 и систему в целом, выдавая на выход 26 состояния системы нулевой потенциал.

Случай не работы ни одного из ММПУ системы более сложен. Как видно из вре- менной диаграммы (фиг. 3), даже при нормальном функционировании системы в случае передачи управления от модуля к модулю в течение одного такта существует такое состояние, при котором на выходах 27.1 блоков 27 постоянной памяти микрокоманд всех ММПУ будут единицы (между 4-м и 5-м импульсами). Такое состояние возникает, когда один из модулей передает управление, а второй его принимает. Но это состоя- ние не может длиться более одного такта. Следовательно, задержка времени существования такого состояния более, чем на один такт, равносильна отказу системы. Это может произойти, например, в случае, когда между модулями, передающим управление и принимающим его, остались исправными менее двух линий связи либо сбои произошли во всех линиях и управление верно передано быть не может. Мгновенный останов системы и наличие контрольных незадействованных по связи выходов у каждого модуля дают возможность довольно полно и быстро выяснить причину останова.

Выход i передачи управления модуля i не задействован для связи с другими модулями (следовательно, менее подвержен сбоям и отказам), является i-м контрольным выходом системы (14.1-14.4). Всего таких выходов у системы п. С их помощью можно организовать внешний по отношению к системе аппаратный диагностический контроль.

Контроль за длительностью состояния, при котором не работают все л модулей (в нашем примере п 4) системы, осуществляется с помощью элемента И 9 и счетчика 5. Как только все модули системы вышли из активного состояния, на выходе элемента И 9 появляется единица, которая разрешает работу счетчика 5, находившегося в нулевом состоянии. Так как при нормальном функционировании системы единица может возникать на выходе элемента И 9 в промежутке между задними фронтами импульсов, поступающих с первого 7.1 выхода генератора 7 (см. фиг. 3), то синхронизацию счетчика 5 будем осуществлять импульсами, поступающими с второго выхода 7.2 счетчика 7. Счетчику 5 отказа разрешается считать до одного. Если он перешел из состояния 01 в состояние 00, то считается, что система работает нормально. Но так только счетчик успел достигать до двух (10), фиксируется отказ системы. Ведь длительность импульса на выходе элемента И 9 не может быть больше одного периода частоты генератора 7, следовательно, если счетчик 5 досчитал до двух, значит все ММПУ системы не работают более одного такта - а это отказ, о чем и говорит единица, поступающая с второго разряда счетчика 7 через элемент ИЛИ 10 на К-вход триггера 6 пуска, который обнуляется первым же импульсом с первого выхода 7.1 генератора 7.

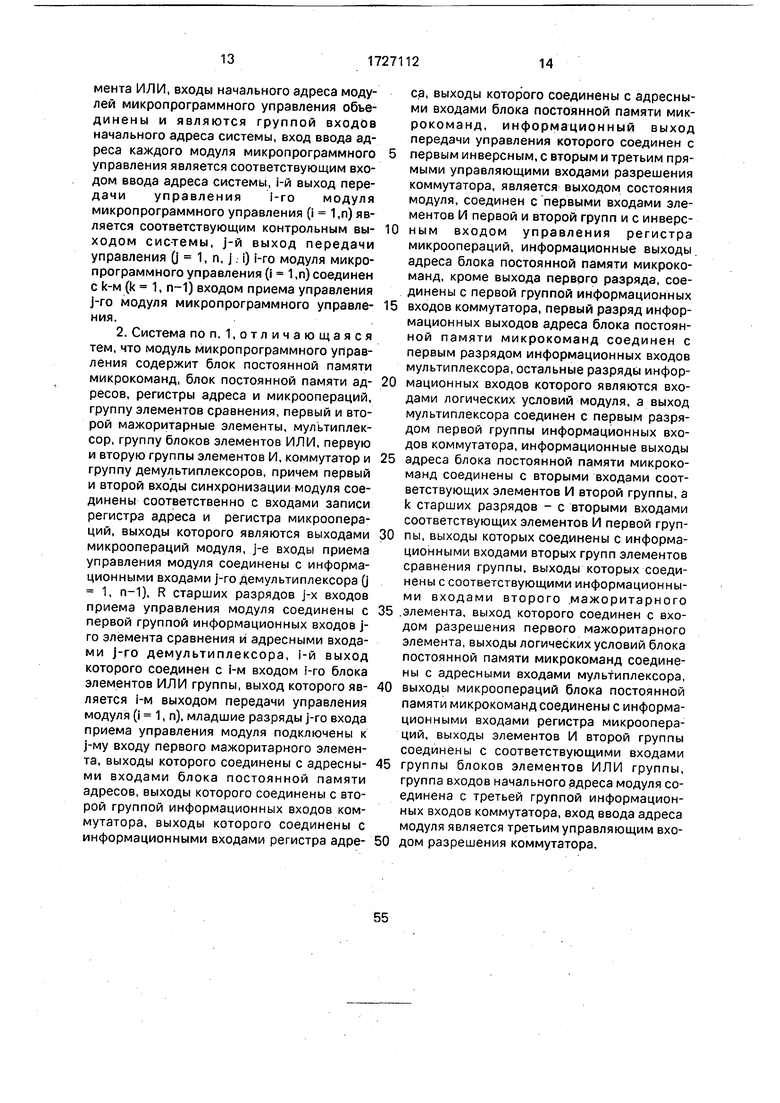

Формула изобретения 1. Распределенная система для программного управления с мажоритировани- ем, содержащая триггер пуска, генератор тактовых импульсов и п модулей микропрограммного управления, причем вход пуска системы соединен с асинхронным установочным входом триггера пуска, прямой выход которого является выходом состояния системы и соединен с разрешающим входом генератора тактовых импульсов, первый выход которого соединен с синхровходом триггера пуска и с первыми входами синхронизации всех модулей микропрограммного управления, второй выход генератора тактовых импульсов соединен с вторыми входами синхронизации всех модулей микропрограммного управления, выходы микроопераций которых являются соответствующими выходами микроопераций системы, входы логических условий модулей микропрограммного управления объединены и являются входами логических условий системы, отличающаяся тем, что, с целью повышения надежности функционирования системы, в нее введены пороговый элемент, счетчик отказа, элемент И и элемент ИЛИ, выход которого соединен с синхровходом сброса триггера пуска, второй выход генератора тактовых импульсов соединен со счетным входом счетчика отказов, выход второго разряда которого соединен с первым входом элемента ИЛИ, выход состояния каждого модуля микропрограммного управления соединен с соответствующим входом порогового элемента и входом элемента И, выход которого соединен с входом разрешения и инверсным входом сброса счетчика отказа, выход порогового элемента соединен с вторым входом элемента ИЛИ, входы начального адреса модулей микропрограммного управления объединены и являются группой входов начального адреса системы, вход ввода адреса каждого модуля микропрограммного управления является соответствующим входом ввода адреса системы, i-й выход передачи управления i-ro модуля микропрограммного управления (i 1,n) является соответствующим контрольным выходом сис-темы, j-й выход передачи управления Q 1, n, j. i) i-ro модуля микропрограммного управления (i 1 ,п) соединен с к-м (к 1, п-1) входом приема управления j-ro модуля микропрограммного управления.

2. Система по п. 1,отличающаяся тем, что модуль микропрограммного управления содержит блок постоянной памяти микрокоманд, блок постоянной памяти адресов, регистры адреса и микроопераций, группу элементов сравнения, первый и второй мажоритарные элементы, мультиплексор, группу блоков элементов ИЛИ, первую и вторую группы элементов И, коммутатор и группу демультиплексоров, причем первый и второй входы синхронизации модуля соединены соответственно с входами записи регистра адреса и регистра микроопераций, выходы которого являются выходами микроопераций модуля, j-e входы приема управления модуля соединены с информационными входами j-ro демультиплексора (J 1, n-1), R старших разрядов j-x входов приема управления модуля соединены с первой группой информационных входов j- го элемента сравнения и адресными входами j-ro демультиплексора, i-й выход которого соединен с i-м входом i-ro блока элементов ИЛИ группы, выход которого является i-м выходом передачи управления модуля (i 1, п), младшие разряды j-ro входа приема управления модуля подключены к j-му входу первого мажоритарного элемента, выходы которого соединены с адресными входами блока постоянной памяти адресов, выходы которого соединены с второй группой информационных входов коммутатора, выходы которого соединены с информационными входами регистра адреса, выходы которого соединены с адресными входами блока постоянной памяти микрокоманд, информационный выход передачи управления которого соединен с

первым инверсным, с вторым и третьим прямыми управляющими входами разрешения коммутатора, является выходом состояния модуля, соединен с первыми входами элементов И первой и второй групп и с инверсным входом управления регистра микроопераций, информационные выходы адреса блока постоянной памяти микрокоманд, кроме выхода первого разряда, соединены с первой группой информационных

входов коммутатора, первый разряд информационных выходов адреса блока постоянной памяти микрокоманд соединен с первым разрядом информационных входов мультиплексора, остальные разряды информационных входов которого являются входами логических условий модуля, а выход мультиплексора соединен с первым разрядом первой группы информационных входов коммутатора, информационные выходы

адреса блока постоянной памяти микрокоманд соединены с вторыми входами соответствующих элементов И второй группы, а k старших разрядов - с вторыми входами соответствующих элементов И первой группы, выходы которых соединены с информационными входами вторых групп элементов сравнения группы, выходы которых соединены с соответствующими информационными входами второго мажоритарного

.элемента, выход которого соединен с входом разрешения первого мажоритарного элемента, выходы логических условий блока постоянной памяти микрокоманд соединены с адресными входами мультиплексора,

выходы микроопераций блока постоянной памяти микрокоманд соединены с информационными входами регистра микроопераций, выходы элементов И второй группы соединены с соответствующими входами

группы блоков элементов ИЛИ группы, группа входов начального адреса модуля соединена с третьей группой информационных входов коммутатора, вход ввода адреса модуля является третьим управляющим входом разрешения коммутатора.

Щиг.1

21.i(n-D a

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении агрегатируе- мых отказоустойчивых систем для управления технологическими процессами. Цель изобретения - повышение надежности функционирования системы. Поставленная цель достигается тем, что в систему, содержащую триггер пуска, генератор тактовых импульсов и п модулей микропрограммного управления, дополнительно введены пороговый элемент, счетчик отказа, элемент И и элемент ИЛИ. Введение новых элементов обеспечивает повышение достоверности передачи информации между модулями системы при передаче управления от одного модуля к другому за счет многомаршрутно- сти, что дает возможность при приеме исправлять сбои или отказы, возникшие в процессе функционирования системы. Т з.п. ф-лы, 3 ил. (Л С

I q-к

a-K

2Ы o

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-04-15—Публикация

1990-04-02—Подача