Изобретение относится к области электротехники, а именно к цифровым делителям частоты, и может быть использовано в системах фазовой автоподстройки частоты (ФАПЧ).

При больших значениях синтезируемых частот в системах фазовой автоподстройки частоты актуальна проблема проектирования делителя частоты с высокой входной частотой. Если стандартный синхронный счётчик не может работать на высокой частоте, требуется поиск альтернативных решений, например, таких, как переход от стандартных триггеров в пользу триггеров на дифференциальной логике или динамических триггеров, память которых основана на паразитных ёмкостях. Но такие триггеры требуют совершенно другого маршрута проектирования (значительно более затратного) по сравнению с классическим маршрутом, основанном на применении стандартной логики.

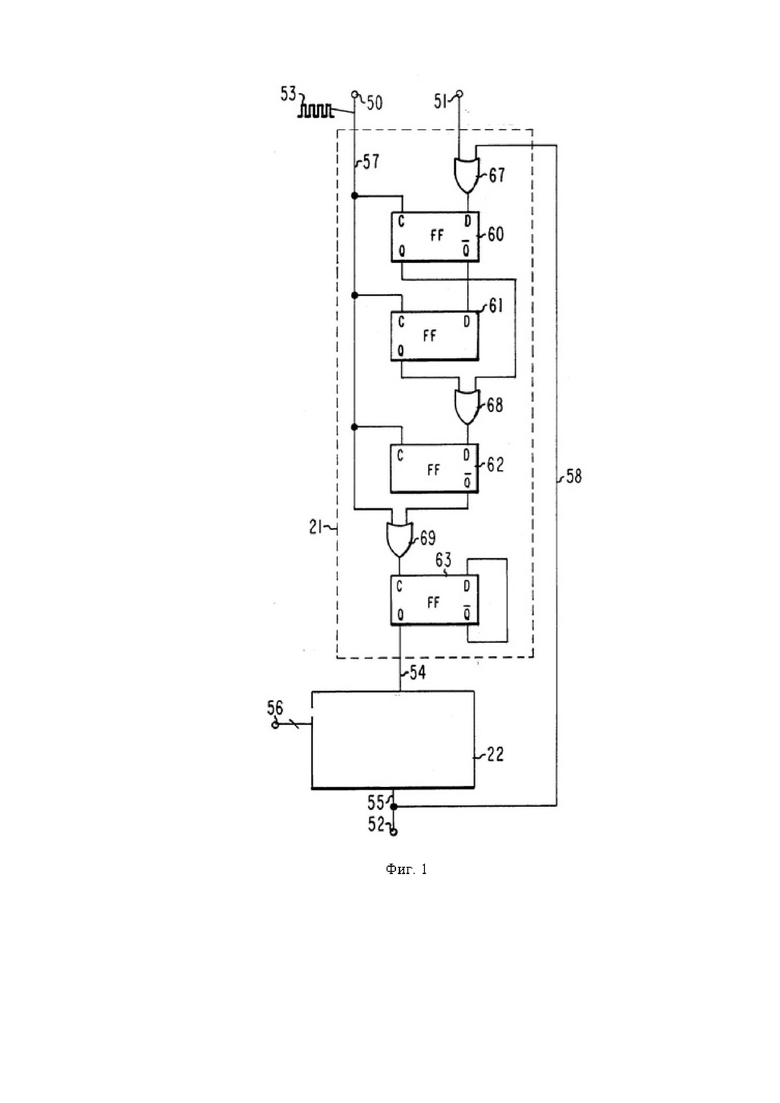

Наиболее близким к заявленному изобретению является дробный цифровой делитель частоты, описанный в патенте US4573176, в котором для повышения быстродействия используется предделитель частоты входного сигнала на два, который для получения нечётного коэффициента деления пропускает один импульс входного тактового сигнала каждый раз, когда выходной сигнал программируемого делителя, выполненного на основе счётчика, принимает заданное логическое состояние (см. последнее предложение раздела abstract на первой странице). «Обоснование такого решения заключается в том, что «программируемые делители имеют довольно сложную логику с относительно большими задержками распространения и установки сигналов. Поэтому они не могут работать на высоких частотах (500-750 МГц, в настоящее время типичное ограничение составляет 250 МГц). В патентуемом делителе ограничение по частоте преодолено благодаря использованию предделителя…» На Фиг. 1 показано, что блоки 61 и 68 также как в заявленном изобретении формирует детектор переднего фронта выходного сигнала счётчика, а блок 63 – предделитель на два. Данный цифровой делитель частоты выбран в качестве прототипа изобретения.

Недостаток прототипа заключается в следующем. В отличие от заявленного изобретения, в прототипе пропуск одного импульса входного тактового сигнала предделителем, выполненным на триггере 63, осуществляется за счёт блокирования тактового входа С триггера 63 логическим элементом 69. Наличие логического элемента в цепи тактового сигнала триггера приводит к увеличению задержки передачи сигнала и тем самым уменьшает значение максимальной рабочей частоты всей схемы. Кроме того, известно, что дополнительные буферы или логические элементы в цепи тактового сигнала увеличивают фазовый шум (джиттер) выходных сигналов. Джиттер является критичным параметром для таких систем, как например, синтезаторы частот, цифровые приёмопередатчики, аналого-цифровые преобразователи.

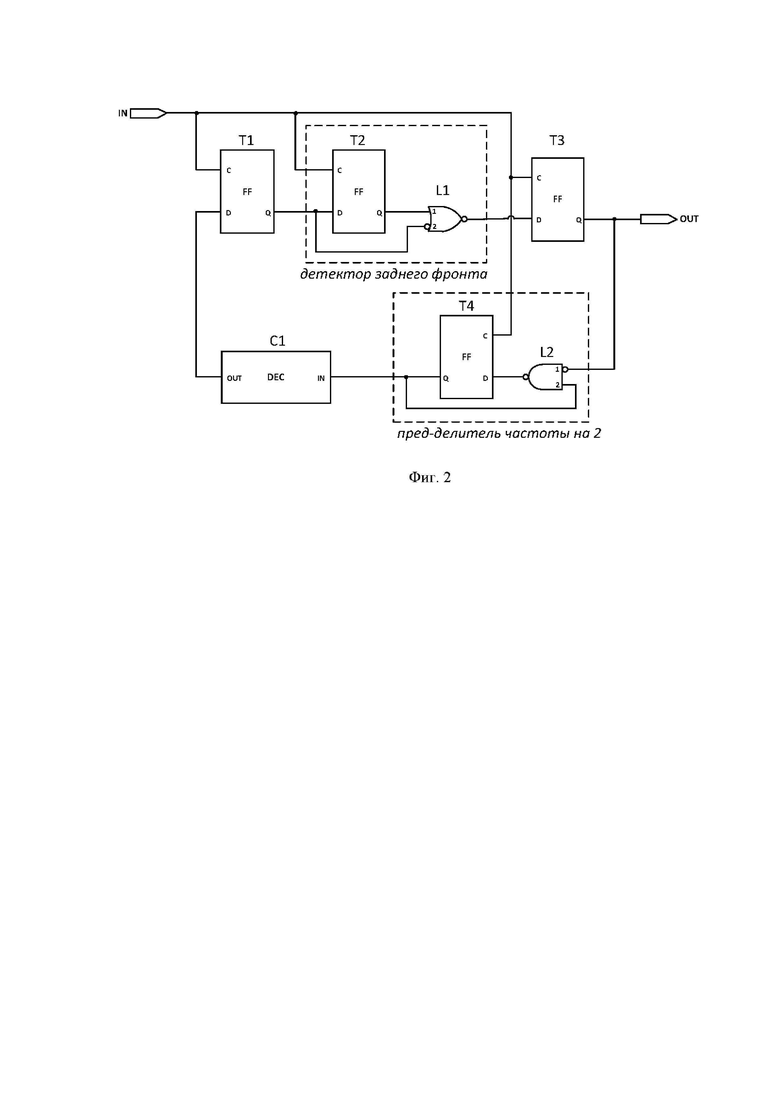

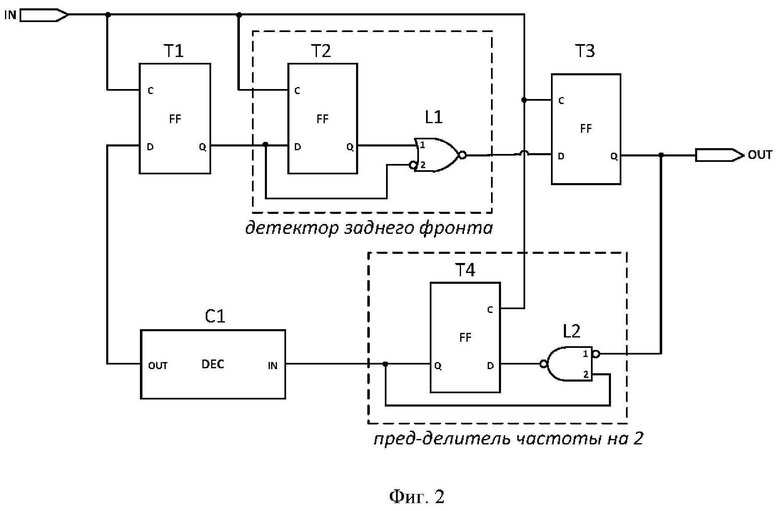

В заявленном изобретении указанный недостаток устранён за счёт подключения логического элемента L2 не к тактовому входу С триггера T4, а к его информационному входу D. Триггер T4 предделителя постоянно тактируется входным сигналом (поэтому отсутствует дополнительная задержка сигнала, и не возрастает джиттер), но благодаря введению логического элемента L2 в цепь его обратной связи между информационным входом D и выходом Q, пропуск одного импульса входного тактового сигнала происходит за счёт перезаписывания в триггер Т4 логической «1», когда выходной сигнал делителя OUT принимает значение «1», в результате состояние триггера Т4 не меняется на противоположное, и состояние «1» на его выходе продлевается на один импульс входного тактового сигнала, что так же, как и в прототипе, позволяет получить нечётный коэффициент деления частоты.

Техническим результатом изобретения является создание синтезируемого цифрового делителя частоты с увеличенным предельным значением частоты тактового сигнала, за счет установки логического вентиля на сигнале обратной связи.

Поставленный технический результат достигнут путем создания цифрового делителя частоты, содержащего соединенные между собой четыре D-триггера, два логических элемента и счетчик, причем вход делителя частоты соединен с тактовыми входами четырех D-триггеров, информационный вход первого D-триггера соединен с выходом счетчика, вход которого соединен с выходом четвертого D-триггера, информационный вход которого соединен с выходом второго логического элемента, первый вход которого соединен с выходом третьего D-триггера и выходом делителя частоты, а второй вход второго логического элемента соединен с входом счетчика и с выходом четвертого D-триггера, при этом выход первого D-триггера соединен с информационным входом второго D-триггера, выход которого соединен с первым входом первого логического элемента, выход которого соединен с информационным входом третьего D-триггера, выход которого соединен с выходом делителя частоты, а второй вход первого логического элемента соединен с выходом первого D-триггера и с информационным входом второго D-триггера, о т л и ч а ю щ е г о с я тем, что второй D-триггер и первый логический элемент образуют детектор заднего фронта, а четвертый D-триггер и второй логический элемент образуют предделитель частоты на два, при этом второй логический элемент подключен к информационному входу четвертого триггера и выполнен с возможностью обеспечения пропуска предделителем одного такта входного сигнала.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

Фиг. 1. Логическая схема цифрового делителя частоты, выполненная согласно прототипу.

Фиг. 2. Логическая схема цифрового делителя частоты на нечётное число 2N+1, выполненная согласно изобретению.

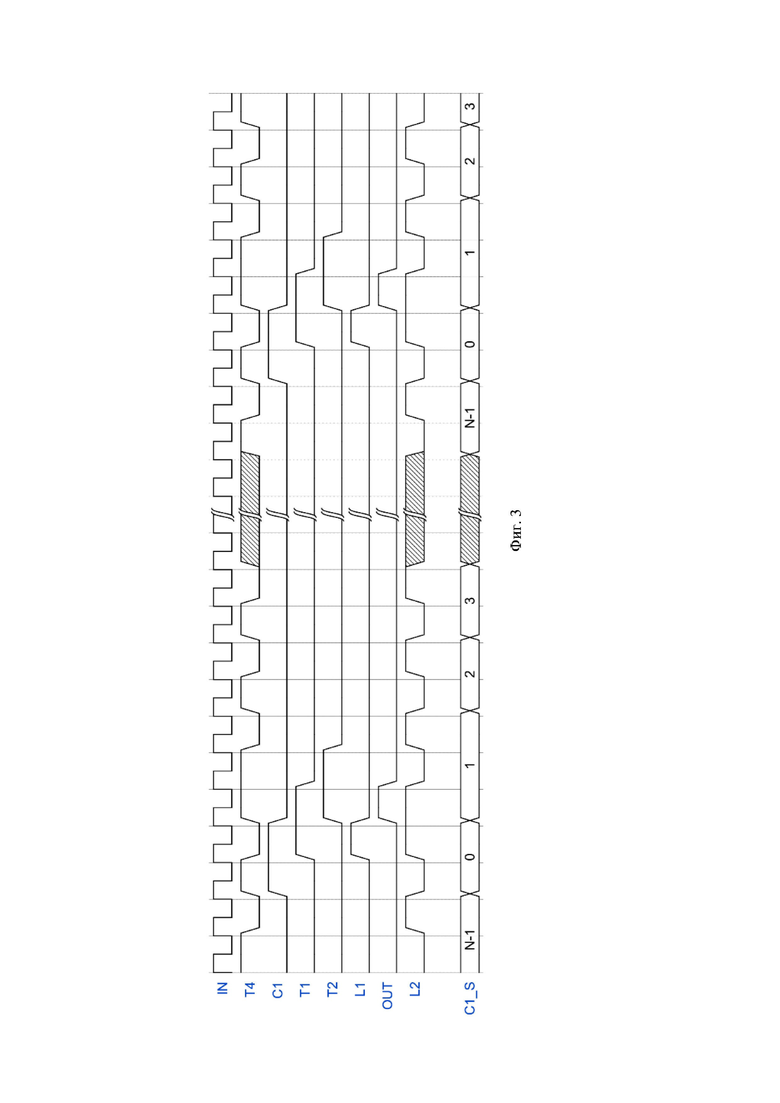

Фиг. 3. Временные диаграммы сигналов цифрового делителя частоты на 2N+1, выполненные согласно изобретению.

Рассмотрим принцип функционирования заявленного цифрового делителя частоты. Например, для формирования целочисленного синтезатора, позволяющего получить выходную частоту 1590 МГц из входной частоты 30 МГц, необходим делитель частоты 1.59 ГГц на нечётное число 53. На стандартной логике используемой технологии такой делитель синтезировать невозможно по причине нехватки быстродействия базовых логических элементов. Чётные коэффициенты деления легче получить, используя предделитель на два, а затем делитель нужной разрядности на основе синхронного счётчика. Для получения же нечётных коэффициентов деления (2N+1) было воплощено оригинальное решение: предделитель частоты на два тактирует делитель частоты на N, выполненный на синхронном счётчике, и после того, как счётчик досчитывает до N-1, предделитель пропускает один такт входного сигнала. В результате выходной сигнал имеет период в (2N+1) раз превышающий период входного сигнала.

Данное решение применимо так же и для построения делителя на произвольное число N (например, для данного примера разрядность счётчика может быть 7 бит). В таком делителе функция пропуска такта активна для нечётных N и отключена для чётных. Фактически младший бит управляет функцией пропуска 1 такта.

Рассмотрим вариант выполнения заявленного цифрового делителя частоты (Фиг. 2). Цифровой делитель частоты содержит четыре D-триггера Т1, Т2, Т3, Т4, два логических элемента L1 и L2 и счетчик C1. Вход делителя частоты соединен с тактовыми входами четырех D-триггеров Т1, Т2, Т3, Т4. Информационный вход первого D-триггера соединен с выходом счетчика С1. Вход счетчика С1 соединен с выходом четвертого D-триггера Т4. Информационный вход четвертого D-триггера Т4 соединен с выходом второго логического элемента L2. Первый вход второго логического элемента L2 соединен с выходом третьего D-триггера Т3 и выходом делителя частоты. Второй вход второго логического элемента L2 соединен с входом счетчика C1 и с выходом четвертого D-триггера Т4. Выход первого D-триггера Т1 соединен с информационным входом второго D-триггера Т2. Выход второго D-триггера Т2 соединен с первым входом первого логического элемента L1. Выход первого логического элемента L1 соединен с информационным входом третьего D-триггера Т3. Выход третьего D-триггера Т3 соединен с выходом делителя частоты. Второй вход первого логического элемента L1 соединен с выходом первого D-триггера Т1 и с информационным входом второго D-триггера Т2.

На схеме Фиг. 2 (результат синтеза RTL) D-триггеры T1 и T2 задерживают на два такта входного сигнала IN выходной сигнал синхронного счётчика C1. На выходе логического элемента L1 формируется «1» только тогда, когда выходной сигнал первого D-триггера T1 равен «1», а выходной сигнал второго D-триггера T2 равен «0». Так детектируют задний фронт импульса на выходе счётчика С1. Третий D-триггер T3 задерживает выходной сигнал первого логического элемента L1 на один такт входного сигнала IN и формирует выходной сигнал OUT. Четвертый D-триггер T4 c логическим элементом L2 образуют предделитель частоты входного сигнала IN на два. Цифровой предделитель частоты работает, когда его выходной сигнал OUT равен «0», и устанавливается в состояние «1» по следующему переднему фронту входного сигнала IN после установки сигнала OUT в «1». В данной схеме цифрового делителя частоты вышеописанный механизм управления обеспечивает продление состояния «1» на выходе предделителя на один такт входного сигнала IN. В результате задерживается тактирование счётчика C1 (который делит частоту на N) на один такт входного сигнала IN, что обеспечивает деление частоты входного сигнала IN на 2N+1.

Хотя описанный выше вариант выполнения заявленного изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

| Устройство для ввода аналоговой информации | 1989 |

|

SU1672434A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2300112C2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ФАЗЫ | 1992 |

|

RU2028727C1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Делитель частоты с переменным коэффициентом деления | 2020 |

|

RU2752485C1 |

| Устройство для извлечения квадратного корня из напряжения | 1989 |

|

SU1721615A1 |

Изобретение относится к области электротехники. Техническим результатом изобретения является создание синтезируемого цифрового делителя частоты с увеличенным предельным значением частоты тактового сигнала за счет установки логического вентиля на сигнале обратной связи. 3 ил.

Цифровой делитель частоты, содержащий соединенные между собой четыре D-триггера, два логических элемента и счетчик, причем вход делителя частоты соединен с тактовыми входами четырех D-триггеров, информационный вход первого D-триггера соединен с выходом счетчика, вход которого соединен с выходом четвертого D-триггера, информационный вход которого соединен с выходом второго логического элемента, первый вход которого соединен с выходом третьего D-триггера и выходом делителя частоты, а второй вход второго логического элемента соединен с входом счетчика и с выходом четвертого D-триггера, при этом выход первого D-триггера соединен с информационным входом второго D-триггера, выход которого соединен с первым входом первого логического элемента, выход которого соединен с информационным входом третьего D-триггера, выход которого соединен с выходом делителя частоты, а второй вход первого логического элемента соединен с выходом первого D-триггера и с информационным входом второго D-триггера, отличающийся тем, что второй D-триггер и первый логический элемент образуют детектор заднего фронта, а четвертый D-триггер и второй логический элемент образуют предделитель частоты на два, при этом второй логический элемент подключен к информационному входу четвертого триггера и выполнен с возможностью обеспечения пропуска предделителем одного такта входного сигнала.

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1503070A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1653156A1 |

| US 4573176 A1, 25.02.1986. | |||

Авторы

Даты

2022-03-15—Публикация

2021-08-18—Подача