Изобретение относится к области аналоговой микроэлектроники и может быть использовано в аналоговых интерфейсах и устройствах преобразования сигналов, в том числе работающих в диапазоне низких температур и проникающей радиации [1].

Быстродействие дифференциальных операционных усилителей (ДОУ), которое характеризуется максимальной скоростью нарастания выходного напряжения (Slew Rate – SR) и временем установления переходного процесса (tуст.), определяет динамические параметры многих аналоговых интерфейсов датчиков, буферных каскадов, АЦП, драйверов линий связи и т.п.

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители, реализуемые на основе двухканальной структуры входного каскада (Dual-Input-Stage), содержащего два параллельно-включенных по входу дифференциальных усилителя [2-45]. Причем структура Dual-Input-Stage реализуется как на биполярных [2-23], так и на полевых [24-45] транзисторах. Благодаря многоканальности такое схемотехническое решение достаточно популярно как в зарубежных, так и в российских широкополосных аналоговых микросхемах, в т.ч. с опцией rail-to-rail по выходу (т.е. диапазону изменения выходного напряжения ДОУ «от одной шины питания до другой»).

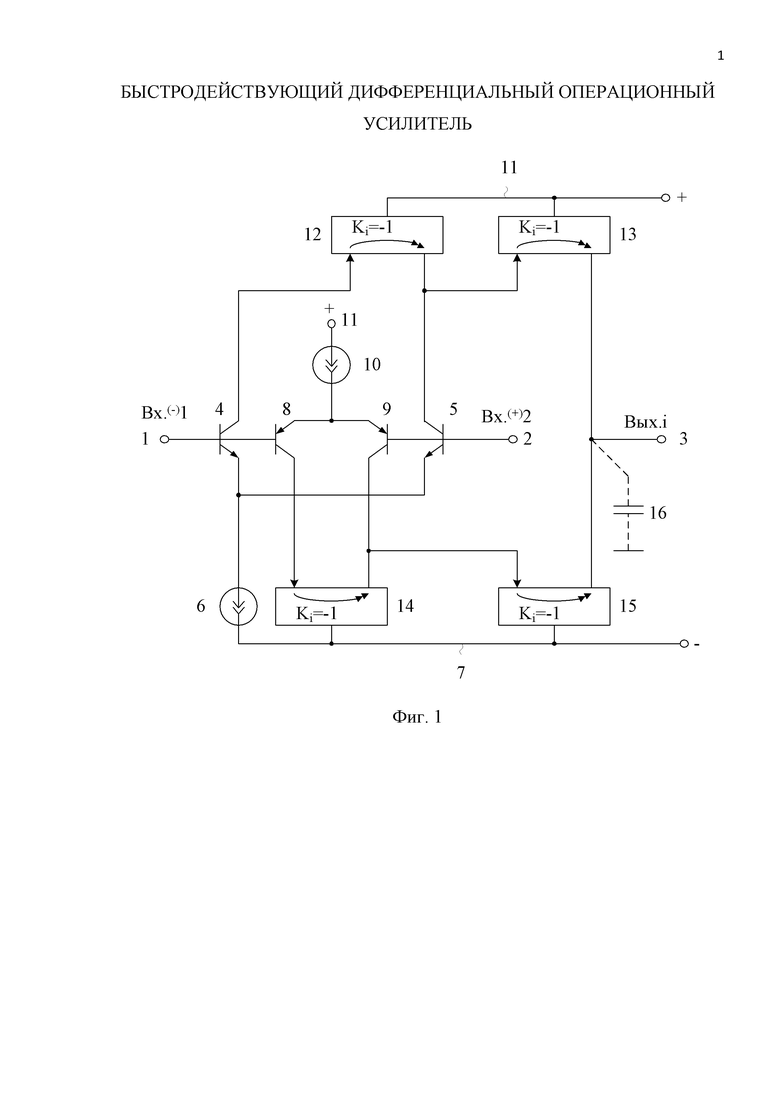

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ по патенту US 4.636.743, fig.1, (1987 г.). Он содержит (фиг. 1) первый 1 и второй 2 дифференциальные входы устройства, токовый выход 3 устройства, первый 4 входной транзистор, база которого соединена с первым 1 дифференциальным входом устройства, а эмиттер соединен с эмиттером второго 5 входного транзистора и через первый 6 токостабилизирующий двухполюсник соединен с первой 7 шиной источника питания, третий 8 входной транзистор, база которого соединена с первым 1 входом устройства, а эмиттер соединен с четвертым 9 входным транзистором и через второй 10 токостабилизирующий двухполюсник соединен со второй 11 шиной источника питания, причем базы второго 5 и четвертого 9 входных транзисторов соединены со вторым 2 входом устройства, коллектор первого 4 входного транзистора соединен со входом первого 12 токового зеркала, согласованного со второй 11 шиной источника питания, коллектор второго 5 входного транзистора подключен к токовому выходу первого 12 токового зеркала и входу второго 13 токового зеркала, согласованного со второй 11 шиной источника питания, коллектор третьего 8 входного транзистора соединен со входом третьего 14 токового зеркала, согласованного с первой 7 шиной источника питания, коллектор четвертого 9 входного транзистора подключен к токовому выходу третьего 14 токового зеркала и входу четвертого 15 токового зеркала, согласованного с первой 7 шиной источника питания, токовые выходы второго 13 и четвертого 15 токовых зеркал соединены с токовым выходом 3 устройства и первым 16 корректирующим конденсатором.

Существенный недостаток известного ДОУ фиг. 1 состоит в том, что в данной схеме не реализуется высокое быстродействие в режиме большого сигнала. Это обусловлено нелинейным режимом работы входного каскада (транзисторы 4, 5, 8,9, токовые зеркала 12, 14) и выходного каскада (токовые зеркала 13, 15) – отсутствием пропорциональности между входным дифференциальным напряжением ДОУ и током перезаряда первого 16 корректирующего конденсатора ДОУ [46].

Основная задача предполагаемого изобретения состоит в повышении более чем в 30 раз максимальной скорости нарастания выходного напряжения ДОУ, в т.ч. при работе входных транзисторов ДОУ в режиме микротоков, т.е. с малым энергопотреблением.

Поставленная задача достигается тем, что в дифференциальном операционном усилителе фиг. 1, содержащем первый 1 и второй 2 дифференциальные входы устройства, токовый выход 3 устройства, первый 4 входной транзистор, база которого соединена с первым 1 дифференциальным входом устройства, а эмиттер соединен с эмиттером второго 5 входного транзистора и через первый 6 токостабилизирующий двухполюсник соединен с первой 7 шиной источника питания, третий 8 входной транзистор, база которого соединена с первым 1 входом устройства, а эмиттер соединен с четвертым 9 входным транзистором и через второй 10 токостабилизирующий двухполюсник соединен со второй 11 шиной источника питания, причем базы второго 5 и четвертого 9 входных транзисторов соединены со вторым 2 входом устройства, коллектор первого 4 входного транзистора соединен со входом первого 12 токового зеркала, согласованного со второй 11 шиной источника питания, коллектор второго 5 входного транзистора подключен к токовому выходу первого 12 токового зеркала и входу второго 13 токового зеркала, согласованного со второй 11 шиной источника питания, коллектор третьего 8 входного транзистора соединен со входом третьего 14 токового зеркала, согласованного с первой 7 шиной источника питания, коллектор четвертого 9 входного транзистора подключен к токовому выходу третьего 14 токового зеркала и входу четвертого 15 токового зеркала, согласованного с первой 7 шиной источника питания, токовые выходы второго 13 и четвертого 15 токовых зеркал соединены с токовым выходом 3 устройства и первым 16 корректирующим конденсатором, предусмотрены новые элементы и связи – между входами второго 13 и четвертого 15 токовых зеркал включена цепь согласования потенциалов 17, причем между объединенными эмиттерами первого 4 и второго 5 входных транзисторов и объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов включен второй 18 корректирующий конденсатор.

На чертеже фиг. 1 показана схема ДОУ-прототипа.

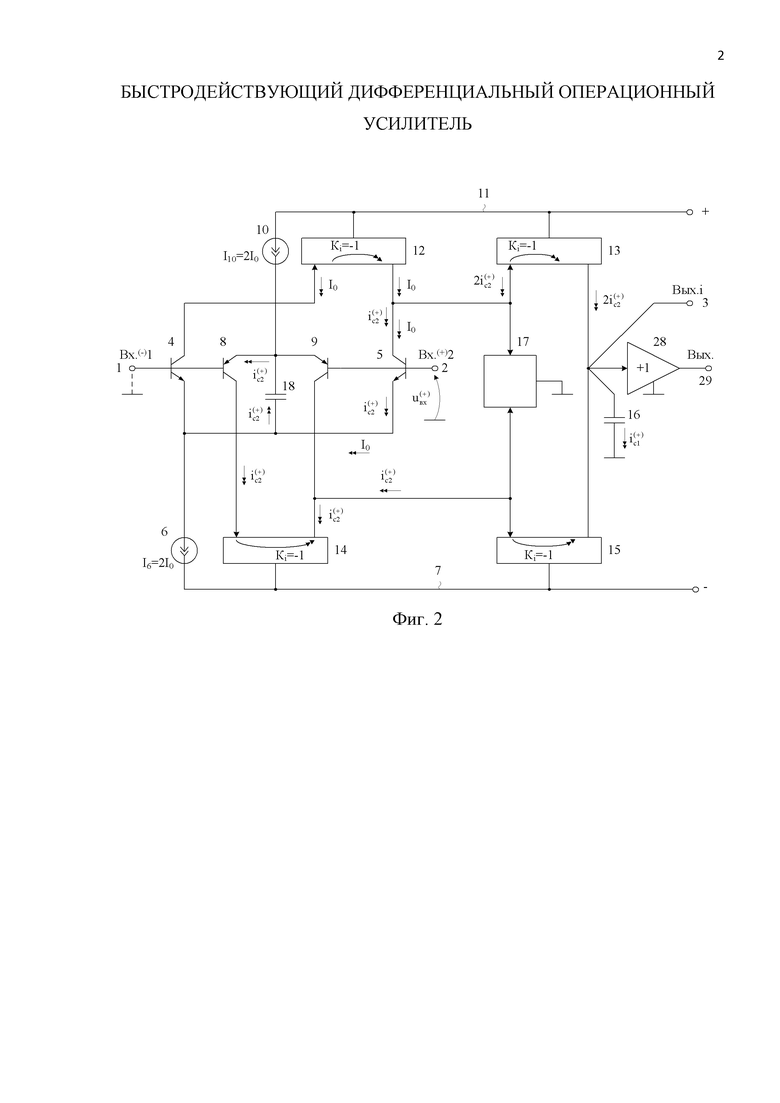

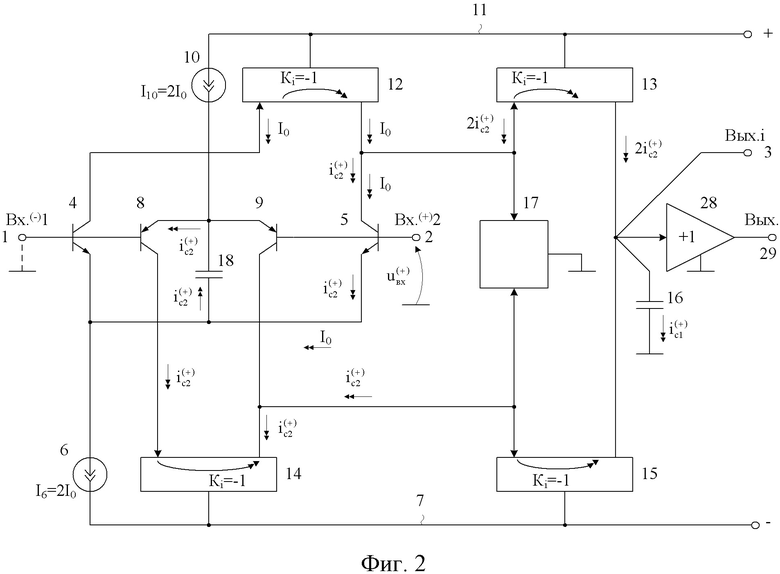

На чертеже фиг. 2 представлена схема заявляемого ДОУ в соответствии с п.1 и п.4 формулы изобретения.

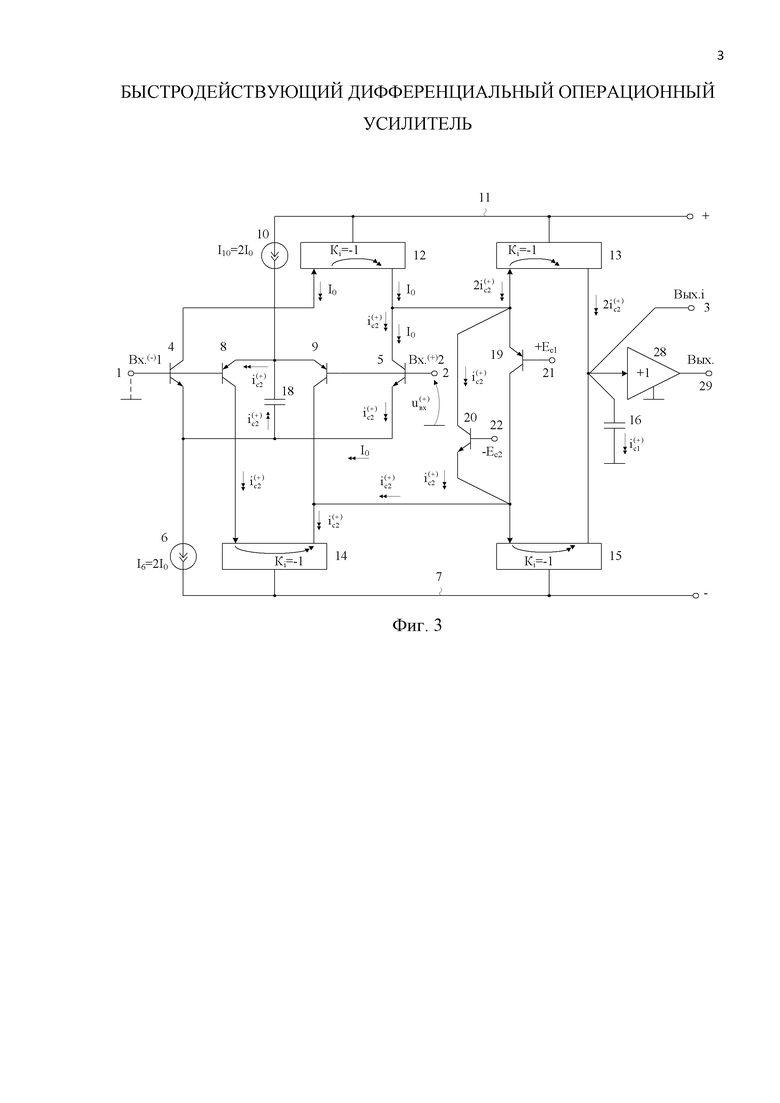

На чертеже фиг. 3 приведена схема заявляемого ДОУ в соответствии с п.2 и п.4 формулы изобретения.

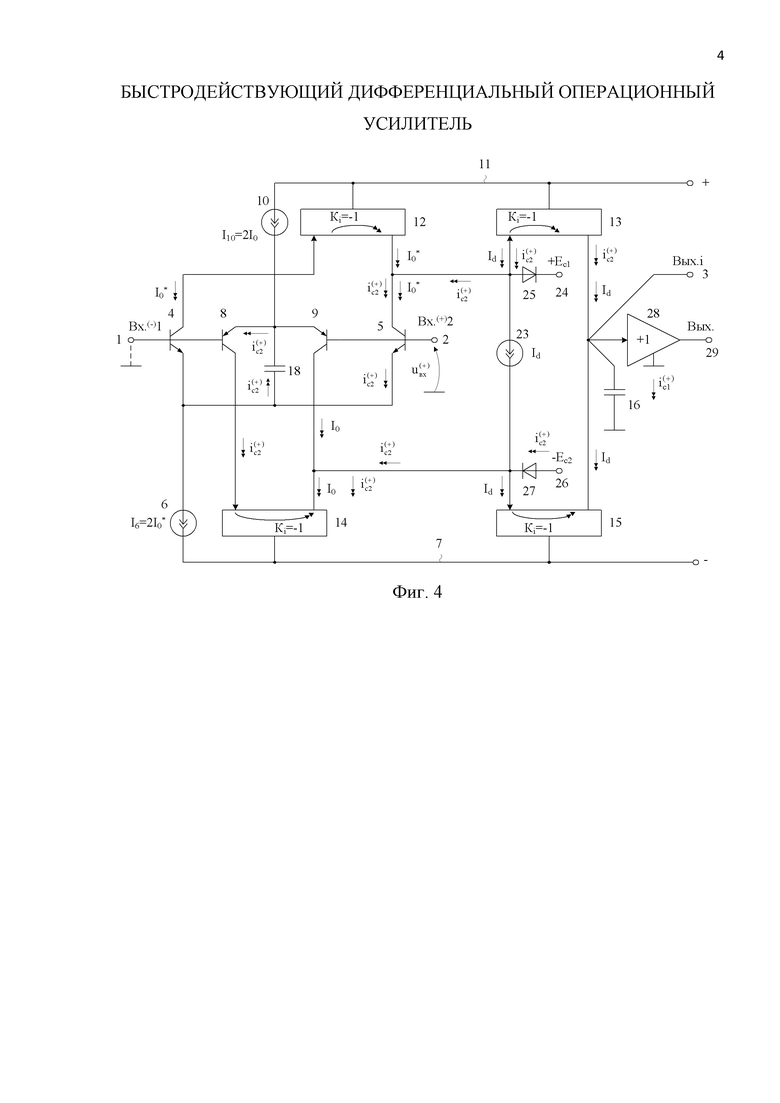

На чертеже фиг. 4 показана схема заявляемого ДОУ в соответствии с п.2, п.3 и п.4 формулы изобретения.

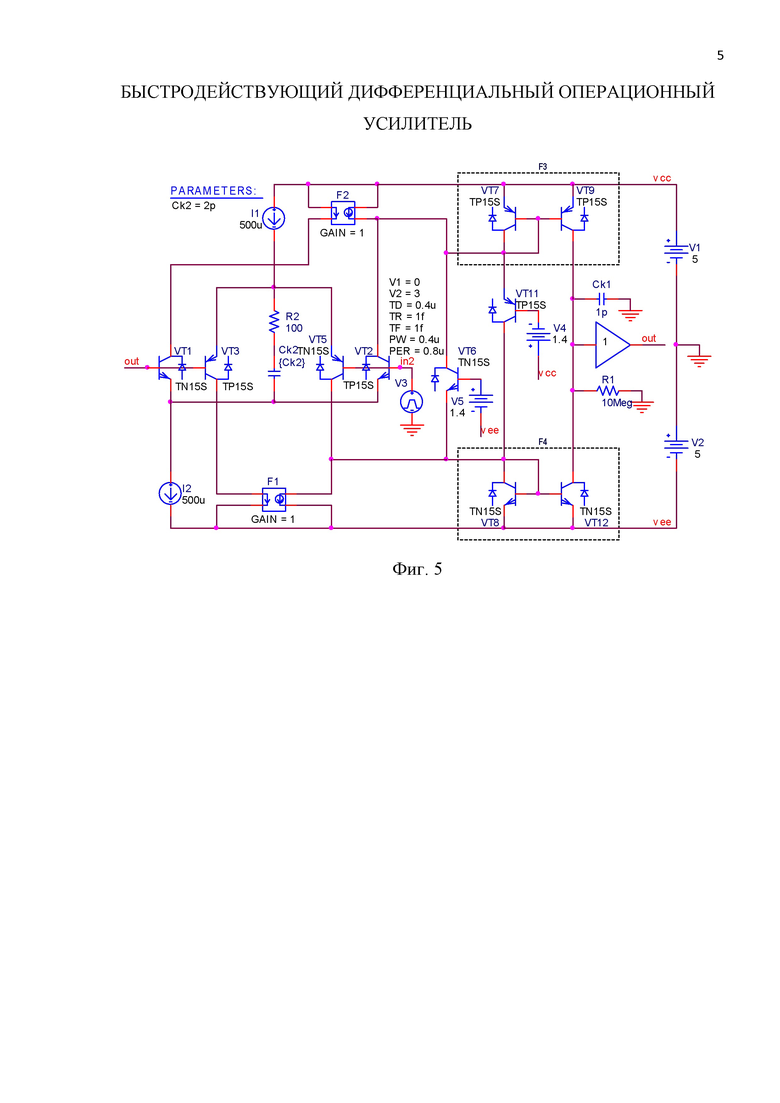

На чертеже фиг. 5 представлена схема ДОУ фиг. 3 в среде моделирования ORCAD (техпроцесс АО «НПП «Пульсар») на реальных токовых зеркалах F3 и F4 для импульсного входного напряжения с амплитудой 3 В и 100% отрицательной обратной связью.

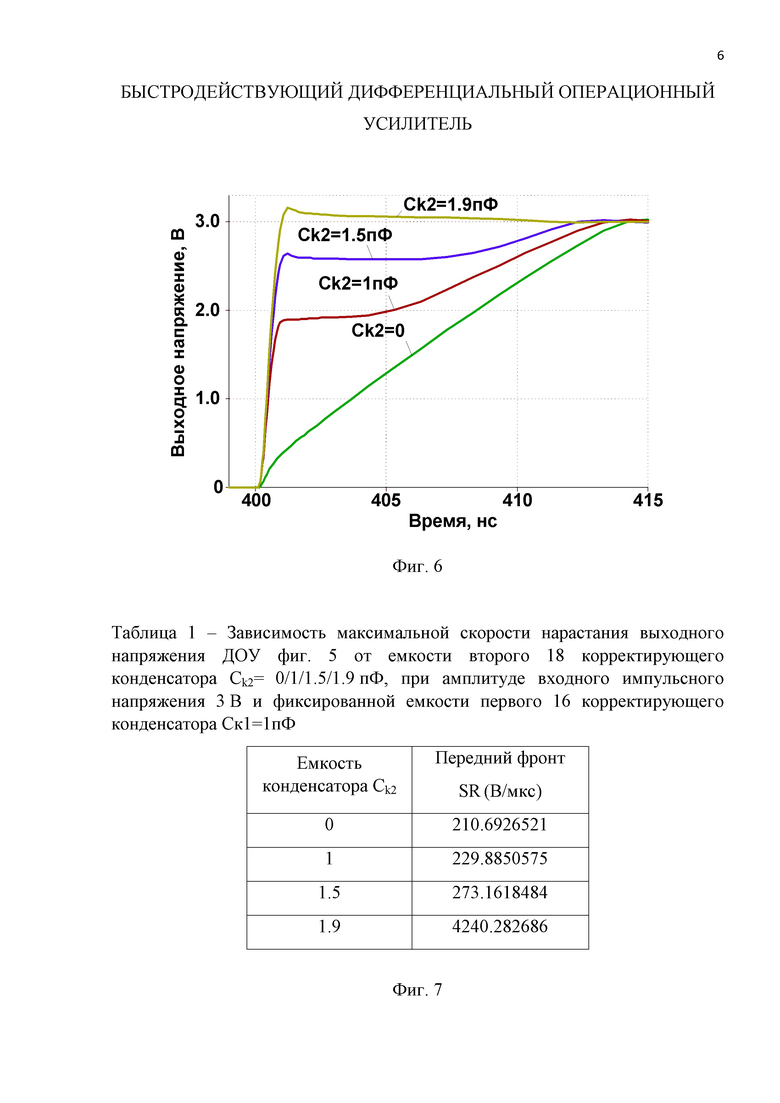

На чертеже фиг. 6 приведена осциллограмма переднего фронта выходного напряжения ДОУ фиг. 5 при емкости первого 16 корректирующего конденсатора Ск1=1пФ, различных емкостях второго 18 корректирующего конденсатора Сk2=0/1/1.5/1.9 пФ, амплитуде входного импульсного напряжения 3 В, температуре t=27°С.

На чертеже фиг. 7 представлена таблица 1, которая характеризует зависимость максимальной скорости нарастания выходного напряжения SR ДОУ фиг. 5 от емкости второго 18 корректирующего конденсатора Сk2= 0/1/1.5/1.9 пФ при амплитуде входного импульсного напряжения 3 В и фиксированной емкости первого 16 корректирующего конденсатора Ск1=1пФ.

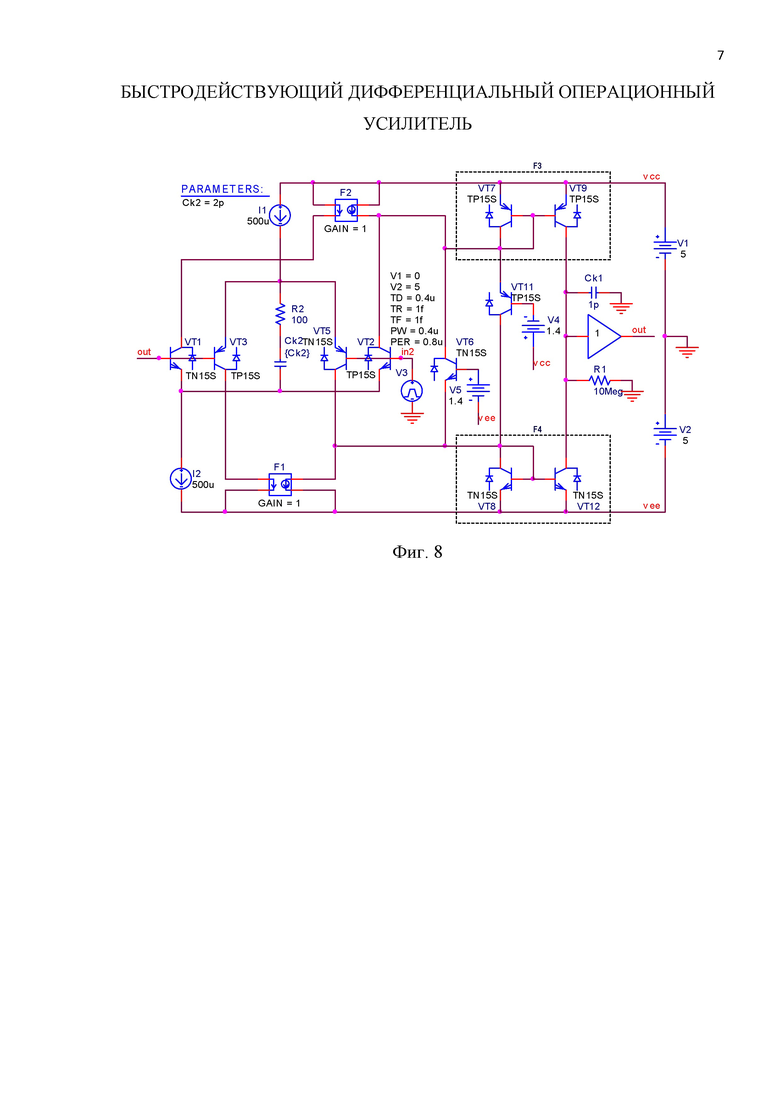

На чертеже фиг. 8 показана схема ДОУ фиг. 3 в среде моделирования ORCAD (техпроцесс АО «НПП «Пульсар») на реальных токовых зеркалах F3 и F4 для импульсного входного напряжения с более высокой амплитудой 5 В и 100% отрицательной обратной связью.

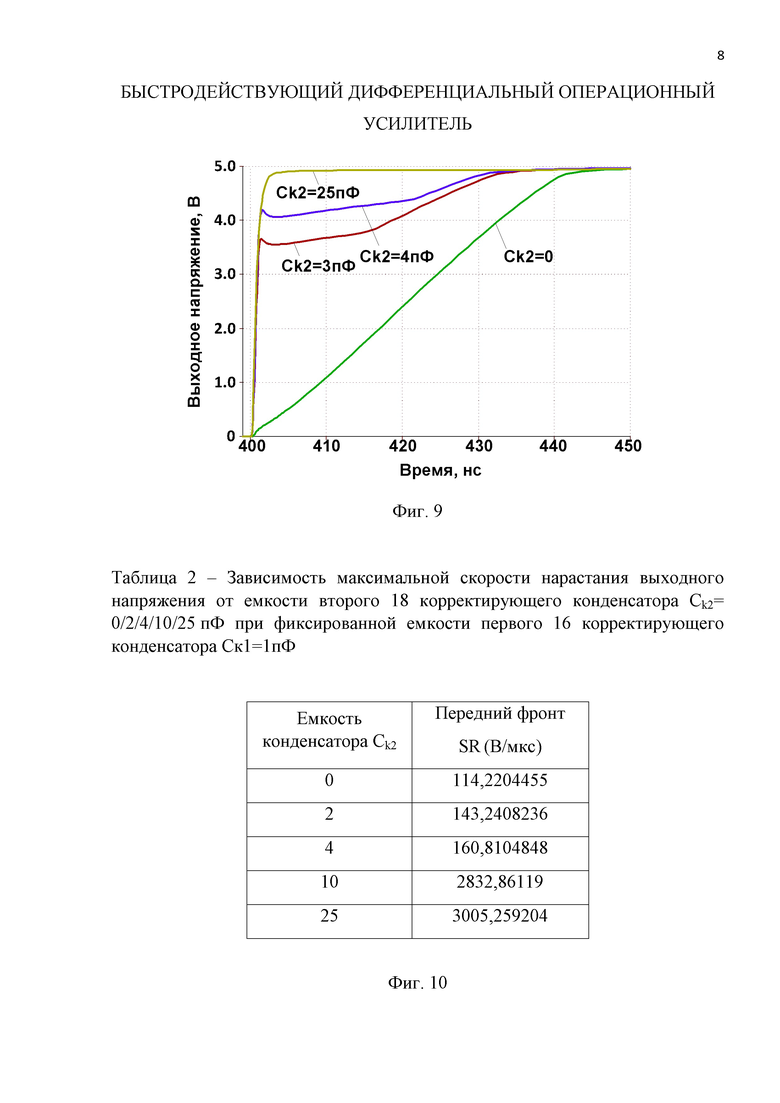

На чертеже фиг. 9 приведена осциллограмма переднего фронта выходного напряжения ДОУ фиг. 8 при фиксированной емкости первого 16 корректирующего конденсатора Ск1=1пФ и различных емкостях второго 18 корректирующего конденсатора Сk2=0/3/4/25 пФ при более высокой амплитуде входного импульсного напряжения 5 В, температуре t=27°С.

На чертеже фиг. 10 представлена таблица 2, которая характеризует зависимость максимальной скорости нарастания выходного напряжения ДОУ фиг. 8 от емкости второго 18 корректирующего конденсатора Сk2= 0/2/4/10/25 пФ при фиксированной емкости первого 16 корректирующего конденсатора Ск1=1пФ.

Быстродействующий дифференциальный операционный усилитель фиг. 2 содержит первый 1 и второй 2 дифференциальные входы устройства, токовый выход 3 устройства, первый 4 входной транзистор, база которого соединена с первым 1 дифференциальным входом устройства, а эмиттер соединен с эмиттером второго 5 входного транзистора и через первый 6 токостабилизирующий двухполюсник соединен с первой 7 шиной источника питания, третий 8 входной транзистор, база которого соединена с первым 1 входом устройства, а эмиттер соединен с четвертым 9 входным транзистором и через второй 10 токостабилизирующий двухполюсник соединен со второй 11 шиной источника питания, причем базы второго 5 и четвертого 9 входных транзисторов соединены со вторым 2 входом устройства, коллектор первого 4 входного транзистора соединен со входом первого 12 токового зеркала, согласованного со второй 11 шиной источника питания, коллектор второго 5 входного транзистора подключен к токовому выходу первого 12 токового зеркала и входу второго 13 токового зеркала, согласованного со второй 11 шиной источника питания, коллектор третьего 8 входного транзистора соединен со входом третьего 14 токового зеркала, согласованного с первой 7 шиной источника питания, коллектор четвертого 9 входного транзистора подключен к токовому выходу третьего 14 токового зеркала и входу четвертого 15 токового зеркала, согласованного с первой 7 шиной источника питания, токовые выходы второго 13 и четвертого 15 токовых зеркал соединены с токовым выходом 3 устройства и первым 16 корректирующим конденсатором. Между входами второго 13 и четвертого 15 токовых зеркал включена цепь согласования потенциалов 17, причем между объединенными эмиттерами первого 4 и второго 5 входных транзисторов и объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов включен второй 18 корректирующий конденсатор.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, цепь согласования потенциалов 17 содержит первый 19 и второй 20 дополнительные транзисторы разного типа проводимости, причем эмиттер первого 19 дополнительного транзистора соединен со входом второго 13 токового зеркала, коллектор – подключен ко входу четвертого 15 токового зеркала, а база соединена с первым 21 дополнительным источником напряжения смещения, коллектор второго 20 дополнительного транзистора соединен со входом второго 13 токового зеркала, эмиттер – подключен ко входу четвертого 15 токового зеркала, а база соединена со вторым 22 дополнительным источником напряжения смещения.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, цепь согласования потенциалов 17 содержит вспомогательный двухполюсник 23, включенный между входами второго 13 и четвертого 15 токовых зеркал, причем между входом второго 13 токового зеркала и третьим 24 источником напряжения смещения включен первый 25 дополнительный p-n переход, а между входом четвертого 15 токового зеркала и четвертым 26 источником напряжения смещения включен второй 27 дополнительный p-n переход.

Кроме этого, на чертежах фиг. 2, фиг. 3, фиг. 4, в соответствии с п. 4 формулы изобретения, токовый выход 3 устройства связан со входом дополнительного буферного усилителя 28, потенциальный выход которого 29 является низкоомным потенциальным выходом заявляемого устройства.

Рассмотрим работу предлагаемого ДОУ фиг. 3 в режиме большого сигнала со 100% отрицательной обратной связью с низкоомного потенциального выхода 29 ДОУ на инвертирующий вход 1. Такой режим соответствует типовой схеме измерения SR в неинвертирующем включении ДОУ (фиг. 5).

В статическом режиме эмиттерные токи первого 4, второго 5, третьего 8, четвертого 9 входных транзисторов определяются первым 6 и вторым 10 токостабилизирующими двухполюсниками. Первый 16 корректирующий конденсатор определяет частоту единичного усиления ДОУ фиг. 2 и запас устойчивости по фазе. Второй 18 корректирующий конденсатор в режиме малого сигнала не влияет на амплитудно-частотную характеристику ДОУ, т.к. включен в мостовую схему, образуемую первым 4, вторым 5 и третьим 8, четвертым 9 входными транзисторами.

Если на неинвертирующий вход 2 ДОУ фиг. 3 подать большой положительный импульсный сигнал uвх(+) , соизмеримый с напряжением на второй 11 шине источника питания, то это вызывает запирание четвертого 9 и первого 4 входных транзисторов и формирование большого импульса тока через второй 18 корректирующий конденсатор (ic2(+)). Этот ток (ic2(+)) передается в первый 16 корректирующий конденсатор по двум каналам. Во первых, он поступает в эмиттер и далее в коллектор второго 5 входного транзистора и далее на выход второго 13 токового зеркала. С другой стороны, ток ic2(+) передается в эмиттер второго 20 дополнительного транзистора и далее на вход второго 13 токового зеркала. То есть в рассматриваемой схеме ДОУ первый 16 корректирующий конденсатор перезаряжается удвоенным током ic2(+). В результате перезаряд первого 16 корректирующего конденсатора существенно ускоряется (фиг. 6), что в конечном итоге повышает быстродействие ОУ фиг. 2 (см. таблицу 1, фиг. 7).

При большом отрицательном входном импульсе напряжения uвх(-) на входе схема ДОУ фиг. 3 работает аналогично: запираются второй 5 и третий 8 входные транзисторы. Формирующийся при этом импульс тока ic2(-) передается с удвоенным значением в первый 16 корректирующий конденсатор. В конечном итоге, это существенно ускоряет перезаряд первого 16 корректирующего конденсатора (см. фиг. 6 и фиг. 7) и способствует повышению быстродействия ДОУ фиг. 3 (см. таблицу 2 фиг. 10) при отрицательном входном импульсе.

Статический режим выходного каскада с токовым выходом 3 (второе 13 и четвертое 15 токовые зеркала) устанавливается цепью согласования потенциалов 17 (первый 19 и второй 20 дополнительные транзисторы, первый 21 и второй 22 дополнительные источники напряжения смещения).

В схеме фиг. 4 при малых входных сигналах первый 25 и второй 27 дополнительные p-n переходы находятся в закрытом состоянии, что обеспечивается третьим 24 и четвертым 26 источниками напряжения смещения, а также схемотехникой входных цепей второго 13 и четвертого 15 токовых зеркал.

Таким образом, заявляемое устройство обладает существенными преимуществами по быстродействию в режиме большого сигнала в сравнении с ДОУ-прототипом. Моделирование показывает, что применение биполярно-полевого техпроцесса [1] обеспечивает его работоспособность в тяжелых условиях эксплуатации.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

1. Патент US 5.153.529, 1992 г.

2. Патент US 5.455.536, fig. 2, 1995 г.

3. Патент US 7.411.451, fig. 2, 2008 г.

4. Патент US 5.291.149, fig. 1, 1994 г.

5. Патент US 5.610.557, fig. 1, 1997 г.

6. Патент US 5.455.535 fig. 2, 1995 г.

7. Патент US 7.791.414, fig. 6, 2010 г.

8. Патент US 5.729.177, fig. 1, 1998 г.

9. Патент US 4.649.352, 1987 г.

10. Патент US 4.417.292, fig. 1, 1983 г.

11. Патент SU 1385255, 1988 г.

12. Патент US 5.610.547, fig. 28, fig. 34 1997 г.

13. Патент SU 459780, 1975 г.

14. Патент US 5.420.540, 1995 г.

15. Патент US 4.406.990, fig. 4, 1983 г.

16. Патент US 4.607.232, 1986 г.

17. Патент US 5.523.718, fig. 1, 1996 г.

18. Патент РФ № 2193273, 2002 г.

19. Патент US № 6.366.170, 2002 г.

20. Патент US № 4.837.523, 1989 г.

21. Патент US № 5.140.280, 1992 г.

22. Патент US № 4.600.893, fig. 3, 1986 г.

23. Патент US 6.628.168, fig.2, 2003 г.

24. Патентная заявка US 2006/0125522, fig. 3, 2006 г.

25. Патентная заявка US 2009/0302895, 2009 г.

26. Патент US 5.714.906, fig. 4, 1998 г.

27. Патент US 7.408.410, 2008 г.

28. Патент EP 0318263, 1989 г.

29. Патент US 2005/0285677, 2005 г.

30. Патент US 5.070.306, fig. 3, 1991 г.

31. Патент US 2010/001797, 2010 г.

32. Патент US 6.972.623, fig. 4, fig. 6, 2005 г.

33. Патент US 2008/0252374, 2008 г.

34. Патент US 7.586.373, 2009 г.

35. Патент US 2006/0215787, 2006 г.

36. Патент US 7.453.319, 2008 г.

37. Патент US 2004/0174216, fig. 2, 2004 г.

38. Патент US 7.215.200, fig. 6, 2007 г.

39. Патент US № 6.433.637 фиг. 2, 2002 г.

40. Патент US № 6.392.485, 2002 г.

41. Патент US 5.963.085, fig. 3, 1999 г.

42. Патент US 6.788.143, 2004 г.

43. Патент US 4.390.850, 1983 г.

44. Патент US 6.696.894, fig. 1, 2004 г.

45. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668983C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения | 2023 |

|

RU2810544C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2676014C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| Компенсационный стабилизатор напряжения | 2018 |

|

RU2683249C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в аналоговых интерфейсах и устройствах преобразования сигналов. Технический результат заключается в повышении максимальной скорости нарастания выходного напряжения ДОУ. Быстродействующий дифференциальный операционный усилитель содержит дифференциальные входы устройства, токовый выход устройства, входной транзистор, эмиттер, токостабилизирующий двухполюсник, источник питания, транзистор, токовые зеркала, корректирующий конденсатор. 3 з.п. ф-лы, 10 ил.

1. Быстродействующий дифференциальный операционный усилитель, содержащий первый (1) и второй (2) дифференциальные входы устройства, токовый выход (3) устройства, первый (4) входной транзистор, база которого соединена с первым (1) дифференциальным входом устройства, а эмиттер соединен с эмиттером второго (5) входного транзистора и через первый (6) токостабилизирующий двухполюсник соединен с первой (7) шиной источника питания, третий (8) входной транзистор, база которого соединена с первым (1) входом устройства, а эмиттер соединен с четвертым (9) входным транзистором и через второй (10) токостабилизирующий двухполюсник соединен со второй (11) шиной источника питания, причем базы второго (5) и четвертого (9) входных транзисторов соединены со вторым (2) входом устройства, коллектор первого (4) входного транзистора соединен со входом первого (12) токового зеркала, согласованного со второй (11) шиной источника питания, коллектор второго (5) входного транзистора подключен к токовому выходу первого (12) токового зеркала и входу второго (13) токового зеркала, согласованного со второй (11) шиной источника питания, коллектор третьего (8) входного транзистора соединен со входом третьего (14) токового зеркала, согласованного с первой (7) шиной источника питания, коллектор четвертого (9) входного транзистора подключен к токовому выходу третьего (14) токового зеркала и входу четвертого (15) токового зеркала, согласованного с первой (7) шиной источника питания, токовые выходы второго (13) и четвертого (15) токовых зеркал соединены с токовым выходом (3) устройства и первым (16) корректирующим конденсатором, отличающийся тем, что между входами второго (13) и четвертого (15) токовых зеркал включена цепь согласования потенциалов (17), причем между объединенными эмиттерами первого (4) и второго (5) входных транзисторов и объединенными эмиттерами третьего (8) и четвертого (9) входных транзисторов включен второй (18) корректирующий конденсатор.

2. Быстродействующий дифференциальный операционный усилитель по п. 1, отличающийся тем, что цепь согласования потенциалов (17) содержит первый (19) и второй (20) дополнительные транзисторы разного типа проводимости, причем эмиттер первого (19) дополнительного транзистора соединен со входом второго (13) токового зеркала, коллектор подключен ко входу четвертого (15) токового зеркала, а база соединена с первым (21) дополнительным источником напряжения смещения, коллектор второго (20) дополнительного транзистора соединен со входом второго (13) токового зеркала, эмиттер подключен ко входу четвертого (15) токового зеркала, а база соединена со вторым (22) дополнительным источником напряжения смещения.

3. Быстродействующий дифференциальный операционный усилитель по п. 1, отличающийся тем, что цепь согласования потенциалов (17) содержит вспомогательный двухполюсник (23), включенный между входами второго (13) и четвертого (15) токовых зеркал, причем между входом второго (13) токового зеркала и третьим (24) источником напряжения смещения включен первый (25) дополнительный p-n переход, а между входом четвертого (15) токового зеркала и четвертым (26) источником напряжения смещения включен второй (27) дополнительный p-n переход.

4. Быстродействующий дифференциальный операционный усилитель по п. 1, отличающийся тем, что токовый выход (3) устройства связан со входом дополнительного буферного усилителя (28), потенциальный выход которого (29) является низкоомным потенциальным выходом устройства.

| US 4636743, 13.01.1987 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2007 |

|

RU2364020C1 |

| ШИРОКОПОЛОСНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИАЛЬНЫМ ВЫХОДОМ | 2009 |

|

RU2393627C1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2019-05-21—Публикация

2018-07-23—Подача