Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве BiJFet (биполярно-полевых) буферных усилителей различных аналоговых устройств, допускающих работу в условиях воздействия проникающей радиации и низких температур.

Известно значительное количество схем буферных усилителей (БУ), которые реализуются на биполярных (BJT) и полевых (BiJFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-27]. Во многих случаях схема БУ адаптируется под конкретные технологические процессы и внешние воздействующие факторы, например, влияние низких температур и радиации, т.к. только в этом случае обеспечивается реализациях предельных параметров БУ.

В современной радиоэлектронной аппаратуре находят применение буферные усилители, реализованные в виде истоковых повторителей на BiJFet или КМОП транзисторах [1-27]. Известны также двухтактные выходные каскады только на КМОП транзисторах с p- или n-каналами

[22-25]. В ряде случаев двухтактные выходные каскады выполняются на входных КМОП транзисторах и выходных биполярных транзисторах [26]. Благодаря простоте вышеназванные схемотехнические решения наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе типовых технологических процессов.

Ближайшим прототипом заявляемого устройства является буферный усилитель, представленный в патенте США № 4.596.958. Он содержит вход 1 и выход 2 устройства, первый 3 повторитель напряжения, низкоомный выход которого соединен с выходом устройства 2, второй 4 повторитель напряжения, низкоомный выход которого соединен с выходом устройства 2, первый 5 и второй 6 полевые транзисторы, первый 7 токостабилизирующий двухполюсник, включенный между первой 8 шиной источника питания и истоком первого 5 полевого транзистора, источник опорного тока 9, причем коллекторная цепь первого 3 повторителя напряжения связана с первой 8 шиной источника питания, а стоковая цепь второго 4 повторителя напряжения связана со второй 10 шиной источника питания.

Существенный недостаток известного буферного усилителя состоит в том, что в рамках данной архитектуры его схема не может быть реализована только на комплементарных полевых транзисторах с управляющим p-n переходом, для которых подтверждены работоспособность [28] в условиях проникающей радиации и низких, в т.ч. криогенных, температур, а также низкий уровень шумов. Формальная замена n-p-n биполярных транзисторов в схеме БУ-прототипа фиг. 1 на полевые транзисторы с управляющим p-n переходом и n-каналом невозможна, т.к. в этом случае в известной схеме возникает неуправляемый сквозной ток первого 3 и второго 4 повторителей напряжения. Это не позволяет установить стабильный статический режим известного БУ. Таким образом, схема БУ-прототипа имеет ограниченное применение.

Основная задача предполагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного схемотехнического решения БУ, в т.ч. на комплементарных полевых транзисторах, обеспечивающего при высокой линейности амплитудной характеристики повышенную стабильность статического режима и низкий уровень шумов при работе в диапазоне низких температур.

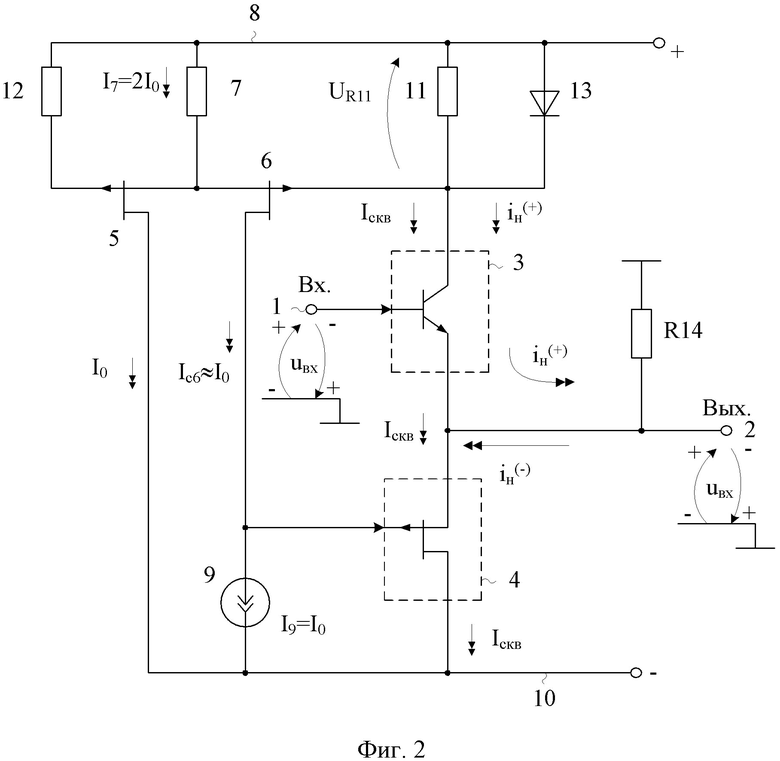

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, первый 3 повторитель напряжения, низкоомный выход которого соединен с выходом устройства 2, второй 4 повторитель напряжения, низкоомный выход которого соединен с выходом устройства 2, первый 5 и второй 6 полевые транзисторы, первый 7 токостабилизирующий двухполюсник, включенный между первой 8 шиной источника питания и истоком первого 5 полевого транзистора, источник опорного тока 9, причем коллекторная цепь первого 3 повторителя напряжения связана с первой 8 шиной источника питания, а стоковая цепь второго 4 повторителя напряжения связана со второй 10 шиной источника питания, предусмотрены новые элементы и связи – коллекторная цепь первого 3 повторителя напряжения связана с первой 8 шиной источника питания через первый 11 дополнительный резистор, затвор второго 6 полевого транзистора подключен к коллекторной цепи первого 3 повторителя напряжения, сток второго 6 полевого транзистора связан со второй 10 шиной источника питания через источник опорного тока 9 и соединен со входом второго 4 повторителя напряжения, истоки первого 5 и второго 6 полевых транзисторов объединены, причем затвор первого 5 полевого транзистора связан с первой 8 шиной источника питания.

На чертеже фиг. 1 представлена схема БУ-прототипа, а на чертеже фиг. 2 – схема заявляемого буферного усилителя в соответствии с п.1, п.2, п.3, п.4, а также п.6 формулы изобретения.

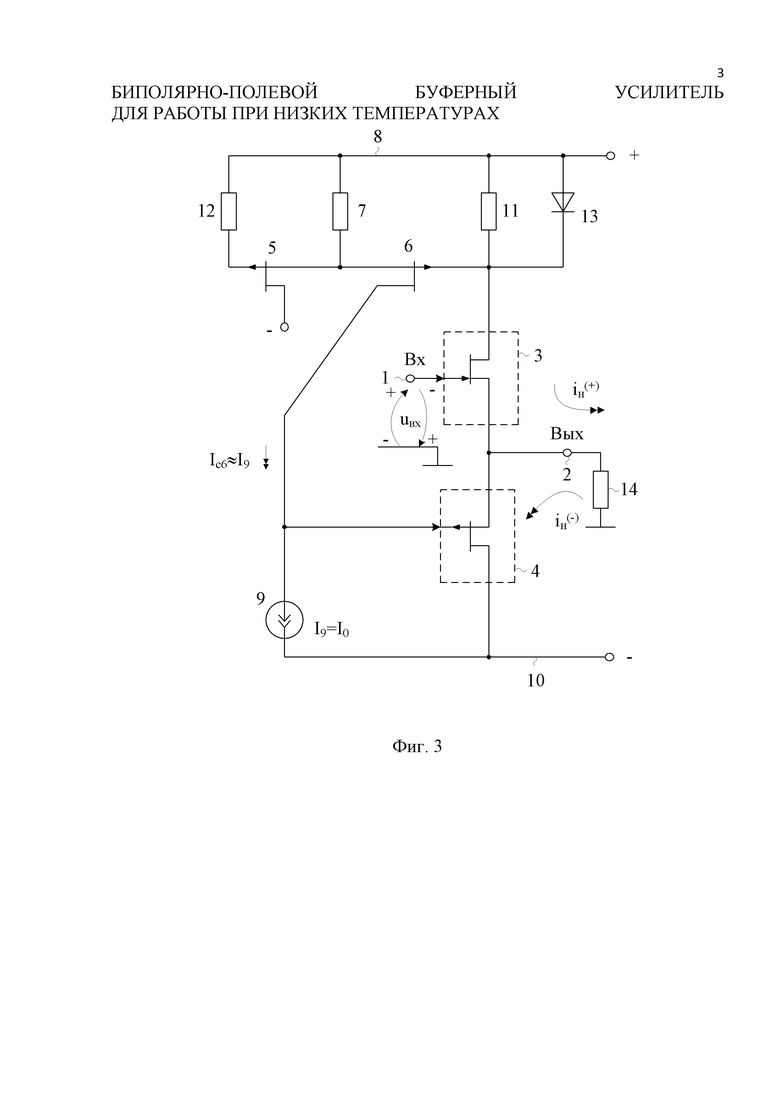

На чертеже фиг. 3 показана схема заявляемого буферного усилителя в соответствии с п.5 и п.6 формулы изобретения.

На чертеже фиг. 4 приведена схема заявляемого буферного усилителя по п. 7 формулы изобретения, соответствующая также п.2, п.3, п.4, п.6 формулы изобретения.

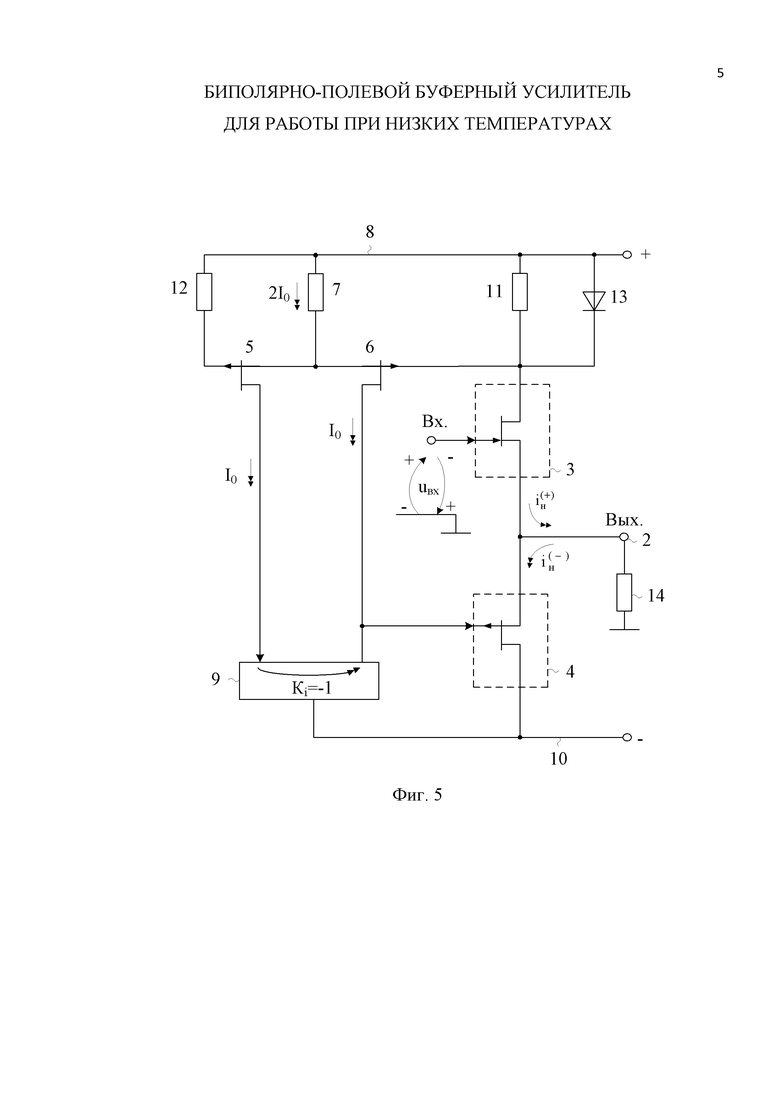

На чертеже фиг. 5 показана схема заявляемого буферного усилителя, соответствующая п.1, п.2, п.3, п.5, п.6 и п.7 формулы изобретения.

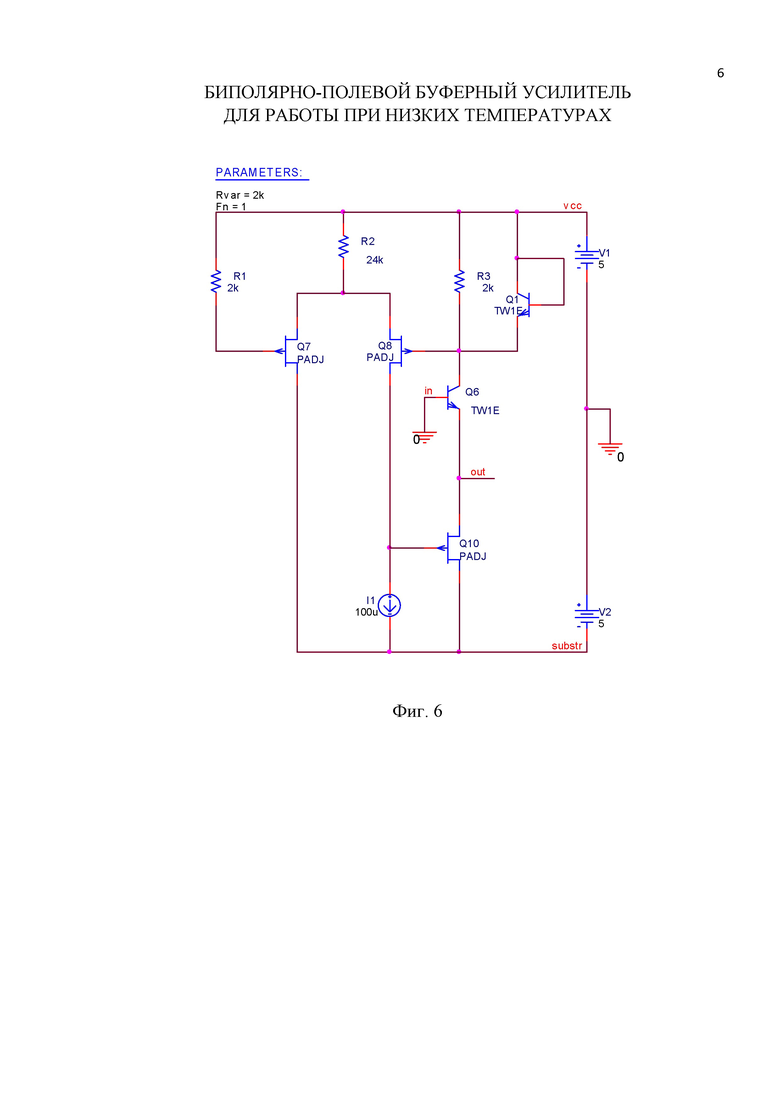

На чертеже фиг. 6 представлен BiJFet буферный усилитель фиг. 3 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов базового матричного кристалла АБМК_1.4 (ОАО «Интеграл», г.Минск).

На чертеже фиг. 7 приведена амплитудная характеристика БУ фиг. 6 при статическом токе I1=100 мкА и разных сопротивлениях Rн нагрузки 14 (0.5 кОм, 2 кОм, 10 кОм, 100 кОм).

На чертеже фиг. 8 показана амплитудная характеристика БУ фиг. 6 при статическом токе I1=10 мкА и разных сопротивлениях Rн нагрузки 14 (0.5 кОм, 2 кОм, 100 кОм).

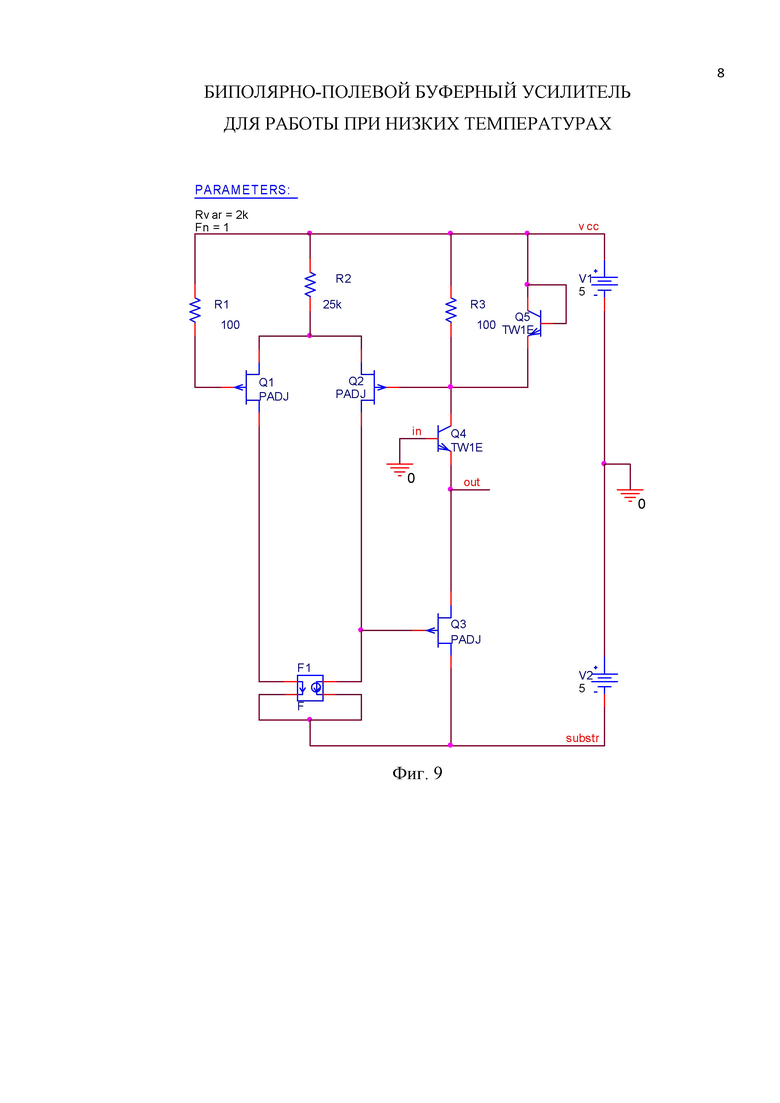

На чертеже фиг. 9 представлена схема схема BiJFet БУ фиг. 4 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов базового матричного кристалла АБМК_1.4 (ОАО «Интеграл», г.Минск).

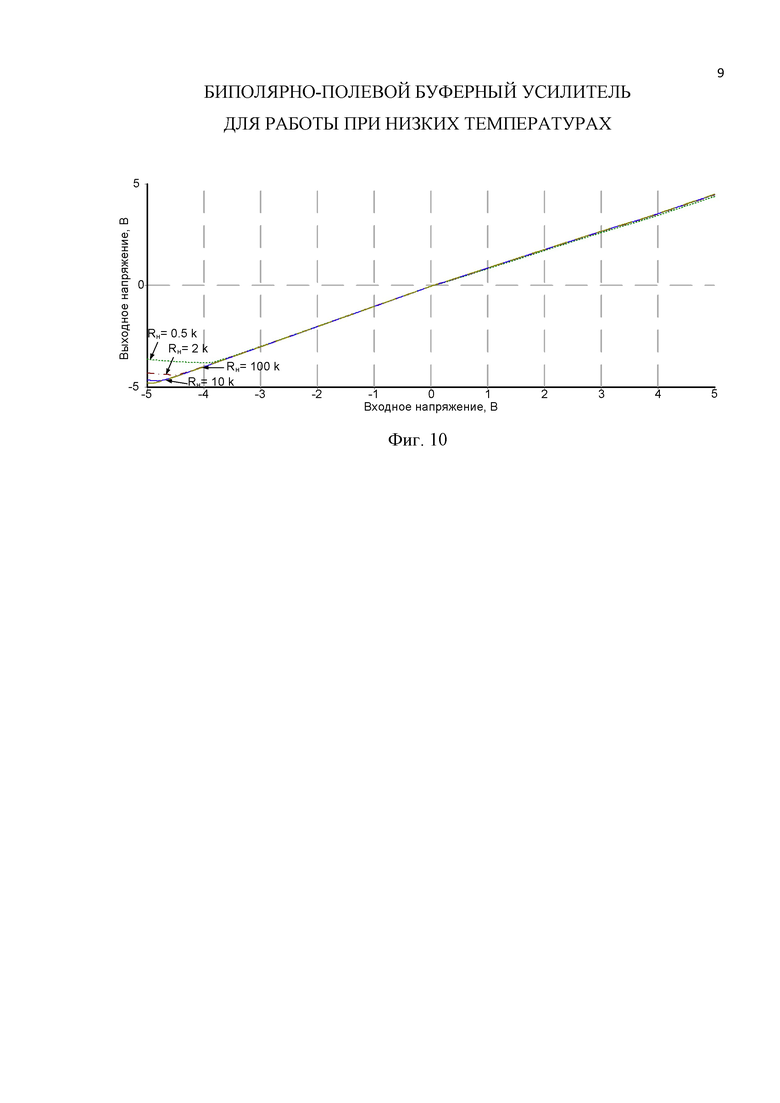

На чертеже фиг. 10 приведена амплитудная характеристика БУ фиг. 9 при коэффициенте передачи управляемого источника опорного тока 9 Кi=-1 и разных сопротивлениях нагрузки Rн (0.5 кОм, 2 кОм, 10 кОм, 100 кОм).

Биполярно-полевой буферный усилитель для работы при низких температурах фиг. 2 содержит вход 1 и выход 2 устройства, первый 3 повторитель напряжения, низкоомный выход которого соединен с выходом устройства 2, второй 4 повторитель напряжения, низкоомный выход которого соединен с выходом устройства 2, первый 5 и второй 6 полевые транзисторы, первый 7 токостабилизирующий двухполюсник, включенный между первой 8 шиной источника питания и истоком первого 5 полевого транзистора, источник опорного тока 9, причем коллекторная цепь первого 3 повторителя напряжения связана с первой 8 шиной источника питания, а стоковая цепь второго 4 повторителя напряжения связана со второй 10 шиной источника питания, отличающийся тем, что коллекторная цепь первого 3 повторителя напряжения связана с первой 8 шиной источника питания через первый 11 дополнительный резистор, затвор второго 6 полевого транзистора подключен к коллекторной цепи первого 3 повторителя напряжения, сток второго 6 полевого транзистора связан со второй 10 шиной источника питания через источник опорного тока 9 и соединен со входом второго 4 повторителя напряжения, истоки первого 5 и второго 6 полевых транзисторов объединены, причем затвор первого 5 полевого транзистора связан с первой 8 шиной источника питания.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, затвор первого 5 полевого транзистора связан с первой 8 шиной источника питания через второй 12 дополнительный резистор.

На чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, параллельно первому 11 дополнительному резистору включен дополнительный прямосмещённый p-n переход 13. В качестве нагрузки используется двухполюсник 14, подключенный к выходу 2 устройства.

На чертеже фиг. 2, в соответствии с п. 4 формулы изобретения, в качестве первого 3 повторителя напряжения используется эмиттерный повторитель напряжения на биполярном транзисторе, база которого соединена со входом 1 устройства, а эмиттер подключен к выходу 2 устройства.

Кроме этого, на чертеже фиг. 2 представлен частный вариант выполнения второго 4 повторителя напряжения - на полевом транзисторе с управляющим p-n переходом (п. 6 формулы изобретения).

Пример построения заявляемого буферного усилителя в соответствии с п. 5 и п. 6 формулы изобретения представлен на чертеже фиг.3.

На чертеже фиг. 4 приведена схема заявляемого буферного усилителя по п. 7 формулы изобретения, соответствующая также п.2, п.3, п.4, п.6 формулы изобретения.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, в качестве первого 3 повторителя напряжения используется истоковый повторитель напряжения на полевом транзисторе с управляющим p-n переходом, затвор которого соединен со входом 1 устройства, а исток подключен к выходу 2 устройства.

На чертеже фиг. 5, в соответствии с п. 6 формулы изобретения, в качестве второго 4 повторителя напряжения используется истоковый повторитель напряжения на полевом транзисторе с управляющим p-n переходом, затвор которого соединен со стоком второго 6 полевого транзистора, а исток подключен к выходу 2 устройства.

Кроме этого, на чертеже фиг. 5, в соответствии с п. 7 формулы изобретения, источник опорного тока 9 выполнен в виде управляемого источника опорного тока, управляющий вход которого связан со стоком первого 5 полевого транзистора.

Рассмотрим работу предлагаемого БУ фиг. 2.

В статическом режиме при R14=Rн=Rvar=∞, Uвх=0 в схеме фиг. 2 устанавливаются следующие токи

где Iu6=Ic6, Iu5=Ic5=I0 – токи истока и стока второго 6 и первого 5 полевого транзистора; I9 – ток источника опорного тока 9.

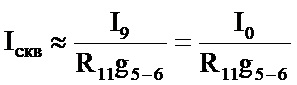

Сквозной статический ток первого 5 и второго 6 полевых транзисторов, протекающий между шинами питания БУ 8 и 10, определяется формулой

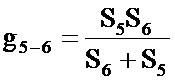

где

Таким образом, в предлагаемом БУ сквозной ток Iскв контролируется отрицательной обратной связью и может быть установлен на заданном уровне путем изменения тока источника опорного тока 9 или сопротивления первого 11 дополнительного резистора.

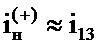

Если на вход БУ подается положительное входное напряжение

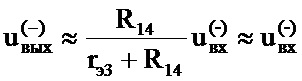

где rэ3 – дифференциальное сопротивление эмиттерного перехода биполярного транзистора в структуре первого 3 повторителя напряжения, R14 – сопротивление нагрузки 14.

Приращение тока

При отрицательном приращении

Второй 12 дополнительный резистор обеспечивает симметрирование статического режима первого 5 и второго 6 полевых транзисторов по цепи затвора. В ряде случаев данный резистор может отсутствовать.

При больших значениях тока нагрузки положительной полярности

Особенность схемы фиг.3 состоит в том, что она реализована только на полевых транзисторах с управляющим p-n переходом, что благоприятно сказывается на ее работе при низких температурах, а также при низком уровне шумов.

В схеме фиг. 4 источник опорного тока 9 реализован в виде управляемого источника опорного тока на основе классического токового зеркала 9 [21]. В конечном итоге, это позволяет получить высокую линейность амплитудной характеристики БУ (см. фиг. 10) без применения в схеме каких-либо источников опорного тока.

Схема фиг. 5, также как и схема фиг. 3, выполнена только на полевых транзисторах, что позволяет обеспечить ее работоспособность в диапазоне низких температур при малом уровне шумов [28].

Результаты компьютерного моделирования схемы фиг. 6, представленные на фиг. 7 и фиг. 8, показывают, что заявляемый БУ характеризуется достаточно высокой линейностью амплитудной характеристики при малом энергопотреблении в статическом режиме. Это является одной из замечательных особенностей предлагаемого БУ.

Аналогичными параметрами характеризуется и БУ фиг. 5 (фиг. 9), результаты компьютерного моделирования которого приведены на чертеже фиг. 10.

Таким образом, компьютерное моделирование (фиг. 7, фиг. 8, фиг. 10) показывает, что предлагаемый буферный усилитель, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [28], имеет существенные достоинства в сравнении с известными вариантами построения БУ при их реализации в рамках BiJFet технологического процесса.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 4.596.958 (прототип)

2. WO 2007135139

3. US 4743862

4. US 6433638, fig. 1a-2

5. US 20050253653

6. US 4825174, fig. 3, fig. 6

7. RU 2099856, fig. 3

8. US 4904953, fig. 2

9. US 7896339, fig. 4

10. US 6342814

11. US 2010/0182086

12. US 5387880, fig. 1

13. US 4598253

14. US 4667165, fig. 2

15. US 4596958

16. US 7116172, fig. 4, fig. 5

17. US 5648743

18. US 5367271, fig. 2

19. US 2000/0112075, fig. 3

20. US 5065043, fig. 1f

21. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ.— Изд. 2-е. — М.: Издательство БИНОМ. 2014. - 704 с. Рис. 3.26, рис. 3.28, рис. 3.29

22. US 2007/0115056, fig. 2

23. US 7548117, fig. 5

24. EP 0 293486 B1, fig. 5

25. Patt Boonyaporn, Varakorn Kasemsuwan. A High Performance Class AB CMOS Rail to Rail Voltage Follower // ASIC, 2002. Proceedings. 2002 IEEE Asia-Pacific Conference on, pp. 161-163

26. US 4420726, fig. 1 – fig. 3

27. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

28. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2677401C1 |

| ВЫХОДНОЙ КАСКАД BIJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668981C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ n-КАНАЛЬНЫХ ПОЛЕВЫХ И p-n-p БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2784376C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| ИСТОКОВЫЙ ПОВТОРИТЕЛЬ СИГНАЛА С МАЛЫМ УРОВНЕМ СИСТЕМАТИЧЕСКОЙ СОСТАВЛЯЮЩЕЙ НАПРЯЖЕНИЯ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784373C1 |

Изобретение относится к области аналоговой микроэлектроники. Технический результат заключается в повышении стабильности статического режима и низком уровне шумов при работе устройства в диапазоне низких температур с высокой линейностью амплитудной характеристики. Биполярно-полевой буферный усилитель содержит вход (1) и выход (2) устройства, первый (3) повторитель напряжения, низкоомный выход которого соединен с выходом устройства (2), второй (4) повторитель напряжения, низкоомный выход которого соединен с выходом устройства (2), первый (5) и второй (6) полевые транзисторы, первый (7) токостабилизирующий двухполюсник, включенный между первой (8) шиной источника питания и истоком первого (5) полевого транзистора, источник опорного тока (9), причем коллекторная цепь первого (3) повторителя напряжения связана с первой (8) шиной источника питания, а стоковая цепь второго (4) повторителя напряжения связана со второй (10) шиной источника питания. 6 з.п. ф-лы, 10 ил.

1. Биполярно-полевой буферный усилитель для работы при низких температурах, содержащий вход (1) и выход (2) устройства, первый (3) повторитель напряжения, низкоомный выход которого соединен с выходом устройства (2), второй (4) повторитель напряжения, низкоомный выход которого соединен с выходом устройства (2), первый (5) и второй (6) полевые транзисторы, первый (7) токостабилизирующий двухполюсник, включенный между первой (8) шиной источника питания и истоком первого (5) полевого транзистора, источник опорного тока (9), причем коллекторная цепь первого (3) повторителя напряжения связана с первой (8) шиной источника питания, а стоковая цепь второго (4) повторителя напряжения связана со второй (10) шиной источника питания, отличающийся тем, что коллекторная цепь первого (3) повторителя напряжения связана с первой (8) шиной источника питания через первый (11) дополнительный резистор, затвор второго (6) полевого транзистора подключен к коллекторной цепи первого (3) повторителя напряжения, сток второго (6) полевого транзистора связан со второй (10) шиной источника питания через источник опорного тока (9) и соединен со входом второго (4) повторителя напряжения, истоки первого (5) и второго (6) полевых транзисторов объединены, причем затвор первого (5) полевого транзистора связан с первой (8) шиной источника питания.

2. Биполярно-полевой буферный усилитель для работы при низких температурах по п.1, отличающийся тем, что затвор первого (5) полевого транзистора связан с первой (8) шиной источника питания через второй (12) дополнительный резистор.

3. Биполярно-полевой буферный усилитель для работы при низких температурах по п.1, отличающийся тем, что параллельно первому (11) дополнительному резистору включен дополнительный прямосмещённый p-n переход (13).

4. Биполярно-полевой буферный усилитель для работы при низких температурах по п.1, отличающийся тем, что в качестве первого (3) повторителя напряжения используется эмиттерный повторитель напряжения на биполярном транзисторе, база которого соединена со входом (1) устройства, а эмиттер подключен к выходу (2) устройства.

5. Биполярно-полевой буферный усилитель для работы при низких температурах по п.1, отличающийся тем, что в качестве первого (3) повторителя напряжения используется истоковый повторитель напряжения на полевом транзисторе с управляющим p-n переходом, затвор которого соединен со входом (1) устройства, а исток подключен к выходу (2) устройства.

6. Биполярно-полевой буферный усилитель для работы при низких температурах по п.1, отличающийся тем, что в качестве второго (4) повторителя напряжения используется истоковый повторитель напряжения на полевом транзисторе с управляющим p-n переходом, затвор которого соединен со стоком второго (6) полевого транзистора, а исток подключен к выходу (2) устройства.

7. Биполярно-полевой буферный усилитель для работы при низких температурах по п.1, отличающийся тем, что источник опорного тока (9) выполнен в виде управляемого источника опорного тока, управляющий вход которого связан со стоком первого (5) полевого транзистора.

| US 4596958, 24.06.1986 | |||

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2595927C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2479108C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2467471C1 |

Авторы

Даты

2018-10-25—Публикация

2018-03-12—Подача