Изобретение относится к области аналоговой микроэлектроники и может быть использовано для усиления сигнала по мощности с коэффициентом передачи по напряжению, близким к единице, например, в активных RC-фильтрах класса Sallen-Key.

Известно значительное количество схем микроэлектронных повторителей сигнала (ПС), которые реализуются на комплементарных биполярных (BJT) или полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-28]. Следует отметить, что ПС с малым напряжением смещения нуля является базовым функциональным узлом антиалайзинговых фильтров низких частот со структурами Sallen-Key [29,30], включаемых на входе АЦП в устройствах радиотехники, связи и автоматики. В аналоговой схемотехнике находят также применение повторители сигнала, которые содержат в своей структуре токовые зеркала [31-38].

В настоящее время одним из векторов развития электронной компонентной базы нового поколения является применение аналоговых устройств, реализуемых на арсенид-галлиевых, нитрид-галлиевых и карбид-кремниевых транзисторах. Существуют совмещенные технологические процессы [39-42], позволяющие создавать на одном кристалле полевые и биполярные транзисторы на широкозонных полупроводниках. Однако, данные технологии требуют специальной схемотехники, которая должна учитывать набор разрешенных активных и пассивных компонентов. Заявляемое устройство ориентировано на применение таких техпроцессов.

Ближайшим прототипом заявляемого устройства является усилитель сигнала (фиг. 1), представленный в статье Itakura K. et al. A GaAs Bi-FET technology for large scale integration //International Technical Digest on Electron Devices Meeting. – IEEE, 1989. – С. 389-392. (фиг. 7). Схема прототипа фиг. 1 содержит вход 1 и выход 2 устройства, входной полевой транзистор с p-каналом 3, затвор которого соединен со входом 1 устройства, выходной n-p-n биполярный транзистор 4, коллектор которого связан с первой 5 шиной источника питания, а эмиттер подключен к выходу 2 устройства, источник опорного тока 6, включенный между выходом устройства 2 и второй 7 шиной источника питания.

Основная задача предполагаемого изобретения состоит в создании повторителя сигнала, обеспечивающего малые значения систематической составляющей напряжения смещения нуля (Uсм), что актуально для построения антиалайзинговых фильтров низких частот, включаемых на входе аналого-цифровых преобразователей [43].

Поставленная задача достигается тем, что в повторителе сигнала фиг. 1, содержащем вход 1 и выход 2 устройства, входной полевой транзистор с p-каналом 3, затвор которого соединен со входом 1 устройства, выходной n-p-n биполярный транзистор 4, коллектор которого связан с первой 5 шиной источника питания, а эмиттер подключен к выходу 2 устройства, источник опорного тока 6, включенный между выходом устройства 2 и второй 7 шиной источника питания, предусмотрены новые элементы и связи - сток входного полевого транзистора с p-каналом 3 соединен с первой 5 шиной источника питания, исток соединен с базой выходного n-p-n биполярного транзистора 4 и через прямосмещенный p-n переход на биполярном n-p-n транзисторе 8 связан с выходом устройства 2, при этом источник опорного тока 6 содержит первый 9 и второй 10 вспомогательные полевые транзисторы с p-каналом, затворы которых соединены со второй 7 шиной источника питания, стоки соединены с выходом устройства 2, а истоки объединены и подключены ко второй 7 шине источника питания через два параллельно включенных прямосмещенных p-n перехода на первом 11 и втором 12 вспомогательных n-p-n биполярных транзисторах, коллекторы которых соединены с базами.

На чертеже фиг. 1 показан усилитель сигнала – прототип, представленный в статье Itakura K. et al. A GaAs Bi-FET technology for large scale integration //International Technical Digest on Electron Devices Meeting. – IEEE, 1989. – С. 389-392. (фиг. 7).

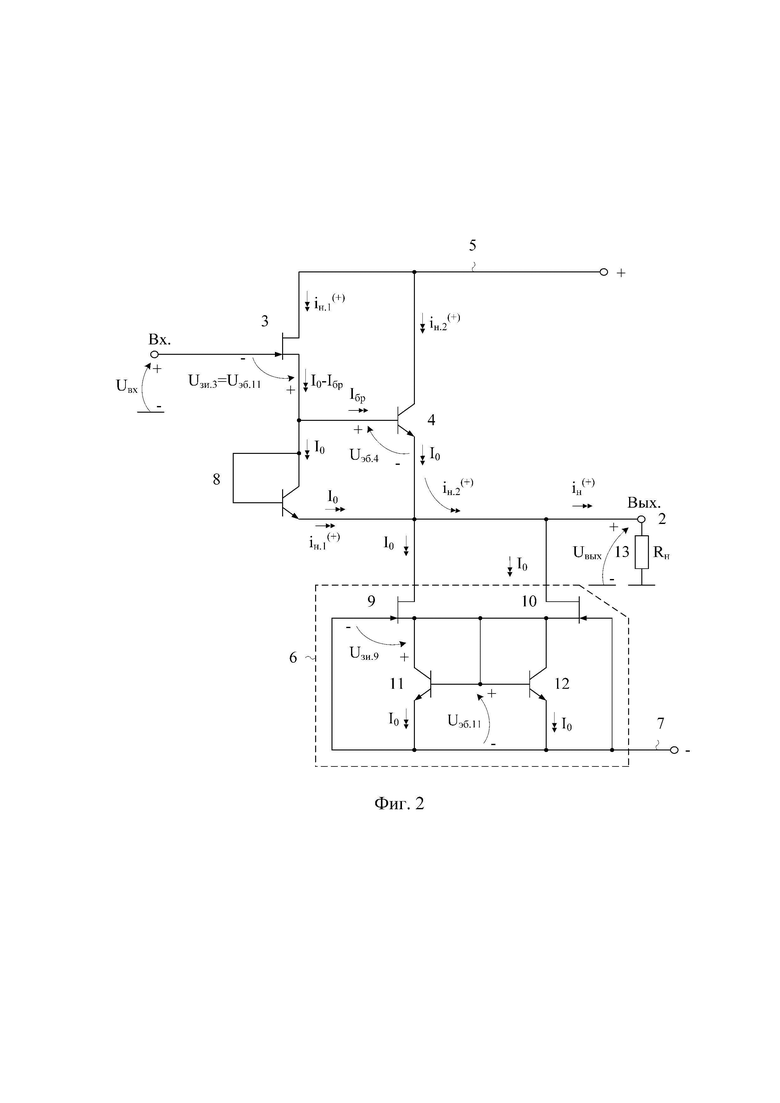

На чертеже фиг. 2 приведена схема заявляемого повторителя сигнала в соответствии с п. 1 формулы изобретения.

На чертеже фиг. 3 представлен CJFET и CBiJT повторитель сигнала в соответствии с п. 2 формулы изобретения.

На чертеже фиг. 4 показана схема для моделирования повторителя сигнала фиг. 2 в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload=1 МОм на моделях кремниевых транзисторов аналоговых базовых матричных кристаллов АО «Интеграл» (г. Минск) [44,45,46].

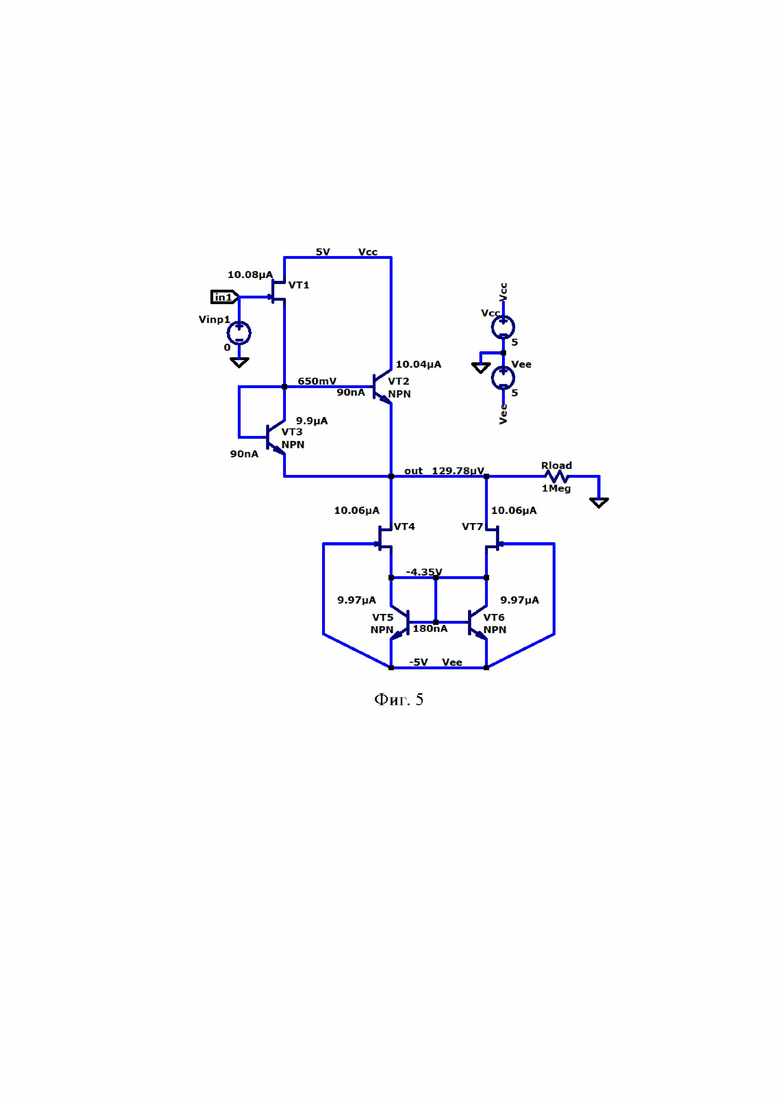

На чертеже фиг. 5 приведена схема для моделирования повторителя сигнала фиг. 2 в среде LTspice при t=-197oC, +Vcc=-Vee=5 В, Rload=1 МОм.

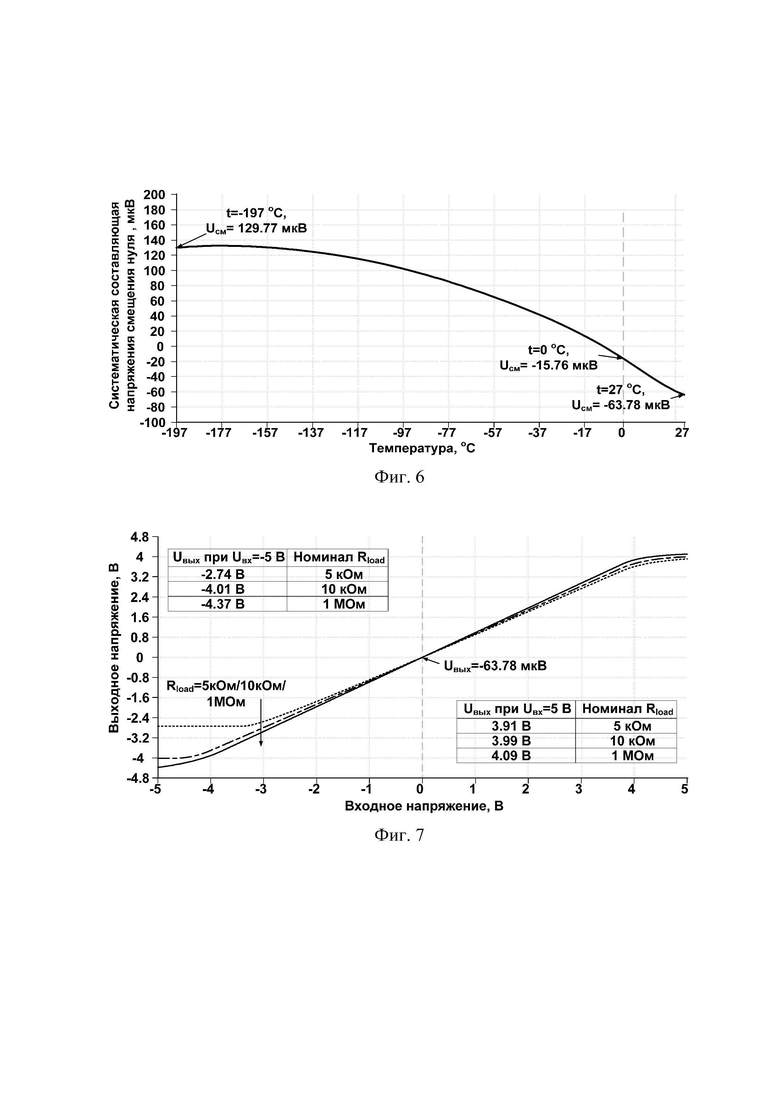

На чертеже фиг. 6 представлена зависимость систематической составляющей напряжения смещения нуля повторителя сигнала фиг. 2 от температуры при +Vcc=-Vee=5 В, Rload=1 Мом.

На чертеже фиг. 7 показана амплитудная характеристика повторителя сигнала фиг. 4 в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload= 5кОм/ 10кОм/1 МОм.

Истоковый повторитель сигнала с малым уровнем систематической составляющей напряжения смещения нуля фиг. 2 содержит вход 1 и выход 2 устройства, входной полевой транзистор с p-каналом 3, затвор которого соединен со входом 1 устройства, выходной n-p-n биполярный транзистор 4, коллектор которого связан с первой 5 шиной источника питания, а эмиттер подключен к выходу 2 устройства, источник опорного тока 6, включенный между выходом устройства 2 и второй 7 шиной источника питания. Сток входного полевого транзистора с p-каналом 3 соединен с первой 5 шиной источника питания, исток соединен с базой выходного n-p-n биполярного транзистора 4 и через прямосмещенный p-n переход на биполярном n-p-n транзисторе 8 связан с выходом устройства 2, при этом источник опорного тока 6 содержит первый 9 и второй 10 вспомогательные полевые транзисторы с p-каналом, затворы которых соединены со второй 7 шиной источника питания, стоки соединены с выходом устройства 2, а истоки объединены и подключены ко второй 7 шине источника питания через два параллельно включенных прямосмещенных p-n перехода на первом 11 и втором 12 вспомогательных n-p-n биполярных транзисторах, коллекторы которых соединены с базами.

На чертеже фиг. 2 в качестве элемента нагрузки Rн используется двухполюсник 13.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, в схему введен первый 14 дополнительный полевой транзистор с n-каналом, затвор которого подключен ко входу 1 устройства, сток соединен со второй 7 шиной источника питания, а исток соединен с базой первого 15 дополнительного p-n-p биполярного транзистора и через первый 16 дополнительный прямосмещенный p-n переход соединен с выходом устройства 2 и эмиттером первого 15 дополнительного p-n-p биполярного транзистора, коллектор которого связан со второй 7 шиной источника питания, причем эмиттер первого 15 дополнительного p-n-p биполярного транзистора соединен со стоками второго 17 и третьего 18 дополнительных полевых транзисторов с n-каналом, затворы которых подключены к первой 5 шине источника питания, а истоки объединены и связаны с первой 5 шиной источника питания через два параллельно включенных p-n перехода 19 и 20, выполненных на p-n-p биполярных транзисторах, коллекторы которых соединены с базами.

Рассмотрим работу предлагаемого повторителя сигнала фиг. 2.

Особенность повторителя сигнала на чертеже фиг. 2 состоит в том, что здесь статический режим транзисторов схемы по току определяется первым 9 и вторым 10 вспомогательными полевыми транзисторами с p-каналом и p-n переходами на первом 11 и втором 12 вспомогательных n-p-n биполярных транзисторах. Это позволяет за счет изменения ширины канала JFET выбирать заданные значения токов входного полевого транзистора с p-каналом 3 и выходного n-p-n биполярного транзистора 4:

где Uзи.i – напряжение затвор-исток i-го полевого транзистора при токе истока, равном IR.

Введение новых элементов и связей между ними в соответствии с формулой изобретения позволяет получить малые значения напряжения смещения нуля ПС (фиг. 4, фиг. 5) в широком диапазоне температур (фиг. 6).

Заявляемый повторитель сигнала допускает параметрическую оптимизацию параметров, например, по критерию минимизации систематической составляющей напряжения смещения нуля за счет рационального выбора ширины и длины канала входного полевого транзистора с p-каналом 3.

Учитывая, что выходное статическое напряжение предлагаемого ПС измеряется десятками-сотнями микровольт, в соответствии с п. 2 формулы изобретения возможно параллельное (по входу и выходу) включение двух идентичных по схемотехнике, но отличающихся типами каналов входных полевых транзисторов в соответствии с фиг. 3. Это позволяет получить двухтактные повторители напряжения, обеспечивающие токи положительного и отрицательного направлений в более низкоомных нагрузках.

Таким образом, компьютерное моделирование в среде LTspice и оптимизация заявляемой схемы повторителя сигнала показывает, что предлагаемый ПС, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [44,45], имеет существенные достоинства в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, 1999 г.

4. Патент US 5.197.124, fig. 25, 1993 г.

5. Патент US 7.764.123, fig. 3, 2010 г.

6. Патент US № 6.268.769 fig.3, 2001 г.

7. Патент US № 6.420.933, 2002 г.

8. Патент US № 5.223.122, 1993 г.

9. Патентная заявка US № 2004/0196101, 2004 г.

10. Патентная заявка US № 2005/0264358 fig.1, 2005 г.

11. Патентная заявка US № 2002/0175759, 2002 г.

12. Патент US № 5.049.653 fig.8, 1991 г.

13. Патент US № 4.837.523, 1989 г.

14. Патент US № 5.179.355, 1993 г.

15. Патент Японии JP 10.163.763, 1991 г.

16. Патент Японии JP 10.270.954, 1992 г.

17. Патент US № 5.170.134 fig.6, 1992 г.

18. Патент US № 4.540.950, 1985 г.

19. Патент US № 4.424.493, 1984 г.

20. Патент Японии JP 6310950, 2018 г.

21. Патент US № 5.378.938, 1995 г.

22. Патент US № 4.827.223, 1989 г.

23. Патент US № 6.160.451, 2000 г.

24. Патент US № 4.639.685, 1987 г.

25. А.св. СССР 1506512, 1986 г.

26. Патент US № 5.399.991, 1995 г.

27. Патент US № 6.542.032, 2003 г.

28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

29. Butyrlagin, Nikolay; Denisenko, Darya; Prokopenko, Nikolay; Inanov, Yuri (2022): Bank of new schemes of active RC-filters of the Sallen-Key subclass with independent tuning of the main parameters. TechRxiv. Preprint. https://doi.org/10.36227/techrxiv.19614813.v1

30. Prokopenko, N.; Budyakov, P.; Bugakova, A. Research and Comparative Modeling of the Si, GaAs and GaN JFET/CMOS Buffer Amplifiers for Sallen-Key LPF Design Problems with A Low Offset Voltage's Systematic Component . Preprints 2022, 2022050026 (doi: 10.20944/preprints202205.0026.v1).https://www.preprints.org/manuscript/202205.0026/v1

31. Itakura K. et al. A GaAs Bi-FET technology for large scale integration //International Technical Digest on Electron Devices Meeting. – IEEE, 1989. – С. 389-392. (фиг. 7)

32. Патент RU 2479109, 2013 г. (токовое зеркало на транзисторе 15 в эмиттерной цепи транзистора 2)

33. Патент RU 2536672, фиг.3 (токовое зеркало 8 в эмиттерной цепи транзистора 2), 2014 г.

34. Патент GB 2029662, fig. 1, 1979 г. (токовое зеркало (элементы 14, 12) в эмиттерной цепи транзистора 10)

35. Патент US 4236119 (токовое зеркало на элементах 14 и 12 в эмиттерной цепи транзистора 10)

36. Патентная заявка US 2001/0017571, fig.2, fig. 3 (токовое зеркало на транзисторах 214, 208)

37. Патент US 3673508, 1972 г., fig. 1 (токовое зеркало на транзисторе 22 в эмиттерной цепи транзистора 12)

38. Патент ФРГ 2055939, 1971 г., fig. 5 (токовое зеркало на транзисторе Q3 в эмиттерной цепи транзистора Q1)

39. M. Fresina, "Trends in GaAs HBTs for wireless and RF," 2011 IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Atlanta, GA, USA, 2011, pp. 150-153. doi: 10.1109/BCTM.2011.6082769

40. P. J. Zampardi, M. Sun, C. Cismaru and J. Li, "Prospects for a BiCFET III-V HBT Process," 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 2012, pp. 1-3. doi: 10.1109/CSICS.2012.6340116

41. W. Liu, D. Hill, D. Costa and J. S. Harris, "High-performance microwave AlGaAs-InGaAs Pnp HBT with high-DC current gain," in IEEE Microwave and Guided Wave Letters, vol. 2, no. 8, pp. 331-333, Aug. 1992. doi: 10.1109/75.153604

42. Peatman W. et al. InGaP-Plus™: advanced GaAs BiFET technology and applications // CS MANTECH Conference, May 14-17, 2007, Austin, Texas, USA. pp. 243-246.

43. Динамические погрешности процесса ввода аналоговых сигналов датчиков в системах управления и контроля: моногр. / Л. К. Самойлов, Д. Ю. Денисенко, Н. Н. Прокопенко. – М.: СОЛОН-Пресс, 2021. – 240 с.

44. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

45. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

46. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. – М.: СОЛОН-Пресс, 2021. – 200 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ С МАЛЫМ УРОВНЕМ СИСТЕМАТИЧЕСКОЙ СОСТАВЛЯЮЩЕЙ НАПРЯЖЕНИЯ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784045C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| АНТИАЛАЙЗИНГОВЫЙ ФИЛЬТР НИЗКИХ ЧАСТОТ СЕМЕЙСТВА SALLEN-KEY С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ ДЛЯ РАБОТЫ С БЫСТРОДЕЙСТВУЮЩИМИ АНАЛОГО-ЦИФРОВЫМИ ПРЕОБРАЗОВАТЕЛЯМИ | 2022 |

|

RU2782454C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2766868C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ | 2021 |

|

RU2767976C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2670777C9 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ n-КАНАЛЬНЫХ ПОЛЕВЫХ И p-n-p БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2784376C1 |

| НЕИНВЕРТИРУЮЩИЙ ВЫХОДНОЙ КАСКАД АРСЕНИД-ГАЛЛИЕВОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2784049C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

Изобретение относится к области аналоговой микроэлектроники. Технический результат: создание повторителя сигнала, обеспечивающего малые значения систематической составляющей напряжения смещения нуля. Для этого предложен истоковый повторитель сигнала, который содержит вход (1) и выход (2) устройства, входной полевой транзистор с p-каналом (3), выходной n-p-n биполярный транзистор (4), первую (5) шину источника питания, источник опорного тока (6), вторую (7) шину источника питания. Сток входного полевого транзистора с p-каналом (3) соединен с первой (5) шиной источника питания, исток соединен с базой выходного n-p-n биполярного транзистора (4) и через прямосмещенный p-n-переход на биполярном n-p-n-транзисторе (8) связан с выходом устройства (2), при этом источник опорного тока (6) содержит первый (9) и второй (10) вспомогательные полевые транзисторы с p-каналом, затворы которых соединены со второй (7) шиной, стоки соединены с выходом (2), а истоки объединены и подключены ко второй (7) шине через два параллельно включенных прямосмещенных p-n-перехода на первом (11) и втором (12) вспомогательных транзисторах. 1 з.п. ф-лы, 7 ил.

1. Истоковый повторитель сигнала с малым уровнем систематической составляющей напряжения смещения нуля, содержащий вход (1) и выход (2) устройства, входной полевой транзистор с p-каналом (3), затвор которого соединен со входом (1) устройства, выходной n-p-n биполярный транзистор (4), коллектор которого связан с первой (5) шиной источника питания, а эмиттер подключен к выходу (2) устройства, источник опорного тока (6), включенный между выходом устройства (2) и второй (7) шиной источника питания, отличающийся тем, что сток входного полевого транзистора с p-каналом (3) соединен с первой (5) шиной источника питания, исток соединен с базой выходного n-p-n биполярного транзистора (4) и через прямосмещенный p-n-переход на биполярном n-p-n-транзисторе (8) связан с выходом устройства (2), при этом источник опорного тока (6) содержит первый (9) и второй (10) вспомогательные полевые транзисторы с p-каналом, затворы которых соединены со второй (7) шиной источника питания, стоки соединены с выходом устройства (2), а истоки объединены и подключены ко второй (7) шине источника питания через два параллельно включенных прямосмещенных p-n-перехода на первом (11) и втором (12) вспомогательных n-p-n биполярных транзисторах, коллекторы которых соединены с базами.

2. Истоковый повторитель сигнала с малым уровнем систематической составляющей напряжения смещения нуля по п. 1, отличающийся тем, что в схему введен первый (14) дополнительный полевой транзистор с n-каналом, затвор которого подключен ко входу (1) устройства, сток соединен со второй (7) шиной источника питания, а исток соединен с базой первого (15) дополнительного p-n-p биполярного транзистора и через первый (16) дополнительный прямосмещенный p-n-переход соединен с выходом устройства (2) и эмиттером первого (15) дополнительного p-n-p биполярного транзистора, коллектор которого связан со второй (7) шиной источника питания, причем эмиттер первого (15) дополнительного p-n-p биполярного транзистора соединен со стоками второго (17) и третьего (18) дополнительных полевых транзисторов с n-каналом, затворы которых подключены к первой (5) шине источника питания, а истоки объединены и связаны с первой (5) шиной источника питания через два параллельно включенных p-n-перехода (19) и (20), выполненных на p-n-p биполярных транзисторах, коллекторы которых соединены с базами.

| ITAKURA K | |||

| et al., "A GaAs Bi-FET technology for large scale integration", International Technical Digest on Electron Devices Meeting, IEEE, 1989, стр | |||

| Гидравлический подъемник | 1922 |

|

SU389A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2536671C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2530263C1 |

| US 10141897 B2, 27.11.2018. | |||

Авторы

Даты

2022-11-24—Публикация

2022-08-15—Подача