Изобретение относится к области аналоговой микросхемотехники и может быть использовано в качестве BiJFet (биполярно-полевых) буферных усилителей, допускающих работу в условиях низких температур и воздействия проникающей радиации.

Известно значительное количество схем буферных усилителей (БУ), которые реализуются на биполярных (BJT) и полевых (BiJFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-25]. Во многих случаях схема БУ адаптируется под конкретные технологические процессы и внешние воздействующие факторы, например влияние низких температур и радиации, т.к. только в этом случае обеспечивается реализация предельных параметров БУ.

Для работы в тяжелых условиях эксплуатации (воздействие низких, в т.ч. криогенных температур, потока нейтронов, накопленной дозы радиации, гамма-квантов и т.д.) хорошо зарекомендовали себя микросхемы на основе BiJFet технологического процесса [26]. Однако данный технологический процесс не обеспечивает удовлетворительную работу аналоговых микросхем с использованием в их сигнальных цепях p-n-р транзисторов [26]. В этой связи в BiJFet ОУ рекомендуется преимущественно применять только полевые транзисторы с управляющим р-n переходом и биполярные n-р-n транзисторы [26]. Это накладывает существенные ограничения на применяемые схемотехнические решения выходных каскадов аналоговых микросхем данного класса.

В современной радиоэлектронной аппаратуре находят применение буферные усилители, реализованные в виде истоковых повторителей на BiJFet или КМОП транзисторах [1-20]. Известны также двухтактные выходные каскады только на КМОП транзисторах с р- или n-каналами [21-24]. В ряде случаев двухтактные выходные каскады выполняются на входных КМОП транзисторах и выходных биполярных транзисторах [25]. Благодаря простоте вышеназванные схемотехнические решения наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе базовых технологических процессов.

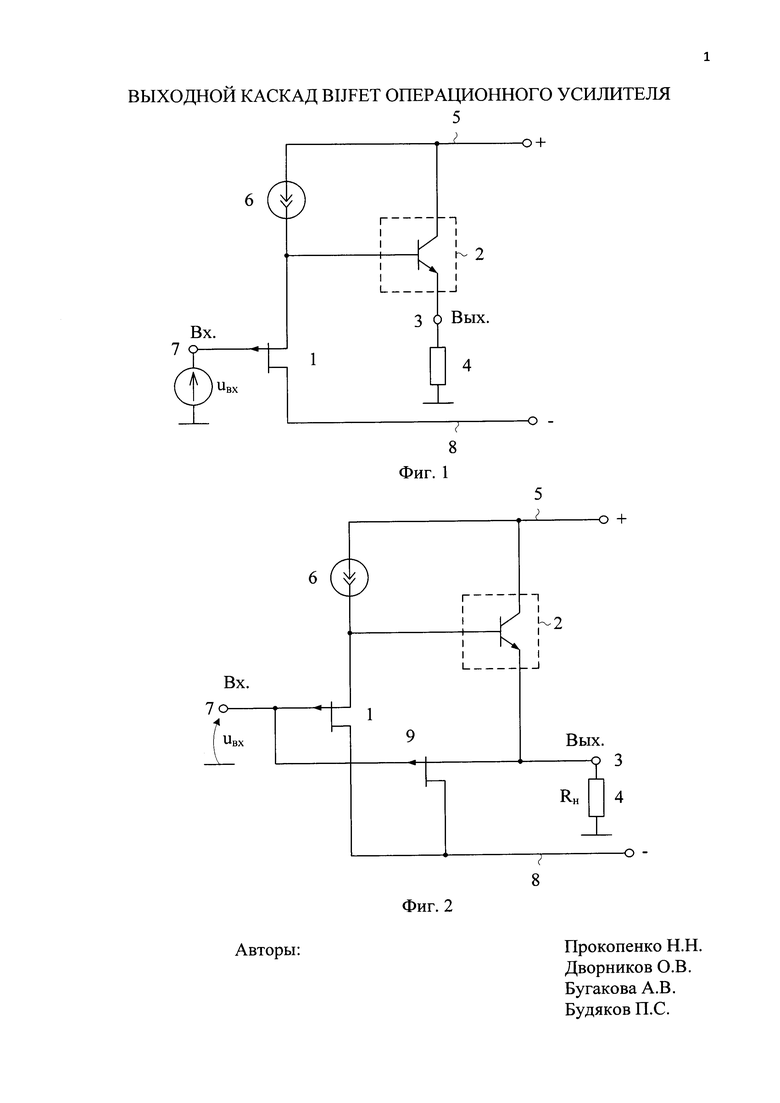

Ближайшим прототипом (фиг. 1) заявляемого устройства является выходной каскад по патенту US 4420726, fig. 1, fig. 2. Он содержит (фиг. 1) входной полевой транзистор 1 и выходной биполярный транзистор 2, эмиттер которого соединен с выходом устройства 3 и нагрузкой 4, а коллектор подключен к первой 5 шине источника питания, токостабилизирующий двухполюсник 6, включенный между базой выходного биполярного транзистора 2 и первой 5 шиной источника питания, причем исток входного полевого транзистора 1 связан с базой выходного биполярного транзистора 2, затвор входного полевого транзистора 1 подключен к входу устройства 7, а сток входного полевого транзистора 1 связан со второй 8 шиной источника питания.

Существенный недостаток известного буферного усилителя состоит в том, что из-за ограничений BiJFet технологического процесса, например, 3КБТ ОАО «Интеграл» (г. Минск), в нем не рекомендуется использовать р-n-р транзисторы и, как следствие, в БУ-прототипе не реализуется двухтактное усиление класса «АВ», что отрицательно сказывается на его энергетических параметрах, линейности амплитудной характеристики, уровне нелинейных искажений сигналов и др.

Основная задача предполагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного схемотехнического решения БУ для BiJFet технологических процессов (например, для базовых матричных кристаллов АБМК-1.3, АБМК-1.7, АБМК-2.1 и др.), обеспечивающего двухтактное преобразование входного напряжения (режим класса АВ) при высокой линейности проходной характеристики, малом входном токе, высоком входном дифференциальном сопротивлении.

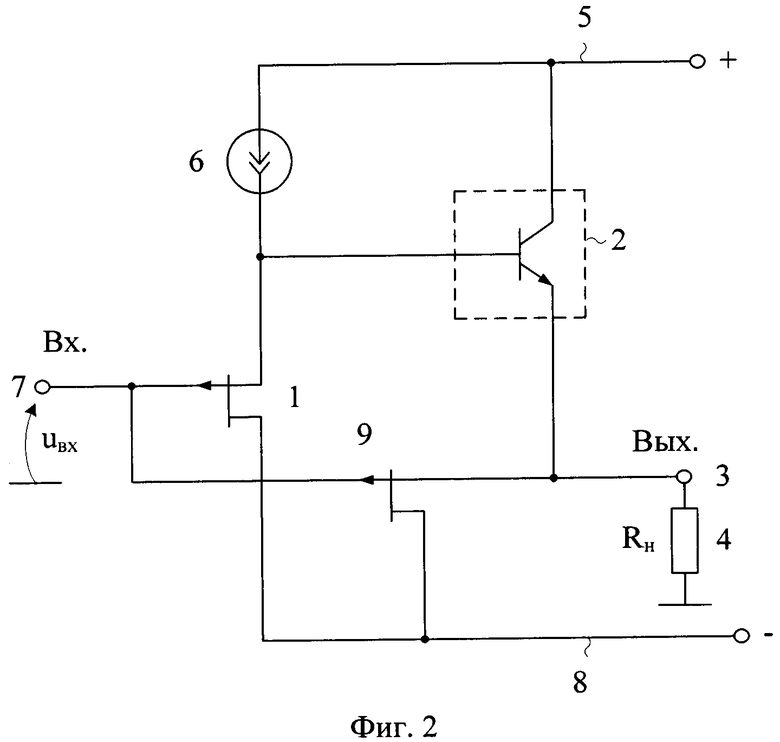

Поставленная задача достигается тем, что в выходном каскаде биполярно-полевого операционного усилителя фиг. 1, содержащем входной полевой транзистор 1 и выходной биполярный транзистор 2, эмиттер которого соединен с выходом устройства 3 и нагрузкой 4, а коллектор подключен к первой 5 шине источника питания, токостабилизирующий двухполюсник 6, включенный между базой выходного биполярного транзистора 2 и первой 5 шиной источника питания, причем исток входного полевого транзистора 1 связан с базой выходного биполярного транзистора 2, затвор входного полевого транзистора 1 подключен к входу устройства 7, а сток входного полевого транзистора 1 связан со второй 8 шиной источника питания, предусмотрены новые элементы и связи - в схему введен дополнительный полевой транзистор 9, затвор которого соединен с входом устройства 7, исток подключен к выходу устройства 3, а сток соединен со второй 8 шиной источника питания.

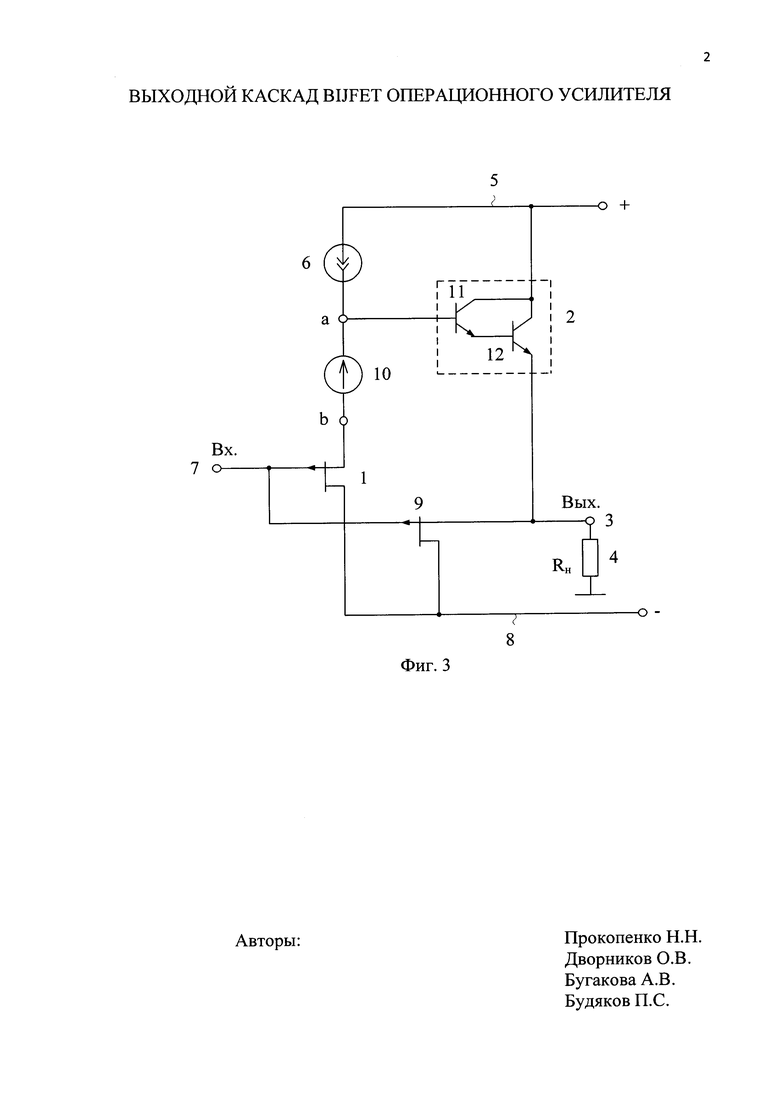

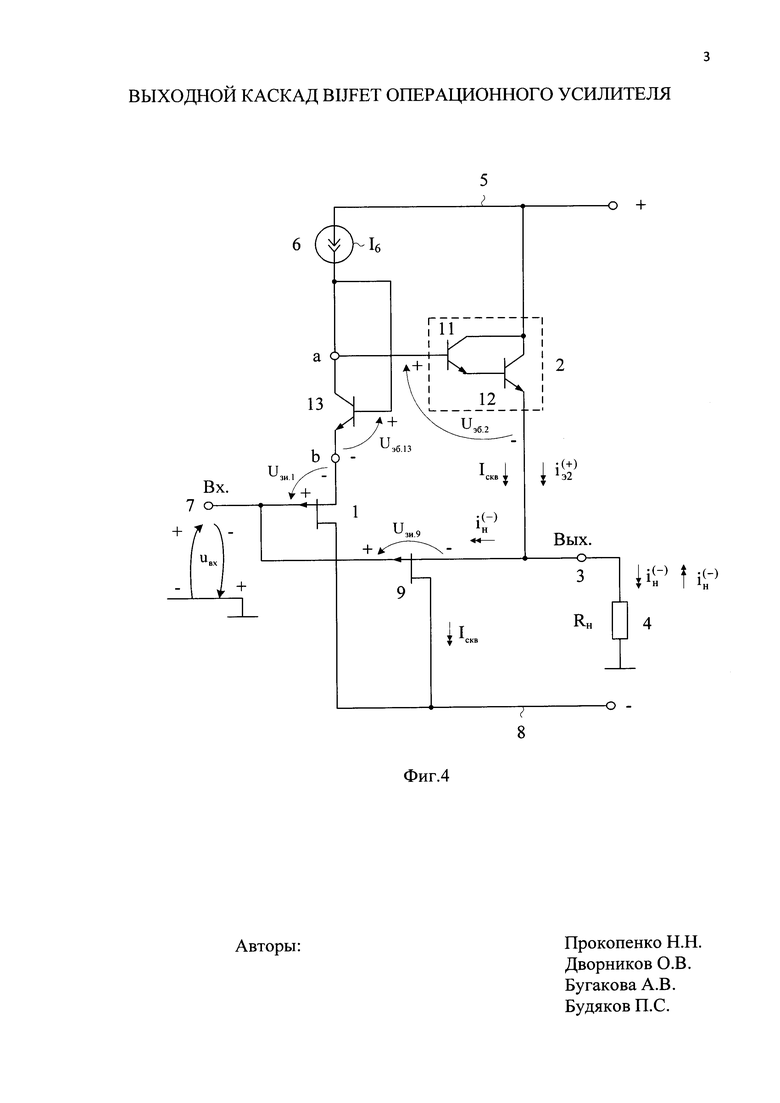

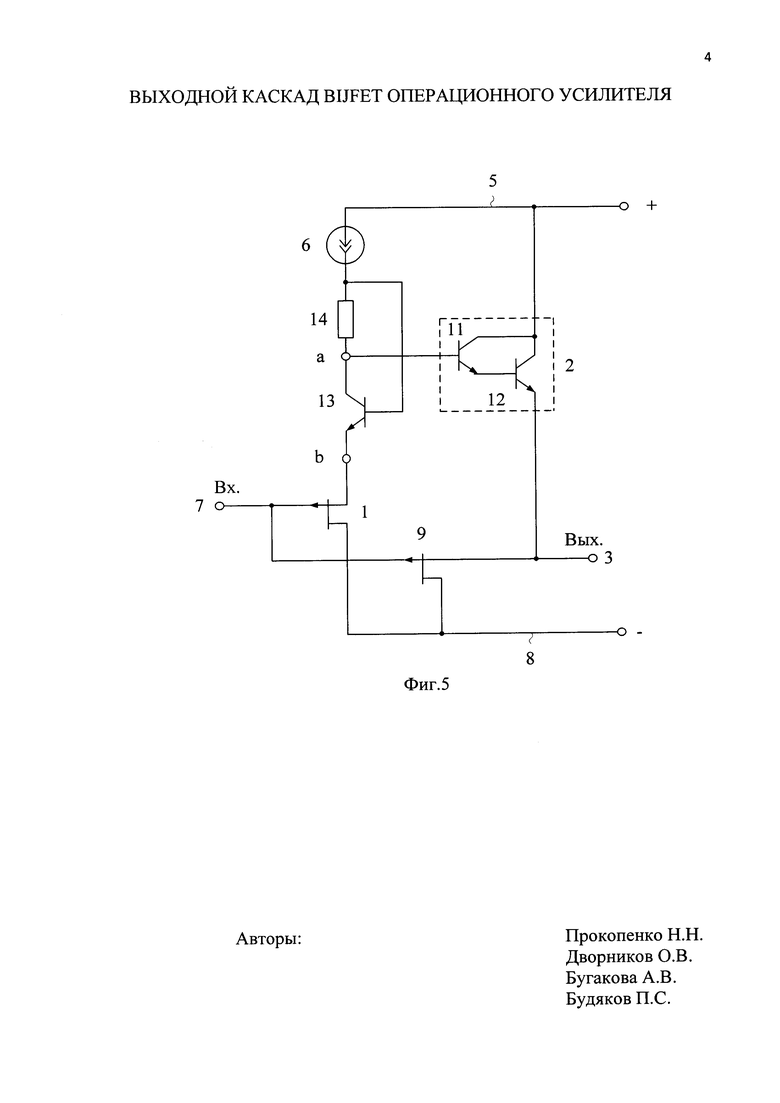

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения. На фиг. 3 представлена схема заявляемого устройства в соответствии с п. 2 и п. 3 формулы изобретения, а на фиг. 4 - п. 4 формулы изобретения. На фиг. 5 показана схема заявляемого устройства в соответствии с п. 5 формулы изобретения.

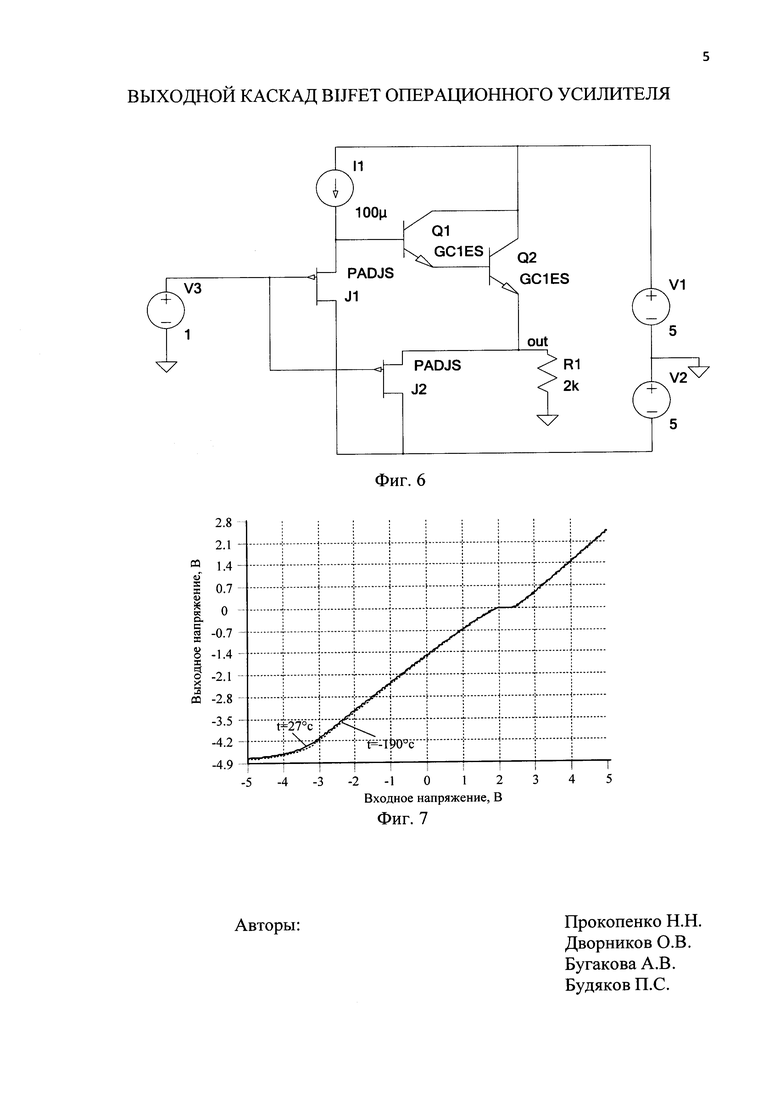

На фиг. 6 приведена схема заявляемого выходного каскада (соответствующая фиг. 2 и фиг. 3) в среде LTSpice на радиационно-зависимых и низкотемпературных моделях транзисторов базового матричного кристалла АБМК_1.7 [27].

На фиг. 7 представлена зависимость выходного напряжения заявляемого выходного каскада фиг. 6 от входного напряжения при разных температурах t=-190÷27°c, при токе I1=200 мкА (модели транзисторов PADJ сильноточные).

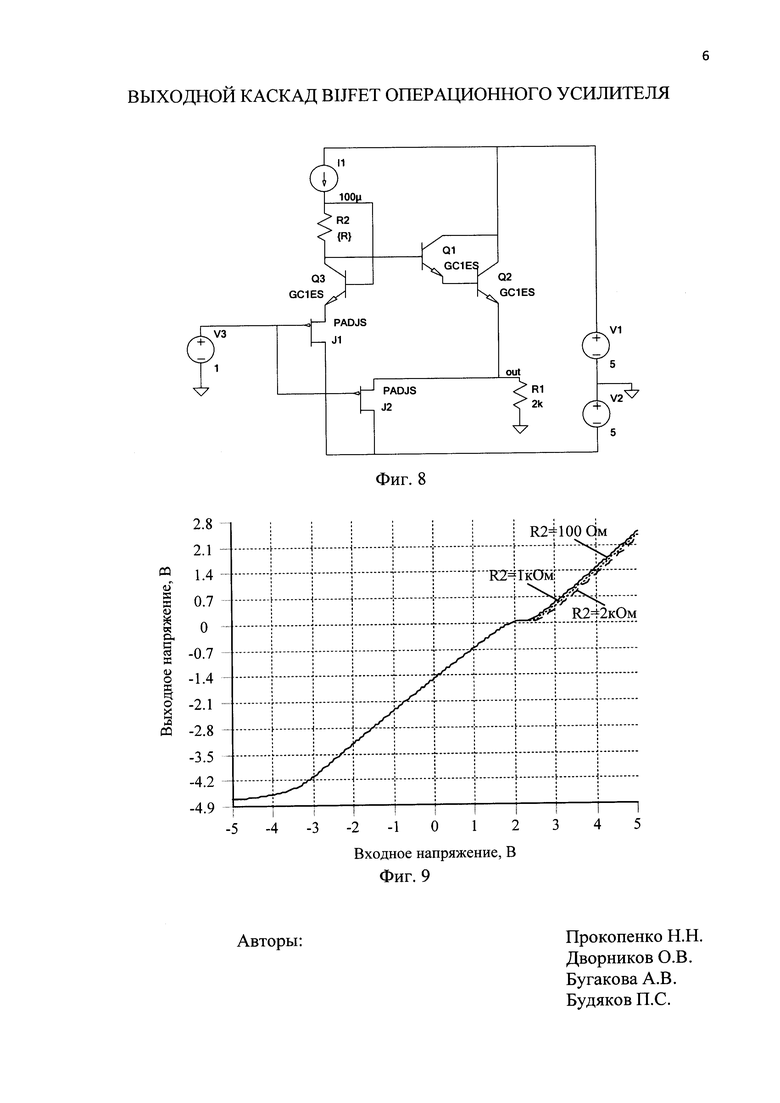

На фиг. 8 показана схема заявляемого выходного каскада, соответствующая фиг. 5, в среде LTSpice на радиационно-зависимых низкотемпературных моделях транзисторов базового матричного кристалла АБМК_1.7 [27].

На фиг. 9 приведена зависимость выходного напряжения заявляемого выходного каскада, соответствующая фиг. 8, от входного напряжения при разных значениях сопротивления R2=100÷2000 Ом, при t=-190°C, R1=2 кOм (модели транзисторов PADJ сильноточные).

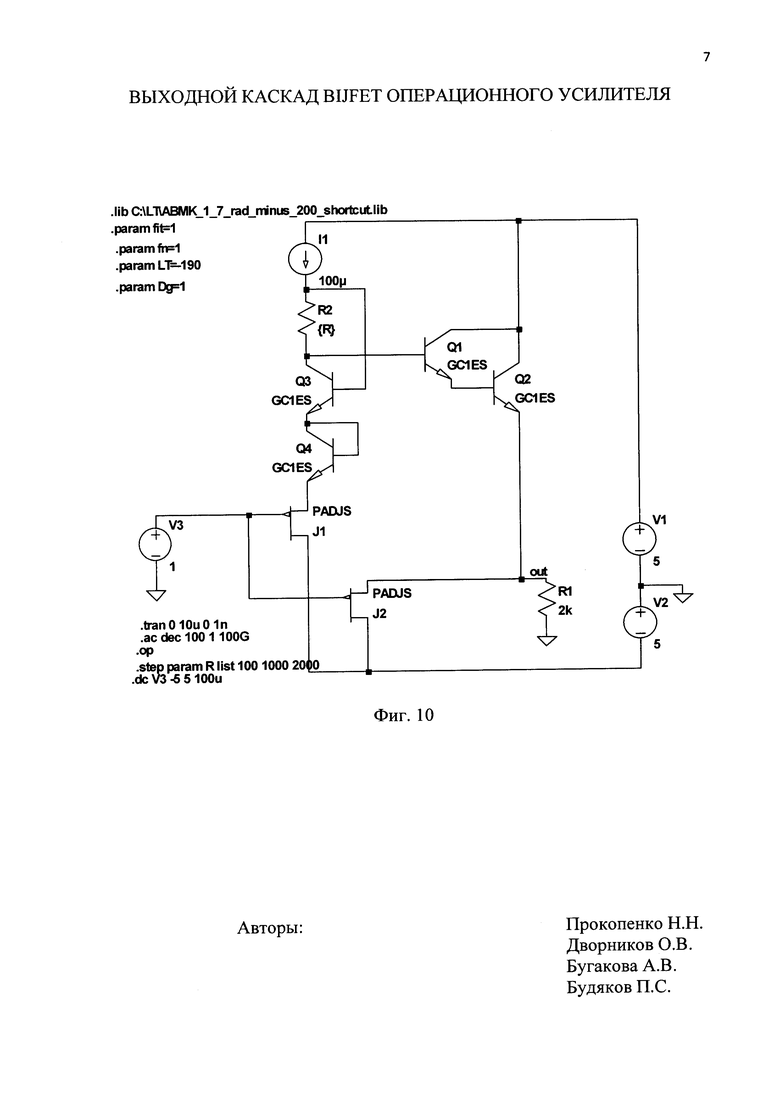

На фиг. 10 представлена схема заявляемого выходного каскада, соответствующая фиг. 5 и фиг. 3, в среде LTSpice на низкотемпературных моделях транзисторов базового матричного кристалла АБМК_1.7 [27].

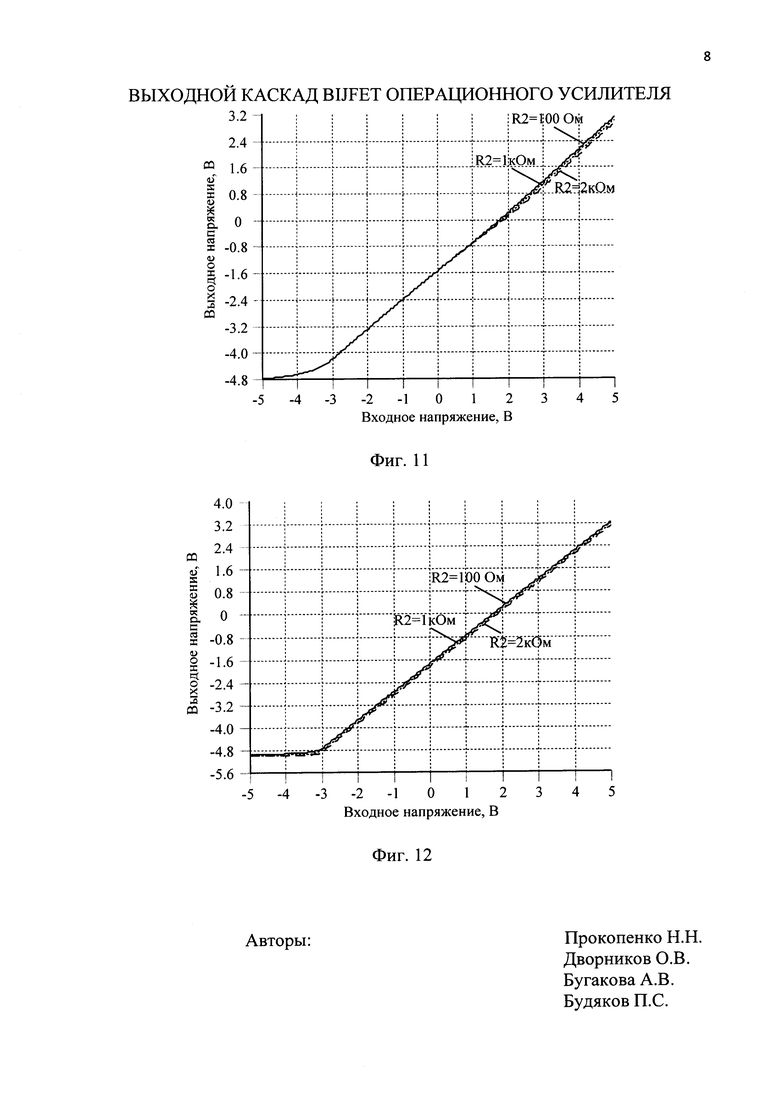

На фиг. 11 показана зависимость выходного напряжения заявляемого выходного каскада, соответствующая фиг. 10, от входного напряжения при разных значениях сопротивления R2=100÷2000 Ом, при низких температурах t=-190°C, R1=2 кOм (модели транзисторов PADJ сильноточные).

На фиг. 12 приведена зависимость выходного напряжения заявляемого выходного каскада, соответствующая фиг. 10, от входного напряжения при разных значениях сопротивления R2=100÷2000 Ом, при комнатной температуре t=27°C, R1=1 ГОм (модели транзисторов PADJ сильноточные).

Выходной каскад BiJFet (биполярно-полевого) операционного усилителя фиг. 2 содержит входной полевой транзистор 1 и выходной биполярный транзистор 2, эмиттер которого соединен с выходом устройства 3 и нагрузкой 4, а коллектор подключен к первой 5 шине источника питания, токостабилизирующий двухполюсник 6, включенный между базой выходного биполярного транзистора 2 и первой 5 шиной источника питания, причем исток входного полевого транзистора 1 связан с базой выходного биполярного транзистора 2, затвор входного полевого транзистора 1 подключен к входу устройства 7, а сток входного полевого транзистора 1 связан со второй 8 шиной источника питания. В схему введен дополнительный полевой транзистор 9, затвор которого соединен с входом устройства 7, исток подключен к выходу устройства 3, а сток соединен со второй 8 шиной источника питания. В частном случае, выходной биполярный транзистор может быть реализован на основе составного транзистора Дарлингтона.

На фиг. 3, в соответствии с п. 2 формулы изобретения, исток входного полевого транзистора 1 связан с базой выходного биполярного транзистора 2 через цепь согласования потенциалов 10.

На фиг. 3, в соответствии с п. 3 формулы изобретения, выходной биполярный транзистор 2 выполнен по схеме классического составного транзистора Дарлингтона на транзисторах 11 и 12.

На фиг. 4, в соответствии с п. 4 формулы изобретения, цепь согласования потенциалов 10 содержит дополнительный транзистор 13, эмиттер которого подключен к истоку входного полевого транзистора 1, коллектор связан с базой выходного биполярного транзистора 2, а база дополнительного транзистора 13 соединена с токостабилизирующим двухполюсником 6 и связана с коллектором данного дополнительного транзистора 13.

На фиг. 5, в соответствии с п. 5 формулы изобретения, база дополнительного транзистора 13 подключена к токостабилизирующему двухполюснику 6 и связана с коллектором дополнительного транзистора 13 и базой выходного биполярного транзистора 2 через дополнительный резистор 14.

Рассмотрим работу предлагаемого БУ, фиг. 4.

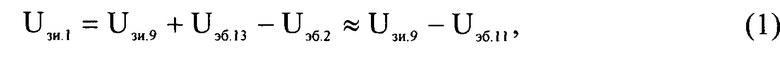

В статическом режиме напряжение затвор-исток Uзи.9 дополнительного полевого транзистора 9 больше, чем напряжение затвор-исток Uзи.1 входного полевого транзистора 1, так как

где Uэб.13 - напряжение эмиттер-база транзистора 13; Uэб.2 - напряжение эмиттер база составного транзистора 2; Uэб.11 - напряжение эмиттер-база транзистора 11.

Как следствие статический ток истока дополнительного полевого транзистора 9 меньше, чем статический тока входного транзистора 1, что обеспечивает малое значение сквозного тока БУ (Iскв.).

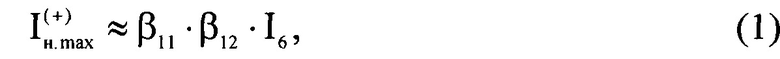

При положительном входном напряжении БУ фиг. 4 ток в нагрузке Rн определяется приращением эмиттерного тока  транзистора 2. При этом максимальное значение тока в нагрузке определяется формулой

транзистора 2. При этом максимальное значение тока в нагрузке определяется формулой

где I6 - ток двухполюсника 6; β11, β12 - коэффициенты усиления по току базы транзисторов 11 и 12.

Если входное напряжение принимает отрицательные значения, то отрицательное приращение тока в нагрузке  обеспечивается током стока дополнительного полевого транзистора 9. При этом максимальные значения

обеспечивается током стока дополнительного полевого транзистора 9. При этом максимальные значения  определяются стокозатворной характеристикой дополнительного полевого транзистора 9. Во многих случаях

определяются стокозатворной характеристикой дополнительного полевого транзистора 9. Во многих случаях  может измеряться единицами-десятками милиампер (8÷15 мА). Этого достаточно для многих применений БУ.

может измеряться единицами-десятками милиампер (8÷15 мА). Этого достаточно для многих применений БУ.

Следует заметить, что в схеме фиг. 4 входное сопротивление БУ определяется входными сопротивлениями полевых транзисторов 1 и 9, что особенно важно для получения больших коэффициентов усиления по напряжению ОУ с динамическими нагрузками на основе токовых зеркал [26].

В схеме фиг. 5, в соответствии с п. 5 формулы изобретения, вводится дополнительный резистор 14, влияющий на зону нечувствительности проходной характеристики БУ в области средних значений входных напряжений (фиг. 7). Так, при сопротивлении R14=0 зона нечувствительности будет минимальной.

В ряде случаев в эмиттер транзистора 13 (фиг. 10) может вводиться дополнительный р-n переход (Q4), что позволяет с помощью рационального выбора его сопротивления обеспечить линейную проходную характеристику фиг. 12 в широком диапазоне температур при различных вариантах построения составного транзистора 2 (одиночный вариант, схема Дарлингтона, схема Линна и т.д.).

Компьютерное моделирование (фиг. 7, фиг. 9, фиг. 11, фиг. 12) показывает, что предлагаемый буферный усилитель, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации, имеет существенные достоинства в сравнении с известными вариантами построения БУ при их реализации в рамках BiJFet технологического процесса.

Источники информации

1. WO 2007135139.

2. US 4743862.

3. US 6433638, fig. 1a-2.

4. US 20050253653.

5. US 4825174, fig. 3, fig. 6.

6. RU 2099856, fig. 3.

7. US 4904953, fig. 2.

8. US 7896339, fig. 4.

9. US 6342814.

10. US 2010/0182086.

11. US 5387880, fig. 1.

12. US 4598253.

13. US 4667165, fig. 2.

14. US 4596958.

15. US 7116172, fig. 4, fig. 5.

16. US 5648743.

17. US 5367271, fig. 2.

18. US 2000/0112075, fig. 3.

19. US 5065043, fig. 1f.

20. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 2-е. – М.: Издательство БИНОМ. 2014. - 704 с. Рис. 3.26, рис. 3.28, рис. 3.29.

21. US 2007/0115056, fig. 2.

22. US 7548117, fig. 5.

23. EP 0 293486 B1, fig. 5.

24. Patt Boonyaporn, Varakorn Kasemsuwan. A High Performance Class AB CMOS Rail to Rail Voltage Follower // ASIC, 2002. Proceedings. 2002 IEEE Asia-Pacific Conference on, pp. 161-163.

25. US 4420726, fig. 1 - fig. 3.

26. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

27. O.V. Dvornikov, V.L. Dziatlau, N.N. Prokopenko, K.О. Petrosiants, N.V. Kozhukhov and V.A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2677401C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2670777C9 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах | 2022 |

|

RU2792710C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

Изобретение относится к области аналоговой микросхемотехники и может быть использовано в качестве биполярно-полевых (BiJFet) буферных усилителей. Техническим результатом является обеспечение двухтактного преобразования входного напряжения при высокой линейности проходной характеристики, малом входном токе, высоком входном дифференциальном сопротивлении. Выходной каскад BiJFet (биполярно-полевого) операционного усилителя содержит входной полевой транзистор (1) и выходной биполярный транзистор (2), эмиттер которого соединен с выходом устройства (3) и нагрузкой (4), а коллектор подключен к первой (5) шине источника питания, токостабилизирующий двухполюсник (6), включенный между базой выходного биполярного транзистора (2) и первой (5) шиной источника питания, причем исток входного полевого транзистора (1) связан с базой выходного биполярного транзистора (2), затвор входного полевого транзистора (1) подключен к входу устройства (7), а сток входного полевого транзистора (1) связан со второй (8) шиной источника питания. В схему введен дополнительный полевой транзистор (9), затвор которого соединен с входом устройства (7), исток подключен к выходу устройства (3), а сток соединен со второй (8) шиной источника питания. 4 з.п. ф-лы, 12 ил.

1. Выходной каскад BiJFet (биполярно-полевого) операционного усилителя, содержащий входной полевой транзистор (1) и выходной биполярный транзистор (2), эмиттер которого соединен с выходом устройства (3) и нагрузкой (4), а коллектор подключен к первой (5) шине источника питания, токостабилизирующий двухполюсник (6), включенный между базой выходного биполярного транзистора (2) и первой (5) шиной источника питания, причем исток входного полевого транзистора (1) связан с базой выходного биполярного транзистора (2), затвор входного полевого транзистора (1) подключен к входу устройства (7), а сток входного полевого транзистора (1) связан со второй (8) шиной источника питания, отличающийся тем, что в схему введен дополнительный полевой транзистор (9), затвор которого соединен с входом устройства (7), исток подключен к выходу устройства (3), а сток соединен со второй (8) шиной источника питания.

2. Выходной каскад BiJFet (биполярно-полевого) операционного усилителя по п. 1, отличающийся тем, что исток входного полевого транзистора (1) связан с базой выходного биполярного транзистора (2) через цепь согласования потенциалов (10).

3. Выходной каскад BiJFet (биполярно-полевого) операционного усилителя по п. 1, отличающийся тем, что выходной биполярный транзистор (2) выполнен по схеме составного транзистора Дарлингтона.

4. Выходной каскад BiJFet (биполярно-полевого) операционного усилителя по п. 2, отличающийся тем, что цепь согласования потенциалов (10) содержит дополнительный транзистор (13), эмиттер которого подключен к истоку входного полевого транзистора (1), коллектор связан с базой выходного биполярного транзистора (2), а база дополнительного транзистора (13) соединена с токостабилизирующим двухполюсником (6) и связана с коллектором данного дополнительного транзистора (13).

5. Выходной каскад BiJFet (биполярно-полевого) операционного усилителя по п. 4, отличающийся тем, что база дополнительного транзистора (13) подключена к токостабилизирующему двухполюснику (6) и связана с коллектором дополнительного транзистора (13) и базой выходного биполярного транзистора (2) через дополнительный резистор (14).

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

Авторы

Даты

2018-10-05—Публикация

2017-11-09—Подача