Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве арсенид-галлиевого выходного каскада различных аналоговых устройств, допускающих работу в условиях воздействия проникающей радиации, низких и высоких температур.

Известно значительное количество схем выходных каскадов усилителей мощности и буферных усилителей (БУ) аналоговых микроэлектронных изделий, которые реализуются на биполярных (BJT) и полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-26]. Сегодня популярны схемы БУ с составными BJT и CMOS (JFET) выходными транзисторами с разными типами каналов [31-33], однотактные БУ с входным CMOS и выходными n-р-n транзисторами [34], двухтактные БУ с выходными однотипными JFET транзисторами и входными биполярными p-n-р (n-р-n) [35], двухтактные БУ на комплементарных JFET транзисторах [36-39], однотактные БУ только на JFET [40].

Во многих применениях схема БУ адаптируется под конкретные технологические процессы и внешние воздействующие факторы, например, влияние низких температур и радиации, т.к. только в этом случае обеспечивается реализациях предельных параметров БУ.

В настоящее время в российской и зарубежной микроэлектронике уделяется повышенное внимание арсенид-галлиевым микросхемам. Данное направление создания электронной компонентной базы относится к числу наиболее перспективных в задачах космического приборостроения. Однако, особенности арсенид-галлиевых технологических процессов накладывают существенные ограничения на типы реализуемых транзисторов и их характеристики. Так, например, арсенид-галлиевый технологический процесс, освоенный фирмами США [27-30], а также Минским научно-исследовательским институтом радиоматериалов (https://mniirm.by/), ориентирован на изготовление аналоговых схем, содержащих только полевые GaAs транзисторы с управляющим р-n переходом и биполярные GaAs р-n-р транзисторы. Применение других полупроводниковых приборов не допускается. Это накладывает существенные ограничения на схемотехнику аналоговых устройств, ориентированных на данный технологический процесс.

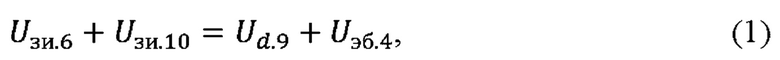

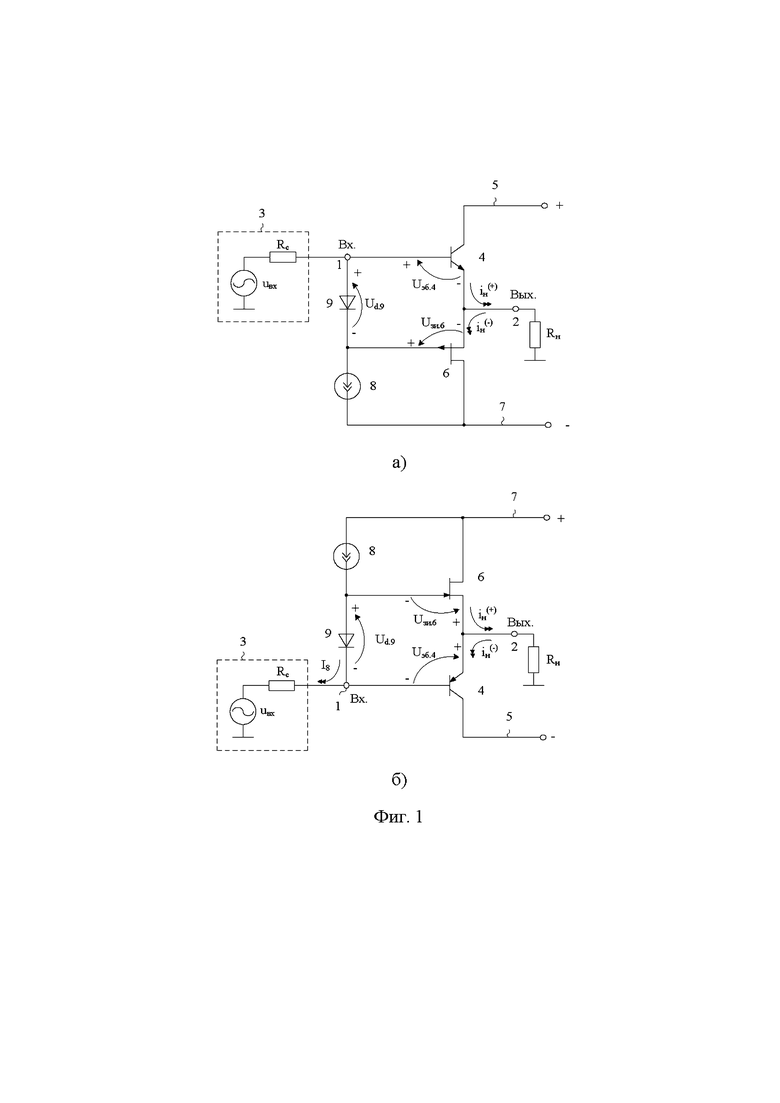

Ближайшим прототипом (фиг. 1) заявляемого устройства является схема буферного усилителя, которая используется в серийных микросхемах LF155, LF256, LF357 (http://www.mit.edu/6.301/LF155.pdf) фирмы National Semiconductor (США). В рамках современных технологических процессов она может быть реализована на полевых транзисторах или с р- или n-каналами. Буферный усилитель-прототип (фиг. 1б) содержит вход 1 и выход 2 устройства, источник сигнала 3, соединенный со входом 1 устройства, выходной биполярный транзистор 4, база которого соединена со входом 1 устройства, а коллектор связан с первой 5 шиной источника питания, причем выход устройства 2 связан с эмиттером выходного биполярного транзистора 4, входной полевой транзистор 6, сток которого согласован со второй 7 шиной источника питания, вспомогательный источник тока 8, согласующий р-n переход 9.

Существенный недостаток буферного усилителя - прототипа состоит в том, что при его реализации на GaAs JFET и GaAs p-n-p BJT работа схемы БУ фиг. 1 возможна только в том случае, если он согласован по входу с дополнительным эмиттерным повторителем (как это сделано в микросхеме LF155). То есть в известной схеме фиг. 1 через источник сигнала 3 всегда протекает статический ток вспомогательного источника тока 8, что не допускается во многих других случаях ее практического использования. С другой стороны, исключение из схемы р-n перехода 9 создает зону нечувствительности на амплитудной характеристике БУ. Таким образом, реализация известной схемы на основе арсенид-галлиевых JFET и BJT транзисторах не позволяет обеспечить высокую линейность амплитудной характеристики и малый входной ток БУ.

Основная задача предполагаемого изобретения состоит в создании буферного усилителя, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим р-n переходом и биполярных GaAs p-n-р транзисторах и обеспечивающего малую зону нечувствительности амплитудной характеристики.

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, источник сигнала 3, соединенный со входом 1 устройства, выходной биполярный транзистор 4, база которого соединена со входом 1 устройства, а коллектор связан с первой 5 шиной источника питания, причем выход устройства 2 связан с эмиттером выходного биполярного транзистора 4, входной полевой транзистор 6, сток которого согласован со второй 7 шиной источника питания, вспомогательный источник тока 8, согласующий р-n переход 9, предусмотрены новые элементы и связи - затвор входного полевого транзистора 6 соединен со входом 1 устройства, его исток связан со вспомогательным источником тока 8 и подключен к затвору дополнительного полевого транзистора 10, сток дополнительного полевого транзистора 10 согласован со второй 7 шиной источника питания, а исток связан с выходом 2 устройства через согласующий р-n переход 9 и подключен к стоку входного полевого транзистора 6.

На чертеже фиг. 1 показана схема буферного усилителя - прототипа.

На чертеже фиг. 2 приведена схема заявляемого GaAs буферного усилителя в соответствии с п. 1 формулы изобретения.

На чертеже фиг. 3 представлена схема заявляемого GaAs буферного усилителя с уменьшенной зоной нечувствительности в соответствии с п. 2 формулы изобретения.

На чертеже фиг.4 показана схема заявляемого GaAs БУ фиг. 2 в среде LTspice без входного смещения (V1=0) при t=27°С, Vcc=Vee=±10 В, Rload=∞ Ом, I1=20 мкА и количестве параллельно включеных GaAs полевых транзисторов VT3=5 шт.

На чертеже фиг. 5 приведена амплитудная характеристика GaAs БУ фиг. 4 в среде LTspice при t=27°С, Vcc=Vee=±10 В, напряжении смещения V1=-1.3 В, Rload=1 кОм/2 кОм/4 кОм/10 кОм/∞ Ом, I1=20 мкА.

На чертеже фиг. 6 представлена схема для моделирования GaAs БУ с GaAs дополнительными р-n переходами 9 и 11 фиг. 3 в среде LTspice при t=27°С, R1=2 кОм, Vcc=Vee=±10 В, Rload=∞ Ом и напряжении смещения V1=-1.83 В.

На чертеже фиг. 7 показана амплитудная характеристика GaAs БУ с GaAs дополнительными р-n переходами 9 и 11 фиг. 6 в среде LTspice при t=27°С, R1=2 кОм, Vcc=Vee=±10 В, Rload=2 кОм/10 кОм/∞ Ом и напряжении смещения V1=-1.83 В.

Двухтактный арсенид-галлиевый буферный усилитель с малой зоной нечувствительности амплитудной характеристики фиг. 2 содержит вход 1 и выход 2 устройства, источник сигнала 3, соединенный со входом 1 устройства, выходной биполярный транзистор 4, база которого соединена со входом 1 устройства, а коллектор связан с первой 5 шиной источника питания, причем выход устройства 2 связан с эмиттером выходного биполярного транзистора 4, входной полевой транзистор 6, сток которого согласован со второй 7 шиной источника питания, вспомогательный источник тока 8, согласующий р-n переход 9. Затвор входного полевого транзистора 6 соединен со входом 1 устройства, его исток связан со вспомогательным источником тока 8 и подключен к затвору дополнительного полевого транзистора 10, сток дополнительного полевого транзистора 10 согласован со второй 7 шиной источника питания, а исток связан с выходом 2 устройства через согласующий р-n переход 9 и подключен к стоку входного полевого транзистора 6.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, в качестве вспомогательного источника тока 8 используется токостабилизирующий резистор, включенный между истоком входного полевого транзистора 6 и эмиттером выходного биполярного транзистора 4, причем выход устройства 2 связан с эмиттером выходного биполярного транзистора 4 через дополнительный р-n переход 11.

На чертежах фиг. 1 - фиг. 3 двухполюсник Rн моделирует свойства нагрузки.

Рассмотрим работу буферного усилителя фиг. 2.

В статическом режиме (Rн=∞, uвх=0) в схеме БУ фиг. 2 устанавливаются токи и напряжения, показанные в среде LTspice для частного случая моделирования на чертеже фиг. 4. При этом все транзисторы работают при токах истока (эмиттера) порядка 10-80 мкА, т.к. за счет рационального выбора вспомогательного источника тока 8 обеспечивается равенство:

где Ud.9 - статическое напряжение на согласующем р-n переходе 9;

Uзи.6, Uзи.10 - напряжения затвор-исток входного полевого транзистора 6 и дополнительного полевого транзистора 10;

Uэб.4 - напряжение эмиттер-база выходного биполярного транзистора 4.

За счет введения дополнительного полевого транзистора 10 и согласующего р-n перехода 9 в схеме БУ фиг. 2 реализуется слаботочный статический режим.

Входной ток БУ фиг. 2 равен току базы выходного биполярного транзистора 4:

где Iэ.4 - ток эмиттера выходного биполярного транзистора 4;

β4 - коэффициент усиления по току базы выходного биполярного транзистора 4.

Если на вход 1 подается положительное напряжение, то это вызывает увеличение тока истока дополнительного полевого транзистора 10 и создает ток положительного направления iн(+) в нагрузке Rн. При этом подзапирается выходной биполярный транзистор 4. Максимальное значение тока нагрузки Iн.max(+) определяется максимальным допустимым током истока дополнительного полевого транзистора 10. При параллельном включении нескольких элементарных полевых транзисторов в качестве дополнительного полевого транзистора 10 численные значения максимального тока Iн.max(+) могут быть увеличены до заданных значений.

При уменьшении отрицательного напряжения uвх(-) на входе 1, которое практически с единичным коэффициентом передается в исток дополнительного полевого транзистора 10, подзапирается дополнительный полевой транзистор 10 и согласующий р-n переход 9, а ток iн(-) обеспечивается по цепи эмиттера выходного биполярного транзистора 4. Как следствие, максимальный отрицательный ток Iн.max(+) в нагрузке Rн будет определяться (3 выходного биполярного транзистора 4 и сопротивлением Rc источника сигнала 3.

Схема фиг. 3 в сравнении со схемой фиг. 2 обеспечивает более широкие возможности установления статического режима по току, в т.ч. сквозного тока БУ, а также рабочих токов полевых и биполярных транзисторов. Основное уравнение, определяющее статический режим схемы фиг. 3, имеет вид

За счет выбора тока вспомогательного источника тока 8 в схеме фиг. 3 можно управлять численными значениями напряжения Uзи.6, и как следствие, выбирать заданный статический режим БУ.

Амплитудная характеристика предлагаемого БУ фиг. 4, представленная на чертеже фиг. 5, показывает, что рассматриваемая схема со смещением нуля источника V1 обеспечивает выходные напряжения с максимальной амплитудой 8,9 - 9,94 В. Для низкоомных сопротивлений нагрузки необходимо увеличивать ширину канала применяемых полевых транзисторов или использовать параллельное включение нескольких активных элементов JFET.

Компьютерное моделирование (фиг. 4, фиг. 5, фиг. 6) показывает, что предлагаемый буферный усилитель, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [26], имеет существенные достоинства в сравнении с известными вариантами построения БУ при их реализации в рамках рассматриваемого арсенид-галлиевого технологического процесса, обеспечивающего создание только полевых транзисторов с управжющим р-n переходом и биполярных p-n-р транзисторов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU №2523947 fig. 4, 2014 г.

2. Патент WO 2007135139, 2007 г.

3. Патент US 4743862, 1988 г.

4. Патент US 6433638, fig. 1a-2, 2002 г.

5. Патентная заявка US 20050253653,2005 г.

6. Патент US 4825174, fig. 3, fig. 6,1989 г.

7. Патент RU 2099856, fig. 3, 1997 г.

8. Патент US 4904953, fig. 2,1990 г.

9. Патент US 7896339, fig. 4, 2011 г.

10. Патент US 6342814, 2002 г.

11. Патентная заявка US 2010/0182086, 2010 г.

12. Патент US 5387880, fig. 1,1995 г.

13. Патент US 4598253,1986 г.

14. Патент US 4667165, fig. 2,1987 г.

15. Патент US 4596958,1986 г.

16. Патент US 7116172, fig. 4, fig. 5, 2006 г.

17. Патент US 5648743,1997 г.

18. Патент US 5367271, fig. 2,1994 г.

19. Патентная заявка US 2000/0112075, fig. 3, 2000 г.

20. Патент US 5065043, fig. 1f, 1991 г.

21. Патентная заявка US 2007/0115056, fig. 2, 2007 г.

22. Патент US 7548117, fig. 5, 2009 г.

23. Патент ЕР 0 293486 B1, fig. 5,1991 г.

24. Патент US 4420726, fig. 1 - fig. 3, 1983 г.

25. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ.- Изд. 2-е. - М.: Издательство БИНОМ. 2014. - 704 с. Рис. 3.26, рис. 3.28, рис. 3.29

26. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. - М.: СОЛОН-Пресе, 2021. - 200 с.

27. М. Fresina, "Trends in GaAs HBTs for wireless and RF," 2011 IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Atlanta, GA, USA, 2011, pp.150-153. doi: 10.1109/BCTM.2011.6082769

28. P. J. Zampardi, M. Sun, C. Cismaru and J. Li, "Prospects for a BiCFET III-V HBT Process," 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 2012, pp. 1-3. doi: 10.1109/CSICS.2012.6340116

29. W. Liu, D. Hill, D. Costa and J. S. Harris, "High-performance microwave AlGaAs-InGaAs Pnp HBT with high-DC current gain," in IEEE Microwave and Guided Wave Letters, vol. 2, no. 8, pp.331-333, Aug. 1992. doi: 10.1109/75.153604

30. Peatman W. et al. InGaP-Plus™ advanced GaAs BiFET technology and applications // CS MANTECH Conference, May 14-17, 2007, Austin, Texas, USA. pp. 243-246.

31. Патентная заявка US 2007/0115056, fig.2, 2007 г.

32. Патент DE 2548906, fig. 1,1975 г.

33. Патент WO 2014/168518 (PCT RU 2014/000255), fig. 8, 2014 г.

34. Патент US 4.420.726, fig. 1, fig. 3,1983 г.

35. Патент DE 2354552, fig. 2, 1973 г.

36. Патент RU 2723673, 2020 г.

37. Патент RU 2721940, 2020 г.

38. D. Danyuk. Linear Integrated Systems Headphone Amplifier Evaluation Board. URL: https://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluatio n_Board.pdf

39. Патент US 5.083.046, fig. 3, 1992 г.

40. Патент US 5.367.271, fig. 2, 1994 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2766868C1 |

| НЕИНВЕРТИРУЮЩИЙ ВЫХОДНОЙ КАСКАД АРСЕНИД-ГАЛЛИЕВОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2784049C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ n-КАНАЛЬНЫХ ПОЛЕВЫХ И p-n-p БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2784376C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве арсенид-галлиевого выходного каскада различных аналоговых устройств, допускающих работу в условиях воздействия проникающей радиации, низких и высоких температур. Технический результат: создание буферного усилителя, реализуемого на JFET арсенид-галлиевых полевых транзисторах с управляющим р-n-переходом и биполярных GaAs p-n-р-транзисторах и обеспечивающего малую зону нечувствительности амплитудной характеристики. Двухтактный арсенид-галлиевый буферный усилитель с малой зоной нечувствительности амплитудной характеристики содержит вход (1) и выход (2) устройства, источник сигнала (3), соединенный со входом (1) устройства, выходной биполярный транзистор (4), база которого соединена со входом (1) устройства, а коллектор связан с первой (5) шиной источника питания, причем выход устройства (2) связан с эмиттером выходного биполярного транзистора (4), входной полевой транзистор (6), сток которого согласован со второй (7) шиной источника питания, вспомогательный источник тока (8), согласующий р-n-переход (9). Затвор входного полевого транзистора (6) соединен со входом (1) устройства, его исток связан со вспомогательным источником тока (8) и подключен к затвору дополнительного полевого транзистора (10), сток дополнительного полевого транзистора (10) согласован со второй (7) шиной источника питания, а исток связан с выходом (2) устройства через согласующий р-n-переход (9) и подключен к стоку входного полевого транзистора (6). 1 з.п. ф-лы, 7 ил.

1. Двухтактный арсенид-галлиевый буферный усилитель с малой зоной нечувствительности амплитудной характеристики, содержащий вход (1) и выход (2) устройства, источник сигнала (3), соединенный со входом (1) устройства, выходной биполярный транзистор (4), база которого соединена со входом (1) устройства, а коллектор связан с первой (5) шиной источника питания, причем выход устройства (2) связан с эмиттером выходного биполярного транзистора (4), входной полевой транзистор (6), сток которого согласован со второй (7) шиной источника питания, вспомогательный источник тока (8), согласующий р-n-переход (9), отличающийся тем, что затвор входного полевого транзистора (6) соединен со входом (1) устройства, его исток связан со вспомогательным источником тока (8) и подключен к затвору дополнительного полевого транзистора (10), сток дополнительного полевого транзистора (10) согласован со второй (7) шиной источника питания, а исток связан с выходом (2) устройства через согласующий р-n-переход (9) и подключен к стоку входного полевого транзистора (6).

2. Двухтактный арсенид-галлиевый буферный усилитель с малой зоной нечувствительности амплитудной характеристики по п. 1, отличающийся тем, что в качестве вспомогательного источника тока (8) используется токостабилизирующий резистор, включенный между истоком входного полевого транзистора (6) и эмиттером выходного биполярного транзистора (4), причем выход устройства (2) связан с эмиттером выходного биполярного транзистора (4) через дополнительный р-n-переход (11).

| ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ТРАНЗИСТОРОВ | 2013 |

|

RU2523947C1 |

| УСИЛИТЕЛЬНЫЙ КАСКАД | 1994 |

|

RU2099856C1 |

| US 4420726 A1, 13.12.1983 | |||

| US 7548117 B2, 16.06.2009 | |||

| US 5065043 A1, 12.11.1991 | |||

| US 4904953 A1, 27.02.1990. | |||

Авторы

Даты

2023-02-03—Публикация

2022-03-17—Подача