Изобретение относится к области автоматики и измерительной техники и может быть использовано в арифметических устройствах, специализированных и универсальных ЭВМ.

Из существующего уровня техники известны параллельные сумматоры аналогичного назначения, в состав которых входят двоичные вероятностные элементы, распределительные линии задержки, накопительный счетчик, выходная группа вентилей, счетчик делитель и элемент «ИЛИ» (Вероятностный сумматор параллельного типа, АС №409221, СССР, опубл. 29.07.1973). Основным недостатком данного прототипа является большой аппаратный объем.

Наиболее близким к заявленному техническому решению является параллельный вероятностный сумматор выполняющий операцию суммирования над параллельно поступающими данными, содержащий N-1 элементов задержки, разделяющие во времени вероятностные отображения слагаемых, схему «ИЛИ» на N входов, на входы которой поступают вероятностные отображения с задержкой относительно друг друга и накопительный счетчик, выполняющий операцию суммирования членов вероятностного отображения (Патент 171033, Российская Федерация, МПК G06F 19/00 Параллельный вероятностный сумматор, опубл. 17.05.2017, Бюл. №14.). Основным недостатком второго прототипа является недостаточное быстродействие т.к. вероятностное отображение суммы образуется со сжатием во времени и для восстановления исходного периода следования членов вероятностного отображения требуется введение дополнительных запоминающих элементов.

Задачей, на решение которой направлено заявляемое изобретение - повышение быстродействия выполнения операции сложении нескольких вероятностно представленных операндов при одновременном уменьшении аппаратного объема устройства в целом.

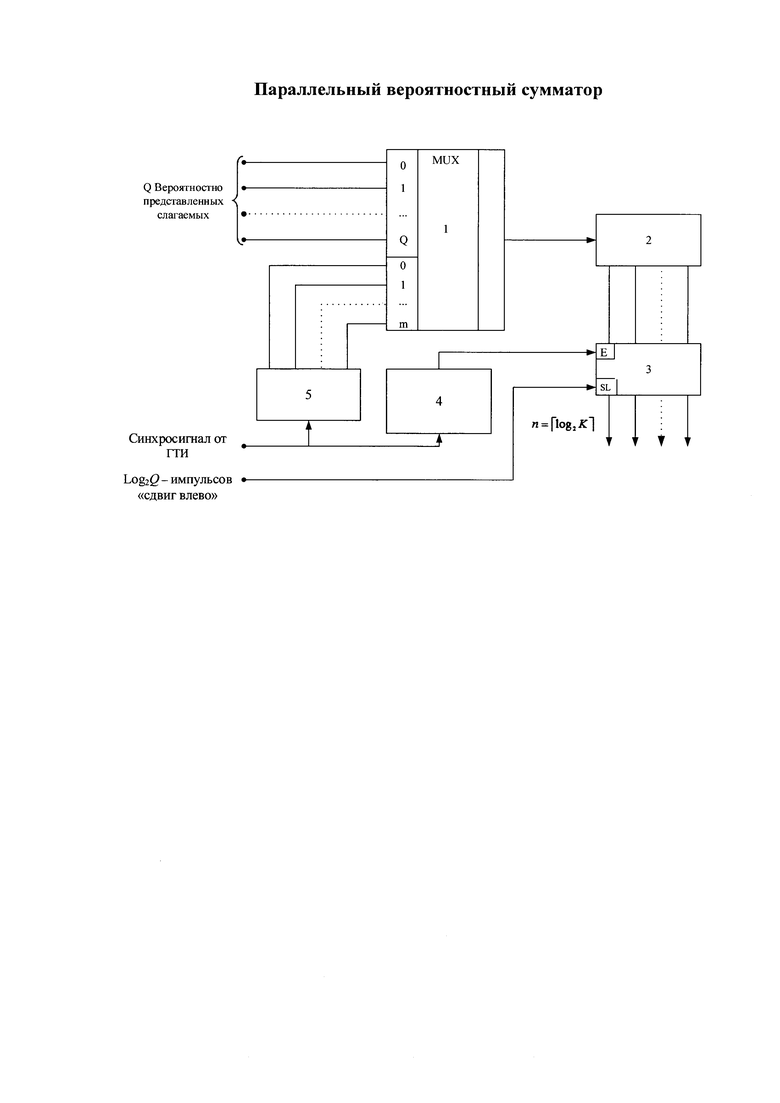

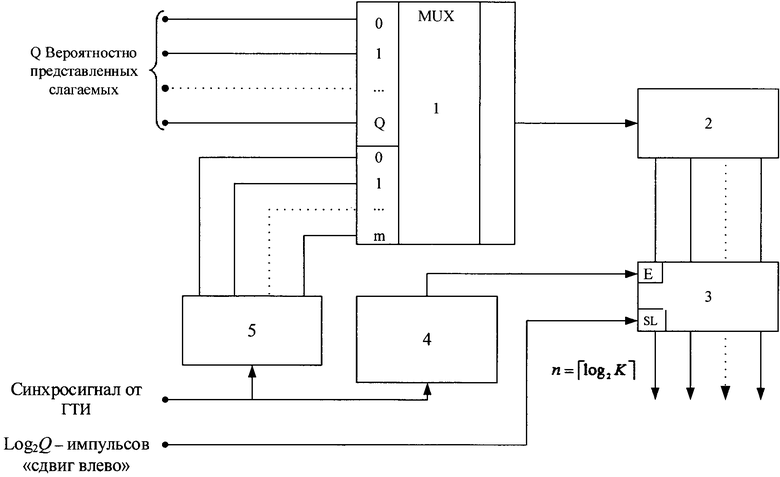

Данная задача решается за счет того, что заявленный параллельный вероятностный сумматор содержит n-разрядный счетчик результата, n-разрядный регистр результата, K-разрядный счетчик количества испытаний, генератор псевдослучайных равномерно распределенных чисел и мультиплексор на M=Log2Q управляющих входов, на которые поступает случайный равномерно распределенный сигнал с генератора псевдослучайных равномерно распределенных чисел, а на информационные входы подаются Q вероятностно представленных отображений слагаемых, выход мультиплексора подключен ко входу счетчика результата, который содержит n=[log2K] разрядов, где K - количество статистических испытаний, параллельные выходы которого нагружены на параллельные входы регистра результата аналогичной разрядности, на разрешающий вход которого подключен выход счетчика количества испытаний, на вход «сдвиг влево» регистра результата последовательно подается Log2Q импульсов сдвига, а на входы синхронизации счетчика количества испытаний и генератора псевдослучайных равномерно распределенных чисел подается синхросигнал с генератора тактовых импульсов, при этом выход регистра результата является выходом всей схемы.

Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является повышение быстродействия и одновременное снижение аппаратного объема устройства, сравнительно с прототипами, достигаемое путем замены схемы прототипов на схему, содержащую: n-разрядный счетчик результата, n-разрядный регистр результата, K-разрядный счетчик количества испытаний, генератор псевдослучайных равномерно распределенных чисел и мультиплексор на Log2Q управляющих входов.

Сущность изобретения поясняется чертежом, на котором изображена схема параллельного вероятностного сумматора, в состав которой входят:

1 - мультиплексор (MUX);

2 - счетчик результата (СчР);

3 - регистр результата (РгР);

4 - счетчик количества испытаний (СчКИ);

5 - генератор псевдослучайных равномерно распределенных чисел (ГПРРЧ).

Работу параллельного вероятностного сумматора можно рассматривать как работу «переключателя», который в тактовые моменты времени случайным образом подключает к выходу одну из входных шин. Получить такой «переключатель» можно, подавая случайные числа, представленные в параллельном позиционном коде, на информационные входы мультиплексора. Тогда значение логической функции дизъюнкции на выходе мультиплексора в j-й момент времени будет равно:

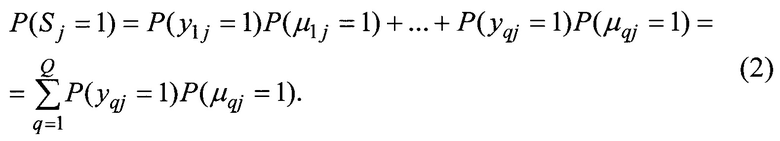

где μqj - значение логической переменной (бита унитарного кода) на управляющем входе мультиплексора.

Определим вероятность того, что Sj примет единичное значение по формуле:

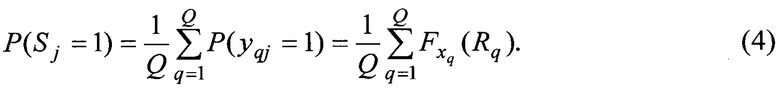

В случае если случайный сигнал на управляющих входах мультиплексора равномерен:

и выражение (2) приобретает вид:

При линейном вероятностном преобразовании  выражение (4) упростится и будет иметь вид:

выражение (4) упростится и будет иметь вид:

Из выражения (5) следует:

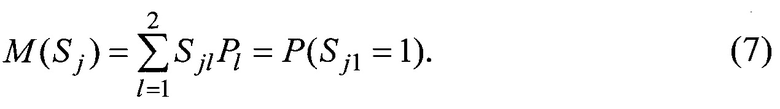

Для определения P(Sj=1) найдем МО случайной величины Sj, которая может принимать только два возможных значения - 0 или 1

В качестве оценки МО (7), с учетом следствия из теоремы Чебышева, примем:

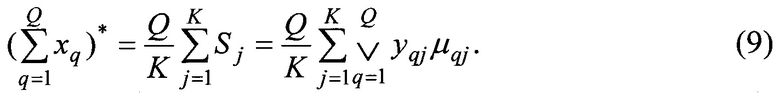

Окончательное выражение для вычисления суммы (5) вероятностных отображений с учетом (8) имеет вид:

Суть предложенного метода параллельного вероятностного суммирования заключается в выполнении параллельной операции арифметического сложения вероятностно представленных операндов, при котором сумматор можно рассматривать как «переключатель», который в тактовые моменты времени случайным образом подключает к выходу одну из входных шин, что позволяет значительно уменьшить аппаратный объем устройства в сравнении с первым прототипом, либо значительно ускорить получение результата в сравнении со вторым прототипом.

Работает устройство следующим образом. На информационные входы мультиплексора в последовательном коде побитно подаются вероятностно представленные слагаемые. В свою очередь, адресные входы мультиплексора подключены к ГПРРЧ, благодаря чему в каждый такт с выхода мультиплексора на СчР будет подаваться одно из K значений вероятностного отображения слагаемого, номер которого в позиционном коде, в данный такт, сгенерировано ГПРРЧ. СчКИ подсчитывает количество статистических испытаний и при достижении К испытаний выдает разрешающий сигнал для записи значения из СчР в РгР. После чего, для получения результата выполнения операции суммирования над Q вероятностно представленными операндами в двоичном позиционном коде необходимо подать на РгР Log2Q сигналов «сдвиг влево».

Таким образом для восстановления результата в классическую цифровую форму необходимо после проведения К испытаний переписать содержимое СчР в РгР и выполнить в РгР операцию «сдвиг влево» на Log2Q разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫЙ КОД - ВЕРОЯТНОСТНОЕ ОТОБРАЖЕНИЕ | 2017 |

|

RU2660831C1 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| ИМИТАТОР ДЖИТТЕРА | 2005 |

|

RU2303852C2 |

| N-СВЯЗНЫЙ МАРКОВСКИЙ ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2024 |

|

RU2841349C1 |

| ЦИФРОВОЙ ИМИТАТОР СЛУЧАЙНЫХ СИГНАЛОВ | 2019 |

|

RU2718417C1 |

| Устройство для определения законов распределения вероятностей | 1984 |

|

SU1188753A2 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| ВЫЧИСЛИТЕЛЬ ЭКСТРОПОЛИРОВАННОЙ КООРДИНАТЫ И СКОРОСТИ ЕЁ ИЗМЕНЕНИЯ ПО МЕТОДУ НАИМЕНЬШИХ КВАДРАТОВ | 2018 |

|

RU2713627C1 |

Изобретение относится к области автоматики и измерительной техники. Технический результат направлен на расширение арсенала средств того же назначения. Параллельный вероятностный сумматор включает n-разрядный счетчик результата, n-разрядный регистр результата, K-разрядный счетчик количества испытаний, генератор псевдослучайных равномерно распределенных чисел и мультиплексор на M=Log2Q управляющих входов, на которые поступает случайный равномерно распределенный сигнал с генератора псевдослучайных равномерно распределенных чисел, а на информационные входы подаются Q вероятностно представленных отображений слагаемых, выход мультиплексора подключен ко входу счетчика результата, параллельные выходы которого нагружены на параллельные входы регистра результата аналогичной разрядности, на разрешающий вход которого подключен выход счетчика количества испытаний, на вход «сдвиг влево» регистра результата последовательно подается Log2Q импульсов сдвига, а на входы синхронизации счетчика количества испытаний и генератора псевдослучайных равномерно распределенных чисел подается синхросигнал с генератора тактовых импульсов, при этом выход регистра результата является выходом всей схемы. 1 ил.

Параллельный вероятностный сумматор, характеризующийся тем, что содержит n-разрядный счетчик результата, n-разрядный регистр результата, K-разрядный счетчик количества испытаний, генератор псевдослучайных равномерно распределенных чисел и мультиплексор на M=Log2Q управляющих входов, на которые поступает случайный равномерно распределенный сигнал с генератора псевдослучайных равномерно распределенных чисел, а на информационные входы подаются Q вероятностно представленных отображений слагаемых, выход мультиплексора подключен ко входу счетчика результата, который содержит n=[log2K] разрядов, где K - количество статистических испытаний, параллельные выходы которого нагружены на параллельные входы регистра результата аналогичной разрядности, на разрешающий вход которого подключен выход счетчика количества испытаний, на вход «сдвиг влево» регистра результата последовательно подается Log2Q импульсов сдвига, а на входы синхронизации счетчика количества испытаний и генератора псевдослучайных равномерно распределенных чисел подается синхросигнал с генератора тактовых импульсов, при этом выход регистра результата является выходом всей схемы.

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| US 6014684 A, 11.01.2000 | |||

| УСТРОЙСТВО для связи ПРОЛЕТНОГО РЕЗОНАТОРА | 0 |

|

SU171033A1 |

| ВЕРОЯТНОСТНЫЙ СУММАТОР ПАРАЛЛЕЛЬНОГО ТИПА | 0 |

|

SU409221A1 |

Авторы

Даты

2018-12-26—Публикация

2017-07-27—Подача