1

Изобретение относится к автоматике и вычислительной технике и может найти применение при обработке сигналов , представленных в кодовой и широтно-импульсной формах при вьадаче результатов вычислений в кодовой и частотно-импульсной формах.

Известно множительно-делительное устройство, содержащее цифро-управляемые и широтно-управляемые проводимости, образующие мостовую схему, в диагональ которой включен усилитель разбаланса, соединенный с упргшляюсшм генератором импульсов и с цифровым генератором кодов Ц.

Недостатками устройства являются пониженная точность вычислений, отсутствие представлениярезультата в частотно-импульсной форме и неоднородность элементной базы.

Известно также множительно-делительное устройство, содержащее реверсивный счетчик, суммирующий и вычитающий входы которого подключены к выходам первого и второго элементов И, а выходы разрядов подключены через последовательно соединенные регистр памяти и преобразователь код-напряжение к входу ге- нератора управляемой частоты, выход

которого соединен с выходом устройства и с первым входом второго элемента И, второй вход которого и пер вый зкоя первого элемента И подключены к входу делителя и входу первого сомножителя, представленных в широтно-импульсной форме 12. : Недостатками устройства являются пониженная надежность, отсутствие

® представления результате в кодовойформе и неоднородность элементной ба зы.

Наиболее близким к предлагаемсжу является множительно-делительное

15 устройство, содержащее реверсивный двоичный счетчик, суммирующий вход которого соединен с выходом первого элемента И, внчитаюиий вход, - с выходом второго элемента И, а выходы

20 разрядов подключены к кодовому выходу устройства и к кодовому входу первого двоичного умиоямтеля, соединенного частотным входом с шииой опорной частоты, а выходом - с частотным выходом устройства и первым входом первого логического триггерного кольца, подключенного вторым входом к входу делителя, а выходом

к первсму входу второго элемента И,

30 причем первый зхоя первого элемента И соединен с выходом второго логического триггерного кольца, подключенного входами к входам сомножителей делимого 3.

Недостатком .данного устройства является сложность реализации при рвработке сигналов, представленных в широтно-импульсной и кодовой формах, что обусловлено необходимостью введения соответствующих преобразую( блоков, приводящего к дополнительному понижению точности и быстродействия.

Цель изобретения - упрощение устройства при обработке сигналов , пред ставленных в широтио-импульсноп и ко,дрвой формах.

Поставленная цель достигается тем что множительно-делительное устройство, содержащее реверсивный двоичный счетчик, сумглирующий вход которого соединен с выходом первого элемента, И, вычитающий вход - с выходом второго элемента И, а выходы разрядов подключены к кодовому выходу устройства и к кодовому входу первого двоичного умножителя, соединенного частотным входом с шиной опорной частоты, а выходом - с частотным выходом устройства, дополнительно содержит второй двоичный умножитель, подключенный кодовым входом к входу кода первого сомножителя делимого, частотным входом - к шине опорной частоты, а выходом - к первому входу первого элемента И, соединенного вторым ВХОДОМ с входом второго ;сомножителя делимого, представленного в широтно-импульсной форме, а выход первого двоичного умножителя соединен с первым входом второго элемента И, подключенного втор«лм входом к входу делителя, представленного в широтно-импульсной форме.

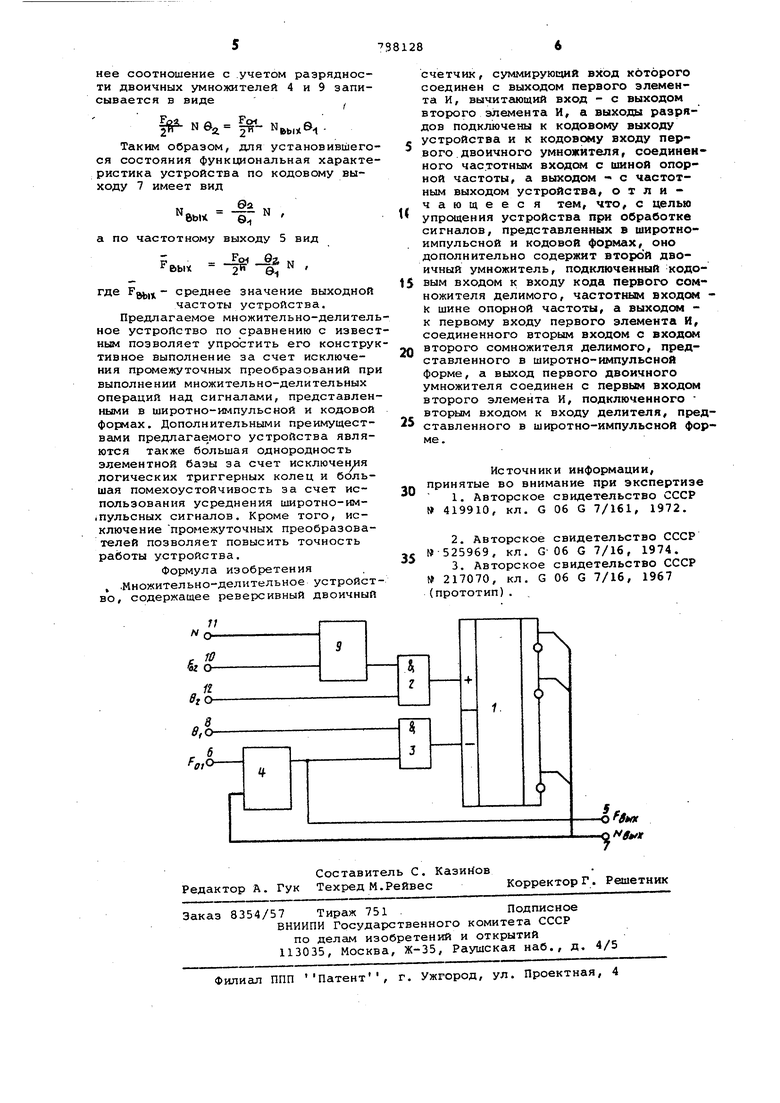

На чертеже изображена блок-схема множительно-делительного устройства.

Устройство содержит реверсивный двоичный счетчик 1, суммирующий вход которого подключен к выходу первого элемента И 2, вычитающий вход - к выходу второго элемента И 3, а выхо.ды разрядов - к кодовому входу пер;вого двоичного умножителя 4. Умножитель 4 соединен выходок с частотным выходом 5 устройства и с первым входом второго элемента И 3 и подключен частотным входом к шине 6 опорной частоты 1,. Выхода разрядов счетчика

Iсоединены с кодовым выходом 7 устройства. Второй вход второго элемента И 3 подключен к входу 8 делителя Q/1 , представленного в широтно-импульсной форме. Частотный и кодовый входы второго двоичного умножителя

9соединены соответственно с шиной

10опорной частоты FQ и с входом

IIкода N первого сомножителя делимого. Выход умножителя 9 подключен к первому входу первого элемента И 2, соединенного вторым входом с входом 12 второго сомножителя в делимого, представленного в широтно-импульсной форме.

Принцип действия множительно-делительного устройства основан на широтной модуляции частотно-импульсных последовательностей и их автоматической компенсации с помощью отрицательной обратной связи при усреднении формируемых неравномерных импульсных потоков.

Устройство работает следующим образом.

Пусть в начальный момент времени счетчик 1 обнулен, на вход 11 устройства подается двоичный код N, на входы 8 и 12 - широтно-импульсные сигналы 0 и 0i , а на шины б и 10 - опорные импульсные последовательности FO FQ2.f сдвинутые между собой во времени для обеспечения нормальной работы реверсивного счетчика 1. Первый же импульс, появившийся под воздействием кода W на выходе двоичного умножителя 9 в течение интервала времени отпирания элемента И 2 скгнсшом 02. проходит через элемент И 2 и записывается в ре версивный счетчик 1. Двоичный умножитель 4 начинает вырабатывать импульсную последовательность, так как управляющий им код с выхода счетчика 1 становится отличным от нуля. В течение интервала времени отпирания элемента И 2 сигналом 9у на суммирующий вход счетчика 1 подается импульсная последовательность, определяющая кодом N,a на вычитающий вход счетчика 1 в течение интервала времени отпирания элемента И 3 сигналом 0-1 - импульсная последовательность, определяемая выходным кодом NUJ,счетчика 1. Таким образом, с помо1чью элементов И 2 и 3 выполняется широтно-импульсная модуляция последовательностей импульсов, поступающих на входы счетчика 1 в соответствии с текущими Длительностями периодических широтно-импульсных сигналов & и &3. ,

Вследствие наличия отрицательной обратной связи в устройстве устанавливается режим динамического равновесия, характеризующийся (при пренебрежении изменениями выходного кода Ngy счетчика 1, имеющего достаточную разрядность) равенством количества импульсов, приходящих на суммирующий u.N и на вычитающий дМвходы реверсного счетчика 1 в течение периода широтно-импульсной модуляции, т.е.

uN+ uN или F.. F,

где F, F - средние значения частот импульсных последовательностей на суммирующем и вычитающем входах 65 счетчика 1 соответственно. Послед

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2008 |

|

RU2389065C1 |

| Устройство для перемножения двух частотно-импульсных сигналов | 1979 |

|

SU920723A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2222042C2 |

| Множительно-делительное устройство | 1987 |

|

SU1451732A2 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| Широтно-импульсный преобразователь | 2018 |

|

RU2683180C1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1361549A1 |

| Устройство для воспроизведения функций | 1977 |

|

SU703825A1 |

Авторы

Даты

1980-12-15—Публикация

1977-12-26—Подача