Изобретение относится к радиоэлектронике и может быть использовано в качестве операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1-2], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения ОУ, а также в драйверах быстродействующих аналого-цифровых преобразователей.

В современной радиоэлектронной аппаратуре находят применение серийные операционные усилители 154УД3, HA2520, HA5190, OP90, AD797, AD8631, AD8632, AD817, HA-2500, 140УД30, OPA42, в т.ч. на входных биполярных p-n-p [3-25], входных биполярных n-p-n [26-42] и входных полевых [43-55] транзисторах, выполненные на основе архитектуры «перегнутого» каскода. На данные схемотехнические решения выдано более 500 патентов в разных странах мира, например, [3-55]. Таким образом, ОУ на «перегнутых» каскодах являются одним из базовых функциональных узлов современной аналоговой микроэлектроники, в т.ч. дискретно-аналоговых (SC) фильтров [1,2]. Его основное достоинство – расширенный частотный диапазон, а также эффективное использование напряжения питания. Однако, в данном классе известных ОУ [3-55] не решаются проблемы существенного повышения максимальной скорости нарастания выходного напряжения (SR).

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту US 5.420.542, fig. 1A, 1995 г. ОУ-прототип содержит (фиг.1) входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора связан с первой 9 шиной источника питания через первый 10 токостабилизирующий двухполюсник, эмиттер второго 7 выходного транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1 и соединен с первой 9 шиной источника питания через второй 11 токостабилизирующий двухполюсник, коллектор первого 6 выходного транзистора подключен ко входу токового зеркала 12, согласованного со второй 13 шиной источника питания, выход которого связан с коллектором второго 7 выходного транзистора, входом буферного усилителя 14 и корректирующим конденсатором 15.

Существенный недостаток известного ОУ фиг. 1, также как и сотен других операционных усилителей данного класса, состоит в том, что в этой архитектуре существует нежелательная передача входного сигнала через паразитную емкость коллектор-база входного транзистора в высокоимпедансный узел Σ1. Это существенно ухудшает фазо-частотные характеристики ОУ и отрицательно сказывается на его запасе устойчивости по фазе [59].

Кроме этого, максимальный выходной ток «перегнутого» каскода в известном ОУ фиг. 1 при режиме динамической перегрузки входного каскада 1 жестко связан с токами первого 10 и второго 11 токостабилизирующих двухполюсников. Это не позволяет осуществить быстрый перезаряд корректирующего конденсатора 15 (Ск=С15), обеспечивающего устойчивость схемы, что ограничивает максимальную скорость нарастания выходного напряжения в ОУ данного класса [56-58].

Основная задача предлагаемого изобретения состоит в уменьшении влияния паразитной емкости коллектор-база входных транзисторов ОУ на фазо-частотную характеристику и запас устойчивости ОУ по фазе. Кроме этого, в заявляемой схеме обеспечиваются более высокие уровни выходного тока «перегнутого» каскода, перезаряжающего интегрирующий корректирующий конденсатор 15 (Ск=С15). В конечном итоге это повышает быстродействие ОУ в режиме большого сигнала, уменьшает время установления переходного процесса.

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора связан с первой 9 шиной источника питания через первый 10 токостабилизирующий двухполюсник, эмиттер второго 7 выходного транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1 и соединен с первой 9 шиной источника питания через второй 11 токостабилизирующий двухполюсник, коллектор первого 6 выходного транзистора подключен ко входу токового зеркала 12, согласованного со второй 13 шиной источника питания, выход которого связан с коллектором второго 7 выходного транзистора, входом буферного усилителя 14 и корректирующим конденсатором 15, предусмотрены новые элементы и связи – в схему введены первый 17 и второй 18 дополнительные транзисторы, эмиттеры которых объединены и связаны с первой 9 шиной источника питания через дополнительный источник опорного тока 19, коллектор первого 17 дополнительного транзистора связан со второй 13 шиной источника питания, база первого 17 дополнительного транзистора соединена с первым 2 входом входного дифференциального каскада 1, база второго 18 дополнительного транзистора соединена со вторым 3 входом входного дифференциального каскада 1, коллектор второго 18 дополнительного транзистора подключен ко входу дополнительного токового зеркала 20, согласованного со второй 13 шиной источника питания, а выход дополнительного токового зеркала 20 соединен с эмиттером первого 6 выходного транзистора, причем первый 4 токовый выход входного дифференциального каскада 1 связан с первой 9 шиной источника питания.

На чертеже фиг. 1 приведена схема операционного усилителя – прототипа.

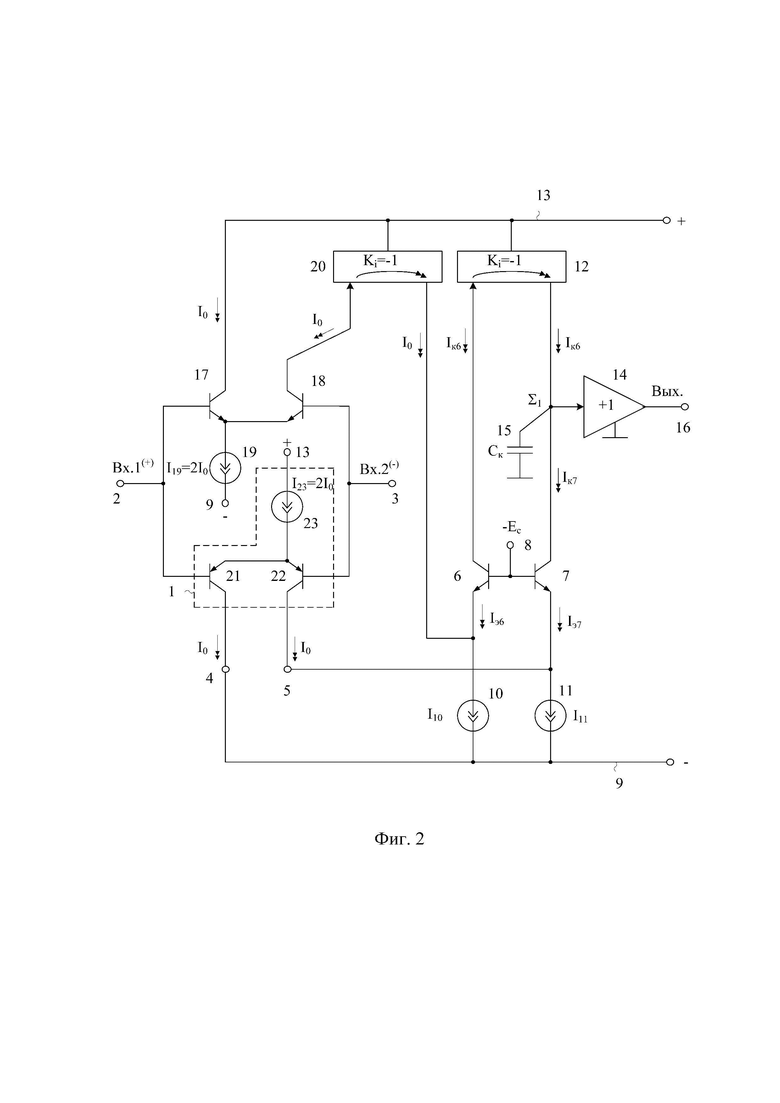

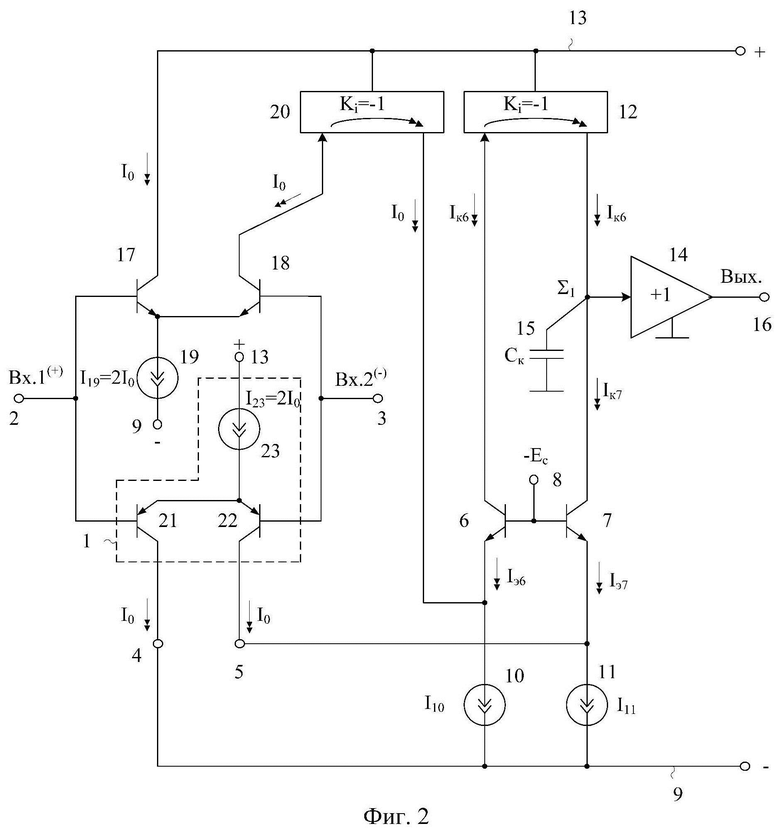

На чертеже фиг. 2 показана схема заявляемого ОУ в соответствии с п. 1 формулы изобретения, а на чертеже фиг. 3 - в соответствии с п. 2 формулы изобретения.

На чертеже фиг. 4 приведен статический режим быстродействующего ОУ фиг. 3 в среде LTspice при t=27 °C, Vcc= 10 В, Vee=-10 В, I1÷I2=200 мкА, I3÷I4=150 мкА, I5=100 мкА, R1=10 МОм, Cк=С15=2 пФ, Cк1=С27=0 пФ.

На чертеже фиг. 5 показана логарифмическая амплитудно-частотная характеристика (ЛАЧХ) ОУ фиг. 4 в среде LTspice при t=27 °C, Vcc= 10 В, Vee=-10 В, I1÷I2=200 мкА, I3÷I4=150 мкА, I5=100 мкА, R1=10 МОм, Cк=С15=2 пФ, Cк1=С27=0 пФ.

На чертеже фиг. 6 представлен переходный процесс переднего фронта заявляемого быстродействующего ОУ фиг. 4 в среде LTspice при t=27 °C, Vcc= 10 В, Vee=-10 В, I1÷I2=200 мкА, I3÷I4=150 мкА, I5=100 мкА, R1=10 МОм, Cк=С15=2 пФ и разных значения емкости вспомогательного корректирующего конденсатора 27 (Cк1=С27=0/50/100 пФ).

На чертеже фиг. 7 приведен переходный процесс заднего фронта заявляемого быстродействующего ОУ фиг. 4 в среде LTspice при t=27 °C, Vcc= 10 В, Vee=-10 В, I1÷I2=200 мкА, I3÷I4=150 мкА, I5=100 мкА, R1=10 МОм, Cк=С15=2 пФ и разных значения емкости вспомогательного корректирующего конденсатора 27 (Cк1=С27=0/50/100 пФ).

Быстродействующий операционный усилитель на основе «перегнутого» каскода фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора связан с первой 9 шиной источника питания через первый 10 токостабилизирующий двухполюсник, эмиттер второго 7 выходного транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1 и соединен с первой 9 шиной источника питания через второй 11 токостабилизирующий двухполюсник, коллектор первого 6 выходного транзистора подключен ко входу токового зеркала 12, согласованного со второй 13 шиной источника питания, выход которого связан с коллектором второго 7 выходного транзистора, входом буферного усилителя 14 и корректирующим конденсатором 15. В схему введены первый 17 и второй 18 дополнительные транзисторы, эмиттеры которых объединены и связаны с первой 9 шиной источника питания через дополнительный источник опорного тока 19, коллектор первого 17 дополнительного транзистора связан со второй 13 шиной источника питания, база первого 17 дополнительного транзистора соединена с первым 2 входом входного дифференциального каскада 1, база второго 18 дополнительного транзистора соединена со вторым 3 входом входного дифференциального каскада 1, коллектор второго 18 дополнительного транзистора подключен ко входу дополнительного токового зеркала 20, согласованного со второй 13 шиной источника питания, а выход дополнительного токового зеркала 20 соединен с эмиттером первого 6 выходного транзистора, причем первый 4 токовый выход входного дифференциального каскада 1 связан с первой 9 шиной источника питания.

В схеме фиг. 2 входной дифференциальный каскад 1 выполнен в частном случае на основе входных транзисторов 21, 22 и источнике опорного тока 23.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, в схему введены первый 24 и второй 25 вспомогательные транзисторы, эмиттеры которых объединены и подключены к первой 9 шине источника питания через вспомогательный токостабилизирующий двухполюсник 26 и параллельно ему включенный вспомогательный корректирующий конденсатор 27, причем база первого 24 вспомогательного транзистора соединена с эмиттером первого 6 выходного транзистора, база второго 25 вспомогательного транзистора соединена с эмиттером второго 7 выходного транзистора, коллектор первого 24 вспомогательного транзистора подключен ко входу буферного усилителя 14, а коллектор второго 25 вспомогательного транзистора соединен со входом токового зеркала 12.

Рассмотрим вначале работу ОУ на чертеже фиг.2.

За счет введения новых элементов и связей между ними в соответствии с п. 1 формулы изобретения в предлагаемом ОУ фиг. 2 исключается паразитная передача входного импульсного сигнала в высокоимпедансный узел Σ1 через емкость коллектор-база входного транзистора, что повышает запас устойчивости ОУ по фазе [59]. Данный положительный эффект объясняется подключением коллекторов транзисторов 17 и 21 и, следовательно, их паразитных емкостей коллектор-база к первой 9 и второй 13 шинам источников питания.

При введении вспомогательного корректирующего конденсатора 27 (Cк1=С27) в ОУ по п. 2 формулы изобретения максимальная скорость нарастания выходного напряжения SR(+) переднего фронта больше в 16,38 раза, чем при отсутствии этого конденсатора. При этом, SR(-) заднего фронта при наличии Cк1 больше в 13,65 раза, чем при его отсутствии. Данные выводы следуют из чертежей фиг. 6, фиг. 7 и таблицы 1.

Таблица 1 – Максимальная скорость нарастания выходного напряжения ОУ по п. 2 формулы изобретения (чертеж фиг. 4) при разных значениях емкости вспомогательного корректирующего конденсатора 27 (Ск1=С27)

переднего фронта ОУ фиг. 6, SR(+), В/мкс

заднего фронта ОУ фиг. 7, SR(-), В/мкс

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения замкнутого ОУ и запаса устойчивости по фазе.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. E. J. Wyers, "Accurate Geometric Programming-Compatible Slew Rate Modeling for Two-Stage Operational Amplifier Design Optimization," 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Shenzhen, China, 2022, pp. 185-189. doi: 10.1109/APCCAS55924.2022.10090335

2. J. Ramirez-Angulo and M. Holmes, "A simple technique to significantly enhance slew rate and bandwidth of one-stage CMOS operational amplifiers," 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 2002, pp. II-II. doi: 10.1109/ISCAS.2002.1011483

Входные ДК на pnp транзисторах ОУ с «перегнутым» каскодом:

1. Патент US 6448583, fig.4, fig.5, fig.6, 2002 г.

2. Патент US 5091701, fig.1, 1992 г.

3. Патент US 5420542, fig.1A, 1995 г.

4. Патент US 5389894, fig.1, 1995 г.

5. Патент US 7545213, fig. 2, 2009 г.

6. Патент US 5282242, fig.2, 1994 г.

7. Патент US 6696888, fig.17, 2004 г .

8. Патент US 4293824, fig.2, 1981 г.

9. Патент US 7411451, fig. 1, 2008 г.

10. Патент RU 2354041, fig.2, 2009 г.

11. Патент US 6501333, fig.1, 2002 г.

12. Патент US 6456162, fig. 3, 2002 г.

13. Патент US 6542030, fig.2, 2003 г.

14. Патент US 3979069, fig.2, 1976 г.

15. Патент RU 2331969, fig.1, 2008 г.

16. Патент EP 0 586251, fig.2, 1994 г.

17. Патент US 3979689, fig.2, 1976 г.

18. Патент US 4600893, fig.7, 1986 г.

19. Патент US 5418491, fig.2, 1995 г.

20. Патент US 4406990, fig.4, 1983 г.

21. Патент US 5422600, fig.2, 1995 г.

22. Патент US 6218900, fig.1, 2001 г.

23. Патентная заявка US 2006/0202762, fig.2, 2006 г.

Входные ДК на npn транзисторах ОУ с «перегнутым» каскодом:

24. Патент РФ 2310268, fig.1, fig.2, 2007 г.

25. Патент US 6529076, 2001 г.

26. Патент US 4600893, fig.6,1986 г.

27. Патент US 2009/0256634, fig.1, 2009 г.

28. Патент US 6734737, fig.7, 2004 г.

29. Патент US 6483382, fig.1, fig.2, 2002 г.

30. Патент US 6304143, fig.1, 2001 г.

31. Патент JP 2009201119 A, fig.1, fig.2, 2009 г.

32. Патент US 5786729, fig.1, fig.2, 1998 г.

33. Патент RU 2421884, fig.1, 2011 г.

34. Патент US 7005921, fig.1B, 2006 г.

35. Патент US 6965266, fig. 1, 2005 г.

36. Патентная заявка US 2008/0024224, fig.1, 2008 г.

37. Патент US 6300831, fig.1, fig. 2, 2001 г.

38. Патент US 6788143, fig. 2, 2004 г.

39. Патент US 4959622, fig.18, 1990 г.

40. Патент US 5327100, fig.2, 1994 г.

Входные ДК на полевых транзисторах ОУ с «перегнутым» каскодом:

41. Патент US 5734296, fig.3, 2008 г.

42. Патент US 4406990, fig.6, 1983 г.

43. Патент US 6580325, fig.35, fig.36, 2003 г.

44. Патент US 6788143, fig.1, fig.4, 2004 г.

45. Патент US 4829266, fig. 10, 1989 г.

46. Патент US 7898330, fig. 1, 2011 г.

47. Патент US 4387309, 1983 г.

48. Патент US 6084475, fig.1, 2000 г.

49. Патентная заявка US 2005/0001682, fig.3, 2005 г.

50. Патент US 6717474, fig.4, 2004 г.

51. Патент US 6018268, fig.1, 2000 г.

52. Патент US 6714076, fig.2, 2004 г.

53. Патент EP 1227580, fig. 1, 2002 г.

Монографии по теории ОУ:

56. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

57. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография / Н.Н.Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. – 222 с.

58. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. – Шахты: Изд-во ЮРГУЭС, 2006. – 231 с.

59. Операционные усилители для всех / Брюс Картер и Рон Манчини; пер. с англ. А.Н. Рабодзея. – М.: Додэка-XXI, 2011. – 544 с. : ил. – (Серия «Схемотехника). – Доп.тит.л.англ. – ISBN 978-5-94120-242-3, рис. 6.15-рис. 6.17

Серийные ОУ на «перегнутых» каскодах

154УД3, HA2520, HA5190, OP90, AD797, AD8631, AD8632, AD817, HA-2500, 140УД30, OPA42.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| Быстродействующий операционный усилитель на основе комплементарного "перегнутого" каскода | 2023 |

|

RU2813280C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2604684C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С «ПЕРЕГНУТЫМ» КАСКОДОМ КЛАССА АВ | 2022 |

|

RU2786512C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592429C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

Изобретение относится к радиоэлектронике. Технический результат: уменьшение влияния паразитной емкости коллектор-база входных транзисторов ОУ на фазочастотную характеристику и запас устойчивости ОУ по фазе. Для этого предложен операционный усилитель на основе «перегнутого» каскода, в схему которого введены первый (17) и второй (18) дополнительные транзисторы, эмиттеры которых объединены и связаны с первой (9) шиной источника питания через дополнительный источник опорного тока (19), коллектор первого (17) дополнительного транзистора связан со второй (13) шиной источника питания, база первого (17) дополнительного транзистора соединена с первым (2) входом входного дифференциального каскада (1), база второго (18) дополнительного транзистора соединена со вторым (3) входом входного дифференциального каскада (1), коллектор второго (18) дополнительного транзистора подключен ко входу дополнительного токового зеркала (20), согласованного со второй (13) шиной источника питания, а выход дополнительного токового зеркала (20) соединен с эмиттером первого (6) выходного транзистора, причем первый (4) токовый выход входного дифференциального каскада (1) связан с первой (9) шиной источника питания. 1 з.п. ф-лы, 7 ил., 1 табл.

1. Быстродействующий операционный усилитель на основе «перегнутого» каскода, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, первый (6) и второй (7) выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения (8), эмиттер первого (6) выходного транзистора связан с первой (9) шиной источника питания через первый (10) токостабилизирующий двухполюсник, эмиттер второго (7) выходного транзистора связан со вторым (5) токовым выходом входного дифференциального каскада (1) и соединен с первой (9) шиной источника питания через второй (11) токостабилизирующий двухполюсник, коллектор первого (6) выходного транзистора подключен ко входу токового зеркала (12), согласованного со второй (13) шиной источника питания, выход которого связан с коллектором второго (7) выходного транзистора, входом буферного усилителя (14) и корректирующим конденсатором (15), отличающийся тем, что в схему введены первый (17) и второй (18) дополнительные транзисторы, эмиттеры которых объединены и связаны с первой (9) шиной источника питания через дополнительный источник опорного тока (19), коллектор первого (17) дополнительного транзистора связан со второй (13) шиной источника питания, база первого (17) дополнительного транзистора соединена с первым (2) входом входного дифференциального каскада (1), база второго (18) дополнительного транзистора соединена со вторым (3) входом входного дифференциального каскада (1), коллектор второго (18) дополнительного транзистора подключен ко входу дополнительного токового зеркала (20), согласованного со второй (13) шиной источника питания, а выход дополнительного токового зеркала (20) соединен с эмиттером первого (6) выходного транзистора, причем первый (4) токовый выход входного дифференциального каскада (1) связан с первой (9) шиной источника питания.

2. Быстродействующий операционный усилитель на основе «перегнутого» каскода по п. 1, отличающийся тем, что в схему введены первый (24) и второй (25) вспомогательные транзисторы, эмиттеры которых объединены и подключены к первой (9) шине источника питания через вспомогательный токостабилизирующий двухполюсник (26) и параллельно ему включенный вспомогательный корректирующий конденсатор (27), причем база первого (24) вспомогательного транзистора соединена с эмиттером первого (6) выходного транзистора, база второго (25) вспомогательного транзистора соединена с эмиттером второго (7) выходного транзистора, коллектор первого (24) вспомогательного транзистора подключен ко входу буферного усилителя (14), а коллектор второго (25) вспомогательного транзистора соединен со входом токового зеркала (12).

| US 5420542 A1, 30.05.1995 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2008 |

|

RU2391768C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

Авторы

Даты

2024-01-11—Публикация

2023-10-09—Подача