Изобретение относится к радиоэлектронике и может быть использовано в качестве операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1-2], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения ОУ, а также в драйверах быстродействующих аналого-цифровых преобразователей.

В современной радиоэлектронной аппаратуре находят применение серийные микросхемы операционных усилителей 154УД3, HA2520, HA5190, OP90, AD797, AD8631, AD8632, AD817, HA-2500, 140УД30, OPA42 на биполярных p-n-p [3-25], биполярных n-p-n [26-42] и полевых [43-55] транзисторах, выполненные на основе архитектуры «перегнутого» каскода. На данные схемотехнические решения выдано более 500 патентов в разных странах мира, например, [3-55]. Таким образом, ОУ на «перегнутых» каскодах являются одним из базовых функциональных узлов современной аналоговой микроэлектроники, в т.ч. для SC-фильтров на переключаемых конденсаторах [1,2]. Их основное достоинство - расширенный частотный диапазон, а также эффективное использование напряжения питания. Однако, в данном классе известных ОУ [3-55] не решаются проблемы существенного повышения максимальной скорости нарастания выходного напряжения (SR).

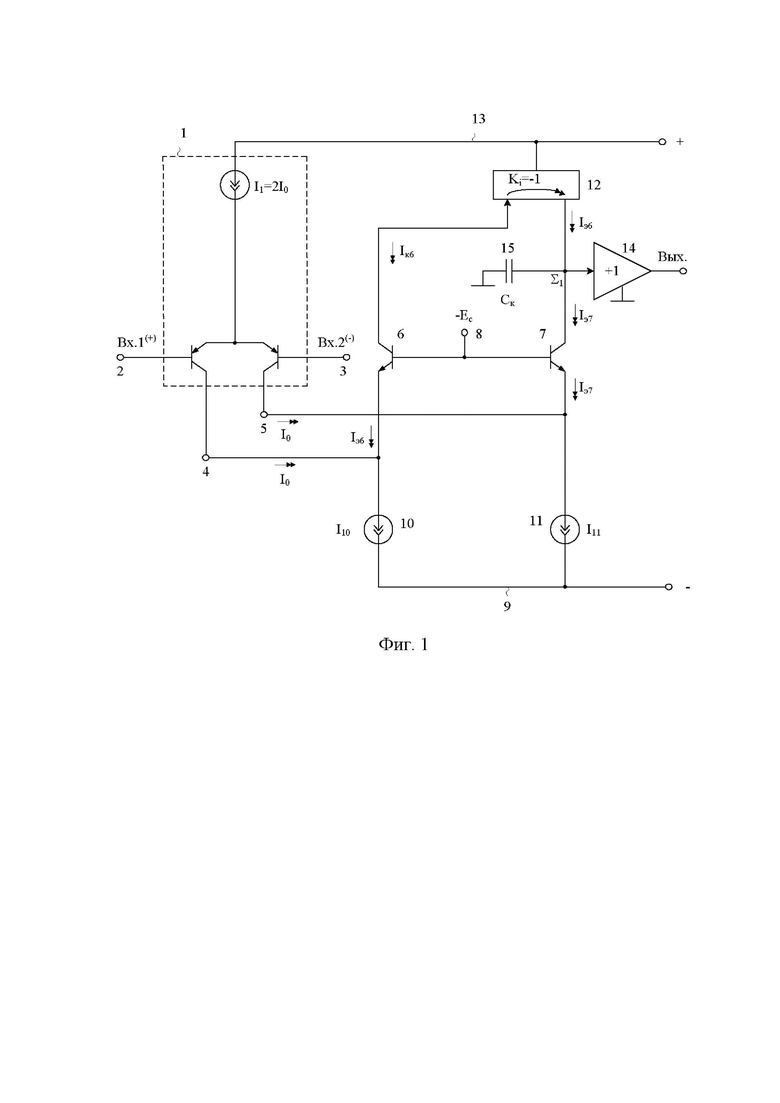

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту US 6.501.333, 2002 г. ОУ-прототип содержит (фиг.1) входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора соединен с первым 4 токовым выходом и связан с первой 9 шиной источника питания через первый 10 токостабилизирующий двухполюсник, эмиттер второго 7 выходного транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1 и соединен с первой 9 шиной источника питания через второй 11 токостабилизирующий двухполюсник, коллектор первого 6 выходного транзистора подключен ко входу токового зеркала 12, согласованного со второй 13 шиной источника питания, выход которого связан с коллектором второго 7 выходного транзистора, входом буферного усилителя 14 и корректирующим конденсатором 15.

Существенный недостаток известного ОУ фиг. 1 состоит в том, что максимальный выходной ток его «перегнутого» каскода (транзисторы 6, 7) в режиме динамической перегрузки входного каскада 1 жестко связан с токами первого 10 и второго 11 токостабилизирующих двухполюсников. Это не позволяет осуществить быстрый перезаряд корректирующего конденсатора 15 (Ск=С15), обеспечивающего устойчивость схемы, что ограничивает максимальную скорость нарастания выходного напряжения в ОУ данного класса.

Основная задача предполагаемого изобретения состоит в обеспечении более высоких уровней выходного тока «перегнутого» каскода, перезаряжающего во время фронта корректирующий конденсатор 15. В конечном итоге это повышает быстродействие ОУ фиг. 2 в режиме большого сигнала, уменьшает время установления переходного процесса.

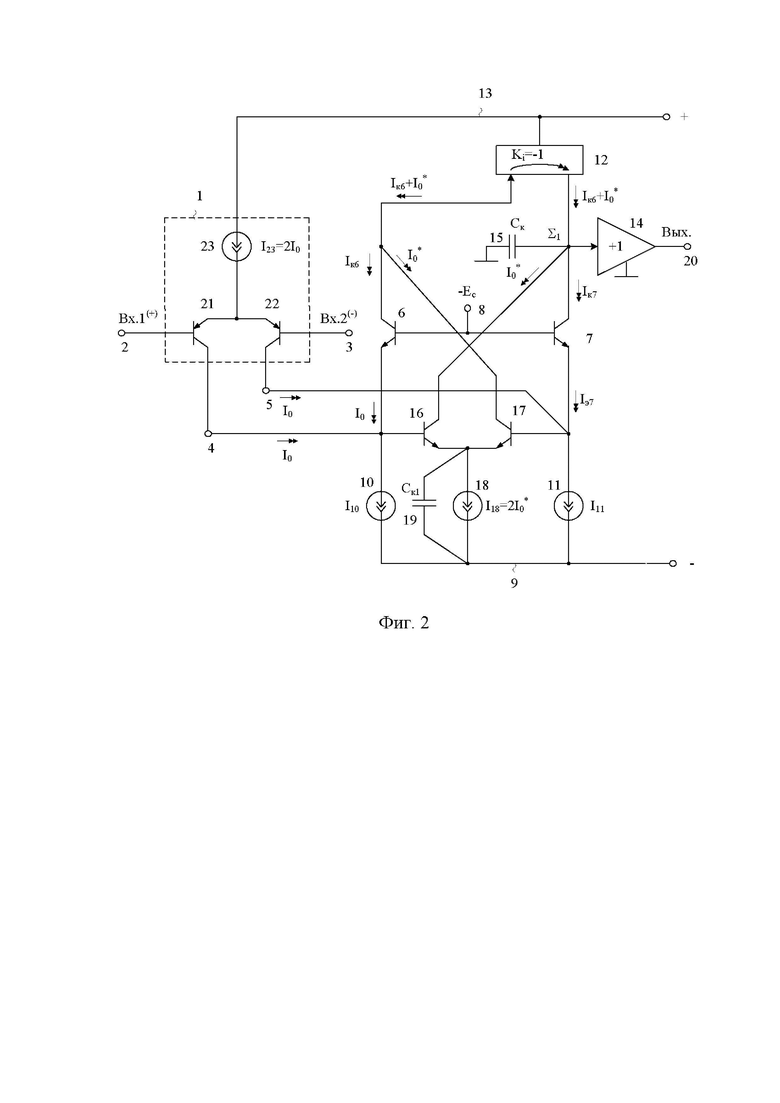

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора соединен с первым 4 токовым выходом и связан с первой 9 шиной источника питания через первый 10 токостабилизирующий двухполюсник, эмиттер второго 7 выходного транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1 и соединен с первой 9 шиной источника питания через второй 11 токостабилизирующий двухполюсник, коллектор первого 6 выходного транзистора подключен ко входу токового зеркала 12, согласованного со второй 13 шиной источника питания, выход которого связан с коллектором второго 7 выходного транзистора, входом буферного усилителя 14 и корректирующим конденсатором 15, предусмотрены новые элементы и связи - в схему введены первый 16 и второй 17 дополнительные транзисторы, эмиттеры которых объединены и подключены к первой 9 шине источника питания через вспомогательный токостабилизирующий двухполюсник 18 и параллельно ему включенный вспомогательный корректирующий конденсатор 19, причем база первого 16 вспомогательного транзистора соединена с эмиттером первого 6 выходного транзистора, база второго 17 вспомогательного транзистора соединена с эмиттером второго 7 выходного транзистора, коллектор первого 16 вспомогательного транзистора подключен ко входу буферного усилителя 14, а коллектор второго 17 вспомогательного транзистора соединен со входом токового зеркала 12.

На чертеже фиг. 1 приведена схема операционного усилителя - прототипа.

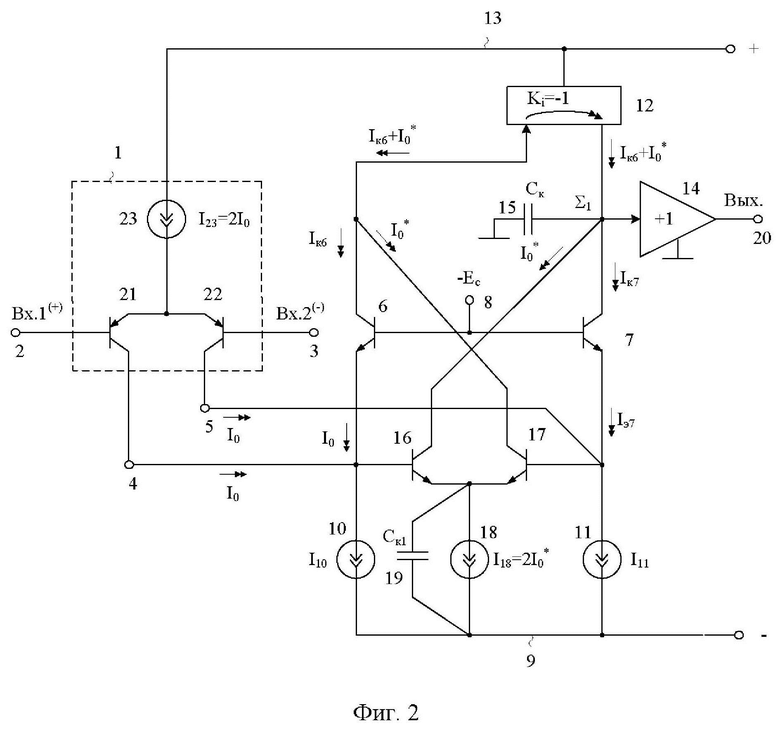

На чертеже фиг. 2 показана схема заявляемого ОУ в соответствии с п. 1 формулы изобретения.

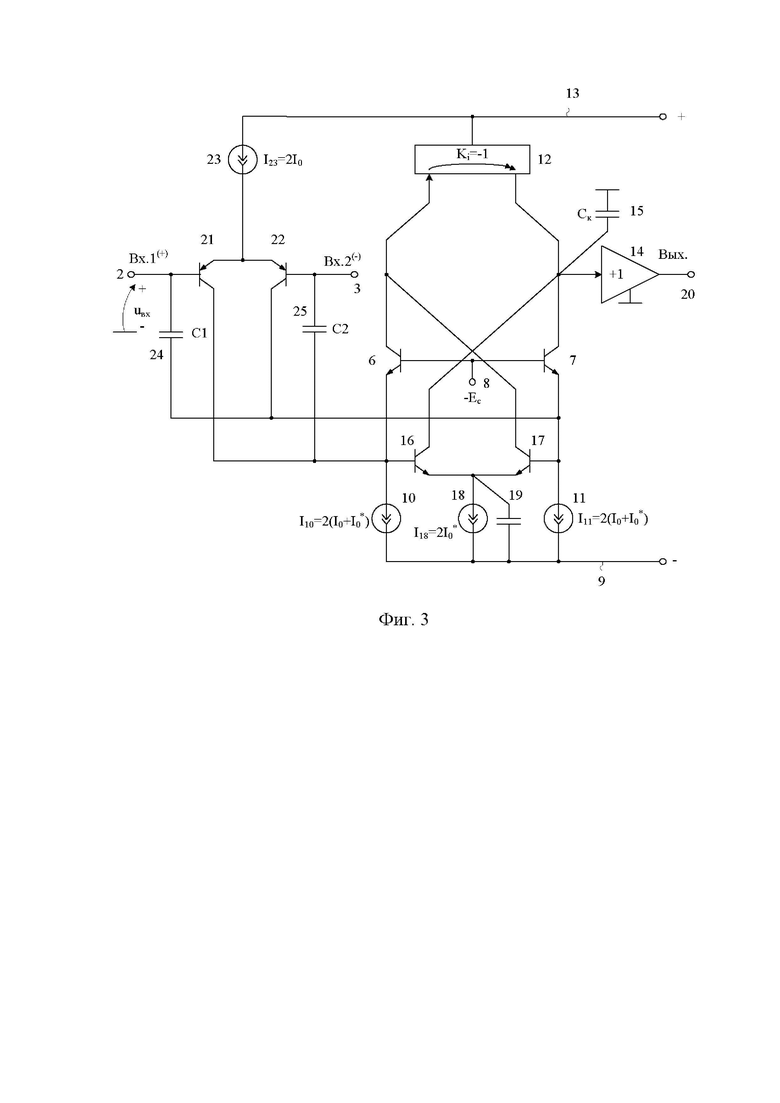

На чертеже фиг. 3 приведена схема заявляемого ОУ в соответствии с п. 2 формулы изобретения.

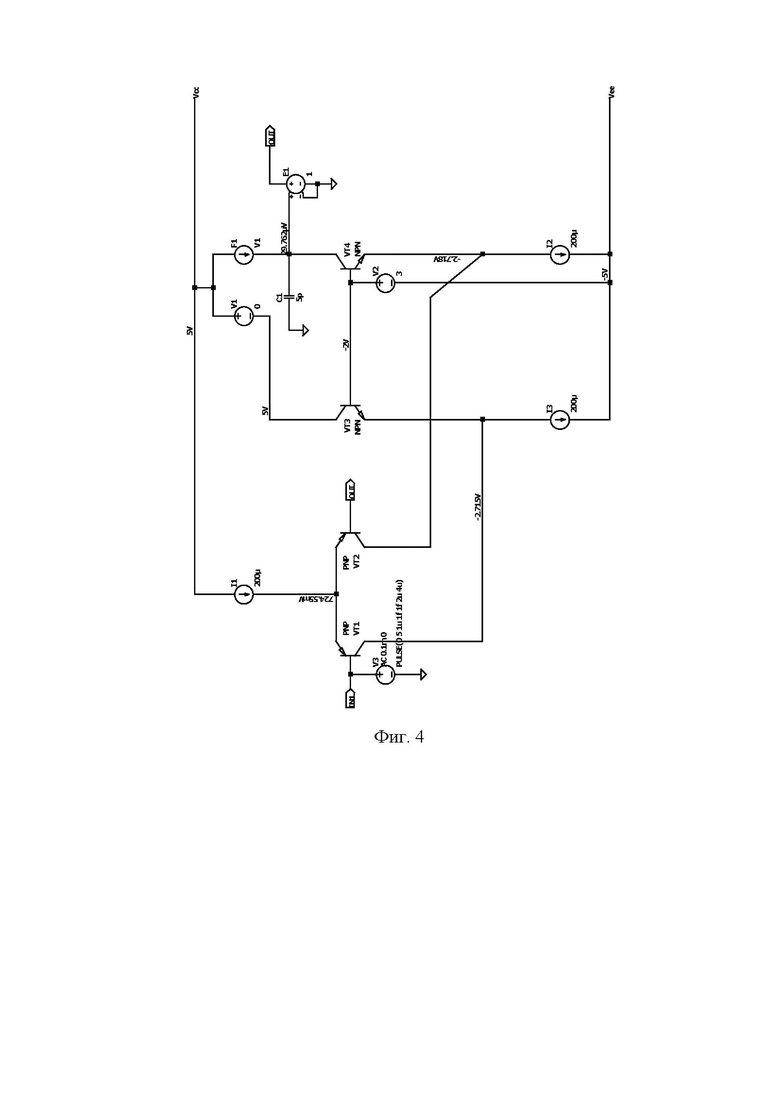

На чертеже фиг. 4 представлен статический режим ОУ - прототипа фиг. 1 в среде LTspice на моделях транзисторов базового матричного кристалла MH2XA031_25.01.21.lib при t=27 °C, Vcc= 5 В, Vee=-5 В, I1÷I3=200 мкА, Ск= С15=5 пФ.

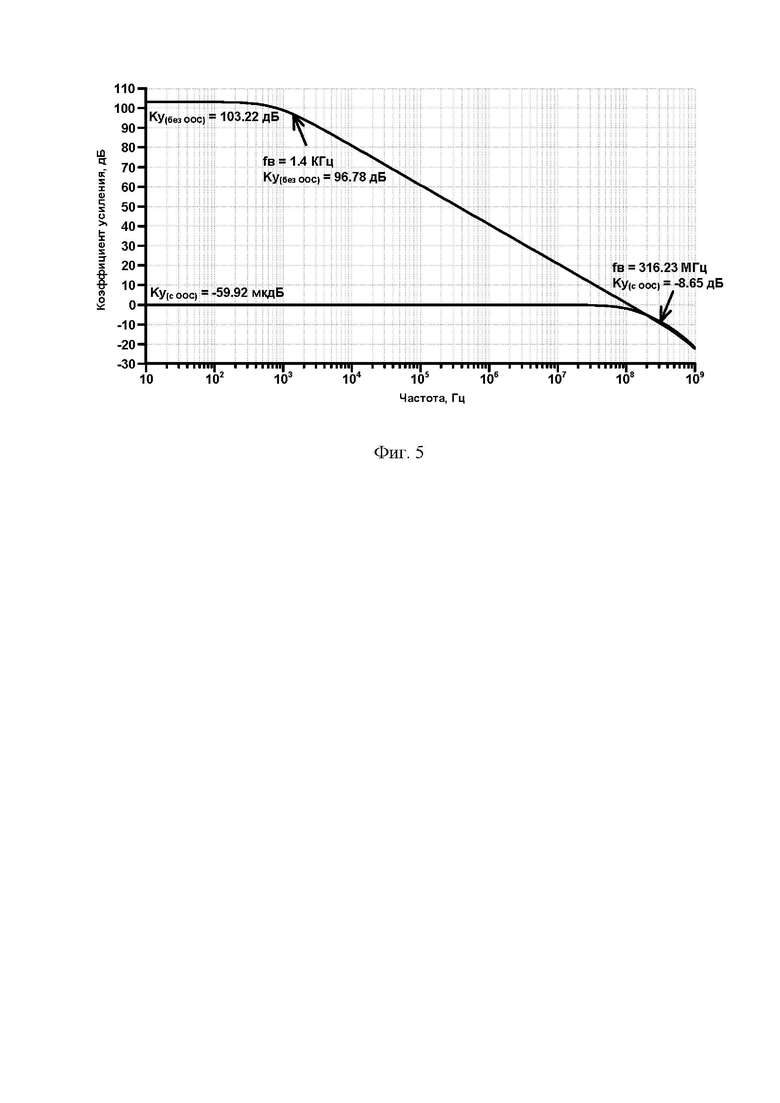

На чертеже фиг. 5 показана логарифмическая амплитудно-чатотная характеристика (ЛАЧХ) ОУ - прототипа фиг. 4 в среде LTspice при t=27 °C, Vcc=5 В, Vee=-5 В, I1÷I3=200 мкА, Ск=С15=5 пФ.

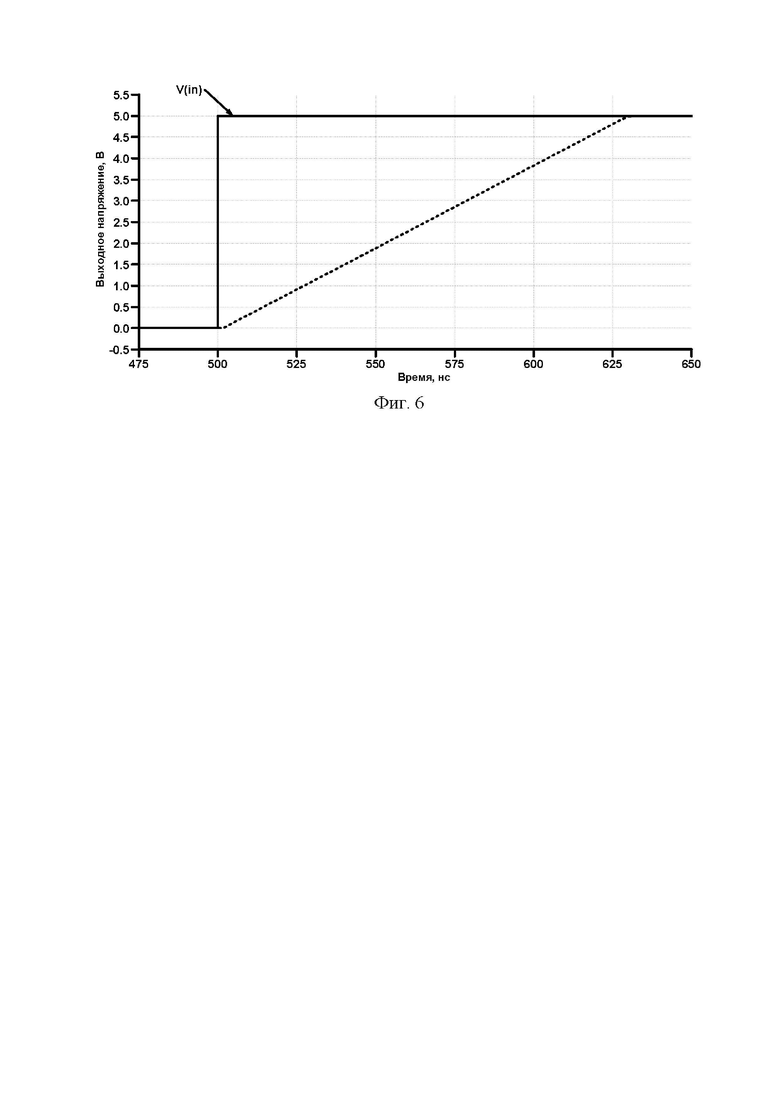

На чертеже фиг. 6 приведен переходный процесс переднего фронта ОУ - прототипа фиг. 4 в среде LTspice при t=27°C, Vcc=5 В, Vee=-5 В, I1÷I3=200 мкА, Ск=С15=5 пФ. Из данного графика следует, что ОУ-прототип имеет сравнительно небольшие значения SR(+)≈39.9 В/мкс.

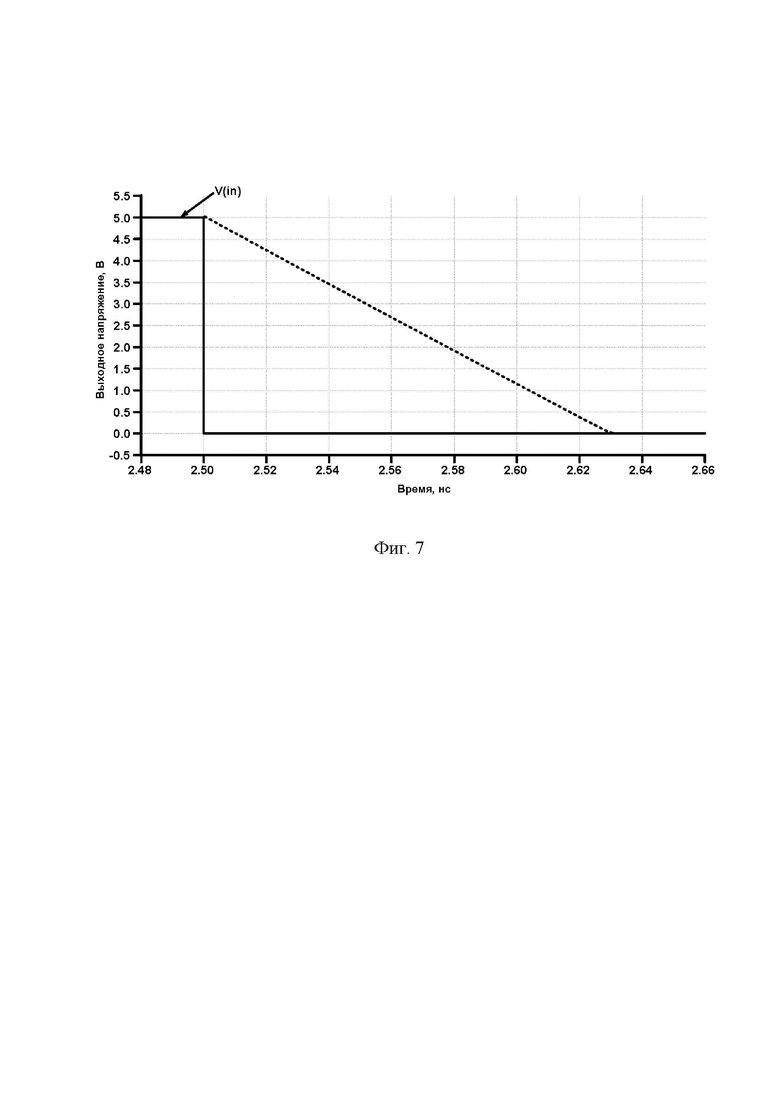

На чертеже фиг. 7 представлен переходный процесс заднего фронта ОУ - прототипа фиг. 4 в среде LTspice при t=27°C, Vcc=5 В, Vee=-5 В, I1÷I3=200 мкА, Ск=С15=5 пФ. Из данного графика следует, что ОУ-прототип имеет сравнительно небольшие значения SR(-)≈38.6 В/мкс.

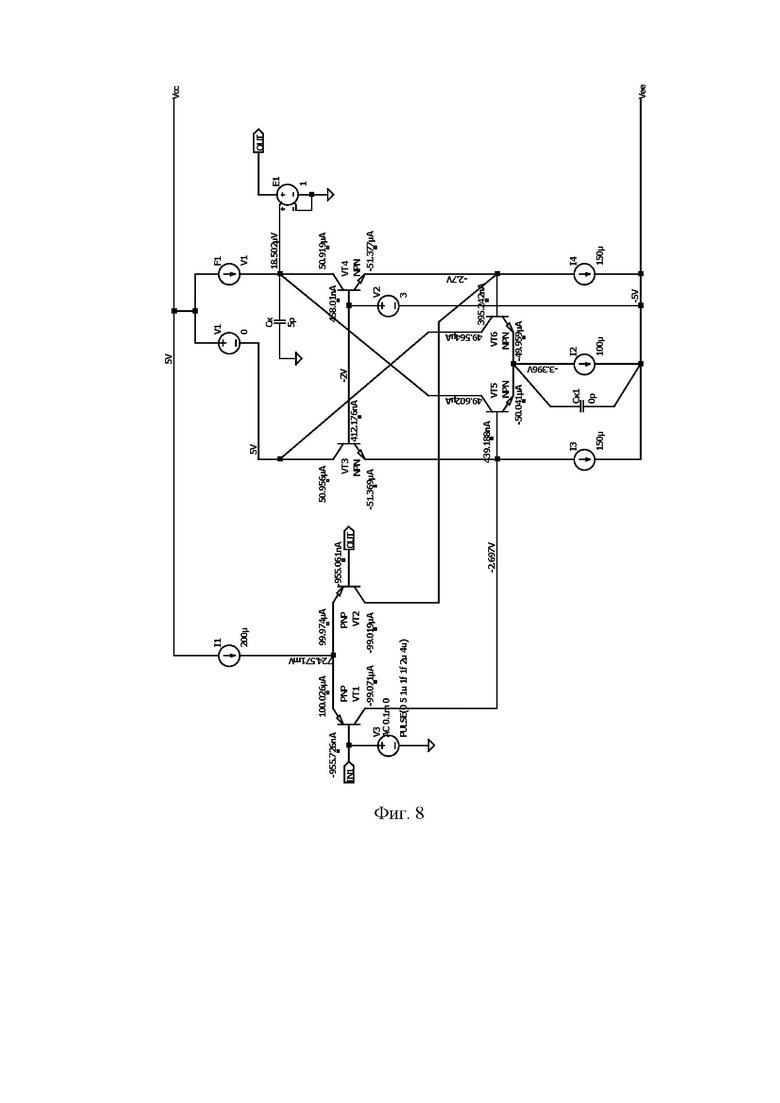

На чертеже фиг. 8 показан статический режим заявляемого быстродействующего ОУ фиг. 2 в среде LTspice на моделях транзисторов базового матричного кристалла MH2XA031_25.01.21.lib при t=27 °C, Vcc= 5 В, Vee=-5 В, I1=200 мкА, I2=100 мкА, I3÷I4=200 мкА, Ск=С15=5 пФ.

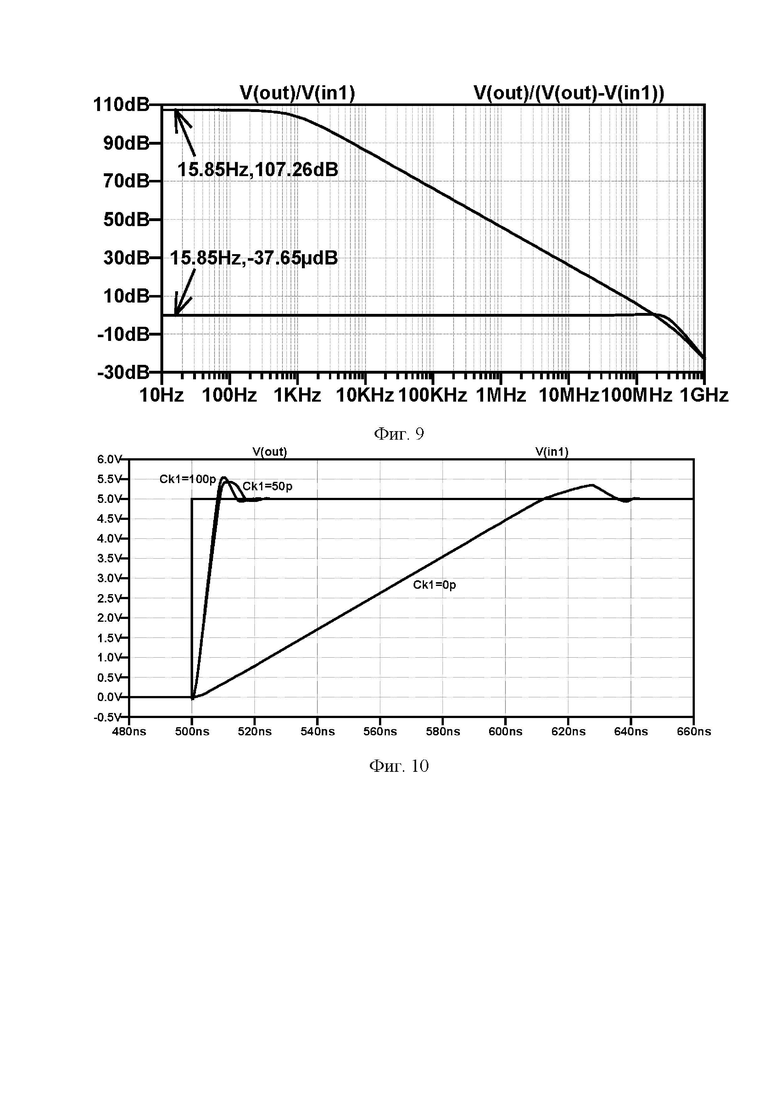

На чертеже фиг. 9 приведена ЛАЧХ быстродействующего ОУ фиг. 8 в среде LTspice при t=27 °C, Vcc= 5 В, Vee=-5 В, I1=200 мкА, I2=100 мкА, I3÷I4=200 мкА, Ск=С15=5 пФ.

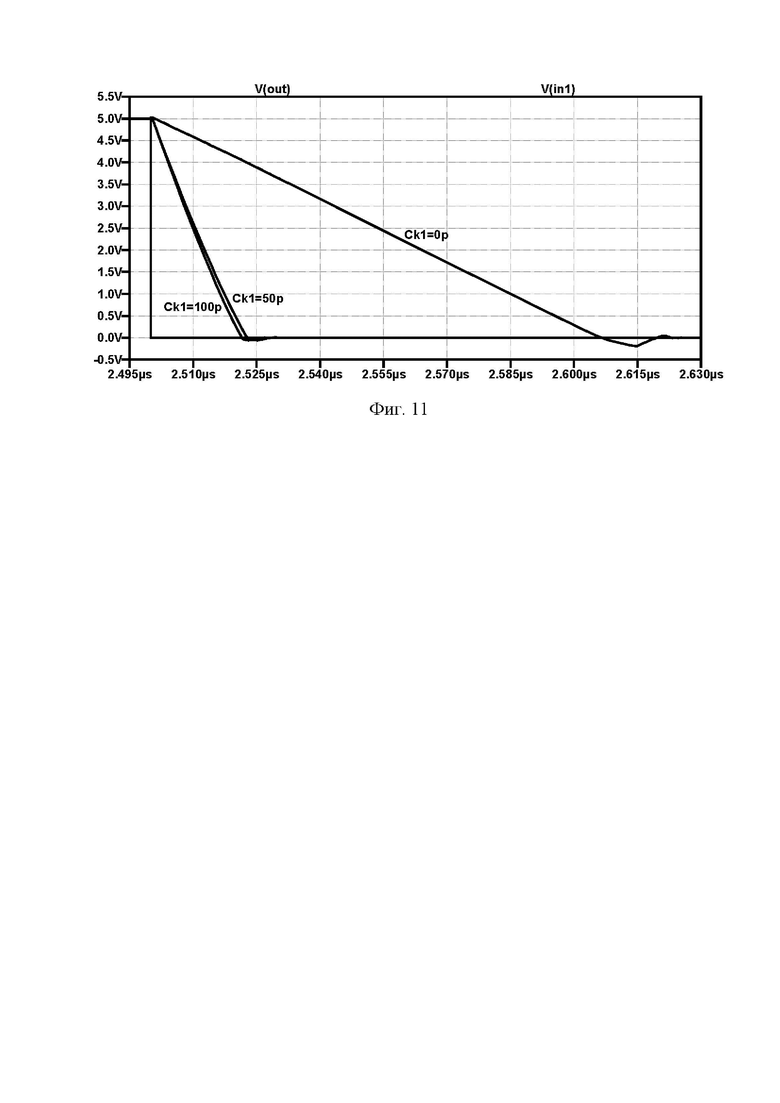

На чертеже фиг. 10 представлен переходный процесс переднего фронта предлагаемого быстродействующего ОУ фиг. 8 в среде LTspice при t=27 °C, Vcc= 5 В, Vee=-5 В, I1=200 мкА, I2=100 мкА, I3÷I4=200 мкА, Ск=С15=5 пФ и разных значениях емкости вспомогательного корректирующего конденсатора 19 (Ск1=С19=0/50/100 пФ).

На чертеже фиг. 11 показан переходный процесс заднего фронта быстродействующего ОУ фиг. 8 в среде LTspice при t=27 °C, Vcc=5 В, Vee=-5 В, I1=200 мкА, I2=100 мкА, I3÷I4=200 мкА, Ск=С15=5 пФ и разных значениях емкости вспомогательного корректирующего конденсатора 19 (Ск1=С19=0/50/100 пФ).

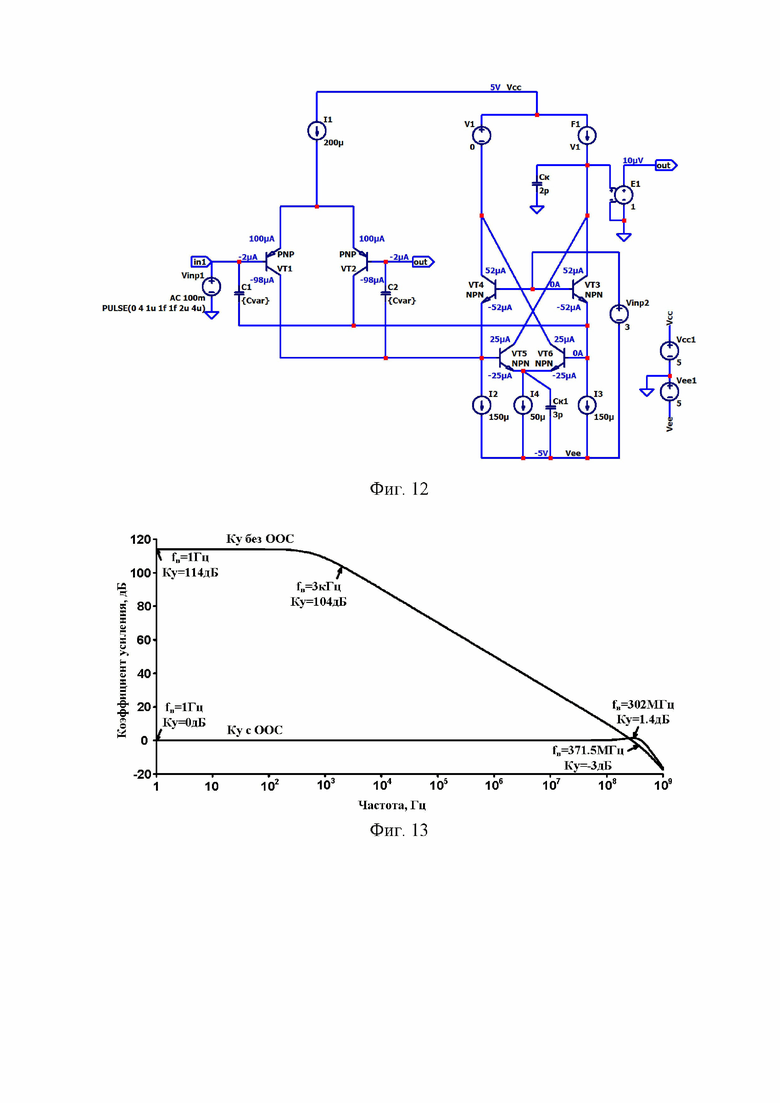

На чертеже фиг. 12 приведен статический режим схемы ОУ фиг. 3, соответствующей п. 2 формулы изобретения, в среде LTspice при t=27oC, Ск=С15=2пФ, Ск1=С19=3пФ, I1=200мкА, I2=I3=150мкА, I4=50мкА, Vinp2 = 3B, Vcc= -Vee=5В.

На чертеже фиг. 13 представлена ЛАЧХ ОУ на чертеже фиг. 12 в среде LTspice при t=27oC, Ск=С15=2пФ, Ск1=С19=3пФ, С1=С24=С2=С25=0пФ, I1=200мкА, I2=I3=150мкА, I4=50мкА, Vinp2 = 3B, Vcc= -Vee=5В.

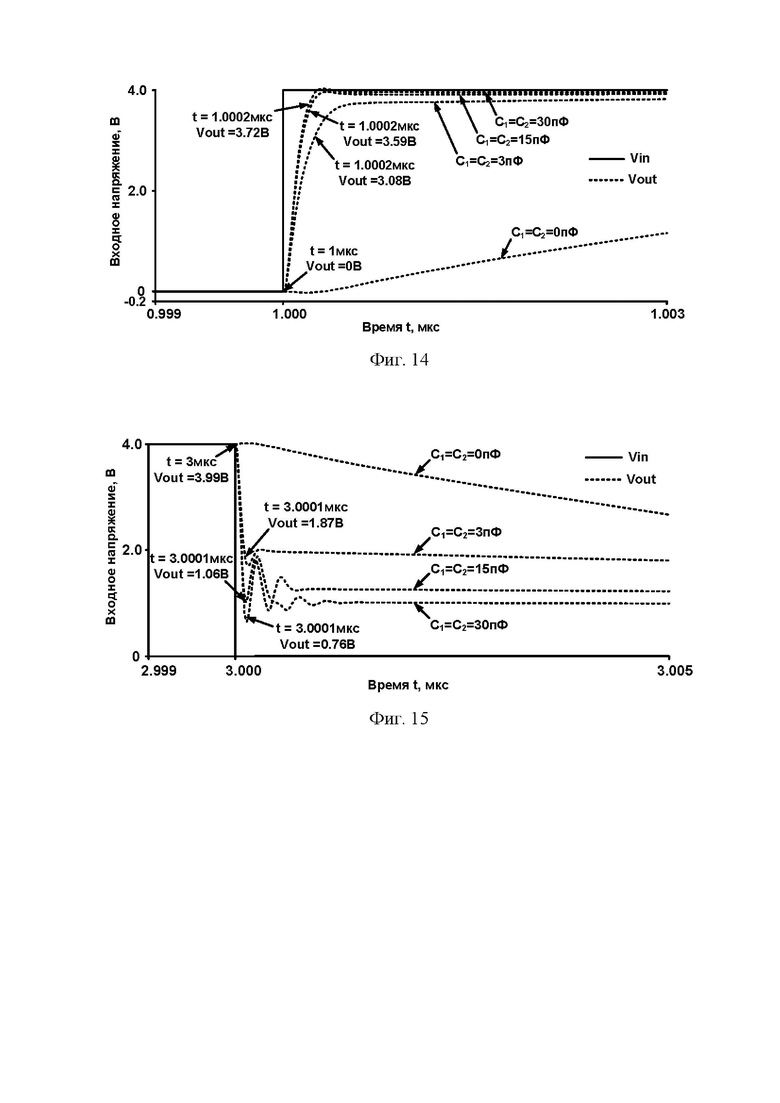

На чертеже фиг. 14 показаны переходные процессы в ОУ фиг. 12 для переднего фронта в среде LTspice при t=27oC, Ск=С15=2пФ, Ск1=С19=3пФ, I1=200мкА, I2=I3=150мкА, I4=50мкА, Vinp2 = 3B, Vcc= -Vee=5В и разных значений емкости первого 24 и второго 25 дополнительных конденсаторов (С1=С24=С2=С25=0пФ; 3пФ; 15пФ; 30пФ).

На чертеже фиг. 15 приведены переходные процессы в ОУ фиг. 12 для заднего фронта в среде LTspice при t=27oC, Ск=С15=2пФ, Ск1=С19=3пФ, I1=200мкА, I2=I3=150мкА, I4=50мкА, Vinp2 = 3B, Vcc= -Vee=5В и разных значений емкости первого 24 и второго 25 дополнительных конденсаторов (С1=С24=С2=С25=0пФ; 3пФ; 15пФ; 30пФ).

Быстродействующий операционный усилитель на основе «перегнутого» каскода с дифференцирующей цепью коррекции переходного процесса (фиг. 2) содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 8, эмиттер первого 6 выходного транзистора соединен с первым 4 токовым выходом и связан с первой 9 шиной источника питания через первый 10 токостабилизирующий двухполюсник, эмиттер второго 7 выходного транзистора связан со вторым 5 токовым выходом входного дифференциального каскада 1 и соединен с первой 9 шиной источника питания через второй 11 токостабилизирующий двухполюсник, коллектор первого 6 выходного транзистора подключен ко входу токового зеркала 12, согласованного со второй 13 шиной источника питания, выход которого связан с коллектором второго 7 выходного транзистора, входом буферного усилителя 14 и корректирующим конденсатором 15. В схему введены первый 16 и второй 17 дополнительные транзисторы, эмиттеры которых объединены и подключены к первой 9 шине источника питания через вспомогательный токостабилизирующий двухполюсник 18 и параллельно ему включенный вспомогательный корректирующий конденсатор 19, причем база первого 16 вспомогательного транзистора соединена с эмиттером первого 6 выходного транзистора, база второго 17 вспомогательного транзистора соединена с эмиттером второго 7 выходного транзистора, коллектор первого 16 вспомогательного транзистора подключен ко входу буферного усилителя 14, а коллектор второго 17 вспомогательного транзистора соединен со входом токового зеркала 12.

Кроме этого, на чертеже фиг. 2 входной дифференциальный каскад 1 реализован (в частном случае) на входных транзисторах 21, 22 и источнике опорного тока 23. Потенциальным выходом 20 заявляемого устройства является выход буферного усилителя 14.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, между первым 2 входом входного дифференциального каскада 1 и эмиттером второго 7 выходного транзистора включен первый 24 дополнительный конденсатор, а между вторым 3 входом входного дифференциального каскада 1 и эмиттером первого 6 выходного транзистора включен второй 25 дополнительный конденсатор.

Рассмотрим работу ОУ на чертеже фиг. 2.

Статический режим ОУ фиг. 2 определяется источником опорного тока 23, первым 10 и вторым 11 токостабилизирующими двухполюсниками, вспомогательным токостабилизирующим двухполюсником 18, а также источником напряжения смещения 8. Важно отметить, что токи первого 10 и второго 11 токостабилизирующих двухполюсников должны выбираться в соответствии с неравенством I10=I11<I23. В этом случае при большом отрицательном импульсном входном сигнале на первом 2 входе напряжение на эмиттере первого 6 выходного транзистора будет во время фронта увеличиваться, что приведет к существенному увеличению через вспомогательный корректирующий конденсатор 19 (Ск1=С19) тока эмиттера первого 16 вспомогательного транзистора и форсированию процесса перезаряда интегрирующего корректирующего конденсатора 15 (С15=Ск). Это позволяет увеличить SR(-).

Если на первый 2 вход подается положительный входной импульс, то возрастает напряжение на эмиттере второго 7 выходного транзистора, что увеличивает через вспомогательный корректирующий конденсатор 19 эмиттерный и коллекторный токи второго 17 вспомогательного транзистора и выходной ток токового зеркала 12. Это позволяет увеличивать SR(+) за счет более быстрого перезаряда емкости корректирующего конденсатора 15 (Ск=С15).

Данные эффекты подтверждаются результатами компьютерного моделирования, представленными на чертежах фиг. 10, фиг. 11, а также данными таблицы 1.

Таким образом, в сравнении с прототипом (фиг. 1, фиг. 6, фиг. 7), в операционном усилителе фиг. 2 (фиг. 8) по п. 1 формулы изобретения, SR для переднего фронта возрастает более чем в 17 раз, а для заднего фронта - более чем в 6 раз.

Дальнейшее повышение максимальной скорости нарастания выходного напряжения в заявляемом ОУ (в сравнении с прототипом) обеспечивается за счет п.2 формулы изобретения, который предусматривает введение двух дополнительных конденсаторов 24 и 25 (фиг. 3). Компьютерное моделирование ОУ фиг. 3 в среде LTspice, представленного на чертеже фиг. 12, показывает, что максимальная скорость нарастания выходного напряжения для переднего и заднего фронтов в данной модификации заявляемого ОУ существенно возрастает (см. фиг. 14, фиг. 15 и таблицу 2).

(передний фронт; фиг. 14)

(задний фронт; фиг. 15)

Из таблицы 2 следует, что при реализации ОУ в соответствии с п. 2 формулы изобретения, максимальная скорость нарастания выходного напряжения принимает экстремально большие значения (при идеальных буферном усилителе 14 и токовом зеркале 12).

Таким образом, введение дополнительных конденсаторов 24 и 25 (С1=С24 и С2=С25) при постоянных значениях емкости вспомогательного корректирующего конденсатора 19 (Ск1=С19=3пФ) дает существенное увеличение предельных значений максимальной скорости нарастания переднего фронта до 18600 В/мкс, а для заднего фронта - до 32300 В/мкс.

Для уменьшения влияния дополнительных конденсаторов 24 (С1=С24) и 25 (С2=С25) на входные емкости ОУ данные элементы могут подключаться к эмиттерам первого 6 и второго 7 выходных транзисторов через вспомогательные буферные усилители или дополнительные резисторы.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения замкнутого ОУ.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. E. J. Wyers, "Accurate Geometric Programming-Compatible Slew Rate Modeling for Two-Stage Operational Amplifier Design Optimization," 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Shenzhen, China, 2022, pp. 185-189. doi: 10.1109/APCCAS55924.2022.10090335.

2. J. Ramirez-Angulo and M. Holmes, "A simple technique to significantly enhance slew rate and bandwidth of one-stage CMOS operational amplifiers," 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 2002, pp. II-II. doi: 10.1109/ISCAS.2002.1011483.

Входные ДК на pnp транзисторах ОУ с «перегнутым» каскодом:

1. Патент US 6448583, fig.4, fig.5, fig.6, 2002 г.

2. Патент US 5091701, fig.1, 1992 г.

3. Патент US 5420542, fig.1A, 1995 г.

4. Патент US 5389894, fig.1, 1995 г.

5. Патент US 7545213, fig. 2, 2009 г.

6. Патент US 5282242, fig.2, 1994 г.

7. Патент US 6696888, fig.17, 2004 г.

8. Патент US 4293824, fig.2, 1981 г.

9. Патент US 7411451, fig. 1, 2008 г.

10. Патент RU 2354041, fig.2, 2009 г.

11. Патент US 6501333, fig.1, 2002 г.

12. Патент US 6456162, fig. 3, 2002 г.

13. Патент US 6542030, fig.2, 2003 г.

14. Патент US 3979069, fig.2, 1976 г.

15. Патент RU 2331969, fig.1, 2008 г.

16. Патент EP 0 586251, fig.2, 1994 г.

17. Патент US 3979689, fig.2, 1976 г.

18. Патент US 4600893, fig.7, 1986 г.

19. Патент US 5418491, fig.2, 1995 г.

20. Патент US 4406990, fig.4, 1983 г.

21. Патент US 5422600, fig.2, 1995 г.

22. Патент US 6218900, fig.1, 2001 г.

23. Патентная заявка US 2006/0202762, fig.2, 2006 г.

Входные ДК на npn транзисторах ОУ с «перегнутым» каскодом:

1. Патент РФ 2310268, fig.1, fig.2, 2007 г.

2. Патент US 6529076, 2001 г.

3. Патент US 4600893, fig.6,1986 г.

4. Патент US 2009/0256634, fig.1, 2009 г.

5. Патент US 6734737, fig.7, 2004 г.

6. Патент US 6483382, fig.1, fig.2, 2002 г.

7. Патент US 6304143, fig.1, 2001 г.

8. Патент JP 2009201119 A, fig.1, fig.2, 2009 г.

9. Патент US 5786729, fig.1, fig.2, 1998 г.

10. Патент RU 2421884, fig.1, 2011 г.

11. Патент US 7005921, fig.1B, 2006 г.

12. Патент US 6965266, fig. 1, 2005 г.

13. Патентная заявка US 2008/0024224, fig.1, 2008 г.

14. Патент US 6300831, fig.1, fig. 2, 2001 г.

15. Патент US 6788143, fig. 2, 2004 г.

16. Патент US 4959622, fig.18, 1990 г.

17. Патент US 5327100, fig.2, 1994 г.

Входные ДК на полевых транзисторах ОУ с «перегнутым» каскодом:

1. Патент US 5734296, fig.3, 2008 г.

2. Патент US 4406990, fig.6, 1983 г.

3. Патент US 6580325, fig.35, fig.36, 2003 г.

4. Патент US 6788143, fig.1, fig.4, 2004 г.

5. Патент US 4829266, fig. 10, 1989 г.

6. Патент US 7898330, fig. 1, 2011 г.

7. Патент US 4387309, 1983 г.

8. Патент US 6084475, fig.1, 2000 г.

9. Патентная заявка US 2005/0001682, fig.3, 2005 г.

10. Патент US 6717474, fig.4, 2004 г.

11. Патент US 6018268, fig.1, 2000 г.

12. Патент US 6714076, fig.2, 2004 г.

13. Патент EP 1227580, fig. 1, 2002 г.

Серийные микросхемы ОУ на «перегнутых» каскодах

154УД3, HA2520, HA5190, OP90, AD797, AD8631, AD8632, AD817, HA-2500, 140УД30, OPA42.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Быстродействующий операционный усилитель на основе комплементарного "перегнутого" каскода | 2023 |

|

RU2813280C1 |

| Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения | 2023 |

|

RU2810544C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С «ПЕРЕГНУТЫМ» КАСКОДОМ КЛАССА АВ | 2022 |

|

RU2786512C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

Изобретение относится к радиоэлектронике. Технический результат: обеспечение более высоких уровней выходного тока в структуре промежуточного каскада ОУ, перезаряжающего во время фронта переходного процесса интегрирующий корректирующий конденсатор ОУ. Для этого предложен быстродействующий операционный усилитель на основе «перегнутого» каскода с дифференцирующей цепью коррекции переходного процесса, в схему которого введены первый (16) и второй (17) дополнительные транзисторы, эмиттеры которых объединены и подключены к первой (9) шине источника питания через вспомогательный токостабилизирующий двухполюсник (18) и параллельно ему включенный вспомогательный корректирующий конденсатор (19), причем база первого (16) вспомогательного транзистора соединена с эмиттером первого (6) выходного транзистора, база второго (17) вспомогательного транзистора соединена с эмиттером второго (7) выходного транзистора, коллектор первого (16) вспомогательного транзистора подключен ко входу буферного усилителя (14), а коллектор второго (17) вспомогательного транзистора соединен со входом токового зеркала (12). 1 з.п. ф-лы, 15 ил., 2 табл.

1. Быстродействующий операционный усилитель на основе «перегнутого» каскода с дифференцирующей цепью коррекции переходного процесса, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, первый (6) и второй (7) выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения (8), эмиттер первого (6) выходного транзистора соединен с первым (4) токовым выходом и связан с первой (9) шиной источника питания через первый (10) токостабилизирующий двухполюсник, эмиттер второго (7) выходного транзистора связан со вторым (5) токовым выходом входного дифференциального каскада (1) и соединен с первой (9) шиной источника питания через второй (11) токостабилизирующий двухполюсник, коллектор первого (6) выходного транзистора подключен ко входу токового зеркала (12), согласованного со второй (13) шиной источника питания, выход которого связан с коллектором второго (7) выходного транзистора, входом буферного усилителя (14) и корректирующим конденсатором (15), отличающийся тем, что в схему введены первый (16) и второй (17) дополнительные транзисторы, эмиттеры которых объединены и подключены к первой (9) шине источника питания через вспомогательный токостабилизирующий двухполюсник (18) и параллельно ему включенный вспомогательный корректирующий конденсатор (19), причем база первого (16) вспомогательного транзистора соединена с эмиттером первого (6) выходного транзистора, база второго (17) вспомогательного транзистора соединена с эмиттером второго (7) выходного транзистора, коллектор первого (16) вспомогательного транзистора подключен ко входу буферного усилителя (14), а коллектор второго (17) вспомогательного транзистора соединен со входом токового зеркала (12).

2. Быстродействующий операционный усилитель на основе «перегнутого» каскода с дифференцирующей цепью коррекции переходного процесса по п.1, отличающийся тем, что между первым (2) входом входного дифференциального каскада (1) и эмиттером второго (7) выходного транзистора включен первый (24) дополнительный конденсатор, а между вторым (3) входом входного дифференциального каскада (1) и эмиттером первого (6) выходного транзистора включен второй (25) дополнительный конденсатор.

| US 6501333 B1, 31.12.2002 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| Операционный усилитель | 1974 |

|

SU500574A1 |

Авторы

Даты

2024-02-06—Публикация

2023-10-17—Подача