Изобретение относится к средствам автоматизации и может быть использовано в частности в системах управления электроагрегатов генераторных с приводом от двигателя внутреннего сгорания.

Известны аналоговые реле различного типа, содержащие измерительный преобразователь и выходной каскад, использующие различные способы измерения контролируемой физической величины /1, 2/.

Их недостатками являются ограниченные функциональные возможности в частности достоверность выходной информации и точность настройки.

Известен цифровой измеритель скорости вращения содержащий импульсный датчик, генератор эталонной частоты, счетчик импульсов, элемент задержки и электронные ключи /3/. Он обеспечивает удовлетворительную точность.

Его недостатком являются невысокие функциональные возможности, заключающиеся в наличии лишь одного выходного канала и невысокая достоверность выходной информации.

Известно реле частоты вращения (РЧВ) с трехканальным выходом по числу уставок, содержащее формирователь коротких импульсов, преобразователь частоты в постоянное напряжение, три пороговых устройства с задатчиками уставок, шесть индикаторов состояния и выходное устройство с тремя каскадами /4/. Наличие трех выходных каналов расширяет возможности РЧВ.

Однако возможные сбои в измерительной части и в выходных каналах при отсутствии самодиагностики отражаются на достоверности выходной информации РЧВ и могут привести к сбою в работе системы управления.

Наиболее близким к изобретению по технической сущности является цифровое четырехканальное реле с функцией реконструктивной диагностики, содержащее четыре приемных реле, с первого по восьмой формирователи коротких импульсов, дешифратор, первый и второй регистры памяти, блок памяти, элемент задержки, с первого по десятый логические элементы ИЛИ, с первого по шестой логические элементы И, с первого по восьмой логические элементы НЕ, выход первого из которых подключен к второму входу первого логического элемента И, а выход второго логического элемент НЕ подключен к второму входу второго логического элемента И, с первого по четвертый индикаторы состояния, причем к входу первого индикатора состояния подключен выход второго логического элемента ИЛИ, к входу второго индикатора состояния - выход четвертого логического элемента ИЛИ, а к входу четвертого индикатора состояния, подключен выход десятого логического элемента ИЛИ, первый вход которого связан с восьмым выходом дешифратора и третьим входом первого логического элемента ИЛИ, второй вход - с девятым выходом дешифратора и вторым входом седьмого логического элемента ИЛИ, третий вход - с выходом второго логического элемента И, четвертым входом четвертого элемента ИЛИ и пятым входом первого логического элемента ИЛИ, четвертый вход - с выходом шестого логического элемента И, шестым входом первого логического элемента ИЛИ и четвертым входом девятого логического элемента ИЛИ, выход которого подключен к входу третьего индикатора состояния, а третий вход связан с выходом четвертого логического элемента И, третьим входом второго логического элемента ИЛИ и пятым входом пятого логического элемента ИЛИ, выход которого подключен к входу четвертого адреса блока памяти, а первый вход - к пятнадцатому выходу дешифратора, второй вход - к одиннадцатому выходу дешифратора и второму входу девятого логического элемента ИЛИ, третий вход - к тринадцатому выходу дешифратора и второму входу четвертого логического элемента ИЛИ, четвертый вход - к четырнадцатому выходу дешифратора и второму входу второго логического элемента ИЛИ, шестой вход - к выходу пятого логического элемента И, пятому входу второго логического элемента ИЛИ и пятому входу четвертого логического элемента ИЛИ, первый вход которого связан со вторым входом восьмого логического элемента ИЛИ и пятым выходом дешифратора, четвертый выход которого соединен со вторым входом первого логического элемента ИЛИ и первым входом девятого логического элемента ИЛИ, нулевой выход дешифратора - с первым входом первого логического элемента ИЛИ, первый выход - с первым входом седьмого логического элемента ИЛИ, второй выход - с первыми входами первого и третьего логических элементов И, третий выход - с первым входом третьего логического элемента ИЛИ, шестой выход - с третьим входом восьмого логического элемента ИЛИ и первым входом второго логического элемента ИЛИ, седьмой выход - с первым входом восьмого логического элемента ИЛИ, выход которого подключен к входу третьего адреса блока памяти, разряды выхода которого являются выходами реле, а вход нулевого адреса блока памяти соединен с выходом первого логического элемента ИЛИ, вход первого адреса - с выходом седьмого логического элемента ИЛИ, вход второго адреса - с выходом третьего логического элемента ИЛИ, второй вход которого связан с четвертым входом второго логического элемента ИЛИ и выходом третьего логического элемента И, второй вход которого связан со вторым входом четвертого логического элемента И, вторым входом пятого логического элемента И, входом первого логического элемента НЕ и первым разрядом выхода второго регистра памяти, второй разряд выхода которого подключен к входу второго логического элемента НЕ и третьему входу пятого логического элемента И, первый вход которого связан с двенадцатым выходом дешифратора и первым входом шестого логического элемента И, второй вход которого соединен с третьим входом второго логического элемента И и выходом седьмого логического элемента НЕ, а третий вход - с выходом восьмого логического элемента НЕ, вход которого связан с третьим входом четвертого логического элемента И и третьим разрядом выхода второго регистра памяти, четвертый разряд выхода которого подключен к входу седьмого логического элемента НЕ, а сбросовый вход второго регистра памяти - к шине СБРОС и сбросовому входу первого регистра памяти, вход записи которого соединен с выходом элемента задержки, разряды выхода - с соответствующими разрядами входа второго регистра памяти, а соответствующие разряды входа - с соответствующими разрядами входа дешифратора и выходами соответствующих приемных реле, кроме того выход первого приемного реле подключен к входу первого формирователя коротких импульсов и входу третьего логического элемента НЕ, выход которого соединен с входом второго формирователя коротких импульсов, связанного выходом с первым входом шестого логического элемента ИЛИ, второй вход которого подключен к выходу первого формирователя коротких импульсов, третий вход - к выходу четвертого формирователя коротких импульсов, вход которого соединен с выходом четвертого логического элемента НЕ, вход которого связан с выходом второго приемного реле и входом третьего формирователя коротких импульсов, выход которого подключен к четвертому входу шестого логического элемента ИЛИ, пятый вход которого соединен с выходом шестого формирователя коротких импульсов, соединенного входом с выходом пятого логического элемента НЕ, вход которого связан с выходом третьего приемного реле и входом пятого формирователя коротких импульсов, подключенного выходом к шестому входу шестого логического элемента ИЛИ, седьмой вход которого соединен с выходом восьмого формирователя коротких импульсов, соединенного входом с выходом шестого логического элемента НЕ, вход которого соединен с выходом четвертого приемного реле и входом седьмого формирователя коротких импульсов, выход которого подключен к восьмому входу шестого логического элемента ИЛИ, связанного выходом с входом записи второго регистра памяти и входом элемента задержки, кроме того выход первого логического элемента И подключен к четвертому входу первого логического элемента ИЛИ и третьему входу четвертого логического элемента ИЛИ, а десятый выход дешифратора соединен с первыми входами второго и четвертого логического элемента И /5/.

Это реле обеспечивает полную диагностику для случаев сбоя одного из приемных реле. Однако для одновременного сбоя двух приемных реле идентифицирует не все ситуации, что ограничивает функциональные возможности.

Цель изобретения - расширение функциональных возможностей путем углубления диагностики бинарных сбоев.

Цель изобретения достигается тем, что четырехканальное цифровое реле с функцией реконструктивной диагностики, содержащее четыре приемных реле, с первого по восьмой формирователи коротких импульсов, дешифратор, первый и второй регистры памяти, блок памяти, элемент задержки, с первого по десятый логические элементы ИЛИ, с первого по шестой логические элементы И, с первого по восьмой логические элементы НЕ, выход первого из которых подключен к второму входу первого логического элемента И, а выход второго логического элемента НЕ подключен к второму входу второго логического элемента И, с первого по четвертый индикаторы состояния, причем к входу первого индикатора состояния подключен выход второго логического элемента ИЛИ, к входу второго индикатора состояния - выход четвертого логического элемента ИЛИ, а к входу четвертого индикатора состояния, подключен выход десятого логического элемента ИЛИ, первый вход которого связан с восьмым выходом дешифратора и третьим входом первого логического элемента ИЛИ, второй вход - с девятым выходом дешифратора и вторым входом седьмого логического элемента ИЛИ, третий вход - с выходом второго логического элемента И, четвертым входом четвертого элемента ИЛИ и пятым входом первого логического элемента ИЛИ, четвертый вход - с выходом шестого логического элемента И, шестым входом первого логического элемента ИЛИ и четвертым входом девятого логического элемента ИЛИ, выход которого подключен к входу третьего индикатора состояния, а третий вход связан с выходом четвертого логического элемента И, третьим входом второго логического элемента ИЛИ и пятым входом пятого логического элемента ИЛИ, выход которого подключен к входу четвертого адреса блока памяти, а первый вход - к пятнадцатому выходу дешифратора, второй вход - к одиннадцатому выходу дешифратора и второму входу девятого логического элемента ИЛИ, третий вход - к тринадцатому выходу дешифратора и второму входу четвертого логического элемента ИЛИ, четвертый вход - к четырнадцатому выходу дешифратора и второму входу второго логического элемента ИЛИ, шестой вход - к выходу пятого логического элемента И, пятому входу второго логического элемента ИЛИ и пятому входу четвертого логического элемента ИЛИ, первый вход которого связан со вторым входом восьмого логического элемента ИЛИ и пятым выходом дешифратора, четвертый выход которого соединен со вторым входом первого логического элемента ИЛИ и первым входом девятого логического элемента ИЛИ, нулевой выход дешифратора - с первым входом первого логического элемента ИЛИ, первый выход - с первым входом седьмого логического элемента ИЛИ, второй выход - с первыми входами первого и третьего логических элементов И, третий выход - с первым входом третьего логического элемента ИЛИ, шестой выход - с третьим входом восьмого логического элемента ИЛИ и первым входом второго логического элемента ИЛИ, седьмой выход - с первым входом восьмого логического элемента ИЛИ, выход которого подключен к входу третьего адреса блока памяти, разряды выхода которого являются выходами реле, а вход нулевого адреса блока памяти соединен с выходом первого логического элемента ИЛИ, вход первого адреса - с выходом седьмого логического элемента ИЛИ, вход второго адреса - с выходом третьего логического элемента ИЛИ, второй вход которого связан с четвертым входом второго логического элемента ИЛИ и выходом третьего логического элемента И, второй вход которого связан со вторым входом четвертого логического элемента И, вторым входом пятого логического элемента И, входом первого логического элемента НЕ и первым разрядом выхода второго регистра памяти, второй разряд выхода которого подключен к входу второго логического элемента НЕ и третьему входу пятого логического элемента И, первый вход которого связан с двенадцатым выходом дешифратора и первым входом шестого логического элемента И, второй вход которого соединен с третьим входом второго логического элемента И и выходом седьмого логического элемента НЕ, а третий вход - с выходом восьмого логического элемента НЕ, вход которого связан с третьим входом четвертого логического элемента И и третьим разрядом выхода второго регистра памяти, четвертый разряд выхода которого подключен к входу седьмого логического элемента НЕ, а сбросовый вход второго регистра памяти - к шине СБРОС и сбросовому входу первого регистра памяти, вход записи которого соединен с выходом элемента задержки, разряды выхода - с соответствующими разрядами входа второго регистра памяти, а соответствующие разряды входа - с соответствующими разрядами входа дешифратора и выходами соответствующих приемных реле, кроме того выход первого приемного реле подключен к входу первого формирователя коротких импульсов и входу третьего логического элемента НЕ, выход которого соединен с входом второго формирователя коротких импульсов, связанного выходом с первым входом шестого логического элемента ИЛИ, второй вход которого подключен к выходу первого формирователя коротких импульсов, третий вход - к выходу четвертого формирователя коротких импульсов, вход которого соединен с выходом четвертого логического элемента НЕ, вход которого связан с выходом второго приемного реле и входом третьего формирователя коротких импульсов, выход которого подключен к четвертому входу шестого логического элемента ИЛИ, пятый вход которого соединен с выходом шестого формирователя коротких импульсов, соединенного входом с выходом пятого логического элемента НЕ, вход которого связан с выходом третьего приемного реле и входом пятого формирователя коротких импульсов, подключенного выходом к шестому входу шестого логического элемента ИЛИ, седьмой вход которого соединен с выходом восьмого формирователя коротких импульсов, соединенного входом с выходом шестого логического элемента НЕ, вход которого соединен с выходом четвертого приемного реле и входом седьмого формирователя коротких импульсов, выход которого подключен к восьмому входу шестого логического элемента ИЛИ, связанного выходом с входом записи второго регистра памяти и входом элемента задержки, кроме того выход первого логического элемента И подключен к четвертому входу первого логического элемента ИЛИ и третьему входу четвертого логического элемента ИЛИ, а десятый выход дешифратора соединен с первыми входами второго и четвертого логического элемента И, снабжено седьмым, восьмым, девятым и десятым логическим элементом И, третий вход которого связан с четвертым разрядом выхода второго регистра памяти, второй вход - с выходом первого логического элемента НЕ и вторыми входами седьмого и девятого логических элементов И, первый вход - с десятым выходом дешифратора, а выход - с четвертым входом третьего логического элемента ИЛИ, восьмым входом второго логического элемента ИЛИ и шестым входом десятого логического элемента ИЛИ, пятый вход которого соединен с шестым входом второго логического элемента ИЛИ, седьмым входом первого логического элемента ИЛИ и выходом седьмого логического элемента И, третий вход которого подключен к выходу седьмого логического элемента НЕ, а первый вход - к девятому выходу дешифратора и первым входам восьмого и девятого логического элемента И, выход которого соединен с третьим входом третьего логического элемента ИЛИ, седьмым входом второго логического элемента ИЛИ и шестым входом девятого логического элемента ИЛИ, пятый вход которого связан с шестым входом четвертого логического элемента ИЛИ, седьмым входом пятого логического элемента ИЛИ и выходу восьмого логического элемента И, второй вход которого подключен к второму разряду выхода второго регистра памяти, а третий вход - к третьему разряду выхода второго регистра памяти и к третьему входу девятого логического элемента И.Седьмой логический элемент И обеспечивает контроль факта одновременного сбоя первого и четвертого приемного реле. Восьмой логический элемент И фиксирует одновременный сбой второго и третьего приемного реле. Девятый логический элемент И выявляет одновременный сбой первого и третьего приемного реле. Десятый логический элемент И устанавливает факт одновременного сбоя приемного реле.

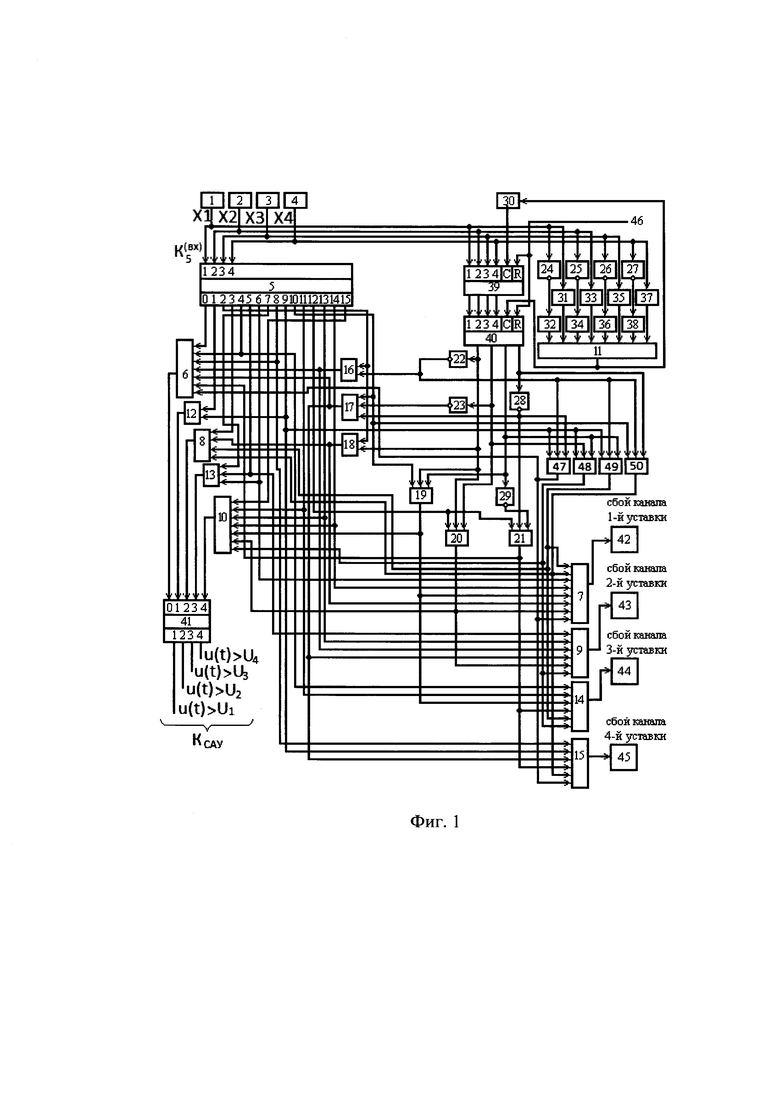

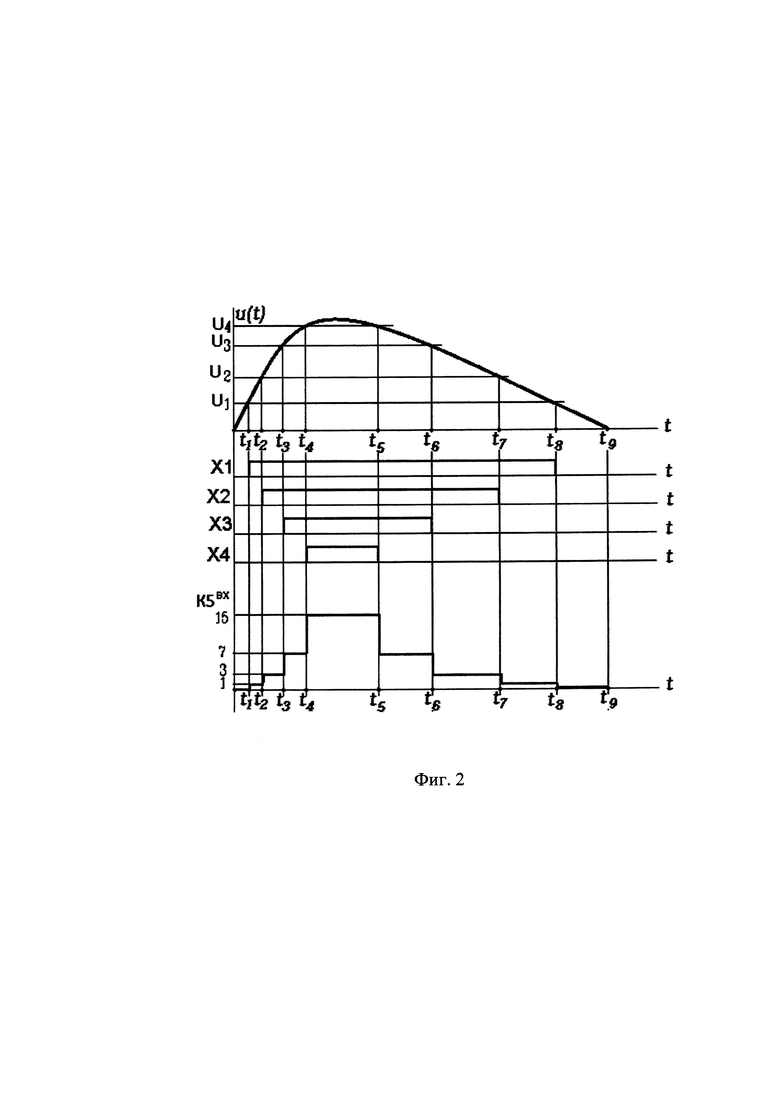

На фиг. 1 представлена схема четырехканального цифрового реле с функцией реконструктивной диагностики, на фиг. 2 - эпюры сигналов на элементах устройства.

Реле (фиг. 1) включает первый 1, второй 2, третий 3 и четвертый 4 приемные датчики соответствующих уставок, дешифратор 5, первый 6, второй 7, третий 8, четвертый 9, пятый 10, шестой 11, седьмой 12, восьмой 13, девятый 14 и десятый 15 логические элементы ИЛИ, первый 16, второй 17, третий 18, четвертый 19, пятый 20 и шестой 21 логические элементы И, первый 22, второй 23, третий 24, четвертый 25, пятый 26, шестой 27, седьмой 28 и восьмой 29 логические элементы НЕ, элемент задержки 30, первый 31, второй 32, третий 33, четвертый 34, пятый 35, шестой 36, седьмой 37 и восьмой 38 формирователи коротких импульсов, первый 39 и второй 40 регистры памяти, блок памяти 41, первый 42, второй 43, третий 44 и четвертый 45 индикаторы сбоя соответствующих каналов, шину СБРОС 46, седьмой 47, восьмой 48, девятый 49 и десятый 50 логические элементы И.

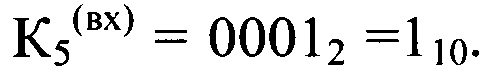

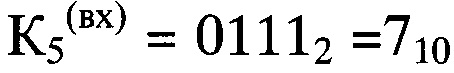

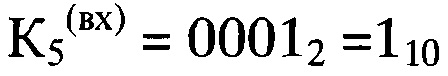

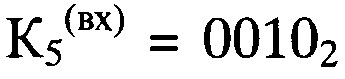

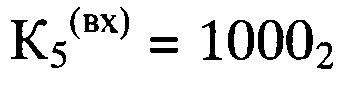

Реле работает следующим образом. Датчики 1…4 настроены на параметры срабатывания соответственно U1, U2, U3 и U4, причем U4>U3>U2>U1 (фиг. 2). По мере возрастания контролируемой величины u(t) в момент времени t1 (фиг. 2) срабатывает датчик 1 и на его выходе появляется сигнал X1. На входе дешифратора 5 устанавливается код  На первом выходе дешифратора 5 появляется сигнал, который через элемент ИЛИ 12 поступает на вход первого адреса блока памяти 41, по которому записан код 00012. В результате появляется сигнал u(t)>U1 на первом выходе блока памяти 41 (код КСАУ=00012), который поступает в систему автоматического управления (САУ).

На первом выходе дешифратора 5 появляется сигнал, который через элемент ИЛИ 12 поступает на вход первого адреса блока памяти 41, по которому записан код 00012. В результате появляется сигнал u(t)>U1 на первом выходе блока памяти 41 (код КСАУ=00012), который поступает в систему автоматического управления (САУ).

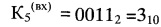

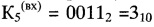

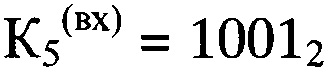

В момент времени t2 (фиг. 2) срабатывает датчик 2 и на его выходе появляется сигнал Х2. На входе дешифратора 5 устанавливается код  и появляется сигнал на третьем его выходе, который через элемент ИЛИ 8 подается на вход второго адреса блока памяти 41, по которому записан код 00112. При этом в САУ с выхода блока памяти 41 поступают два сигнала u(t)>U1 и u(t)>U2 (код КСАУ=00112).

и появляется сигнал на третьем его выходе, который через элемент ИЛИ 8 подается на вход второго адреса блока памяти 41, по которому записан код 00112. При этом в САУ с выхода блока памяти 41 поступают два сигнала u(t)>U1 и u(t)>U2 (код КСАУ=00112).

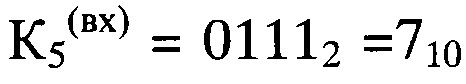

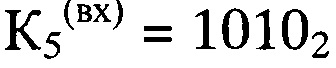

В момент времени t3 (фиг. 2) появляется сигнал Х3 на его выходе датчика 3. На вход дешифратора 5 подается код  . На седьмом выходе дешифратора 5 появляется сигнал, поступающий через элемент ИЛИ 13 подается на вход третьего адреса блока памяти 41, по которому записан код 01112. При этом в САУ с выхода блока памяти 41 поступают три сигнала u(t)>U1, u(t)>U2 и u(t)>U3 (код КСАУ=01112).

. На седьмом выходе дешифратора 5 появляется сигнал, поступающий через элемент ИЛИ 13 подается на вход третьего адреса блока памяти 41, по которому записан код 01112. При этом в САУ с выхода блока памяти 41 поступают три сигнала u(t)>U1, u(t)>U2 и u(t)>U3 (код КСАУ=01112).

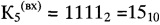

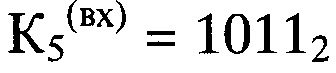

При дальнейшем возрастании контролируемой величины u(t) в момент времени t4 (фиг. 2) срабатывает датчик 4 и на его выходе появляется сигнал Х4. На входе дешифратора 5 формируется код  . Появляется сигнал на пятнадцатом выходе дешифратора 5, который через элемент ИЛИ 10 проходит на вход четвертого адреса блока памяти 41, по которому записан код 11112. С выхода блока памяти 41 в САУ поступают четыре сигнала u(t)>U1, u(t)>U2, u(t)>U3 и u(t)>U4 (код КСАУ=11112).

. Появляется сигнал на пятнадцатом выходе дешифратора 5, который через элемент ИЛИ 10 проходит на вход четвертого адреса блока памяти 41, по которому записан код 11112. С выхода блока памяти 41 в САУ поступают четыре сигнала u(t)>U1, u(t)>U2, u(t)>U3 и u(t)>U4 (код КСАУ=11112).

При уменьшении контролируемой величины u(t) в момент времени t5 (фиг. 2) исчезает сигнал Х4 на выходе датчик 4 и на входе дешифратора 5 устанавливается код  . В САУ с выхода блока памяти 41 подаются три сигнала u(t)>U1, u(t)>U2 и u(t)>U3 (код КСАУ=01112).

. В САУ с выхода блока памяти 41 подаются три сигнала u(t)>U1, u(t)>U2 и u(t)>U3 (код КСАУ=01112).

В момент времени t6 (фиг. 2) исчезает сигнал Х3 на выходе датчик 3 и устанавливается код  на входе дешифратора 5. При этом с выхода блока памяти 41 подаются в САУ два сигнала u(t)>U1 и u(t)>U2 (код КСАУ=00112).

на входе дешифратора 5. При этом с выхода блока памяти 41 подаются в САУ два сигнала u(t)>U1 и u(t)>U2 (код КСАУ=00112).

Последующее уменьшение контролируемой величины u(t) приводит к исчезновению сигнала Х2 на выходе датчика 2 в момент времени t7 (фиг. 2) и установки кода  на входе дешифратора 5. В САУ с выхода блока памяти 41 подается один сигнал u(t)>U1 (код КСАУ=00012).

на входе дешифратора 5. В САУ с выхода блока памяти 41 подается один сигнал u(t)>U1 (код КСАУ=00012).

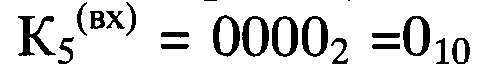

В момент времени t8 (фиг. 2) исчезает сигнал X1 на выходе датчика 1 и устанавливается код  на входе дешифратора 5. С нулевого выхода дешифратора 5 через элемент ИЛИ 6 подается сигнал на вход нулевого адреса блока памяти 41, по которому записан код 00002. При этом с выхода блока памяти 41 сигналы в САУ не подаются (код КСАУ=00002).

на входе дешифратора 5. С нулевого выхода дешифратора 5 через элемент ИЛИ 6 подается сигнал на вход нулевого адреса блока памяти 41, по которому записан код 00002. При этом с выхода блока памяти 41 сигналы в САУ не подаются (код КСАУ=00002).

Таким образом при монотонном возрастании контролируемой величины u(t) наблюдается следующая последовательность появления кодов  на входе дешифратора 5 и выходе блока 41 памяти: 00002, 00012, 00112, 01112, 11112, а при монотонном убывании - 11112, 01112, 00112, 00012, 00002. Эта естественная последовательность кодов указывает на исправность каналов уставок. При этом код КСАУ на выходе блока 41 памяти совпадает с входным кодом

на входе дешифратора 5 и выходе блока 41 памяти: 00002, 00012, 00112, 01112, 11112, а при монотонном убывании - 11112, 01112, 00112, 00012, 00002. Эта естественная последовательность кодов указывает на исправность каналов уставок. При этом код КСАУ на выходе блока 41 памяти совпадает с входным кодом  дешифратора 5 и поступает в САУ без коррекции.

дешифратора 5 и поступает в САУ без коррекции.

При возникновении неисправности в каналах уставок на входе дешифратора 5 могут появиться сбойные коды  : 00102, 01002, 01012, 01102, 10002, 10012, 10102, 10112, 11002, 11012 и 11102, которые требуют коррекции перед передачей в САУ. Выявление неисправного канала осуществляется путем сравнения текущего и предыдущего кодов на входе дешифратора 5, после чего с выходе блока 41 памяти выдается в САУ откорректированный код КСАУ.

: 00102, 01002, 01012, 01102, 10002, 10012, 10102, 10112, 11002, 11012 и 11102, которые требуют коррекции перед передачей в САУ. Выявление неисправного канала осуществляется путем сравнения текущего и предыдущего кодов на входе дешифратора 5, после чего с выходе блока 41 памяти выдается в САУ откорректированный код КСАУ.

С появлением сигналов X1…Х4 на выходе любого датчика 1…4 по фронту сигналов формирователи 31, 33, 35 и 37 вырабатывают импульсы, которые поступают через элемент ИЛИ 11 и элемент задержки 30 на вход записи регистра памяти 39, в который записывается текущий входной код  дешифратора 5. При очередном изменении кода

дешифратора 5. При очередном изменении кода  импульсом с выхода элемента ИЛИ 11 производится перезапись предыдущего кода из регистра памяти 39 в регистр памяти 40. В регистр 39 с задержкой, обеспеченной элементом 30, осуществляется запись очередного текущего кода. Когда исчезают сигналы на выходе датчиков 1…4, перезапись кодов в регистры 39 и 40 производится импульсами, сформированными по задним фронтам сигналов X1…Х4 формирователями 32, 34, 36 и 38, на которые поступают сигналы с выходов элементов НЕ 22, 23, 24 и 25 соответственно. В результате в любой момент времени и при любом характере изменения контролируемой величины в регистр памяти 39 оказывается записан текущий код, а в регистр 40 - предыдущий код

импульсом с выхода элемента ИЛИ 11 производится перезапись предыдущего кода из регистра памяти 39 в регистр памяти 40. В регистр 39 с задержкой, обеспеченной элементом 30, осуществляется запись очередного текущего кода. Когда исчезают сигналы на выходе датчиков 1…4, перезапись кодов в регистры 39 и 40 производится импульсами, сформированными по задним фронтам сигналов X1…Х4 формирователями 32, 34, 36 и 38, на которые поступают сигналы с выходов элементов НЕ 22, 23, 24 и 25 соответственно. В результате в любой момент времени и при любом характере изменения контролируемой величины в регистр памяти 39 оказывается записан текущий код, а в регистр 40 - предыдущий код  с входа дешифратора 5.

с входа дешифратора 5.

Коррекция сбойных кодов осуществляется следующим образом. Код  на входе дешифратора 5 может появиться при сбое датчика 1 или 2. При этом появляется сигнал на втором выходе дешифратора 5, который поступает на первые входы логических элементов И 16 и 18. Если до момента изменения кода на выходе датчика 1 присутствовал сигнал, т.е. в предыдущем коде присутствует единица в первом разряде, сигнал с первого выхода регистра 40 поступает на второй вход элемента И 18. Появляется сигнал на выходе элемента И 18, который через элемент ИЛИ 12 поступает на вход индикатора 42, указывающего на сбой в канале первой уставки. Одновременно сигнал с выхода элемента И 18 поступает на вход второго адреса блока памяти 41 и на его выходах появится скорректированный код 00112. Если до момента изменения кода на выходе датчика 1 сигнал отсутствовал, то на второй вход элемента И 16 поступает сигнал с выхода логического элемента НЕ 22. Появляется сигнал на выходе элемента И16, который через элемент ИЛИ 9 подается на индикатор 43, указывающий на сбой канала второй уставки. Через элемент ИЛИ 6 сигнал с выхода элемента И16 поступает на вход нулевого адреса блока памяти 41, на выходе которого появится скорректированный код КСАУ=00002.

на входе дешифратора 5 может появиться при сбое датчика 1 или 2. При этом появляется сигнал на втором выходе дешифратора 5, который поступает на первые входы логических элементов И 16 и 18. Если до момента изменения кода на выходе датчика 1 присутствовал сигнал, т.е. в предыдущем коде присутствует единица в первом разряде, сигнал с первого выхода регистра 40 поступает на второй вход элемента И 18. Появляется сигнал на выходе элемента И 18, который через элемент ИЛИ 12 поступает на вход индикатора 42, указывающего на сбой в канале первой уставки. Одновременно сигнал с выхода элемента И 18 поступает на вход второго адреса блока памяти 41 и на его выходах появится скорректированный код 00112. Если до момента изменения кода на выходе датчика 1 сигнал отсутствовал, то на второй вход элемента И 16 поступает сигнал с выхода логического элемента НЕ 22. Появляется сигнал на выходе элемента И16, который через элемент ИЛИ 9 подается на индикатор 43, указывающий на сбой канала второй уставки. Через элемент ИЛИ 6 сигнал с выхода элемента И16 поступает на вход нулевого адреса блока памяти 41, на выходе которого появится скорректированный код КСАУ=00002.

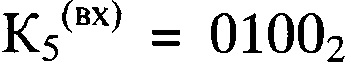

Код  появляется в случае неисправности канала третий уставки. При этом появляется сигнал на четвертом выходе дешифратора 5, который через элемент ИЛИ 14 проходит на вход индикатора 44, указывающий на сбой канала третий уставки. В то же время через элемент 6 поступает сигнал на вход нулевого адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=00002.

появляется в случае неисправности канала третий уставки. При этом появляется сигнал на четвертом выходе дешифратора 5, который через элемент ИЛИ 14 проходит на вход индикатора 44, указывающий на сбой канала третий уставки. В то же время через элемент 6 поступает сигнал на вход нулевого адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=00002.

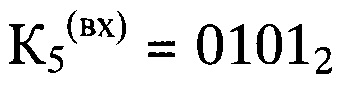

Код  возникает при неисправности канала второй уставки. В этой ситуации появляется сигнал на пятом выходе дешифратора 5, который через элемент ИЛИ 9 подается на вход индикатора 43, диагностирующего сбой канала второй уставки. Одновременно через элемент ИЛИ 13 проходит сигнал на вход третьего адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=01112.

возникает при неисправности канала второй уставки. В этой ситуации появляется сигнал на пятом выходе дешифратора 5, который через элемент ИЛИ 9 подается на вход индикатора 43, диагностирующего сбой канала второй уставки. Одновременно через элемент ИЛИ 13 проходит сигнал на вход третьего адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=01112.

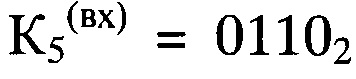

Код  вызван неисправностью канала первой уставки. В этом случае появляется сигнал на шестом выходе дешифратора 5, поступающий через элемент ИЛИ 7 на вход индикатора 42, указывающий на сбой канала первой уставки. Сигнал с шестого выхода дешифратора 5 также через элемент ИЛИ 13 проходит на вход третьего адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=01112.

вызван неисправностью канала первой уставки. В этом случае появляется сигнал на шестом выходе дешифратора 5, поступающий через элемент ИЛИ 7 на вход индикатора 42, указывающий на сбой канала первой уставки. Сигнал с шестого выхода дешифратора 5 также через элемент ИЛИ 13 проходит на вход третьего адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=01112.

Код  наблюдается при сбое канала четвертой уставки. При этом появляется сигнал на восьмом выходе дешифратора 5. Этот сигнал через элемент ИЛИ 15 поступает на вход индикатора 45, указывающего на сбой канала четвертой уставки, а через элемент ИЛИ 6 - на вход нулевого адреса блока памяти 41. На его выход подается скорректированный код КСАУ=00002.

наблюдается при сбое канала четвертой уставки. При этом появляется сигнал на восьмом выходе дешифратора 5. Этот сигнал через элемент ИЛИ 15 поступает на вход индикатора 45, указывающего на сбой канала четвертой уставки, а через элемент ИЛИ 6 - на вход нулевого адреса блока памяти 41. На его выход подается скорректированный код КСАУ=00002.

Код  может появится в случае одинарного сбоя канала четвертой уставки или бинарных сбоев: первого и четвертого канала; второго и третьего канала; первого и третьего канала. Во всех случаях появляется сигнал на девятом выходе дешифратора 5.

может появится в случае одинарного сбоя канала четвертой уставки или бинарных сбоев: первого и четвертого канала; второго и третьего канала; первого и третьего канала. Во всех случаях появляется сигнал на девятом выходе дешифратора 5.

При сбое канала четвертой уставки с выхода дешифратора 5 через элемент ИЛИ 15 сигнал проходит на вход индикатора 45, указывающего на сбой четвертого канала. Одновременно через элемент ИЛИ 12 сигнал поступает на вход первого адреса блока памяти 41, и на его выходе появляется скорректированный код КСАУ=00012.

При сбое каналов первой и четвертой уставки сигнал с выхода дешифратора 5 подготавливает по первому входу логический элемент И 47. На выходе второго регистра памяти 40, хранящим информацию о предыдущем состоянии каналов, присутствует нулевой код. Поэтому на выходе элемента НЕ 22 и элемента НЕ 28 появляются сигналы, которые открывают элемент И 47. Сигнал с выхода элемента И 47 через элемент ИЛИ 7 включает индикатор 42, а через элемент ИЛИ 15 включает индикатор 45, указывая на сбойные каналы. Одновременно сигнал с выхода элемента И 47 через элемент ИЛИ 6 поступает на вход нулевого адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=00002.

При сбое каналов второй и третий уставки на выходе второго регистра памяти 40 присутствует единичный код. Поэтому на второй и третий вход элемента И 48 поступают сигналы. Так как элемент И 48 подготовлен по первому входу сигналом с девятого выхода дешифратора 5, появляется сигнал на его выходе, который через элемент ИЛИ 9 включает индикатор 43, а через элемент ИЛИ 14 включает индикатор 44. Одновременно этот сигнал через элемент ИЛИ 10 поступает на вход четвертого адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=11112.

При сбое каналов первой и третий уставки присутствует сигнал на третьем и четвертом разрядах выхода второго регистра памяти 40. На третий вход элемента И 49 поступает сигнал с третьего разряда выхода регистра памяти 40, на второй вход - с выхода элемента НЕ 22, а по первому входу элемент И 49 подготовлен сигналом с девятого выхода дешифратора 5. Сигнал с выхода элемента И 49 через элемент ИЛИ 7 включает индикатор 42, а через элемент ИЛИ 14 включает индикатор 44. Вместе с тем сигнал с выхода элемента И 49 через элемент ИЛИ 8 поступает на вход второго адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=00112.

Появление на входе дешифратора 5 кода  может быть обусловлено бинарным сбоем первого и третьего канала, второго и четвертого канала или первого и четвертого канала. В всех случаях появляется сигнал на десятом выходе дешифратора 5, который подготавливает по первым входам логические элементы И 17, И 19 и И 50.

может быть обусловлено бинарным сбоем первого и третьего канала, второго и четвертого канала или первого и четвертого канала. В всех случаях появляется сигнал на десятом выходе дешифратора 5, который подготавливает по первым входам логические элементы И 17, И 19 и И 50.

Если до момента изменения кода на выходах первого 1 и третьего 3 датчика присутствовал сигнал, то с первого и третьего выхода регистра 40 поступают сигналы на второй и третий входы элемента И 19. Сигнал с его выхода через элемент ИЛИ 7 подается на индикатор 42, указывающий на сбой канала первой уставки, а через элемент ИЛИ 14 - на индикатор 44, указывающий на сбой канала третий уставки. Одновременно с выхода элемента И 19 через элемент ИЛИ 10 сигнал поступает на вход четвертого адреса блока памяти 41, на выходе которого появится скорректированный код КСАУ=1112.

Если до момента изменения кода на выходах второго 2 и четвертого 4 датчика сигнал отсутствовал, то сигналы низкого уровня со второго и четвертого входа регистра 40 инвертируются элементами НЕ 23 и 28, и на второй и третий входы элемента И 17 поступают сигналы открывающие его. Сигнал с выхода элемента И 17 через элемент ИЛИ 9 включает индикатор 43, показывающий на сбой канала второй уставки, а через элемент ИЛИ 15 - индикатор 45, показывающий на сбой канала четвертой уставки. В то же время сигнал с выхода элемента И 17 через элемент ИЛИ 6 проходит на вход нулевого адреса блока памяти 41, выдающий в САУ скорректированный код КСАУ=00002.

Если до момента изменения кода на выходе первого 1 сигнал отсутствовал, а на выходе четвертого 4 датчика сигнал присутствовал, то на третий вход элемента И 50 поступает сигнал с четвертого разряда выхода блока памяти 40, а на его второй вход сигнал с выхода элемента НЕ 22. Поэтому появляется сигнал на выходе элемента И 50, который через элемент ИЛИ 7 включает индикатор 42, а через элемент ИЛИ 15 включает индикатор 45. Одновременно сигнал с выхода элемента И 50 через элемент ИЛИ 8 поступает на вход второго адреса блока памяти 41, выдающий в САУ скорректированный код КСАУ=00112.

Код  наблюдается при неисправности канала третий уставки. При этом появляется сигнал на одиннадцатом выходе дешифратора 5, который через элемент ИЛИ 14 поступает на вход индикатора 44, указывающего на сбой канала третий уставки. Одновременно через элемент ИЛИ 10 сигнал проходит на вход четвертого адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=1112.

наблюдается при неисправности канала третий уставки. При этом появляется сигнал на одиннадцатом выходе дешифратора 5, который через элемент ИЛИ 14 поступает на вход индикатора 44, указывающего на сбой канала третий уставки. Одновременно через элемент ИЛИ 10 сигнал проходит на вход четвертого адреса блока памяти 41, на выходе которого появляется скорректированный код КСАУ=1112.

Код  может появиться при двойной неисправности каналов первой и второй уставки или при неисправности каналов третий и четвертой уставки. В этих случаях появляется сигнал на двенадцатом выходе дешифратора 5, поступающий на первые входы элементов И 20 и 21.

может появиться при двойной неисправности каналов первой и второй уставки или при неисправности каналов третий и четвертой уставки. В этих случаях появляется сигнал на двенадцатом выходе дешифратора 5, поступающий на первые входы элементов И 20 и 21.

Если до момента изменения кода на выходах первого 1 и второго 2 датчика присутствовал сигнал, то на второй и третий входы элемента И 20 поступают сигналы, которые открывают элемент И 20. С его выхода через элемент ИЛИ 7 подается сигнал на индикатор 42, сообщающий о сбое канала первой уставки, а через элемент ИЛИ 9 - на индикатор 43, сообщающий о сбое канала второй уставки. В то же время с выхода элемента И 20 через элемент ИЛИ 10 проходит сигнал на вход четвертого адреса блока памяти 41, который выдает скорректированный код КСАУ=1112.

Если до момента изменения кода на выходах датчиков 3 и 4 сигнал отсутствовал, то с выхода элементов НЕ 28 и 29 на второй и третий входы элемента И 21 поступают сигналы, которые его открывают. С выхода элемента И 21 проходит сигнал через элемент ИЛИ 14 на индикатор 44, а через элемент ИЛИ 15 на индикатор 45. Индикаторы 44 и 45 указывают на сбои в третьем и четвертом каналах уставок. Одновременно с выхода элемента И 21 через элемент ИЛИ 6 проходит сигнал на вход нулевого адреса блока памяти 41, который подает в САУ скорректированный код КСАУ=00002.

Код  появляется в случае неисправности второго датчика 2. При этом появляется сигнал на тринадцатом выходе дешифратора 5, поступающий через элемент ИЛИ 9 на индикатор 43, указывающий на сбой канала второй уставки, а через элемент ИЛИ 10 сигнал поступает на вход четвертого адреса блока памяти 41, который выдает скорректированный код КСАУ=11112.

появляется в случае неисправности второго датчика 2. При этом появляется сигнал на тринадцатом выходе дешифратора 5, поступающий через элемент ИЛИ 9 на индикатор 43, указывающий на сбой канала второй уставки, а через элемент ИЛИ 10 сигнал поступает на вход четвертого адреса блока памяти 41, который выдает скорректированный код КСАУ=11112.

Код  наблюдается при неисправности первого датчика 1. Эта ситуация сопровождается появлением сигнала на четырнадцатом выходе дешифратора 5, который через элемент ИЛИ 7 включает индикатор 42, указывающий на сбой канала первой уставки. Одновременно сигнал через элемент ИЛИ 10 поступает на вход четвертого адреса блока памяти 41, который выдает скорректированный код КСАУ=11112.

наблюдается при неисправности первого датчика 1. Эта ситуация сопровождается появлением сигнала на четырнадцатом выходе дешифратора 5, который через элемент ИЛИ 7 включает индикатор 42, указывающий на сбой канала первой уставки. Одновременно сигнал через элемент ИЛИ 10 поступает на вход четвертого адреса блока памяти 41, который выдает скорректированный код КСАУ=11112.

В результате каждый сбойный код корректируется, и в САУ поступает достоверная информация.

Таким образом, реле имеет расширенные функциональные возможности, заключающиеся в повышении достоверности выходной информации путем введения функций диагностики измерительной части и каналов уставок реле и коррекции информации при сбоях. Причем устройство идентифицирует восемнадцать сбойных ситуаций, что на четыре больше, чем у прототипа.

Источники информации

1. Сугаков В.Г. Основы автоматизации военных передвижных источников электрической энергии: учеб. пособие. - Кстово: НФВИУ, 2003. 168 с.

2. Дудченко В.Н., Аверкиев А.Н. Измерение неэлектрических величин: конспект лекций. - Кстово: НВВИКУ, 1997. 54 с.

3. Цифровой измеритель скорости вращения. Описание изобретения к авторскому свидетельству RU 1075167, 1984.

4. Комплекс средств контроля дизеля КСКД 17.5. Техническое описание и инструкция по эксплуатации ЗУ2.008.006 ТО. 1994. С. 35-37.

5. Патент на изобретение №2659990 по заявке №2017123705 от 4 июля 2018 г., кл. G01P 3/54.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2018 |

|

RU2706198C1 |

| ЦИФРОВОЕ ЧЕТЫРЕХКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2017 |

|

RU2659990C1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| ЦИФРОВОЕ N-КАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2018 |

|

RU2685445C1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Устройство управления мобильным кормораздатчиком | 1988 |

|

SU1530152A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

Изобретение относится к средствам автоматизации и может быть использовано, в частности, в системах управления электроагрегатов генераторных с приводом от двигателя внутреннего сгорания. Технический эффект, заключающийся в расширении функциональных возможностей, достигается за счёт того, что повышается достоверность выходной информации путем введения функций диагностики измерительной части и каналов уставок реле при одинарных и бинарных сбоях и коррекции информации при сбоях по четырем каналам. 2 ил.

Четырехканальное цифровое реле с функцией реконструктивной диагностики, содержащее четыре приемных реле, с первого по восьмой формирователи коротких импульсов, дешифратор, первый и второй регистры памяти, блок памяти, элемент задержки, с первого по десятый логические элементы ИЛИ, с первого по шестой логические элементы И, с первого по восьмой логические элементы НЕ, выход первого из которых подключен к второму входу первого логического элемента И, а выход второго логического элемент НЕ подключен к второму входу второго логического элемента И, с первого по четвертый индикаторы состояния, причем к входу первого индикатора состояния подключен выход второго логического элемента ИЛИ, к входу второго индикатора состояния - выход четвертого логического элемента ИЛИ, а к входу четвертого индикатора состояния подключен выход десятого логического элемента ИЛИ, первый вход которого связан с восьмым выходом дешифратора и третьим входом первого логического элемента ИЛИ, второй вход - с девятым выходом дешифратора и вторым входом седьмого логического элемента ИЛИ, третий вход - с выходом второго логического элемента И, четвертым входом четвертого элемента ИЛИ и пятым входом первого логического элемента ИЛИ, четвертый вход - с выходом шестого логического элемента И, шестым входом первого логического элемента ИЛИ и четвертым входом девятого логического элемента ИЛИ, выход которого подключен к входу третьего индикатора состояния, а третий вход связан с выходом четвертого логического элемента И, третьим входом второго логического элемента ИЛИ и пятым входом пятого логического элемента ИЛИ, выход которого подключен к входу четвертого адреса блока памяти, а первый вход - к пятнадцатому выходу дешифратора, второй вход - к одиннадцатому выходу дешифратора и второму входу девятого логического элемента ИЛИ, третий вход - к тринадцатому выходу дешифратора и второму входу четвертого логического элемента ИЛИ, четвертый вход - к четырнадцатому выходу дешифратора и второму входу второго логического элемента ИЛИ, шестой вход - к выходу пятого логического элемента И, пятому входу второго логического элемента ИЛИ и пятому входу четвертого логического элемента ИЛИ, первый вход которого связан со вторым входом восьмого логического элемента ИЛИ и пятым выходом дешифратора, четвертый выход которого соединен со вторым входом первого логического элемента ИЛИ и первым входом девятого логического элемента ИЛИ, нулевой выход дешифратора - с первым входом первого логического элемента ИЛИ, первый выход - с первым входом седьмого логического элемента ИЛИ, второй выход - с первыми входами первого и третьего логических элементов И, третий выход - с первым входом третьего логического элемента ИЛИ, шестой выход - с третьим входом восьмого логического элемента ИЛИ и первым входом второго логического элемента ИЛИ, седьмой выход - с первым входом восьмого логического элемента ИЛИ, выход которого подключен к входу третьего адреса блока памяти, разряды выхода которого являются выходами реле, а вход нулевого адреса блока памяти соединен с выходом первого логического элемента ИЛИ, вход первого адреса - с выходом седьмого логического элемента ИЛИ, вход второго адреса - с выходом третьего логического элемента ИЛИ, второй вход которого связан с четвертым входом второго логического элемента ИЛИ и выходом третьего логического элемента И, второй вход которого связан со вторым входом четвертого логического элемента И, вторым входом пятого логического элемента И, входом первого логического элемента НЕ и первым разрядом выхода второго регистра памяти, второй разряд выхода которого подключен к входу второго логического элемента НЕ и третьему входу пятого логического элемента И, первый вход которого связан с двенадцатым выходом дешифратора и первым входом шестого логического элемента И, второй вход которого соединен с третьим входом второго логического элемента И и выходом седьмого логического элемента НЕ, а третий вход - с выходом восьмого логического элемента НЕ, вход которого связан с третьим входом четвертого логического элемента И и третьим разрядом выхода второго регистра памяти, четвертый разряд выхода которого подключен к входу седьмого логического элемента НЕ, а сбросовый вход второго регистра памяти - к шине СБРОС и сбросовому входу первого регистра памяти, вход записи которого соединен с выходом элемента задержки, разряды выхода - с соответствующими разрядами входа второго регистра памяти, а соответствующие разряды входа - с соответствующими разрядами входа дешифратора и выходами соответствующих приемных реле, кроме того выход первого приемного реле подключен к входу первого формирователя коротких импульсов и входу третьего логического элемента НЕ, выход которого соединен с входом второго формирователя коротких импульсов, связанного выходом с первым входом шестого логического элемента ИЛИ, второй вход которого подключен к выходу первого формирователя коротких импульсов, третий вход - к выходу четвертого формирователя коротких импульсов, вход которого соединен с выходом четвертого логического элемента НЕ, вход которого связан с выходом второго приемного реле и входом третьего формирователя коротких импульсов, выход которого подключен к четвертому входу шестого логического элемента ИЛИ, пятый вход которого соединен с выходом шестого формирователя коротких импульсов, соединенного входом с выходом пятого логического элемента НЕ, вход которого связан с выходом третьего приемного реле и входом пятого формирователя коротких импульсов, подключенного выходом к шестому входу шестого логического элемента ИЛИ, седьмой вход которого соединен с выходом восьмого формирователя коротких импульсов, соединенного входом с выходом шестого логического элемента НЕ, вход которого соединен с выходом четвертого приемного реле и входом седьмого формирователя коротких импульсов, выход которого подключен к восьмому входу шестого логического элемента ИЛИ, связанного выходом с входом записи второго регистра памяти и входом элемента задержки, кроме того выход первого логического элемента И подключен к четвертому входу первого логического элемента ИЛИ и третьему входу четвертого логического элемента ИЛИ, а десятый выход дешифратора соединен с первыми входами второго и четвертого логического элемента И, отличающееся тем, что с целью расширения функциональных возможностей путем углубления диагностики бинарных сбоев снабжено седьмым, восьмым, девятым и десятым логическим элементом И, третий вход которого связан с четвертым разрядом выхода второго регистра памяти, второй вход - с выходом первого логического элемента НЕ и вторыми входами седьмого и девятого логических элементов И, первый вход - с десятым выходом дешифратора, а выход - с четвертым входом третьегологического элемента ИЛИ, восьмым входом второго логического элемента ИЛИ и шестым входом десятого логического элемента ИЛИ, пятый вход которого соединен с шестым входом второго логического элемента ИЛИ, седьмым входом первого логического элемента ИЛИ и выходом седьмого логического элемента И, третий вход которого подключен к выходу седьмого логического элемента НЕ, а первый вход - к девятому выходу дешифратора и первым входам восьмого и девятого логического элемента И, выход которого соединен с третьим входом третьего логического элемента ИЛИ, седьмым входом второго логического элемента ИЛИ и шестым входом девятого логического элемента ИЛИ, пятый вход которого связан с шестым входом четвертого логического элемента ИЛИ, седьмым входом пятого логического элемента ИЛИ и выходу восьмого логического элемента И, второй вход которого подключен к второму разряду выхода второго регистра памяти, а третий вход - к третьему разряду выхода второго регистра памяти и к третьему входу девятого логического элемента И.

| Цифровой измеритель скорости вращения | 1981 |

|

SU1075167A1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| JP 11234888 A, 27.08.1999 | |||

| JP 57170234 A, 20.10.1982 | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

2019-11-26—Публикация

2018-12-24—Подача