Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны устройства сравнения двоичных чисел (см., например, третий снизу рис. в табл. 3.5 на стр. 103 в книге Справочник по цифровой вычислительной технике. Малиновский Б.Н., Александров В.Я., Боюн В.П. и др. / Под ред. Б.Н. Малиновского. Киев: Техника, 1974 г.), формирующие признак соотношения х2>х1, где х1,х2∈{0,1} - одноразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных устройств сравнения двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается сравнение n-разрядных двоичных чисел, задаваемых двоичными сигналами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство сравнения двоичных чисел (патент РФ 2330322, кл. G06F 7/00, 2008 г.), которое содержит элемент «Запрет», D-триггер и формирует признак соотношения X>Y, где X, Y - n-разрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется формирование признака соотношения X=Y, где X, Y - n-разрядные двоичные числа, задаваемые двоичными сигналами.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения формирования признаков соотношений X>Y и X=Y, где X, Y есть n-разрядные двоичные числа, задаваемые двоичными сигналами.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройстве сравнения двоичных чисел, содержащем элемент «Запрет» и D-триггер, особенность заключается в том, что в него дополнительно введены два элемента «Запрет», D-триггер и два элемента «Исключающее ИЛИ», причем инвертирующий, неинвертирующий входы j-го  элемента «Запрет» и первый, второй входы второго элемента «Исключающее ИЛИ» соединены соответственно с выходом первого элемента «Исключающее ИЛИ», неинвертирующим выходом (j-1)-го D-триггера и выходами первого, второго элементов «Запрет», а объединенные вход данных первого D-триггера, выход второго элемента «Исключающее ИЛИ» и объединенные вход данных второго D-триггера, выход третьего элемента «Запрет» образуют соответственно первый и второй выходы устройства сравнения двоичных чисел, первый, второй информационные и первый, второй управляющие входы которого подключены соответственно к объединенным неинвертирующему входу первого элемента «Запрет», второму входу первого элемента «Исключающее ИЛИ», объединенным инвертирующему входу первого элемента «Запрет», первому входу первого элемента «Исключающее ИЛИ» и объединенным входу сброса первого D-триггера, входу установки второго D-триггера, объединенным тактовым входам первого, второго D-триггеров.

элемента «Запрет» и первый, второй входы второго элемента «Исключающее ИЛИ» соединены соответственно с выходом первого элемента «Исключающее ИЛИ», неинвертирующим выходом (j-1)-го D-триггера и выходами первого, второго элементов «Запрет», а объединенные вход данных первого D-триггера, выход второго элемента «Исключающее ИЛИ» и объединенные вход данных второго D-триггера, выход третьего элемента «Запрет» образуют соответственно первый и второй выходы устройства сравнения двоичных чисел, первый, второй информационные и первый, второй управляющие входы которого подключены соответственно к объединенным неинвертирующему входу первого элемента «Запрет», второму входу первого элемента «Исключающее ИЛИ», объединенным инвертирующему входу первого элемента «Запрет», первому входу первого элемента «Исключающее ИЛИ» и объединенным входу сброса первого D-триггера, входу установки второго D-триггера, объединенным тактовым входам первого, второго D-триггеров.

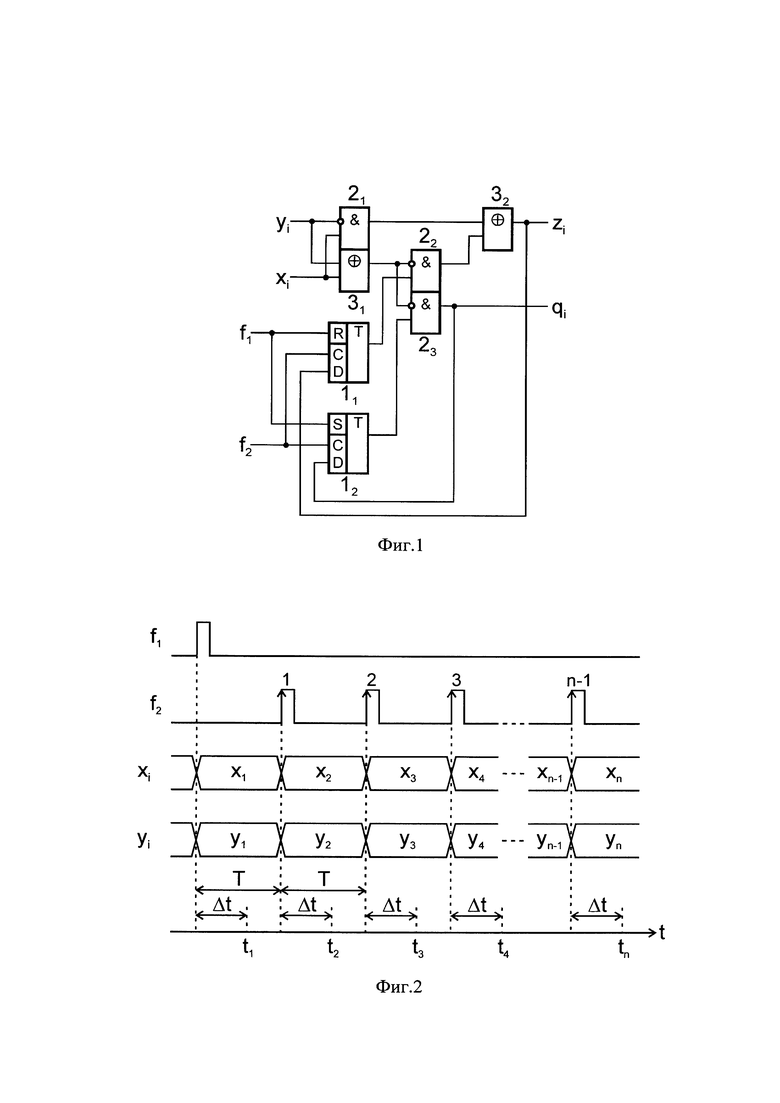

На фиг. 1 и фиг. 2 представлены соответственно схема предлагаемого устройства сравнения двоичных чисел и временные диаграммы, поясняющие принцип его работы.

Устройство сравнения двоичных чисел содержит D-триггеры 11, 12, элементы «Запрет» 21, 22, 23 и элементы «Исключающее ИЛИ» 31, 32, причем инвертирующий, неинвертирующий входы элемента 2j  и первый, второй входы элемента 32 соединены соответственно с выходом элемента 31, неинвертирующим выходом D-триггера 1j-1 и выходами элементов 21, 22, а объединенные вход данных D-триггера 11, выход элемента 32 и объединенные вход данных D-триггера 12, выход элемента 23 образуют соответственно первый и второй выходы устройства сравнения двоичных чисел, первый, второй информационные и первый, второй управляющие входы которого подключены соответственно к объединенным неинвертирующему входу элемента 21, второму входу элемента 31, объединенным инвертирующему входу элемента 21, первому входу элемента 31 и объединенным входу сброса D-триггера 11, входу установки D-триггера 12, объединенным тактовым входам D-триггеров 11, 12.

и первый, второй входы элемента 32 соединены соответственно с выходом элемента 31, неинвертирующим выходом D-триггера 1j-1 и выходами элементов 21, 22, а объединенные вход данных D-триггера 11, выход элемента 32 и объединенные вход данных D-триггера 12, выход элемента 23 образуют соответственно первый и второй выходы устройства сравнения двоичных чисел, первый, второй информационные и первый, второй управляющие входы которого подключены соответственно к объединенным неинвертирующему входу элемента 21, второму входу элемента 31, объединенным инвертирующему входу элемента 21, первому входу элемента 31 и объединенным входу сброса D-триггера 11, входу установки D-триггера 12, объединенным тактовым входам D-триггеров 11, 12.

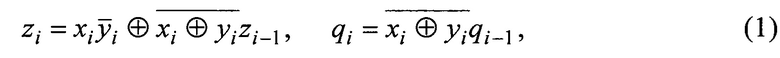

Работа предлагаемого устройства сравнения двоичных чисел осуществляется следующим образом. На его первый, второй управляющие входы подаются соответственно импульсные сигналы ƒ1, ƒ2∈{0,1} (фиг. 2), причем период Т сигнала ƒ2 должен удовлетворять условию Т>Δt, где Δt=max(τТр, τИск.ИЛИ)+τ3апрет+τИск.ИЛИ, а τТр и τ3апрет, τИск.ИЛИ есть длительности задержек, вносимых D-триггером и элементами «Запрет», «Исключающее ИЛИ». Синхронно с передним фронтом импульса сигнала ƒ1, передними фронтами первого, …, (n-1)-го импульсов сигнала ƒ2 на первый и второй информационные входы предлагаемого устройства последовательно подаются двоичные сигналы x1, …, xn∈{0,1} и y1, …, yn∈{0,1} соответственно (фиг. 2), которые задают подлежащие сравнению n-разрядные двоичные числа X и Y (хn, yn задают значения старших, а x1, y1 - младших разрядов). Тогда сигналы на первом, втором выходах предлагаемого устройства будут определяться рекуррентными выражениями

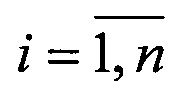

где  есть номер момента времени ti (фиг. 2); z0=0; q0=1. В представленных ниже таблицах приведены значения реализуемых выражениями (1) функций на всех возможных наборах значений их аргументов.

есть номер момента времени ti (фиг. 2); z0=0; q0=1. В представленных ниже таблицах приведены значения реализуемых выражениями (1) функций на всех возможных наборах значений их аргументов.

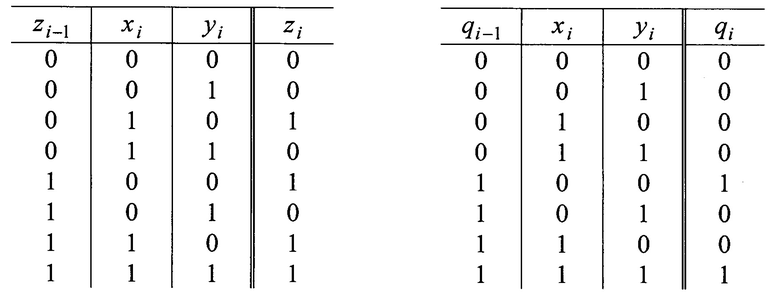

Анализ данных, приведенных в таблицах, позволяет заключить, что: 1) если xi<yi или xi=yi и zi-1=0, то zi=0; 2) если хi>yi или xi=yi и zi-1=1, то zi=1; 3) если qi-1=0 или qi-1=1 и хi≠yi, то qi=0; 4) если qi-1=1 и xi=yi, то qi=1. Таким образом, при i=n на первом, втором выходах предлагаемого устройства получим

,

,  .

.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство сравнения двоичных чисел обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает формирование признаков соотношений X>Y и X=Y, где X, Y есть n-разрядные двоичные числа, задаваемые двоичными сигналами.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2330322C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2020 |

|

RU2757823C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363036C1 |

| СЕЛЕКТОР ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2365975C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2021 |

|

RU2778675C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ ПЯТЬ | 2021 |

|

RU2762544C1 |

| УСТРОЙСТВО ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2770799C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2335797C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2841043C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ БОЛЬШЕГО ИЗ ДВУХ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363034C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом является обеспечение формирования признаков соотношений X>Y и X=Y. Устройство содержит два D-триггера, три элемента «Запрет» и два элемента «Исключающее ИЛИ». 2 ил., 2 табл.

Устройство сравнения двоичных чисел, содержащее элемент «Запрет» и D-триггер, отличающееся тем, что в него дополнительно введены два элемента «Запрет», D-триггер и два элемента «Исключающее ИЛИ», причем инвертирующий, неинвертирующий входы j-го ( ) элемента «Запрет» и первый, второй входы второго элемента «Исключающее ИЛИ» соединены соответственно с выходом первого элемента «Исключающее ИЛИ», неинвертирующим выходом (j-1)-го D-триггера и выходами первого, второго элементов «Запрет», а объединенные вход данных первого D-триггера, выход второго элемента «Исключающее ИЛИ» и объединенные вход данных второго D-триггера, выход третьего элемента «Запрет» образуют соответственно первый и второй выходы устройства сравнения двоичных чисел, первый, второй информационные и первый, второй управляющие входы которого подключены соответственно к объединенным неинвертирующему входу первого элемента «Запрет», второму входу первого элемента «Исключающее ИЛИ», объединенным инвертирующему входу первого элемента «Запрет», первому входу первого элемента «Исключающее ИЛИ» и объединенным входу сброса первого D-триггера, входу установки второго D-триггера, объединенным тактовым входам первого, второго D-триггеров.

) элемента «Запрет» и первый, второй входы второго элемента «Исключающее ИЛИ» соединены соответственно с выходом первого элемента «Исключающее ИЛИ», неинвертирующим выходом (j-1)-го D-триггера и выходами первого, второго элементов «Запрет», а объединенные вход данных первого D-триггера, выход второго элемента «Исключающее ИЛИ» и объединенные вход данных второго D-триггера, выход третьего элемента «Запрет» образуют соответственно первый и второй выходы устройства сравнения двоичных чисел, первый, второй информационные и первый, второй управляющие входы которого подключены соответственно к объединенным неинвертирующему входу первого элемента «Запрет», второму входу первого элемента «Исключающее ИЛИ», объединенным инвертирующему входу первого элемента «Запрет», первому входу первого элемента «Исключающее ИЛИ» и объединенным входу сброса первого D-триггера, входу установки второго D-триггера, объединенным тактовым входам первого, второго D-триггеров.

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2330322C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363037C1 |

| Устройство для сравнения двух @ -разрядных двоичных чисел | 1985 |

|

SU1254466A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| US 4012714 A, 15.03.1977. | |||

Авторы

Даты

2019-06-19—Публикация

2017-11-14—Подача