Изобретение относится к вычислительной технике и может быть использовано при построении средств автоматики, функциональных узлов систем управления и др.

Известны устройства деления двоичных чисел (см., например, нижний рис. в табл. 3.5 на стр. 103 в книге Справочник по цифровой вычислительной технике. Малиновский Б.Н., Александров В.Я., Боюн В.П. и др. / Под ред. Б.Н. Малиновского. Киев: Техника, 1974 г.), которые формируют двоичный код целой части частного двух одноразрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных устройств деления двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка двухразрядных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство деления двоичных чисел (рис. 2 на стр. 24 в книге Цифровые и аналоговые интегральные микросхемы: Справочник / С.В. Якубовский, Л.И. Ниссельсон, В.И. Кулешова и др.; Под ред. С.В. Якубовского. М.: Радио и связь, 1989 г.), которое содержит логический элемент и формирует двоичный код целой части частного двух одноразрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка двухразрядных двоичных чисел.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения формирования двоичного кода целой части частного двух двухразрядных двоичных чисел, задаваемых двоичными сигналами.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройстве деления двоичных чисел, содержащем логический элемент, особенность заключается в том, что в него дополнительно введены четыре логических элемента, причем с первого по четвертый и пятый логические элементы являются соответственно элементами «Запрет» и элементом «ИЛИ», инвертирующий и неинвертирующий входы первого элемента «Запрет» соединены соответственно с инвертирующими входами четвертого и второго элементов «Запрет», инвертирующий вход третьего и неинвертирующий вход четвертого элементов «Запрет» подключены соответственно к выходу второго и неинвертирующему входу третьего элементов «Запрет», а первый, второй входы и выход элемента «ИЛИ» соединены соответственно с выходами первого, третьего элементов «Запрет» и первым выходом устройства деления двоичных чисел, первый, третий, второй, четвертый входы и второй выход которого подключены соответственно к неинвертирующему, инвертирующему входам второго, инвертирующему, неинвертирующему входам и выходу четвертого элементов «Запрет».

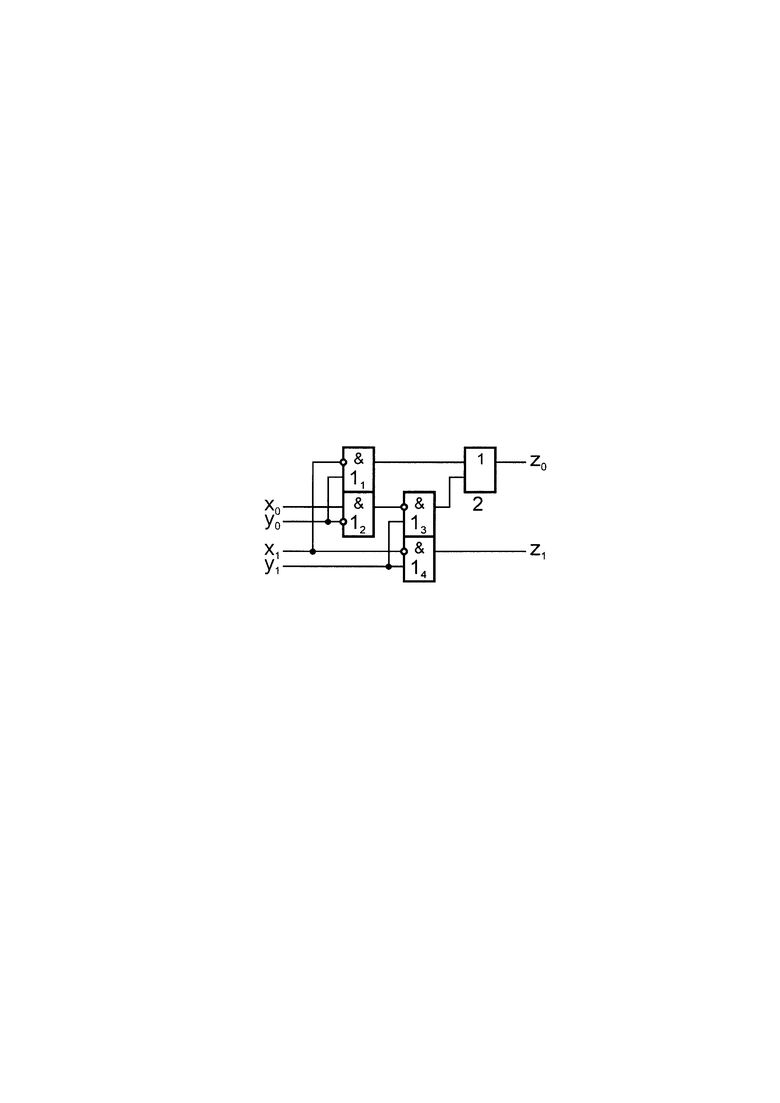

На чертеже представлена схема предлагаемого устройства деления двоичных чисел.

Устройство деления двоичных чисел содержит элементы «Запрет» 11, …, 14 и элемент «ИЛИ» 2, причем инвертирующий и неинвертирующий входы элемента 11 соединены соответственно с инвертирующими входами элементов 14 и 12, инвертирующий вход элемента 13 и неинвертирующий вход элемента 14 подключены соответственно к выходу элемента 12 и неинвертирующему входу элемента 13, а первый, второй входы и выход элемента 2 соединены соответственно с выходами элементов 11, 13 и первым выходом устройства деления двоичных чисел, первый, третий, второй, четвертый входы и второй выход которого подключены соответственно к неинвертирующему, инвертирующему входам элемента 12, инвертирующему, неинвертирующему входам и выходу элемента 14.

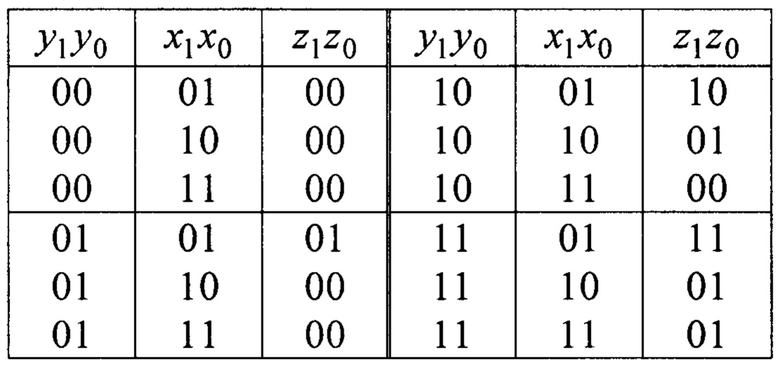

Работа предлагаемого устройства деления двоичных чисел осуществляется следующим образом. На его первый, второй и третий, четвертый входы подаются соответственно двоичные сигналы х0,х1∈{0,1} и у0,у1∈{0,1}, которые задают подлежащие обработке двухразрядные двоичные числа Х=х1х0, Y=y1y0, причем х1,у1 и х0,у0 определяют значения старших и младших разрядов соответственно. В представленной ниже таблице приведены значения выходных сигналов z0,zx предлагаемого устройства, полученные с учетом работы его элементов для всех разрешенных наборов значений сигналов х0,x1,у0,у1.

Согласно представленной таблицы имеем Z=[Y/X], где Z=z1z0 - двухразрядное двоичное число, задаваемое двоичными сигналами z0,z1∈{0,1} (z1 и z0 определяют значения старшего и младшего разрядов соответственно), [] - оператор выделения целой части.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство деления двоичных чисел обладает более широкими по сравнению с прототипом функциональными возможностями, так как формирует двоичный код целой части частного двух двухразрядных двоичных чисел, задаваемых двоичными сигналами.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СЕЛЕКЦИИ МАКСИМАЛЬНОГО ИЗ ДВУХ ДВОИЧНЫХ ЧИСЕЛ | 2005 |

|

RU2298219C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2021 |

|

RU2778675C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ ПЯТЬ | 2021 |

|

RU2762544C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВОИЧНЫХ ЧИСЕЛ | 2018 |

|

RU2678165C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВОИЧНЫХ ЧИСЕЛ | 2018 |

|

RU2681693C1 |

| СУММАТОР ПО МОДУЛЮ q | 2018 |

|

RU2702970C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2692050C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ СЕМЬ | 2021 |

|

RU2764707C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2330322C1 |

| СУММАТОР ПО МОДУЛЮ ПЯТЬ | 2018 |

|

RU2702969C1 |

Изобретение относится к области вычислительной техники и, в частности, может быть использовано при построении средств автоматики, функциональных узлов систем управления. Техническим результатом является обеспечение формирования двоичного кода целой части частного двух двухразрядных двоичных чисел, задаваемых двоичными сигналами. Технический результат заявляемого технического решения достигается тем, что в заявленном решении предусмотрен логический элемент, в который введены четыре логических элемента «Запрет» и элемент «ИЛИ», при этом инвертирующий и неинвертирующий входы первого элемента «Запрет» соединены соответственно с инвертирующими входами четвертого и второго элементов «Запрет», инвертирующий вход третьего и неинвертирующий вход четвертого элементов «Запрет» подключены соответственно к выходу второго и неинвертирующему входу третьего элементов «Запрет», а первый, второй входы и выход элемента «ИЛИ» соединены соответственно с выходами первого, третьего элементов «Запрет» и первым выходом устройства деления двоичных чисел, первый, третий, второй, четвертый входы и второй выход которого подключены соответственно к неинвертирующему, инвертирующему входам второго, инвертирующему, неинвертирующему входам и выходу четвертого элементов «Запрет». 1 ил.

Устройство деления двоичных чисел, содержащее логический элемент и отличающееся тем, что в него дополнительно введены четыре логических элемента, причем с первого по четвертый и пятый логические элементы являются соответственно элементами «Запрет» и элементом «ИЛИ», инвертирующий и неинвертирующий входы первого элемента «Запрет» соединены соответственно с инвертирующими входами четвертого и второго элементов «Запрет», инвертирующий вход третьего и неинвертирующий вход четвертого элементов «Запрет» подключены соответственно к выходу второго и неинвертирующему входу третьего элементов «Запрет», а первый, второй входы и выход элемента «ИЛИ» соединены соответственно с выходами первого, третьего элементов «Запрет» и первым выходом устройства деления двоичных чисел, первый, третий, второй, четвертый входы и второй выход которого подключены соответственно к неинвертирующему, инвертирующему входам второго, инвертирующему, неинвертирующему входам и выходу четвертого элементов «Запрет».

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| АНДРЕЕВ Д.В.: "Универсальные логические модули для обработки многозначных и континуальных данных", УлГТУ, 2010 | |||

| ЯКУБОВСКИЙ С.В | |||

| и др.: "Цифровые и аналоговые интегральные микросхемы: Справочник", Радио и связь, 1989 г | |||

| US 4707798 A, 17.11.1987. | |||

Авторы

Даты

2022-04-21—Публикация

2021-04-02—Подача