Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, выполненных на R-S триггерах.

Известен асинхронный R-S − триггер. [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. − М.: Высшая школа, 2004, с. 620, рис. 8.9, а], содержащий два логических элемента ИЛИ-НЕ.

Недостатком его является большое число используемых транзисторов, что усложняет и удорожает устройство. В частности, в каждом двухвходовом эмиттерном-связанном логическом элементе ИЛИ-НЕ [Манаев Е.И. Основы радиоэлектроники. -М.: Радио и связь, 1985, с.342, рис. 14.23] имеется пять транзисторов, тогда в обсуждаемом асинхронном R-S триггере содержится большое число транзисторов (десять), что приводит к его усложнению и удорожанию.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа триггер с дополнительной симметрией [Гольденберг Л.М., Импульсные и цифровые устройства. − М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и источники постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или к эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзистора, то это повысило бы нагрузочную способность триггера.

Задача, на решение которой направлено изобретение, состоит в упрощении и удишевлении триггерного асинхронного R-S триггера.

Это достигается тем, что в триггерный ассинхронный R-S триггер, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, последовательно соединённые первый резистор, первый транзистор (n-p-n) и второй резистор, свободный вывод первого резистора соединён с выходом источника питающего постоянного напряжения, другой вывод этого резистора соединён с коллектором первого транзистора, а эмиттер последнего соединён с одним из выводов второго резистора, также имеются последовательно соединённые третий резистор, второй транзистор (p-n-p) и четвёртый резистор, свободный вывод третьего резистора подключен к общему выходу источника питающего постоянного напряжения и первого резистора, другой вывод третьего резистора соединён с эмиттером второго транзистора, коллектор этого транзистора подключён к одному из выводов четвёртого резистора, а база соединена с общим выводом первого резистора и коллектора первого транзистора, база первого транзистора подключена к общему выводу коллектора второго транзистора и четвёртого резистора, свободный вывод последнего резистора подключён к свободному выводу второго резистора, введены три дополнительных (n-p-n) транзистора и два дополнительных резистора, а также определены входы и выход R-S триггера, первый дополнительный транзистор и первый дополнительный резистор между собой соединены последовательно, коллектор первого дополнительного транзистора соединён с общим выводом первого резистора и коллектора первого транзистора, а свободный вывод первого дополнительного резистора заземлён, вывод базы первого дополнительного транзистора образует вход S R-S триггера относительно «земли», также последовательно между собой включены второй дополнительный транзистор и второй дополнительный резистор, коллектор второго дополнительного транзистора соединён с общим выводом третьего резистора и эмиттера второго транзистора, а свободный вывод второго дополнительного резистора заземлён, вывод базы второго дополнительного транзистора образует вход R R-S триггера относительно «земли», коллектор третьего дополнительного транзистора подключен к общему выводу второго и четвёртого резисторов, база соединена с общим выводом второго дополнительного резистора и эмиттера второго дополнительного транзистора, а эмиттер заземлён, выход R-S триггера относительно «земли» образует общий вывод коллектора третьего дополнительного транзистора, второго и четвёртого резисторов.

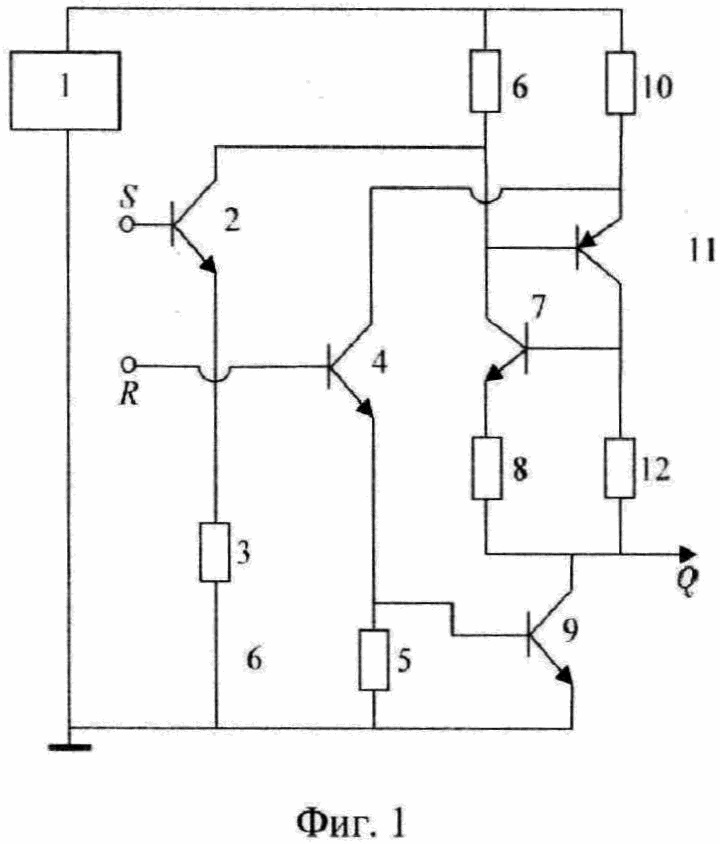

Сущность изобретения поясняется чертежом (фиг. 1).

В триггерном асинхронном R-S триггера общая шина (минусовая) источника 1 питающего постоянного напряжения заземлена. Между собой последовательно соединены транзистор 2 (n-p-n) и резистор 3. Свободный вывод последнего заземлён, а вывод базы транзистора 2 образует вход S R-S триггера относительно «земли». Последовательно между собой включены транзистор 4 (n-p-n) и резистор 5, свободный вывод которого заземлён. Вывод базы транзистора 4 образует вход R R-S триггера относительно «земли». Между собой последовательно соединены резистор 6, транзистор 7 (n-p-n), резистор 8 и транзистор 9 (n-p-n). Свободный вывод резистора 6 подключен к выходу (плюсовой вывод) источника 1 питающего постоянного напряжения, а другой вывод его соединён с коллектором транзистора 7. Общий вывод этих двух последних элементов подключен к коллектору транзистора 2. Эмиттер транзистор 9 заземлён, а его база подключена к общему выводу резистора 5 и эмиттера транзистора 4. Также последовательно между собой соединены резистор 10, транзистор 11 (p-n-p) и резистор 12. Свободный вывод резистора 10 подключен к общему выводу резистора 6 и выхода источника 1 питающего постоянного напряжения, а другой вывод резистора 10 соединён с эмиттером транзистора 11. Общий вывод этих двух последних элементов подключен к коллектору транзистора 4. База транзистора 11 соединена с общим выводом резистора 6 и коллекторов транзисторов 2 и 7, а база транзистора 7 − с общим выводом резистора 12 и коллектора транзистора 11. Выход относительно «земли» R-S триггера образует общий вывод коллектора транзистора 9 и резисторов 8 и 12. Часть схемы на фиг. 1 на транзисторах 7 и 11 образует известный триггер на транзисторах противоположного типа проводимости.

Триггерный асинхронный R-S триггер работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень − уровень логического нуля соответствует значениям напряжения в районе нуля или в районе ближе к нулю, высокий уровень − уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко четыре вольта).

Работа асинхронного R-S триггера отображается известной табл.1, где  и

и  − условное отображение сигналов на входах R-S триггера в данный момент времени,

− условное отображение сигналов на входах R-S триггера в данный момент времени,  − условное отображение состояния триггера в последующее время (состояние на выходе), N − номер по порядку.

− условное отображение состояния триггера в последующее время (состояние на выходе), N − номер по порядку.

При комбинации входных сигналов, соответствующих первой строке табл. 1, малое значение напряжения на входе R определяет малое значение силы электрического тока через транзистор 4, которое не влияет на состояние триггера на транзисторах 7 и 11 (реально почти не влияет или слабо влияет). Существенное значение напряжения на входе S (больше, чем на входе R) вызывает повышенную силу электрического тока через транзистор 2 и соответственно через резистор 6. Напряжение на этом резисторе минусом приложено к базе p-n-p транзистора 11, а плюсом к его эмиттеру через резистор 10. Значение напряжения на резисторе 6 по абсолютной величине должно быть больше порогового напряжения транзистора 11. Такое неравенство и требующийся запас по его выполнению обеспечивается значением сопротивления резистора 3. В результате транзистор 11 проводит электрический ток, напряжение на резисторе 12 плюсом приложено к базе транзистора 7, больше его порогового напряжения и этот транзистор тоже проводит электрический ток. Электрический ток двух транзисторов 7 и 11 замыкается на подключенную к выходу нагрузку и обеспечивает на ней высокий уровень напряжения. На транзистор 9 замыкается весьма малое значение силы электрического тока, так как сила электрического тока через транзистор 4 мала и значение напряжения на резисторе 5 и соответственно на базе транзистора 9 в районе порогового напряжения.

При комбинации входных сигналов, соответствующих второй строчке табл. 1, малое значение напряжения на входе S определяет малое значение силы электрического тока через транзистор 2, которое не влияет на состояние триггера на транзисторах 7 и 11. Существенно большее значение напряжения на входе R вызывает повышенную силу электрического тока через транзистор 4 и соответственно через резистор 10. Напряжение на этом резисторе минусом приложено к эмиттеру (p-n-p) транзистора 11, а плюсом к его базе через резистор 6. Значение напряжения на резисторе 10 должно быть достаточным для существенного уменьшения силы электрического тока через транзистор 11. Это обеспечивается значением сопротивления резистора 5, значением этого же сопротивления обеспечивается требующийся запас для выполнения приведённого условия. Тогда значение силы электрического тока через транзистор 11 находится в районе нуля и значение напряжения на резисторе 12 тоже имеет малое значение. Оно прикладывается к базе транзистора 7, его состояние находится в районе порогового напряжения, и сила электрического тока через него имеет весьма малое значение. В результате сумма силы электрического тока транзисторов 7 и 10 имеет малое значение и значение выходного напряжения R-S триггера находится в районе нуля. Повышенное значение силы электрического тока, через транзистор 4 и соответственно через резистор 5 обеспечивает повышение значения напряжения на этом резисторе и на базе транзистора 9 и через него может протекать номинальный ток значительно больший, чем при предыдущих комбинации входных сигналов. Тогда через этот транзистор разряжается эквивалентная паразитная емкость (выходная емкость R-S триггера и входная ёмкость нагрузки), время разряда уменьшается и не ухудшается быстродействие схемы.

При комбинации входных сигналов, соответствующих третьей строчки табл. 1, малые значения напряжения на входа R и S определяет малые значения силы электрического тока через транзисторы 2 и 4. Они не влияют на состояние триггера на транзисторах противоположного типа проводимости 7 и 11 и не изменяют его состояние. Тогда не изменяется напряжение на выходе R-S триггера, и оно соответствует предыдущей комбинации входных сигналов. То есть это хранение информации.

Комбинация сигналов в четвёртой строке табл. 1, как в существующих схемах асинхронных R-S триггеров, так и в рассматриваемой схеме, является запрещённой комбинацией входных сигналов.

Можно обратить внимание, что при переходе от комбинации входных сигналов в первой строчке табл. 1 к комбинации сигналов во второй строчке, образно говоря, воздействие на уменьшение силы электрического тока в транзисторах 7 и 11 триггера на транзисторах противоположного типа проводимости возрастает, а воздействие на повышение силы электрического тока в транзисторах 7 и 11 уменьшается. Такой прогресс способствует изменению состояния триггера на транзисторах противоположного типа проводимости и установке на выходе R-S триггера низкого уровня напряжения (логический нуль). При переходе от комбинации входных сигналов во второй строчке табл. 1 к комбинации входных сигналов в первой строчке наоборот воздействие на увеличение силы электрического тока в транзисторах 7 и 11 возрастает, а воздействие на уменьшение силы электрического тока в этих транзисторах ослабляется. Это тоже способствует изменению состояния триггера на транзисторах противоположного типа проводимости 7 и 11 и установке на выходе R-S триггера высокого уровня напряжения (логическая единица).

В рассмотренном триггерном асинхронном R-S триггере сила электрического тока внешней нагрузки почти равна сумме силы токов двух транзисторов 7 и 11, то есть двух из имеющихся пяти транзисторов, что повышает нагрузочную способность этого триггера. В приведённом выше аналоге электрический ток нагрузки формирует только один из имеющихся транзисторов.

Таким образом, рассмотренная схема упрощает удишевляет асинхронный R-S триггер. В ней пять транзисторов, а, в частности, в приведённом выше аналоге имеется десять транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный асинхронный Т триггер | 2020 |

|

RU2726848C1 |

| Триггерный двухступенчатый R-S триггер | 2019 |

|

RU2721386C1 |

| Триггерный синхронный R-S триггер | 2018 |

|

RU2692041C1 |

| Триггерный синхронный R-S триггер | 2018 |

|

RU2731438C2 |

| Триггерный двухступенчатый D триггер | 2019 |

|

RU2714106C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

| Триггерный логический элемент И/И-НЕ | 2020 |

|

RU2727613C1 |

| Триггерный синхронный D триггер | 2018 |

|

RU2692422C1 |

| Триггерный сумматор по модулю два | 2018 |

|

RU2700195C1 |

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, выполненных на R-S триггерах. Технический результат - упрощение триггерного асинхронного R-S триггера. Для этого предложен триггерный асинхронный R-S триггер, который содержит пять транзисторов, шесть резисторов и источник питающего постоянного напряжения. Новым является то, что в него введены три дополнительных (n-p-n) транзистора и два дополнительных резистора, а также определены входы и выход R-S триггера. 1 ил., 1 табл.

Триггерный асинхронный R-S триггер, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, последовательно соединённые первый резистор, первый транзистор (n-p-n) и второй резистор, свободный вывод первого резистора соединён с выходом источника питающего постоянного напряжения, другой вывод этого резистора соединён с коллектором первого транзистора, а эмиттер последнего соединён с одним из выводов второго резистора, также имеются последовательно соединённые третий резистор, второй транзистор (p-n-p) и четвёртый резистор, свободный вывод третьего резистора подключен к общему выходу источника питающего постоянного напряжения и первого резистора, другой вывод третьего резистора соединён с эмиттером второго транзистора, коллектор этого транзистора подключён к одному из выводов четвёртого резистора, а база соединена с общим выводом первого резистора и коллектора первого транзистора, база первого транзистора подключена к общему выводу коллектора второго транзистора и четвёртого резистора, свободный вывод последнего резистора подключён к свободному выводу второго резистора, отличающийся тем, что в него введены три дополнительных (n-p-n) транзистора и два дополнительных резистора, а также определены входы и выход R-S триггера, первый дополнительный транзистор и первый дополнительный резистор между собой соединены последовательно, коллектор первого дополнительного транзистора соединён с общим выводом первого резистора и коллектора первого транзистора, а свободный вывод первого дополнительного резистора заземлён, вывод базы первого дополнительного транзистора образует вход S R-S триггера относительно «земли», также последовательно между собой включены второй дополнительный транзистор и второй дополнительный резистор, коллектор второго дополнительного транзистора соединён с общим выводом третьего резистора и эмиттера второго транзистора, а свободный вывод второго дополнительного резистора заземлён, вывод базы второго дополнительного транзистора образует вход R R-S триггера относительно «земли», коллектор третьего дополнительного транзистора подключен к общему выводу второго и четвёртого резисторов, база соединена с общим выводом второго дополнительного резистора и эмиттера второго дополнительного транзистора, а эмиттер заземлён, выход R-S триггера относительно «земли» образует общий вывод коллектора третьего дополнительного транзистора, второго и четвёртого резисторов.

| ГОЛЬДЕНБЕРГ Л.М., Импульсные и цифровые устройства, Москва, Связь, 1973, стр | |||

| ТЕЛЕФОННЫЙ АППАРАТ, ОТЗЫВАЮЩИЙСЯ ТОЛЬКО НА ВХОДЯЩИЕ ТОКИ | 1921 |

|

SU275A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| RS-ТРИГГЕР | 2015 |

|

RU2615069C1 |

| US 8232825 B2, 31.07.2012. | |||

Авторы

Даты

2019-07-02—Публикация

2018-10-09—Подача