Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, в сумматорах цифр, в арифметико-логических устройствах.

Известен сумматор по модулю два [Потёмкин И.С. Функциональные узлы цифровой автоматики. − М.: Энергоатомиздат, 1988, стр. 3, рис. 1.10, д], содержащий четыре логических элемента И-НЕ.

Недостатком его является большое число используемых транзисторов, что усложняет и удорожает устройство. Например, в каждом транзисторно- транзисторном логическом элементе И-НЕ имеется четыре транзистора и один диод, тогда в сумматоре по модулю два содержатся шестнадцать транзисторов и четыре диода, что приводит к его усложнению и удорожанию.

Известен триггер с дополнительной симметрией [Гольденберг Л.М., Импульсные и цифровые устройства. − М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и источники постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или к эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзистора, то это повысило бы нагрузочную способность триггера.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа логический элемент И-НЕ [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 593, рис. 8.5, а], содержащий четыре транзистора, четыре резистора и диод.

Сумматор по модулю два, выполненный на таких логических элементах, содержит большое число транзисторов, что усложняет и удорожает устройство и в этом заключается недостаток. Приведённый логический элемент содержит четыре транзистора и диод, отсюда сумматор по модулю два включает в себя шестнадцать транзисторов и четыре диода. Имеется возможность существенно уменьшить их количество.

Задача, на решение которой направлено изобретение, состоит в упрощении и удишевлении сумматора по модулю два.

Это достигается тем, что в триггерный сумматор по модулю два, содержащий источник питающего постоянного напряжения, общая шина (минусовая) которого заземлена, первый резистор, включенный между выходом (плюсовая шина) питающего источника и базой первого двухэмиттерного транзистора (n-p-n), эмиттеры которого образуют входы логического элемента относительно «земли», последовательно соединённые второй резистор, второй транзистор (n-p-n) и третий резистор, свободный вывод второго резистора соединён с выходом питающего источника, база второго транзистора соединена с коллектором первого транзистора, а свободный вывод третьего резистора заземлен, также имеются последовательно соединённые четвёртый резистор и третий транзистор (n-p-n), свободный вывод четвёртого резистора соединён с выходом питающего источника, введены три дополнительных транзистора и пять дополнительных резисторов, первый и второй дополнительные транзисторы (оба n-p-n) включены между собой параллельно (общий вывод образуют их коллекторы и общий вывод образуют их эмиттеры), базы этих транзисторов соединены со входами триггерного сумматора соответственно, между общим выводом эмиттеров и «землёй» включен первый дополнительный резистор, общий вывод коллекторов соединён с общим выводом имеющегося четвёртого резистора и коллектора имеющегося третьего транзистора, эмиттер третьего дополнительного транзистора (p-n-p) подключен к общему выводу имеющегося второго резистора и коллектора имеющегося второго транзистора, второй дополнительный резистор включен между «землёй» и общим выводом имеющегося второго резистора, коллектора имеющегося второго транзистора и эмиттера третьего дополнительного транзистора, база третьего дополнительного транзистора соединена с общим выводом имеющегося четвёртого резистора, коллектора имеющегося третьего транзистора и коллекторов первого и второго дополнительных транзисторов, третий и четвёртый дополнительные резисторы между собой включены последовательно, свободный вывод третьего дополнительного резистора подключен к коллектору третьего дополнительного транзистора, а свободный вывод четвёртого дополнительного резистора заземлён, база имеющегося третьего транзистора соединена с общим выводом коллектора третьего дополнительного транзистора и третьего дополнительного резистора, пятый дополнительный резистор включен между эмиттером третьего имеющегося транзистора и общим выводом третьего и четвёртого дополнительных резисторов, выход сумматора по модулю два относительно «земли» образует общий вывод дополнительных третьего, четвертого и пятого резисторов.

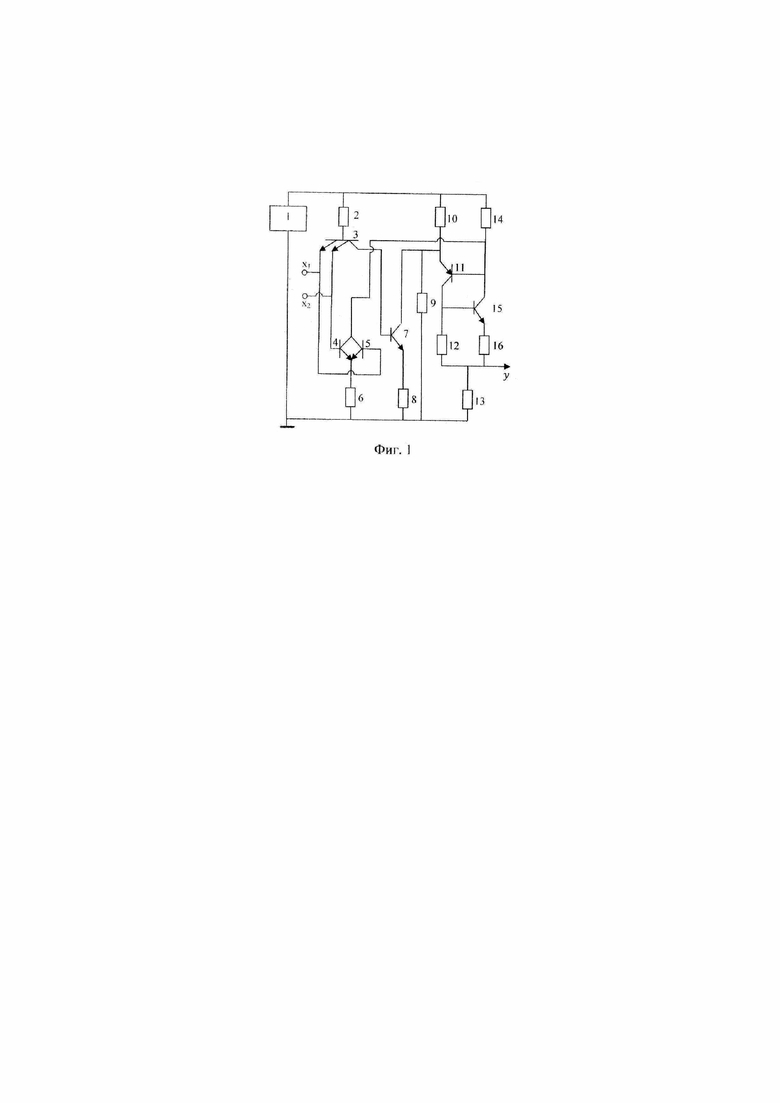

Сущность изобретения поясняется чертежом (фиг. 1).

В триггерном сумматоре по модулю два общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена, а плюсовой вывод выхода соединён с одним из выводов резистора 2. Другой его вывод подключен к базе двухэмиттерного n-p-n транзистора 3. Два вывода двух эмиттеров этого транзистора образуют два входа относительно «земли» триггерного сумматора по модулю два. Также эти два вывода соединены соответственно с базами n-p-n транзисторов 4 и 5. Эмиттеры транзисторов 4 и 5 образуют общий вывод, к которому подключен один из выводов резистора 6, другой вывод его заземлён. Коллектор транзистора 3 соединён с базой n-p-n транзистора 7, а эмиттер последнего − с одним из выводов резистора 8, другой вывод которого заземлён. Резистор 9 включен между «землёй» и коллектором транзистора 7. Между собой последовательно соединены резистор 10, p-n-p транзистор 11, резистор 12 и резистор 13. Свободный вывод резистора 10 подключен к общему выводу резистора 2 и выхода источника 1 питающего постоянного напряжения. Другой вывод резистора 10 соединён с эмиттером транзистора 11, тогда с его коллектором соединён резистор 12. Свободный вывод резистора 13 заземлен. Общий вывод резистора 9 и коллектора транзистора 7 подключен к общему выводу резистора 10 и эмиттера транзистора 11. Между собой последовательно включены резистор 14, n-p-n транзистор 15 и резистор 16. Свободный вывод резистора 14 соединён с общим выводом резистора 2, резистора 10 и выхода источника 1. Общий вывод коллекторов транзисторов 4 и 5 подключен к общему выводу резистора 14 и коллектора транзистора 15, и общий вывод четырёх последних элементов соединён с базой транзистора 11. Свободный вывод резистора 16 соединён с общим выводом резистора 12 и 13. Выход триггерного сумматора по модулю два относительно «земли» образует общий вывод резисторов 12, 16 и 13. Часть схемы на фиг. 1 на транзисторах 11 и 15 является триггером на транзисторах противоположного типа проводимости.

Триггерный сумматор по модулю два работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень − уровень логического нуля соответствует значениям напряжения в районе нуля, высокий уровень − уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко четыре вольта). Работа сумматора по модулю два отображается таблицей 1 (табл. 1). В соответствии с её первой строчкой на оба входа сумматора (х1 и х2) и на базы n-p-n транзисторов 4 и 5 поступают низкие уровни напряжения. Эти уровни напряжения не превышают значения пороговых напряжений названных двух транзисторов, и они закрыты. Оба базо-эмиттерных перехода n-p-n транзистора 3 открыты и на них выделяются малые значения напряжения, как на диодах в открытом состоянии. Базо-коллекторный переход этого транзистора тоже открыт, и в результате на базе

п-p-n транзистора 7 действует низкий уровень напряжения, который не превышает значение порогового напряжения, и транзистор закрыт. В итоге от источника питания 1 электрический ток замыкается через последовательно соединённые резисторы 10 и 9, и напряжение с резистора 10 минусом приложено к эмиттеру p-n-p транзистора 11, а плюсом − к его базе через резистор 14. Такое напряжение поддерживает транзистор 11 закрытом состоянии. Его пороговое напряжение тоже дополнительно способствует закрытому состоянию транзистора. С учётом изменения значений входных напряжений сумматора, дрейфа значений параметров элементов схемы и нестабильности питающего постоянного напряжения источника 1 значение сопротивления резистора 9 позволяет получать требующийся запас по обеспечению закрытого состояния транзистора 11. Нулевое значение силы электрического тока транзистора 11 создаёт на резисторе 12 нулевое значение напряжения. Оно меньше порогового напряжения п-p-n транзистора 15, и он закрыт. В результате выходное напряжение сумматора по модулю два равно нулю (у=0, табл. 1).

В соответствии со второй и третьей строчкой табл. 1 один из двух p-n базо-эмиттерных переходов (диод) транзистора 3 открыт, на базе его малое значение напряжения. Базо-коллекторный переход этого транзистора тоже открыт, на базе транзистора 7 низкий уровень напряжения, и он закрыт. На базу одного из двух транзисторов 4 или 5 поступает высокий уровень напряжения и этот транзистор открыт. Его электрический ток создаёт на резисторе 14 напряжение, которое минусом приложено к базе p-n-p транзистора 11, по абсолютной величине превышает сумму порогового напряжения и напряжения на резисторе 10 и поддерживает его в открытом состоянии. Значение сопротивления резистора 6 позволяет получить требующийся запас по обеспечению открытого состояния транзистора 11. Его электрический ток создаёт на транзисторе 12 напряжение, которое плюсом приложено к базе п-p-n транзистора 15, превышает пороговое напряжение и поддерживает этот транзистор в открытом состоянии. Электрические токи транзисторов 11 и 15 замыкаются на нагрузку и обеспечивают на выходе высокий уровень напряжения (у=1, табл. 1).

Четвёртая строка табл. 1 определяет, что на оба входа (х1 и х2) воздействуют высокие уровни напряжения, которые поддерживают транзисторы 4 и 5 в открытом состоянии. Электрические токи их проходят через резистор 14, создают на нём падение напряжения

где

где

где

Таким образом, в приведённом триггерном сумматоре по модулю два шесть транзисторов, в известных решениях, например, в первом аналоге их больше, свыше чем в два раза. Это упрощает и удишевляет устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И/И-НЕ | 2020 |

|

RU2727613C1 |

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

| Триггерный асинхронный Т триггер | 2020 |

|

RU2726848C1 |

| Триггерный двухступенчатый R-S триггер | 2019 |

|

RU2721386C1 |

| Триггерный логический элемент И | 2019 |

|

RU2728954C1 |

| Триггерный двухступенчатый D триггер | 2019 |

|

RU2714106C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2020 |

|

RU2726853C1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2021 |

|

RU2760206C1 |

| Триггерный логический элемент ИЛИ-НЕ | 2018 |

|

RU2710937C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

Изобретение относится к области цифровой схемотехники, автоматики и промышленной электроники и может быть использовано в блоках вычислительной техники, сумматорах, арифметико-логических устройствах. Техническим результатом является упрощение устройства. Устройство содержит шесть транзисторов, девять резисторов и источник питающего постоянного напряжения. 1 ил., 1 табл.

Триггерный сумматор по модулю два, содержащий источник питающего постоянного напряжения, общая шина (минусовая) которого заземлена, первый резистор, включенный между выходом (плюсовая шина) питающего источника и базой первого двухэмиттерного транзистора (n-p-n), эмиттеры которого образуют входы логического элемента относительно «земли», последовательно соединённые второй резистор, второй транзистор (n-p-n) и третий резистор, свободный вывод второго резистора соединён с выходом питающего источника, база второго транзистора соединена с коллектором первого транзистора, а свободный вывод третьего резистора заземлен, также имеются последовательно соединённые четвёртый резистор и третий транзистор (n-p-n), свободный вывод четвёртого резистора соединён с выходом питающего источника, отличающийся тем, что в него введены три дополнительных транзистора и пять дополнительных резисторов, первый и второй дополнительные транзисторы (оба n-p-n) включены между собой параллельно (общий вывод образуют их коллекторы и общий вывод образуют их эмиттеры), базы этих транзисторов соединены со входами триггерного сумматора соответственно, между общим выводом эмиттеров и «землёй» включен первый дополнительный резистор, общий вывод коллекторов соединён с общим выводом имеющегося четвёртого резистора и коллектора имеющегося третьего транзистора, эмиттер третьего дополнительного транзистора (p-n-p) подключен к общему выводу имеющегося второго резистора и коллектора имеющегося второго транзистора, второй дополнительный резистор включен между «землёй» и общим выводом имеющегося второго резистора, коллектора имеющегося второго транзистора и эмиттера третьего дополнительного транзистора, база третьего дополнительного транзистора соединена с общим выводом имеющегося четвёртого резистора, коллектора имеющегося третьего транзистора и коллекторов первого и второго дополнительных транзисторов, третий и четвёртый дополнительные резисторы между собой включены последовательно, свободный вывод третьего дополнительного резистора подключен к коллектору третьего дополнительного транзистора, а свободный вывод четвёртого дополнительного резистора заземлён, база имеющегося третьего транзистора соединена с общим выводом коллектора третьего дополнительного транзистора и третьего дополнительного резистора, пятый дополнительный резистор включен между эмиттером третьего имеющегося транзистора и общим выводом третьего и четвёртого дополнительных резисторов, выход сумматора по модулю два относительно «земли» образует общий вывод дополнительных третьего, четвертого и пятого резисторов.

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546078C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546082C1 |

| US 4803649 A, 07.02.1989 | |||

| US 4054788 A, 18.10.1977. | |||

Авторы

Даты

2019-09-13—Публикация

2018-10-31—Подача