Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известен логический элемент ИЛИ/ИЛИ-НЕ [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. – М.: Высшая школа, 2004, стр. 605 рис.8.12, а, б] содержащий шесть транзисторов, семь резисторов, два диода и два источника постоянного напряжения. Схема логического элемента имеет два выхода, один из них соответствует реализации логической операции ИЛИ, другой – логической операции ИЛИ-НЕ.

Недостаток его заключается в том, что у него малая нагрузочная способность. Электрический ток только одного транзистора формирует электрический ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих ток нагрузки, то это бы привело к увеличению максимальной силы электрического тока внешней нагрузки логического элемента и в результате к повышению нагрузочной способности.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа логический элемент И/И-НЕ [Ямпольский В.С. Основы автоматики и электронно-вычислительной техники. - М.: Просвещение, 1991, стр. 74, рис. 3.5], содержащий четыре транзистора, четыре резистора, один диод и источник питающего постоянного напряжения.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного транзистора формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это бы привело к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению нагрузочной способности.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента И/И-НЕ.

Это достигается тем, что в триггерный логический элемент И/И-НЕ, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, первый резистор, один из выводов которого подключён к выходу (плюсовой вывод) питающего источника, первый транзистор (n-p-n), база которого подсоединена к свободному выводу первого резистора, транзистор является двухэмиттерным, вывод каждого эмиттера его образуют относительно «земли» два входа  и

и  логического элемента, последовательно включённые второй резистор, второй транзисторов (n-p-n) и третий резистор, свободный вывод второго резистора подсоединён к общему выводу первого резистора и выхода питающего источника, база второго транзистора подключена к коллектору первого транзистора, а свободный вывод третьего резистора заземлён, последовательно включённые четвёртый резистор и третий транзистор (n-p-n), свободный вывод четвёртого резистора соединён с общим выводом первого, второго резисторов и выхода питающего источника, четвёртый транзистор (n-p-n), эмиттер которого заземлён, введены четыре дополнительных транзистора и восемь дополнительных резисторов, последовательно между собой включены первый дополнительный транзистор (n-p-n) и первый дополнительный резистор, коллектор первого дополнительного транзистора подсоединён к общему выводу второго резистора и коллектора второго транзистора, последовательно включены второй дополнительный резистор, второй дополнительный транзистор (p-n-p) и третий дополнительный резистор, свободный вывод второго дополнительного резистора подсоединён к общему выводу первого, второго, четвёртого резисторов и выхода питающего источника, база этого транзистора подключена к общему выводу второго резистора и коллекторов второго и дополнительного первого транзисторов, общий вывод коллектора второго дополнительного транзистора и третьего дополнительного резистора соединён с базой дополнительного первого транзистора, а свободный вывод третьего дополнительного резистора - со свободным выводом первого дополнительного резистора, общий вывод последних резисторов образует относительно «земли» первый выход

логического элемента, последовательно включённые второй резистор, второй транзисторов (n-p-n) и третий резистор, свободный вывод второго резистора подсоединён к общему выводу первого резистора и выхода питающего источника, база второго транзистора подключена к коллектору первого транзистора, а свободный вывод третьего резистора заземлён, последовательно включённые четвёртый резистор и третий транзистор (n-p-n), свободный вывод четвёртого резистора соединён с общим выводом первого, второго резисторов и выхода питающего источника, четвёртый транзистор (n-p-n), эмиттер которого заземлён, введены четыре дополнительных транзистора и восемь дополнительных резисторов, последовательно между собой включены первый дополнительный транзистор (n-p-n) и первый дополнительный резистор, коллектор первого дополнительного транзистора подсоединён к общему выводу второго резистора и коллектора второго транзистора, последовательно включены второй дополнительный резистор, второй дополнительный транзистор (p-n-p) и третий дополнительный резистор, свободный вывод второго дополнительного резистора подсоединён к общему выводу первого, второго, четвёртого резисторов и выхода питающего источника, база этого транзистора подключена к общему выводу второго резистора и коллекторов второго и дополнительного первого транзисторов, общий вывод коллектора второго дополнительного транзистора и третьего дополнительного резистора соединён с базой дополнительного первого транзистора, а свободный вывод третьего дополнительного резистора - со свободным выводом первого дополнительного резистора, общий вывод последних резисторов образует относительно «земли» первый выход  (выход И), последовательно включены третий дополнительный транзистор (p-n-p) и четвёртый дополнительный резистор, эмиттер транзистора подсоединён к общему выводу второго дополнительного резистора и эмиттера второго дополнительного транзистора, база третьего дополнительного транзистора подключена к общему выводу четвёртого резистора и коллектора третьего транзистора, общий вывод четвёртого дополнительного резистора и коллектора третьего дополнительного транзистора соединён с базой третьего транзистора, пятый дополнительный резистор включён между свободным выводом четвёртого дополнительного резистора и эмиттером третьего транзистора, общий вывод четвертого и пятого дополнительных резисторов образует относительно «земли» второй выход

(выход И), последовательно включены третий дополнительный транзистор (p-n-p) и четвёртый дополнительный резистор, эмиттер транзистора подсоединён к общему выводу второго дополнительного резистора и эмиттера второго дополнительного транзистора, база третьего дополнительного транзистора подключена к общему выводу четвёртого резистора и коллектора третьего транзистора, общий вывод четвёртого дополнительного резистора и коллектора третьего дополнительного транзистора соединён с базой третьего транзистора, пятый дополнительный резистор включён между свободным выводом четвёртого дополнительного резистора и эмиттером третьего транзистора, общий вывод четвертого и пятого дополнительных резисторов образует относительно «земли» второй выход  (выход И-НЕ) логического элемента, шестой дополнительный резистор включён между «землёй» и общим выводом четвёртого резистора, коллектора третьего резистора и базой третьего дополнительного транзистора, четвёртый дополнительный (n-p-n) транзистор включён между «землёй» и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента, седьмой дополнительный резистор включён между базой четвёртого дополнительного транзистора и общим выводом четвёртого, пятого дополнительных резисторов и второго выхода логического элемента, восьмой дополнительный резистор включён между базой четвёртого транзистора и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента.

(выход И-НЕ) логического элемента, шестой дополнительный резистор включён между «землёй» и общим выводом четвёртого резистора, коллектора третьего резистора и базой третьего дополнительного транзистора, четвёртый дополнительный (n-p-n) транзистор включён между «землёй» и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента, седьмой дополнительный резистор включён между базой четвёртого дополнительного транзистора и общим выводом четвёртого, пятого дополнительных резисторов и второго выхода логического элемента, восьмой дополнительный резистор включён между базой четвёртого транзистора и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента.

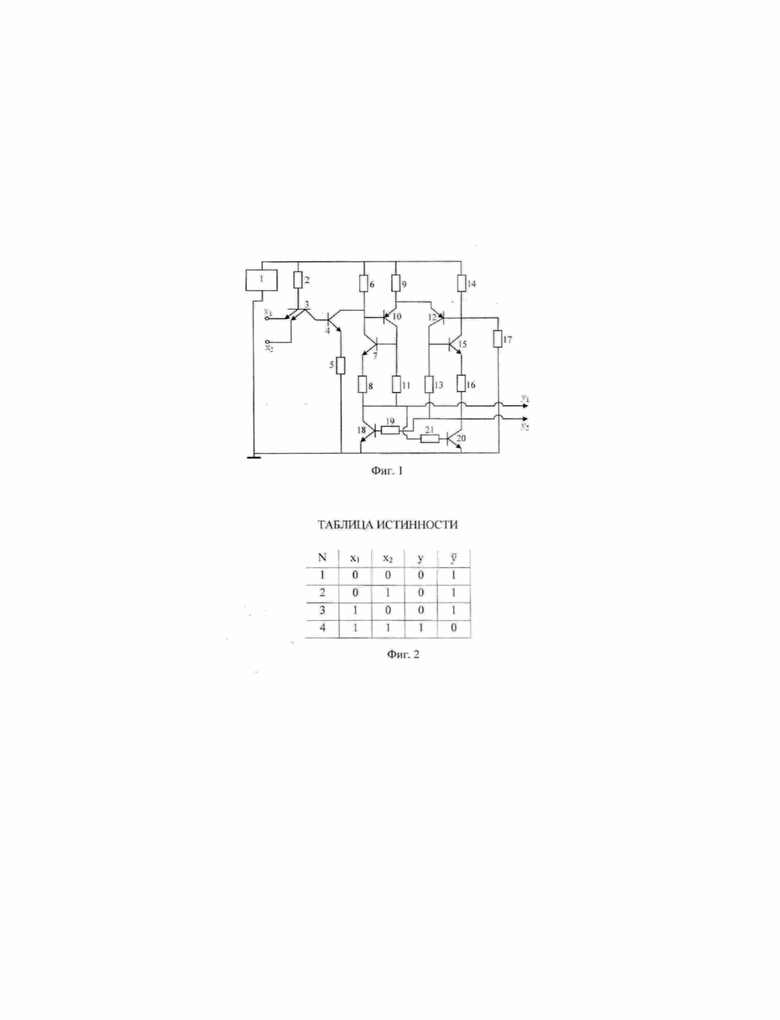

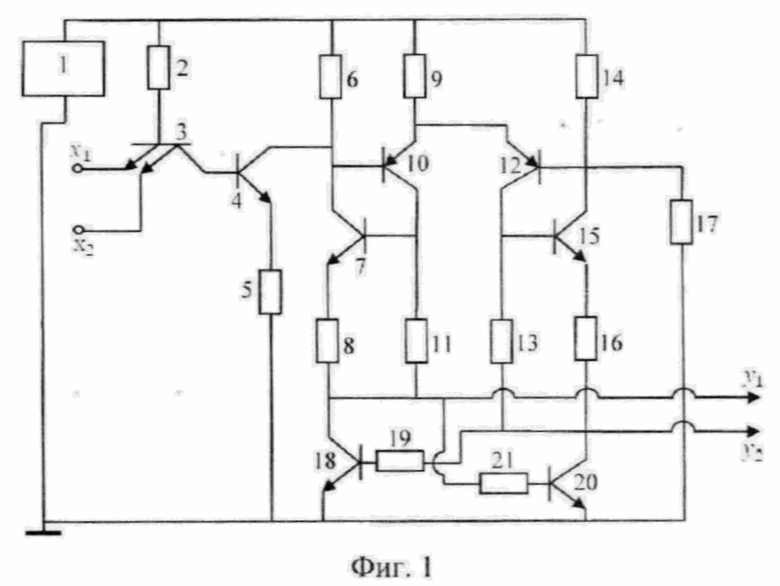

Сущность изобретения поясняется схемой триггерного логического элемента И/И-НЕ (фиг. 1) и таблицей истинности (фиг. 2).

В триггерном логическом элементе И/И-НЕ общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. К выходу (плюсовой вывод) питающего источника подсоединён один из выводов резистора 2. Другой вывод этого резистора подключён к базе двухэмиттерного n-p-n транзистора 3. Два вывода эмиттеров этого транзистора образуют относительно «земли» два входа  и

и  логического элемента. Последовательно между собой включены n-p-n транзистор 4 и резистор 5. База транзистора 4 соединена с коллектором транзистора 3, а свободный вывод резистора 5 заземлён. Последовательно включены резистор 6, n-p-n транзистор 7 и резистор 8. Свободный вывод резистора 6 подсоединён к выходу питающего источника 1, а общий вывод этого резистора и коллектора транзистора 7 подключён к коллектору транзистора 4. Последовательно включены резистор 9, p-n-p транзистор 10 и резистор 11. Свободный вывод резистора 9 подсоединён к выходу питающего источника 1. База транзистора 10 подключена к общему выводу резистора 6 и коллекторов транзисторов 4 и 7. Общий вывод коллектора транзистора 10 и резистора 11 соединён с базой транзистора 7.

логического элемента. Последовательно между собой включены n-p-n транзистор 4 и резистор 5. База транзистора 4 соединена с коллектором транзистора 3, а свободный вывод резистора 5 заземлён. Последовательно включены резистор 6, n-p-n транзистор 7 и резистор 8. Свободный вывод резистора 6 подсоединён к выходу питающего источника 1, а общий вывод этого резистора и коллектора транзистора 7 подключён к коллектору транзистора 4. Последовательно включены резистор 9, p-n-p транзистор 10 и резистор 11. Свободный вывод резистора 9 подсоединён к выходу питающего источника 1. База транзистора 10 подключена к общему выводу резистора 6 и коллекторов транзисторов 4 и 7. Общий вывод коллектора транзистора 10 и резистора 11 соединён с базой транзистора 7.

Свободный вывод резистора 11 соединён со свободным выводом резистора 8 и их общий вывод образует относительно «земли» первый выход  (выход реализации логической операции И) логического элемента. Последовательно включены p-n-p транзистор 12 и резистор 13. Эмиттер транзистора подсоединён к общему выводу резистора 9 и эмиттера транзистора 10. Последовательно включены резистор 14, n-p-n транзистор 15 и резистор 16. Свободный вывод резистора 14 подсоединён к выходу питающего источника 1. Общий вывод этого резистора и коллектора транзистора 15 подключён к базе транзистора 12. База транзистора 15 подсоединена к общему выводу коллектора транзистора 12 и резистора 13. Свободный вывод резистора 16 соединён со свободным выводом резистора 13 и их общий вывод образует относительно «земли» второй вывод

(выход реализации логической операции И) логического элемента. Последовательно включены p-n-p транзистор 12 и резистор 13. Эмиттер транзистора подсоединён к общему выводу резистора 9 и эмиттера транзистора 10. Последовательно включены резистор 14, n-p-n транзистор 15 и резистор 16. Свободный вывод резистора 14 подсоединён к выходу питающего источника 1. Общий вывод этого резистора и коллектора транзистора 15 подключён к базе транзистора 12. База транзистора 15 подсоединена к общему выводу коллектора транзистора 12 и резистора 13. Свободный вывод резистора 16 соединён со свободным выводом резистора 13 и их общий вывод образует относительно «земли» второй вывод  (выход реализации логической операции И-НЕ,

(выход реализации логической операции И-НЕ,  ) логического элемента.

) логического элемента.

На фиг. 1 часть схемы на транзисторах 7, 10 и резисторах 6, 8, 9, 11 является первым триггером на транзисторах противоположного типа проводимости. Часть схемы на транзисторах 12, 15 и резисторах 9, 13, 14, 16 является вторым таким триггером. Резистор 9 входит и в первый, и во второй триггеры и его можно называть общеэмиттрным резистором. Резистор 17 включён между «землёй» и общим выводом резистора 14, базы транзистора 12 и коллектора транзистора 15. Между «землёй» и общим выводом резисторов 8, 11 включён n-p-n транзистор 18. Эмиттер транзистора заземлён. Резистор 19 включён между базой транзистора 18 и общим выводом резисторов 13, 16. Между «землёй» и общим выводом резисторов 13, 16, 19 включён n-p-n транзистор 20. Эмиттер этого транзистора заземлён. Резистор 21 включён между базой транзистора 20 и общим выводом резисторов 8, 11 и коллектора транзистора 18.

Триггерный логический элемент И/И-НЕ работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля или в районе ближе к нулю, высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырёх вольт).

Триггер на транзисторах 7, 10 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состояния оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 6 и 11 нулевые значения напряжения. Они прикладываются к базам транзисторов 7, 10, меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 7 и 10 открыты, их электрические токи создают напряжения в том числе на резисторах 6 и 11 больше по абсолютной величине и по значениям пороговых напряжений транзисторов и поддерживают транзисторы 7, 10 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера. Точно так же работает второй триггер на транзисторах 12 и 15 противоположного типа проводимости.

Работа логического элемента И/И-НЕ отображается таблицей истинности (фиг.2), где  и

и  - условное отображение входных сигналов,

- условное отображение входных сигналов,  - условное отображение сигнала на первом (прямом) выходе логического элемента,

- условное отображение сигнала на первом (прямом) выходе логического элемента,  - условное отображение сигнала на втором (инверсном) выходе и N - номер строки по порядку. В соответствии с первыми тремя строками таблицы истинности на один или оба входа логического элемента поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных p-n переходов транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящем электрический ток состоянии. Базо-коллекторный переход транзистора 3 тоже открыт, в итоге на базе транзистора 4 низкий уровень напряжения и его состояние в худшем случае в районе порогового напряжения. Сила коллекторного тока транзистора 4 настолько мала, что напряжение на резисторе 6 уверенно меньше напряжения порога срабатывания триггера на транзисторах 7, 10, и оно не может его перевести во второе состояние. Делитель на резисторах 14, 17 позволяет получить напряжение на базе транзистора 12 достаточное для обеспечения второго состояния триггера на транзисторах 12, 15. Электрические токи открытых транзисторов 12, 15 обеспечивают на втором (инверсном) выходе логического элемента напряжение уровня логической единицы. Оно через резистор 19 поддерживает транзистор 18 в открытом состоянии. Тогда через этот транзистор разряжается ранняя заряженная эквивалентная паразитная емкость (сумма выходной ёмкости логического элемента и входной ёмкости нагрузки). Малое сопротивление открытого транзистора 18 уменьшает постоянную времени разряда эквивалентной паразитной ёмкости, тем самым уменьшает время разряда этой ёмкости и в результате заметно не ухудшается быстродействие схемы из-за имеющихся паразитных ёмкостей.

- условное отображение сигнала на втором (инверсном) выходе и N - номер строки по порядку. В соответствии с первыми тремя строками таблицы истинности на один или оба входа логического элемента поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных p-n переходов транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящем электрический ток состоянии. Базо-коллекторный переход транзистора 3 тоже открыт, в итоге на базе транзистора 4 низкий уровень напряжения и его состояние в худшем случае в районе порогового напряжения. Сила коллекторного тока транзистора 4 настолько мала, что напряжение на резисторе 6 уверенно меньше напряжения порога срабатывания триггера на транзисторах 7, 10, и оно не может его перевести во второе состояние. Делитель на резисторах 14, 17 позволяет получить напряжение на базе транзистора 12 достаточное для обеспечения второго состояния триггера на транзисторах 12, 15. Электрические токи открытых транзисторов 12, 15 обеспечивают на втором (инверсном) выходе логического элемента напряжение уровня логической единицы. Оно через резистор 19 поддерживает транзистор 18 в открытом состоянии. Тогда через этот транзистор разряжается ранняя заряженная эквивалентная паразитная емкость (сумма выходной ёмкости логического элемента и входной ёмкости нагрузки). Малое сопротивление открытого транзистора 18 уменьшает постоянную времени разряда эквивалентной паразитной ёмкости, тем самым уменьшает время разряда этой ёмкости и в результате заметно не ухудшается быстродействие схемы из-за имеющихся паразитных ёмкостей.

Эмиттерный ток транзистора 12 создаёт на резисторе 9 падение напряжения, которое плюсом приложено через резистор 6 к базе p-n-p транзистора 10, дополнительно способствует его закрытому состоянию и соответственно первому состоянию триггера на транзисторах 7, 10. Нулевое значение силы электрического тока первого триггера на транзисторах противоположного типа проводимости создаёт на первом (прямом) выходе у логического элемента напряжения уровня логического нуля. Оно приложено к резистору 21 и поддерживает транзистор 20 в худшем случае в районе его порогового напряжения. Сила тока этого транзистора весьма мала, и электрический ток транзисторов 12, 15 почти полностью замыкается на внешнюю нагрузку, подключенную ко второму (инверсному) выходу  .

.

В соответствии с четвёртой строкой таблицы истинности (фиг. 2) на оба входа логического элемента подаётся напряжение уровня логической единицы. Базо-эмиттерные и базо-коллекторный p-n переходы транзистора 3 по-прежнему открыты и в результате на базе этого транзистора и на базе транзистора 4 имеется высокий уровень напряжения. В соответствии с этим повышенное значение силы коллекторного тока транзистора 4 создаёт на резисторе 6 повышенное значение напряжения, достаточное для обеспечения открытого состояния транзистора 10 с учётом наличия делителя на резисторах 14, 17 и соответственно второе состояние триггера на транзисторах 7, 10. Электрические токи этих двух транзисторов создают на внешней нагрузке прямого выхода  напряжение уровня логической единицы. Напряжение на резисторе 9 плюсом приложено к базе p-n-p транзистора 12 через резистор 14, а минусом - к эмиттеру этого транзистора. Это напряжение с учётом делителя на резисторах 14, 17 должно обеспечить состояние транзистора 12 в районе его порогового напряжения и в итоге первое состояние триггера на транзисторах 12, 15 противоположного типа проводимости. В результате на инверсном выходе

напряжение уровня логической единицы. Напряжение на резисторе 9 плюсом приложено к базе p-n-p транзистора 12 через резистор 14, а минусом - к эмиттеру этого транзистора. Это напряжение с учётом делителя на резисторах 14, 17 должно обеспечить состояние транзистора 12 в районе его порогового напряжения и в итоге первое состояние триггера на транзисторах 12, 15 противоположного типа проводимости. В результате на инверсном выходе  логического элемента имеется напряжение уровня логического нуля.

логического элемента имеется напряжение уровня логического нуля.

С прямого выхода  логического элемента напряжение уровня логической единицы приложено к резистору 21 и поддерживает транзистор 20 в открытом состоянии. Через него сравнительно быстро разряжается ранее заряженная эквивалентная паразитная ёмкость и в результате в меньшей степени ухудшается быстродействие схемы из-за наличия названной паразитной ёмкости. Эквивалентная паразитная ёмкость зарядилась в предыдущий период, когда инверсном выходе

логического элемента напряжение уровня логической единицы приложено к резистору 21 и поддерживает транзистор 20 в открытом состоянии. Через него сравнительно быстро разряжается ранее заряженная эквивалентная паразитная ёмкость и в результате в меньшей степени ухудшается быстродействие схемы из-за наличия названной паразитной ёмкости. Эквивалентная паразитная ёмкость зарядилась в предыдущий период, когда инверсном выходе  значение напряжения равнялось уровню логической единице. С инверсного выхода

значение напряжения равнялось уровню логической единице. С инверсного выхода  логического элемента напряжение уровня логического нуля прикладывается к резистору 19 и поддерживает транзистор 18 в районе его порогового напряжения, поэтому электрический ток транзисторов 7, 10 почти полностью замыкается на внешнюю нагрузку, подключённую к прямому выходу

логического элемента напряжение уровня логического нуля прикладывается к резистору 19 и поддерживает транзистор 18 в районе его порогового напряжения, поэтому электрический ток транзисторов 7, 10 почти полностью замыкается на внешнюю нагрузку, подключённую к прямому выходу  логического элемента.

логического элемента.

Таким образом, в триггерном логическом элементе И/И-НЕ сила электрического тока внешней нагрузки и по прямому выходу  , и по инверсному выходу

, и по инверсному выходу  почти равна сумме силы токов двух транзисторов (7, 10 и 12, 15) что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки по имеющемуся одному выходу формирует только один транзистор.

почти равна сумме силы токов двух транзисторов (7, 10 и 12, 15) что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки по имеющемуся одному выходу формирует только один транзистор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2021 |

|

RU2760206C1 |

| Триггерный асинхронный Т триггер | 2020 |

|

RU2726848C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2020 |

|

RU2726853C1 |

| Триггерный двухступенчатый R-S триггер | 2019 |

|

RU2721386C1 |

| Триггерный логический элемент И | 2019 |

|

RU2728954C1 |

| Триггерный логический элемент ИЛИ-НЕ | 2021 |

|

RU2767176C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| Триггерный двухступенчатый D триггер | 2019 |

|

RU2714106C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах. Технический результат: повышение нагрузочной способности триггерного логического элемента И/И-НЕ. Для этого предложен триггерный логический элемент И/И-НЕ, который содержит восемь транзисторов, двенадцать резисторов и источник питающего постоянного напряжения. Новым является то, что введены четыре дополнительных транзистора и восемь дополнительных резисторов, последовательно между собой включены первый дополнительный транзистор (n-p-n) и первый дополнительный резистор. 2 ил.

Триггерный логический элемент И/И-НЕ, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, первый резистор, один из выводов которого подключён к выходу (плюсовой вывод) питающего источника, первый транзистор (n-p-n), база которого подсоединена к свободному выводу первого резистора, транзистор является двухэмиттерным, вывод каждого эмиттера его образуют относительно «земли» два входа  и

и  логического элемента, последовательно включённые второй резистор, второй транзистор (n-p-n) и третий резистор, свободный вывод второго резистора подсоединён к общему выводу первого резистора и выхода питающего источника, база второго транзистора подключена к коллектору первого транзистора, а свободный вывод третьего резистора заземлён, последовательно включённые четвёртый резистор и третий транзистор (n-p-n), свободный вывод четвёртого резистора соединён с общим выводом первого, второго резисторов и выхода питающего источника, четвёртый транзистор (n-p-n), эмиттер которого заземлён, отличающийся тем, что в него введены четыре дополнительных транзистора и восемь дополнительных резисторов, последовательно между собой включены первый дополнительный транзистор (n-p-n) и первый дополнительный резистор, коллектор первого дополнительного транзистора подсоединён к общему выводу второго резистора и коллектора второго транзистора, последовательно включены второй дополнительный резистор, второй дополнительный транзистор (p-n-p) и третий дополнительный резистор, свободный вывод второго дополнительного резистора подсоединён к общему выводу первого, второго, четвёртого резисторов и выхода питающего источника, база этого транзистора подключена к общему выводу второго резистора и коллекторов второго и дополнительного первого транзисторов, общий вывод коллектора второго дополнительного транзистора и третьего дополнительного резистора соединён с базой дополнительного первого транзистора, а свободный вывод третьего дополнительного резистора - со свободным выводом первого дополнительного резистора, общий вывод последних резисторов образует относительно «земли» первый выход

логического элемента, последовательно включённые второй резистор, второй транзистор (n-p-n) и третий резистор, свободный вывод второго резистора подсоединён к общему выводу первого резистора и выхода питающего источника, база второго транзистора подключена к коллектору первого транзистора, а свободный вывод третьего резистора заземлён, последовательно включённые четвёртый резистор и третий транзистор (n-p-n), свободный вывод четвёртого резистора соединён с общим выводом первого, второго резисторов и выхода питающего источника, четвёртый транзистор (n-p-n), эмиттер которого заземлён, отличающийся тем, что в него введены четыре дополнительных транзистора и восемь дополнительных резисторов, последовательно между собой включены первый дополнительный транзистор (n-p-n) и первый дополнительный резистор, коллектор первого дополнительного транзистора подсоединён к общему выводу второго резистора и коллектора второго транзистора, последовательно включены второй дополнительный резистор, второй дополнительный транзистор (p-n-p) и третий дополнительный резистор, свободный вывод второго дополнительного резистора подсоединён к общему выводу первого, второго, четвёртого резисторов и выхода питающего источника, база этого транзистора подключена к общему выводу второго резистора и коллекторов второго и дополнительного первого транзисторов, общий вывод коллектора второго дополнительного транзистора и третьего дополнительного резистора соединён с базой дополнительного первого транзистора, а свободный вывод третьего дополнительного резистора - со свободным выводом первого дополнительного резистора, общий вывод последних резисторов образует относительно «земли» первый выход  (выход И), последовательно включены третий дополнительный транзистор (p-n-p) и четвёртый дополнительный резистор, эмиттер транзистора подсоединён к общему выводу второго дополнительного резистора и эмиттера второго дополнительного транзистора, база третьего дополнительного транзистора подключена к общему выводу четвёртого резистора и коллектора третьего транзистора, общий вывод четвёртого дополнительного резистора и коллектора третьего дополнительного транзистора соединён с базой третьего транзистора, пятый дополнительный резистор включён между свободным выводом четвёртого дополнительного резистора и эмиттером третьего транзистора, общий вывод четвертого и пятого дополнительных резисторов образует относительно «земли» второй выход

(выход И), последовательно включены третий дополнительный транзистор (p-n-p) и четвёртый дополнительный резистор, эмиттер транзистора подсоединён к общему выводу второго дополнительного резистора и эмиттера второго дополнительного транзистора, база третьего дополнительного транзистора подключена к общему выводу четвёртого резистора и коллектора третьего транзистора, общий вывод четвёртого дополнительного резистора и коллектора третьего дополнительного транзистора соединён с базой третьего транзистора, пятый дополнительный резистор включён между свободным выводом четвёртого дополнительного резистора и эмиттером третьего транзистора, общий вывод четвертого и пятого дополнительных резисторов образует относительно «земли» второй выход  (выход И-НЕ) логического элемента, шестой дополнительный резистор включён между «землёй» и общим выводом четвёртого резистора, коллектора третьего резистора и базой третьего дополнительного транзистора, четвёртый дополнительный (n-p-n) транзистор включён между «землёй» и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента, седьмой дополнительный резистор включён между базой четвёртого дополнительного транзистора и общим выводом четвёртого, пятого дополнительных резисторов и второго выхода логического элемента, восьмой дополнительный резистор включён между базой четвёртого транзистора и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента.

(выход И-НЕ) логического элемента, шестой дополнительный резистор включён между «землёй» и общим выводом четвёртого резистора, коллектора третьего резистора и базой третьего дополнительного транзистора, четвёртый дополнительный (n-p-n) транзистор включён между «землёй» и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента, седьмой дополнительный резистор включён между базой четвёртого дополнительного транзистора и общим выводом четвёртого, пятого дополнительных резисторов и второго выхода логического элемента, восьмой дополнительный резистор включён между базой четвёртого транзистора и общим выводом первого, третьего дополнительных резисторов и первого выхода логического элемента.

| ЯМПОЛЬСКИЙ В.С., "Основы автоматики и электронно-вычислительной техники", Москва, Просвещение, 1991, стр | |||

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Триггерный логический элемент И-НЕ | 2018 |

|

RU2694151C1 |

| Логический элемент И-НЕ ИШЛ | 1985 |

|

SU1262720A1 |

| Станок для придания концам круглых радиаторных трубок шестигранного сечения | 1924 |

|

SU2019A1 |

Авторы

Даты

2020-07-22—Публикация

2020-02-03—Подача