Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных усилителей и выходных каскадов различных аналоговых устройств (операционных усилителях (ОУ), драйверах линий связи и т.п.), допускающих работу в условиях воздействия проникающей радиации и низких температур.

Известно значительное количество схем микроэлектронных двухтактных выходных каскадов, которые реализуются на комплементарных биполярных (BJT) или полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-28].

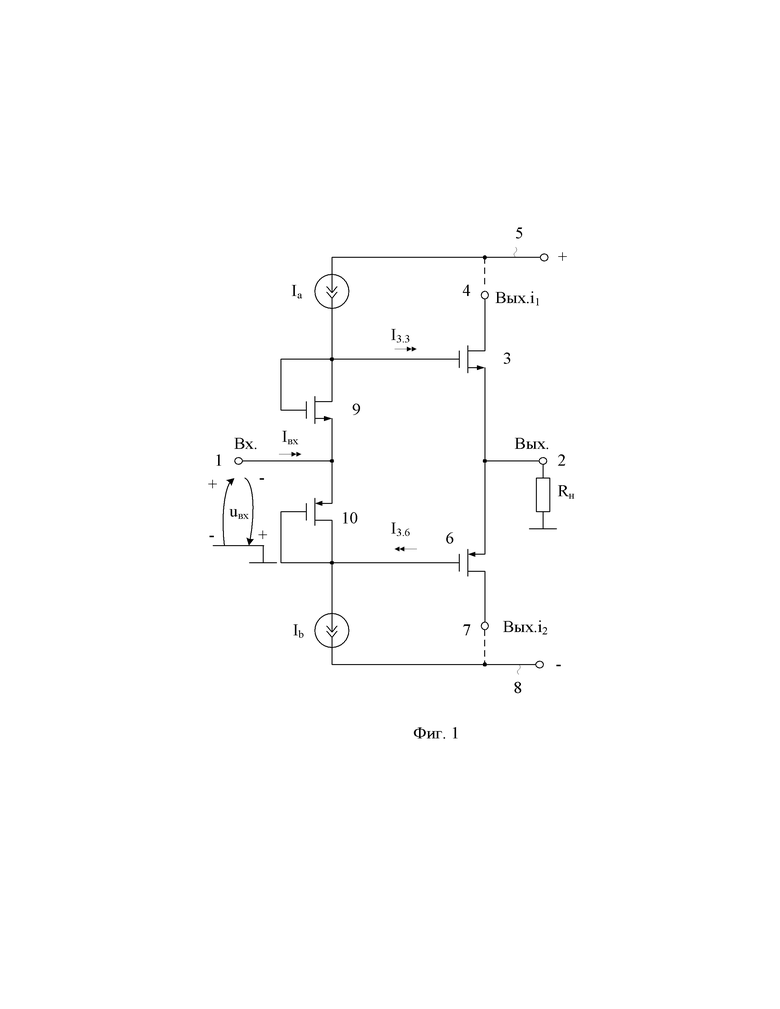

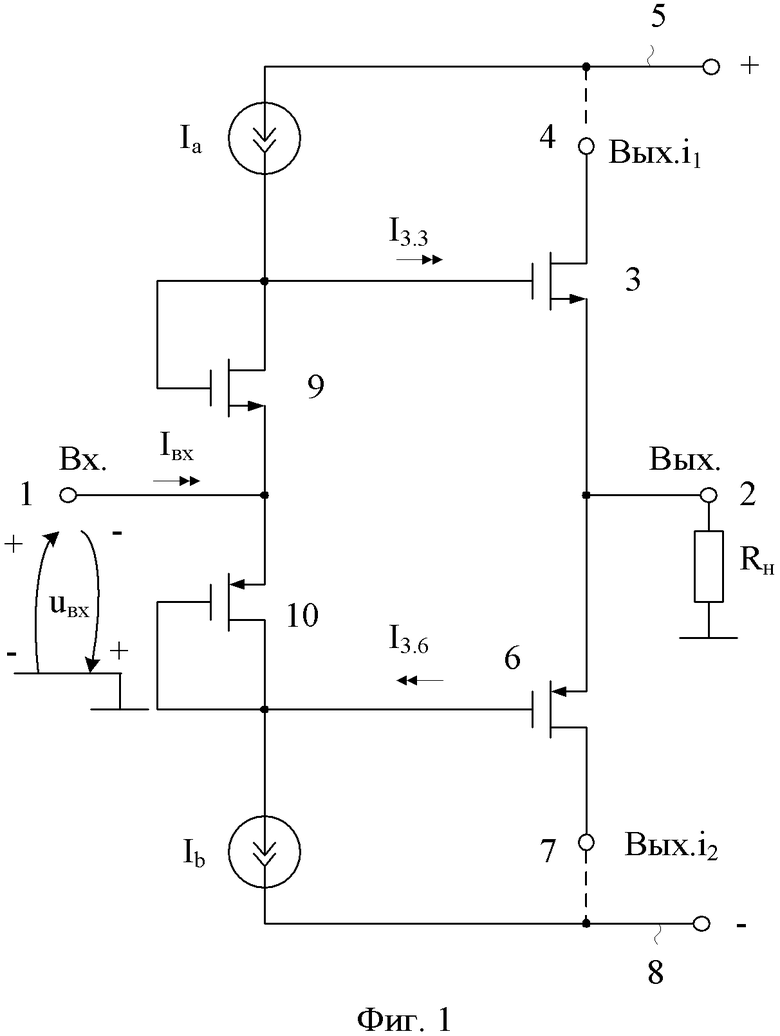

Ближайшим прототипом заявляемого устройства является двухтактный выходной каскад (фиг. 1) на комплементарных полевых транзисторах, представленный в патенте фирмы Japan Radio US 5.497.124, fig.25, 1996 г. Данная схема рассмотрена также в книге Эннс В.И., Кобзев Ю.М. «Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика /под ред. канд. техн. наук В.И. Эннса. – М.: Горячая линия-Телеком. – 2005. – 454 с, fig.3-58». Схема ВК-прототипа фиг. 1 содержит вход 1 и выход 2 устройства, первый 3 входной полевой транзистор, сток которого соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 входной полевой транзистор, сток которого подключен ко второму 7 токовому выходу устройства, согласованному со второй 8 шиной источника питания, первый 9 и второй 10 согласующие прямосмещенные p-n-переходы.

Известный выходной каскад фиг. 1 перспективен для использования в ОУ с потенциальной отрицательной обратной связью [29] (когда используется только выход 2 заявляемого устройства), а также в качестве входных каскадов ОУ с токовой отрицательной обратной связью [28,29], когда используются первый 4 и второй 7 токовые выходы. В последнем случае к величине напряжения смещения нуля ВК предъявляются повышенные требования [28]. При этом из-за неидентичности стоко-затворных характеристик первого 3 и второго 6 входных полевых транзисторов, которую практически невозможно устранить технологическим путем, численные значения систематической составляющей напряжения смещения нуля (Uсм) в схеме фиг. 1 лежат в пределах сотен милливольт. Для ряда задач аналоговой микроэлектроники это недопустимо, что порождает создание достаточно сложных [28] схемотехнических методов компенсации Uсм ВК данного класса.

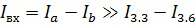

Существенный недостаток известного выходного каскада состоит в том, что его входной статический ток Iвх определяется разностью токов источников опорного тока Ia и Ib (фиг. 1). В результате, применение первого 3 и второго 6 входных полевых транзисторов с чрезмерно малыми входными токами в ВК-прототипе практически не имеет смысла, так как

, (1)

, (1)

где I3.3, I3.6 – токи затворов первого 3 и второго 6 полевых транзисторов.

В практических схемах ВК (фиг. 1) высококачественные источники опорного тока Iа, Ib, существенно влияющие на Iвх (1), выполняются по достаточно сложным транзисторным схемам, что отрицательно влияет на общее энергопотребление и другие параметры ВК.

Таким образом, из-за сравнительно больших входных токов ВК-прототип имеет ограниченное применение, прежде всего, в тяжелых условиях эксплуатации (низкие температуры, проникающая радиация), вызывающих разбалансировку токов Ia (Ib) и увеличение их абсолютных значений.

Основная задача предполагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного схемотехнического решения ВК на комплементарных полевых транзисторах, обеспечивающего (при высокой линейности амплитудной характеристики) сверхмалые значения входного статического тока Iвх, в том числе при работе в диапазоне низких температур.

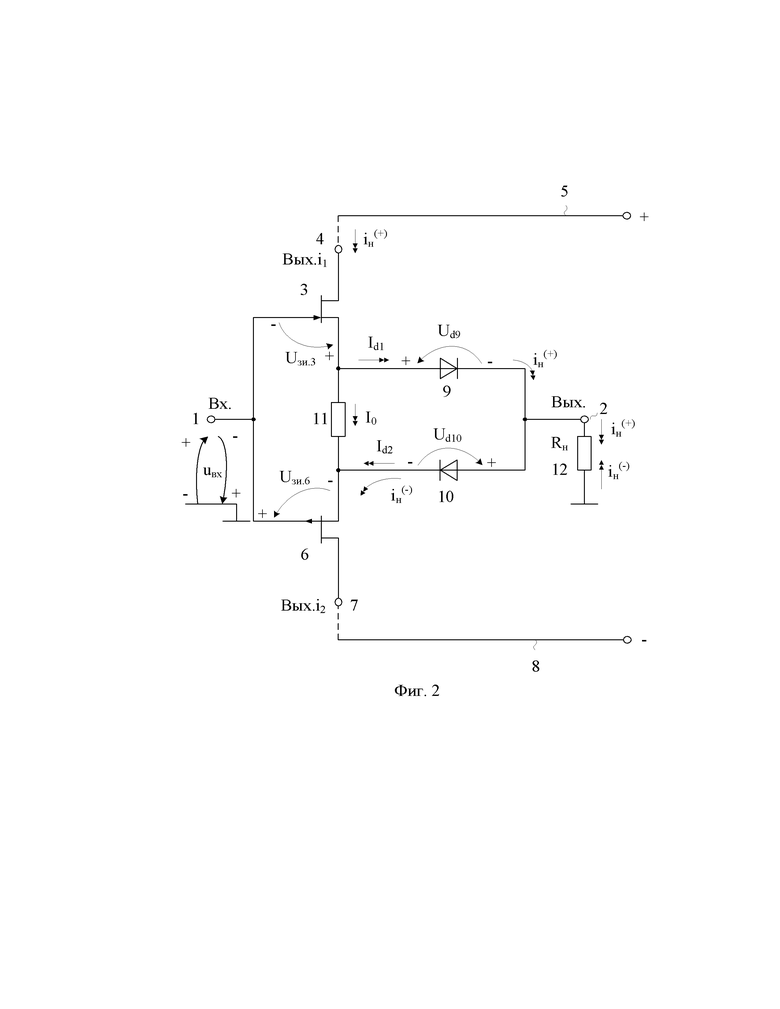

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, первый 3 входной полевой транзистор, сток которого соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 входной полевой транзистор, сток которого подключен ко второму 7 токовому выходу устройства, согласованному со второй 8 шиной источника питания, первый 9 и второй 10 согласующие прямосмещенные p-n-переходы, предусмотрены новые элементы и связи – в качестве первого 3 и второго 6 входных полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом, затворы первого 3 и второго 6 входных полевых транзисторов подключены ко входу 1 устройства, между истоками первого 3 и второго 6 входных полевых транзисторов включен дополнительный резистор 11, исток первого 3 входного полевого транзистора связан с выходом 2 устройства через первый 9 согласующий прямосмещенный p-n-переход, а исток второго 6 входного полевого транзистора соединен с выходом 2 устройства через второй 10 согласующий прямосмещенный p-n-переход.

Первый 4 и второй 7 токовые выходы заявляемого ВК фиг. 2 могут подключаться в некоторых практических схемах ОУ (например, в усилителях с токовой отрицательной обратной связью [28,29]) к токовым зеркалам и другим выходным подсхемам того или иного проектируемого аналогового устройства, решающего практические задачи обработки аналоговых сигналов. В частном случае, в соответствии с п. 2 формулы изобретения, первый 4 токовый выход устройства соединен с первой 5 шиной источника питания, а второй 7 токовый выход устройства соединен со второй 8 шиной источника питания. В данном варианте применения ВК фиг. 2 токовые выходы 4 и 7 не используются, а ВК фиг. 2 выполняет только одну функцию – согласование низкоомной нагрузки 12 с источником входного сигнала (по величине входного сопротивления), а также передачу в нагрузку 12 входного напряжения с коэффициентом передачи, близким к единице.

На фиг. 1 представлена схема ВК-прототипа, а на фиг. 2 – схема предлагаемого CJFet выходного каскада, соответствующая п. 1 и п. 2 формулы изобретения.

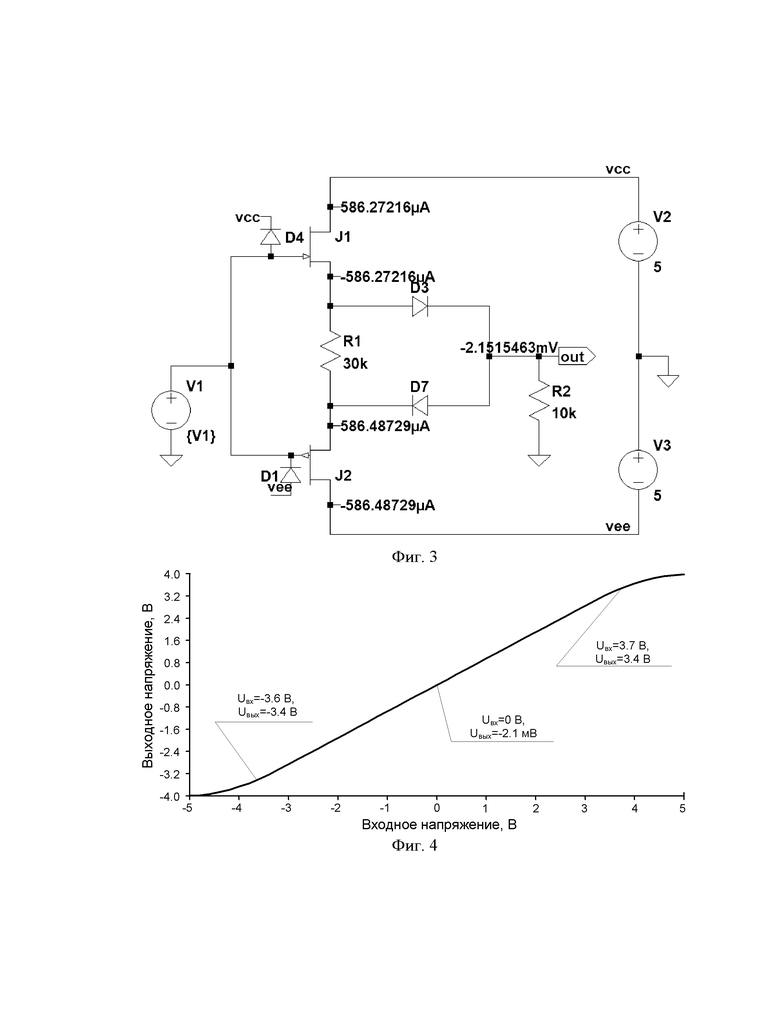

На фиг. 3 показан статический режим схемы ВК фиг. 2 при температуре +25°С, Uвх.=V1=0, R1=30 кОм, Rн=R2=10кОм.

На фиг. 4 приведена зависимость выходного напряжения от входного напряжения схемы ВК фиг. 3 при температуре +25°С, R1=30 кОм, Rн=R2=10кОм.

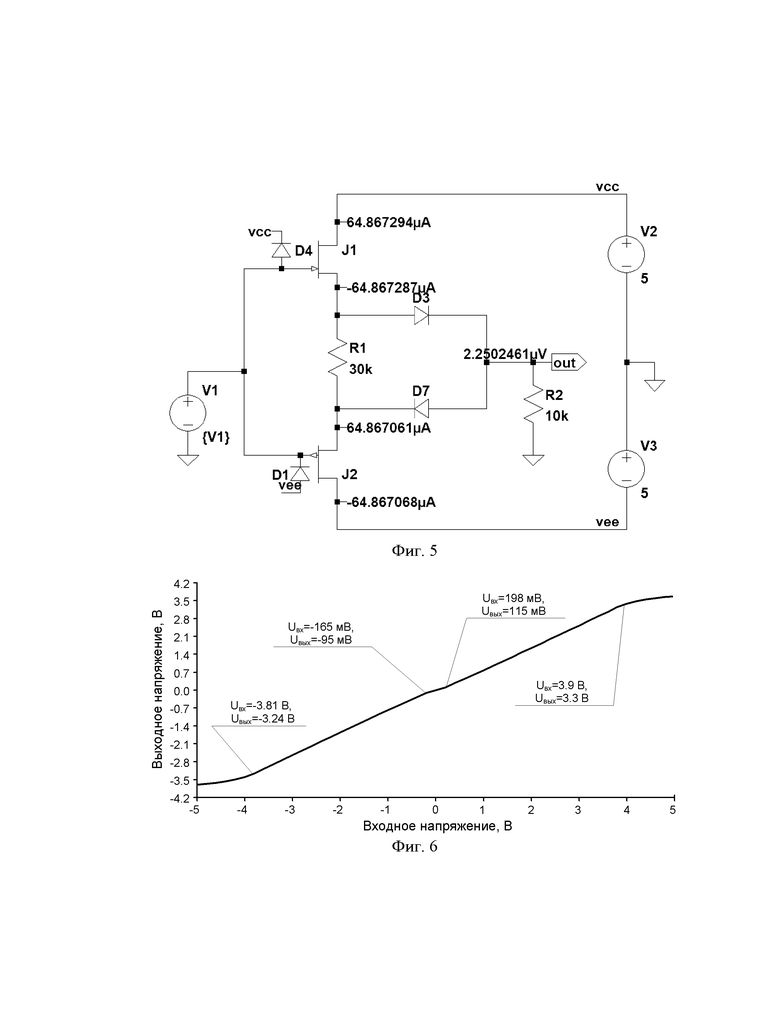

На фиг. 5 представлен статический режим схемы ВК фиг. 2 при температуре -197°С, Uвх.=V1=0, R1=30 кОм, Rн=R2=10кОм.

На фиг. 6 показана зависимость выходного напряжения от входного напряжения схемы ВК фиг. 5 при температуре -197°С, R1=30 кОм, Rн=R2=10кОм.

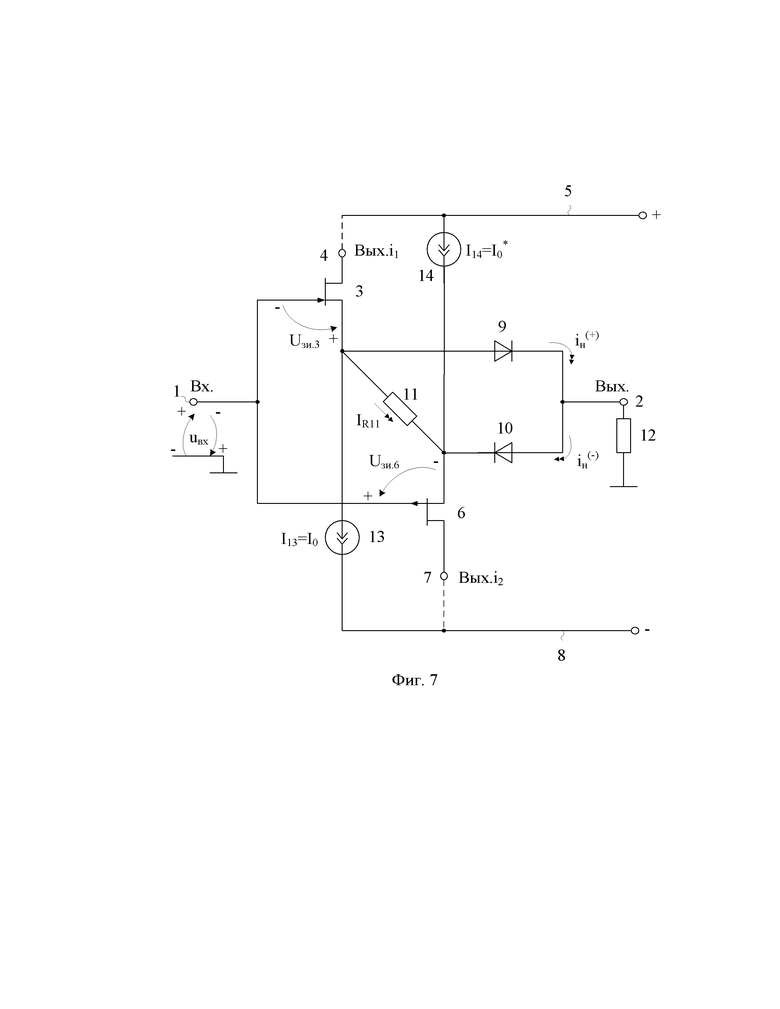

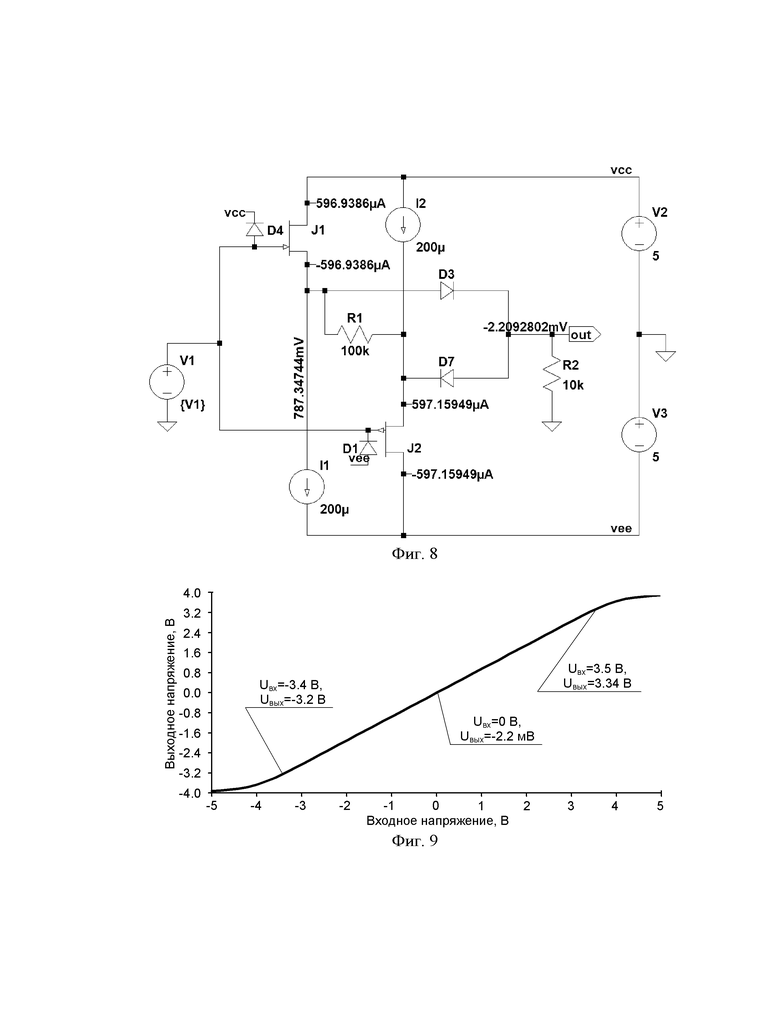

На фиг. 7 приведена схема CJFet выходного каскада в соответствии с п.3 формулы изобретения, а на фиг. 8 - статический режим схемы фиг. 7 c при температуре +25°С, Uвх.=V1=0, R1=100 кОм, Rн=R2=10кОм.

На фиг. 9 представлена зависимость выходного напряжения от входного напряжения схемы ВК фиг. 8 при температуре +25°С, R1=100 кОм, Rн=R2=10кОм.

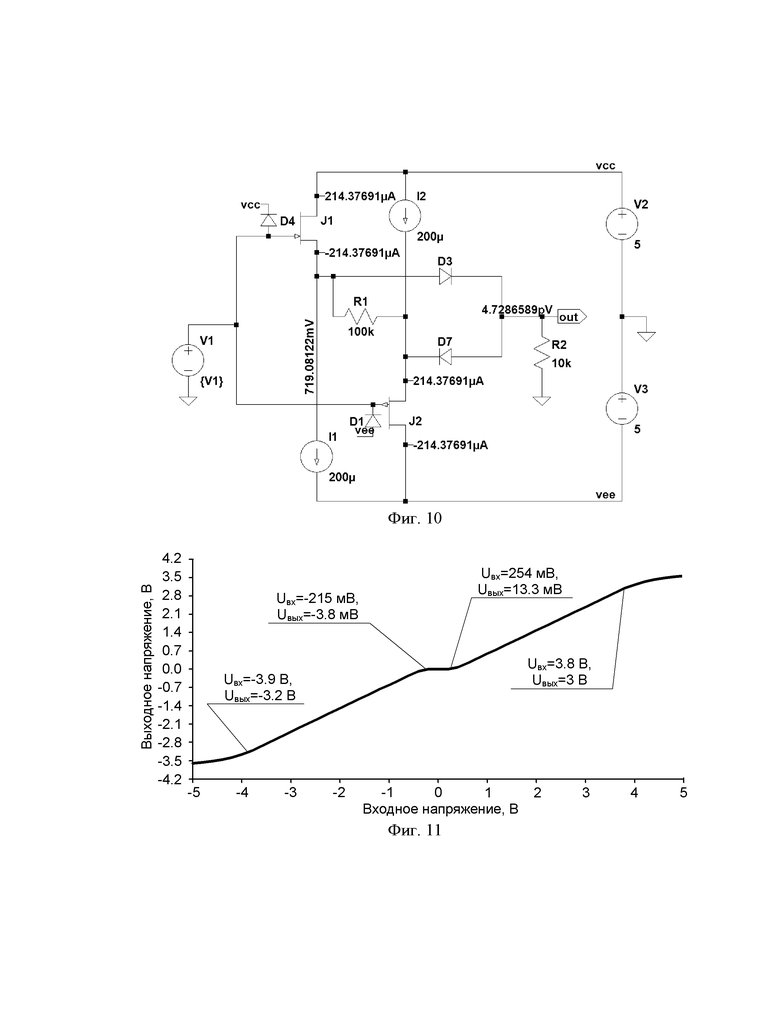

На фиг. 10 показан статический режим схемы фиг. 7 c при температуре -197°С, Uвх.=V1=0, R1=100 кОм, Rн=R2=10кОм.

На фиг. 11 приведена зависимость выходного напряжения от входного напряжения схемы ВК фиг. 10 при температуре -197°С, R1=100 кОм, Rн=R2=10кОм.

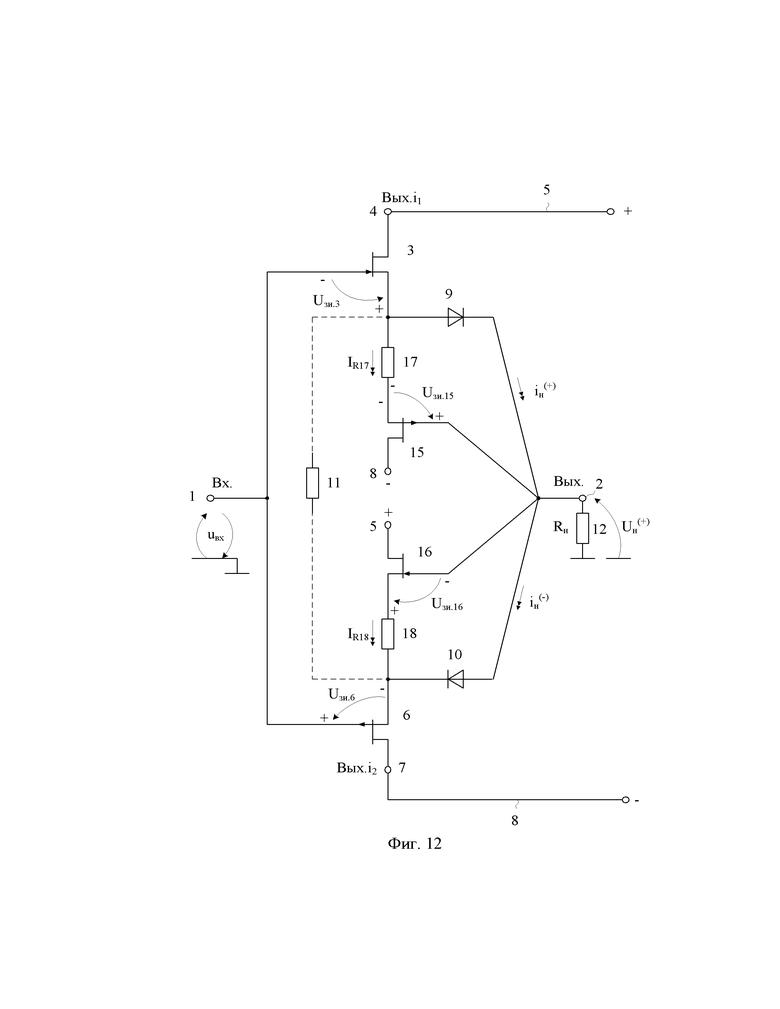

На фиг. 12 представлена схема заявляемого CJFet ВК в соответствии с п.4 формулы изобретения.

Двухтактный выходной каскад класса AB аналоговых микросхем на комплементарных полевых транзисторах для работы при низких температурах фиг. 2 содержит вход 1 и выход 2 устройства, первый 3 входной полевой транзистор, сток которого соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 входной полевой транзистор, сток которого подключен ко второму 7 токовому выходу устройства, согласованному со второй 8 шиной источника питания, первый 9 и второй 10 согласующие прямосмещенные p-n-переходы. В качестве первого 3 и второго 6 входных полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом, затворы первого 3 и второго 6 входных полевых транзисторов подключены ко входу 1 устройства, между истоками первого 3 и второго 6 входных полевых транзисторов включен дополнительный резистор 11, исток первого 3 входного полевого транзистора связан с выходом 2 устройства через первый 9 согласующий прямосмещенный p-n-переход, а исток второго 6 входного полевого транзистора соединен с выходом 2 устройства через второй 10 согласующий прямосмещенный p-n-переход.

На фиг. 2, в соответствии с п.2 формулы изобретения, первый 4 токовый выход устройства соединен с первой 5 шиной источника питания, а второй 7 токовый выход устройства соединен со второй 8 шиной источника питания. Двухполюсник 12 моделирует свойства нагрузки Rн.

На фиг. 7, в соответствии с п. 3 формулы изобретения, исток первого 3 входного полевого транзистора связан со второй 8 шиной источника питания через первый 13 дополнительный источник опорного тока, а исток второго 6 входного полевого транзистора соединен с первой 5 шиной источника питания через второй 14 дополнительный источник опорного тока.

На фиг. 12, в соответствии с п. 4 формулы изобретения, в схему введены первый 15 и второй 16 дополнительные полевые транзисторы с управляющим p-n-переходом, затворы которых объединены и подключены к выходу устройства 2, исток первого 3 входного полевого транзистора соединен с истоком первого 15 дополнительного полевого транзистора с управляющим p-n-переходом через первый 17 вспомогательный резистор, сток первого 15 дополнительного полевого транзистора с управляющим p-n-переходом связан со второй 8 шиной источника питания, исток второго 6 входного полевого транзистора соединен с истоком второго 16 дополнительного полевого транзистора с управляющим p-n-переходом через второй 18 вспомогательный резистор, а сток второго 16 дополнительного полевого транзистора с управляющим p-n-переходом связан с первой 5 шиной источника питания.

В соответствии с п. 5 формулы изобретения, первый 9 и второй 10 согласующие прямосмещенные p-n-переходы могут быть выполнены в виде первого и второго составных двухполюсников, каждый из которых содержит несколько элементарных последовательно соединенных p-n-переходов. Такое схемотехническое решение позволяет уменьшить общее токопотребление схемы ВК.

Рассмотрим работу ВК фиг. 2.

Особенность схемы заявляемого ВК состоит в том, что статический режим первого 3 и второго 6 входных полевых транзисторов по току определяется дополнительным резистором 11, что позволяет за счет изменения его сопротивления обеспечить оптимизацию режима по общему статическому току потребления.

Статический ток I0 через дополнительный резистор 11 определяется уравнениями на основе второго закона Кирхгофа:

, (2)

, (2)

, (3)

, (3)

где Uзи.i – напряжение затвор-исток i-го полевого транзистора при токе истока, равном I0.

Таким образом, в схеме фиг. 2 токи истоков первого 3 и второго 6 входных полевых транзисторов определяются сопротивлением дополнительного резистора 11.

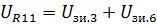

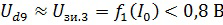

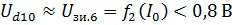

При этом падение напряжения на первом 9 и втором 10 согласующих прямосмещенных кремниевых p-n-переходах зависят от численных значений тока I0, однако не может быть больше 0,7-0,8 В, что обусловлено физическими процессами в кремниевых диодах:

; (4)

; (4)

(5)

(5)

Если ток I0 выбирается в диапазоне десятков микроампер, то расчетные (4), (5) напряжения затвор-исток первого 3 и второго 6 входных полевых транзисторов в данном режиме могут превышать реальные численные значения падения напряжений на первом 9 и втором 10 согласующих прямосмещенных p-n-переходах, которое для типовых кремниевых p-n-переходов близко к 0,7-0,8 В в диапазоне трех порядков протекающих прямых токов. В этом случае, в соответствии с п. 5 формулы изобретения, следует предусмотреть выполнение первого 9 и второго 10 согласующих прямосмещенных p-n-переходов в виде первого и второго составных двухполюсников, каждый из которых содержит несколько (2-3) элементарных последовательно соединенных p-n-переходов. Такое решение позволит обеспечить малое статическое токопотребление заявляемого ВК, а также выполнение им своих основных функций.

Особенность схемы ВК фиг. 7 состоит в том, что здесь начальный статический режим первого 3 и второго 6 входных транзисторов устанавливается первым 13 и вторым 14 дополнительными источниками опорного тока. При этом численные значения сопротивления R11 могут выбираться в пределах, значительно превышающих сопротивление нагрузки 12.

В схеме фиг. 12 статический режим по току первого 3 и второго 6 входных полевых транзисторов устанавливается первым 15 дополнительным полевым транзистором с управляющим p-n-переходом и первым 17 вспомогательным резистором, а также вторым 16 дополнительным полевым транзистором с управляющим p-n-переходом и вторым 18 вспомогательным резистором, которые фактически выполняют функцию первого 13 и второго 14 дополнительных источников опорного тока в схеме фиг. 7.

Компьютерное моделирование в среде LTspice и оптимизация заявляемой схемы (фиг. 4, фиг. 5, фиг. 6) показывает, что предлагаемый ВК, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [30,31], имеет существенные достоинства в сравнении с известными вариантами построения ВК, прежде всего, по величине входного тока.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, 1999 г.

4. Патент US 5.197.124, fig. 25, 1993 г.

5. Патент US 7.764.123, fig. 3, 2010 г.

6. Патент US № 6.268.769 fig.3, 2001 г.

7. Патент US № 6.420.933, 2002 г.

8. Патент US № 5.223.122, 1993 г.

9. Патентная заявка US № 2004/0196101, 2004 г.

10. Патентная заявка US № 2005/0264358 fig.1, 2005 г.

11. Патентная заявка US № 2002/0175759, 2002 г.

12. Патент US № 5.049.653 fig.8, 1991 г.

13. Патент US № 4.837.523, 1989 г.

14. Патент US № 5.179.355, 1993 г.

15. Патент Японии JP 10.163.763, 1991 г.

16. Патент Японии JP 10.270.954, 1992 г.

17. Патент US № 5.170.134 fig.6, 1992 г.

18. Патент US № 4.540.950, 1985 г.

19. Патент US № 4.424.493, 1984 г.

20. Патент Японии JP 6310950, 2018 г.

21. Патент US № 5.378.938, 1995 г.

22. Патент US № 4.827.223, 1989 г.

23. Патент US № 6.160.451, 2000 г.

24. Патент US № 4.639.685, 1987 г.

25. Авт. св. СССР 1506512, 1986 г.

26. Патент US № 5.399.991, 1995 г.

27. Патент US № 6.542.032, 2003 г.

28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

29. N.N. Prokopenko, A.S. Budyakov, J.M. Savchenko, S.V. Korneev. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes // Proceeding of the Third International Conference on Circuits and Systems for Communications – ICCSC’06, Politehnica University, Bucharest, Romania: July 6-7, 2006, pp.149-154.

30. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. Ред. Д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. Гос. Ун-т экономики и сервиса». – Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. – 208 с.

31. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ | 2021 |

|

RU2767976C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2616573C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2766868C1 |

| ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ С МАЛЫМ УРОВНЕМ СИСТЕМАТИЧЕСКОЙ СОСТАВЛЯЮЩЕЙ НАПРЯЖЕНИЯ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784045C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| ИСТОКОВЫЙ ПОВТОРИТЕЛЬ СИГНАЛА С МАЛЫМ УРОВНЕМ СИСТЕМАТИЧЕСКОЙ СОСТАВЛЯЮЩЕЙ НАПРЯЖЕНИЯ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784373C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных усилителей и выходных каскадов различных аналоговых устройств. Технический результат заключается в создании радиационно-стойкого и низкотемпературного схемотехнического решения входного каскада на комплементарных полевых транзисторах, обеспечивающего сверхмалые значения входного статического тока, в том числе при работе в диапазоне низких температур. Двухтактный выходной каскад содержит вход (1) и выход (2) устройства, первый (3) входной полевой транзистор, сток которого соединен с первым (4) токовым выходом устройства, согласованным с первой (5) шиной источника питания, второй (6) входной полевой транзистор, сток которого подключен ко второму (7) токовому выходу устройства, согласованному со второй (8) шиной источника питания, первый (9) и второй (10) согласующие прямосмещенные p-n-переходы. 4 з.п. ф-лы, 12 ил.

1. Двухтактный выходной каскад класса AB аналоговых микросхем на комплементарных полевых транзисторах для работы при низких температурах, содержащий вход (1) и выход (2) устройства, первый (3) входной полевой транзистор, сток которого соединен с первым (4) токовым выходом устройства, согласованным с первой (5) шиной источника питания, второй (6) входной полевой транзистор, сток которого подключен ко второму (7) токовому выходу устройства, согласованному со второй (8) шиной источника питания, первый (9) и второй (10) согласующие прямосмещенные p-n-переходы, отличающийся тем, что в качестве первого (3) и второго (6) входных полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом, затворы первого (3) и второго (6) входных полевых транзисторов подключены к входу (1) устройства, между истоками первого (3) и второго (6) входных полевых транзисторов включен дополнительный резистор (11), исток первого (3) входного полевого транзистора связан с выходом (2) устройства через первый (9) согласующий прямосмещенный p-n-переход, а исток второго (6) входного полевого транзистора соединен с выходом (2) устройства через второй (10) согласующий прямосмещенный p-n-переход.

2. Каскад по п. 1, отличающийся тем, что первый (4) токовый выход устройства соединен с первой (5) шиной источника питания, а второй (7) токовый выход устройства соединен со второй (8) шиной источника питания.

3. Каскад по п. 1, отличающийся тем, что исток первого (3) входного полевого транзистора связан со второй (8) шиной источника питания через первый (13) дополнительный источник опорного тока, а исток второго (6) входного полевого транзистора соединен с первой (5) шиной источника питания через второй (14) дополнительный источник опорного тока.

4. Каскад по п. 1, отличающийся тем, что в схему введены первый (15) и второй (16) дополнительные полевые транзисторы с управляющим p-n-переходом, затворы которых объединены и подключены к выходу устройства (2), исток первого (3) входного полевого транзистора соединен с истоком первого (15) дополнительного полевого транзистора с управляющим p-n-переходом через первый (17) вспомогательный резистор, сток первого (15) дополнительного полевого транзистора с управляющим p-n-переходом связан со второй (8) шиной источника питания, исток второго (6) входного полевого транзистора соединен с истоком второго (16) дополнительного полевого транзистора с управляющим p-n-переходом через второй (18) вспомогательный резистор, а сток второго (16) дополнительного полевого транзистора с управляющим p-n-переходом связан с первой (5) шиной источника питания.

5. Каскад по п. 1, отличающийся тем, что первый (9) и второй (10) согласующие прямосмещенные p-n-переходы выполнены в виде первого и второго составных двухполюсников, каждый из которых содержит несколько элементарных последовательно соединенных p-n-переходов.

| Маслоуловитель для предохранения от попадания масла из шестеренкой коробки в полость якорного подшипника электрической машины | 1930 |

|

SU25819A1 |

| RU 2004107106 A, 10.10.2005 | |||

| US 5907262 A, 25.05.1999 | |||

| US 5049653, 17.09.1991. | |||

Авторы

Даты

2019-11-21—Публикация

2019-07-04—Подача