Предлагаемое изобретение относится к области радиотехники и может использоваться в различных аналоговых устройствах в качестве повторителя сигнала с высоким входным сопротивлением и малой статической ошибкой.

Базовым узлом современных аналоговых устройств является истоковый повторитель напряжения (ИПН), который известен также как схема с общим стоком. Данная структура [1-37] широко используется как в аналоговых (класс H03F), так и в цифровых (класс H03K) устройствах. В последнем случае ИПН выполняет функции драйвера - каскада управления линиями связи или согласующей цепи.

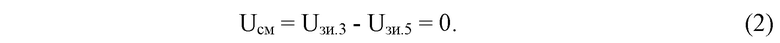

Ближайшим прототипом заявляемого устройства является классический истоковый повторитель напряжения, описанный в патентах US 7.304.540, fig. 1, 2007 г. и US 6.154.580, fig. 4, 2000 г. Он содержит вход 1 и выход 2 устройства, входной полевой транзистор 3, сток которого соединен с первой 4 шиной источника питания, затвор подключен ко входу 1 устройства, а исток связан с выходом 2 устройства, выходной полевой транзистор 5, исток которого связан со второй 6 шиной источника питания, а сток подключен к выходу устройства 2.

Существенный недостаток известного устройства состоит в том, что его напряжение смещения нуля определяется напряжением затвор-исток входного полевого транзистора 3, которое лежит в пределах от 0,5 до 2 В и существенно зависит от его статического тока и конструкции.

Основная задача предполагаемого изобретения состоит в уменьшении систематической составляющей напряжения смещения нуля (Uсм) истокового повторителя с единиц вольт до уровня единиц микровольт.

Поставленная задача достигается тем, что в повторителе напряжения фиг. 1, содержащем вход 1 и выход 2 устройства, входной полевой транзистор 3, сток которого соединен с первой 4 шиной источника питания, затвор подключен ко входу 1 устройства, а исток связан с выходом 2 устройства, выходной полевой транзистор 5, исток которого связан со второй 6 шиной источника питания, а сток подключен к выходу устройства 2, предусмотрены новые элементы и связи – исток входного полевого транзистора 3 связан с выходом устройства 2 через первый 7 прямосмещенный p-n-переход, а исток выходного полевого транзистора 5 связан со второй 6 шиной источника питания через второй 8 прямосмещенный p-n-переход, причем затвор выходного полевого транзистора 5 соединен со второй 6 шиной источника питания.

На чертеже фиг. 1 показан истоковый повторитель напряжения – прототип по патенту US 7.304.540, fig. 1, 2007 г. Кроме этого, данная схема присутствует в патенте US 6.154.580, fig. 4, 2000 г.

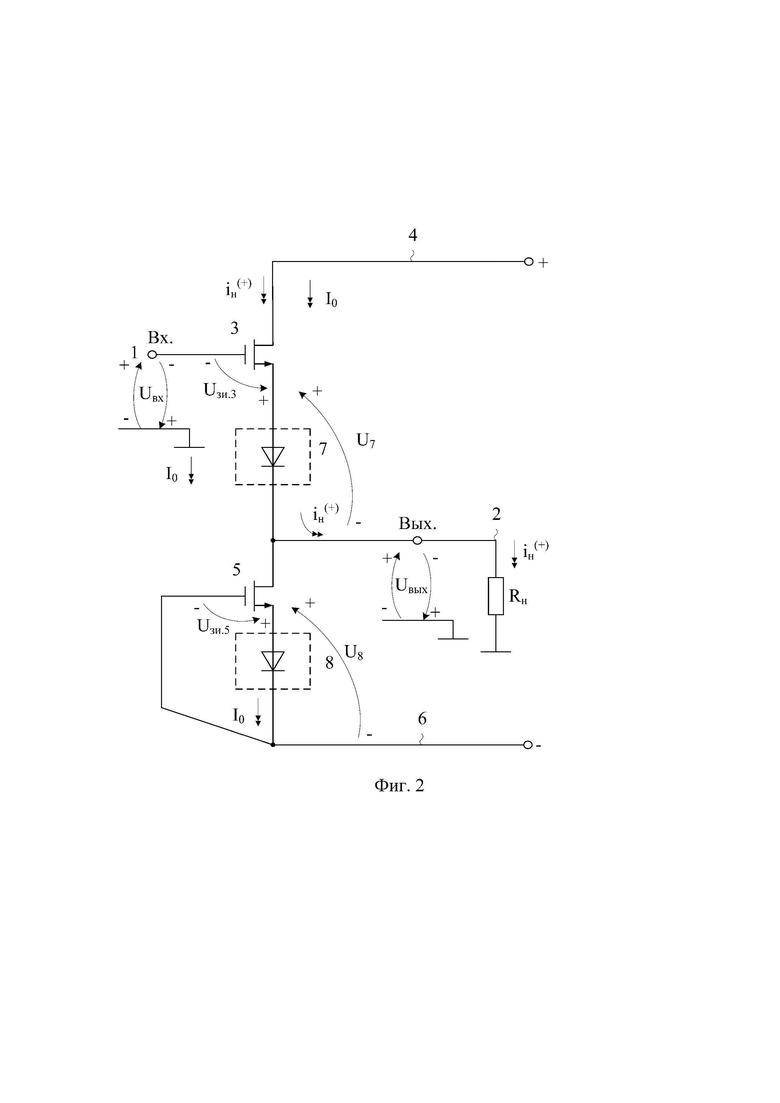

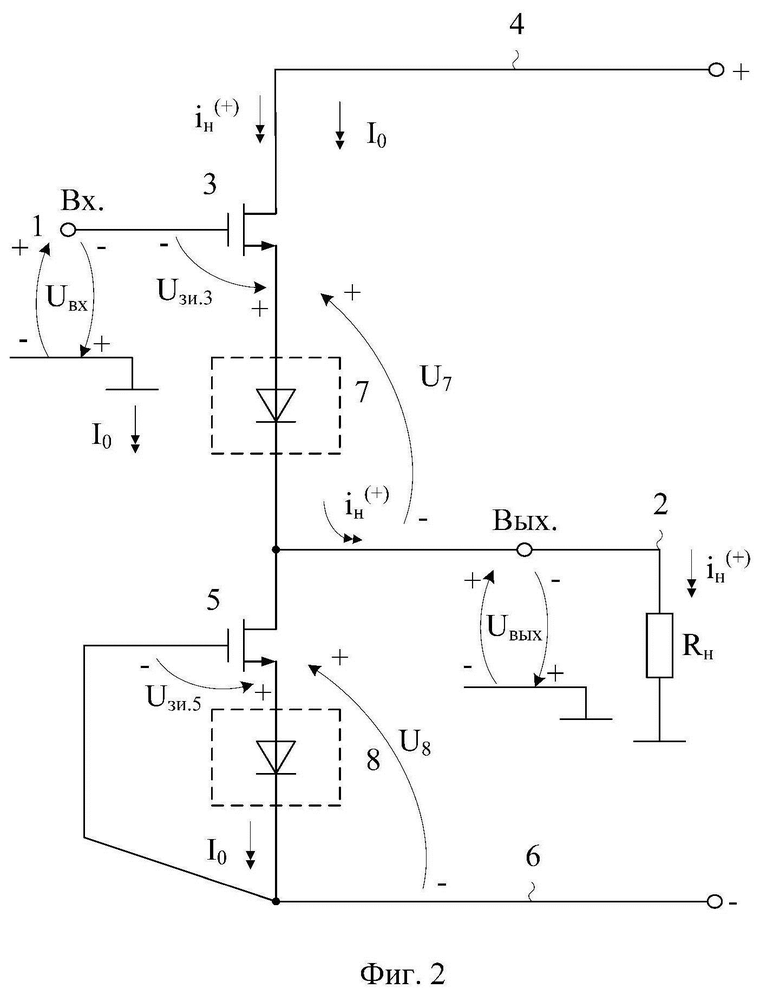

На чертеже фиг. 2 представлен заявляемый истоковый повторитель напряжения в соответствии с п. 1 и п.2 формулы изобретения.

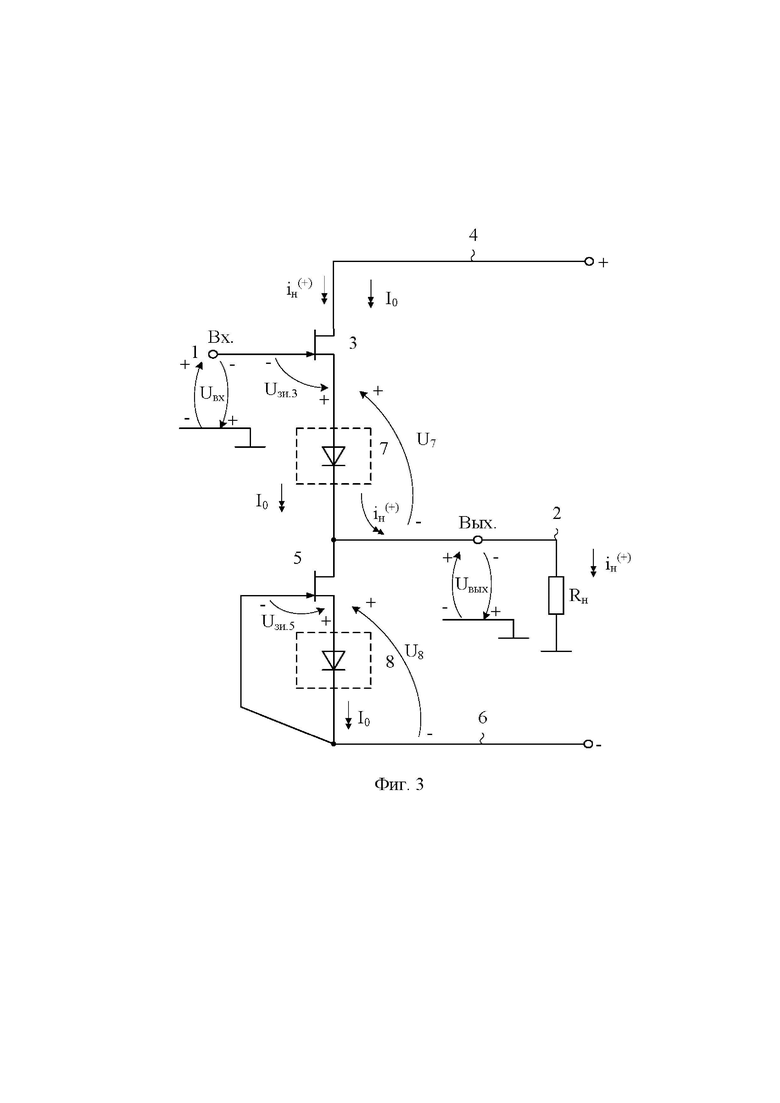

На чертеже фиг. 3 приведен истоковый повторитель напряжения в соответствии с п. 3 формулы изобретения.

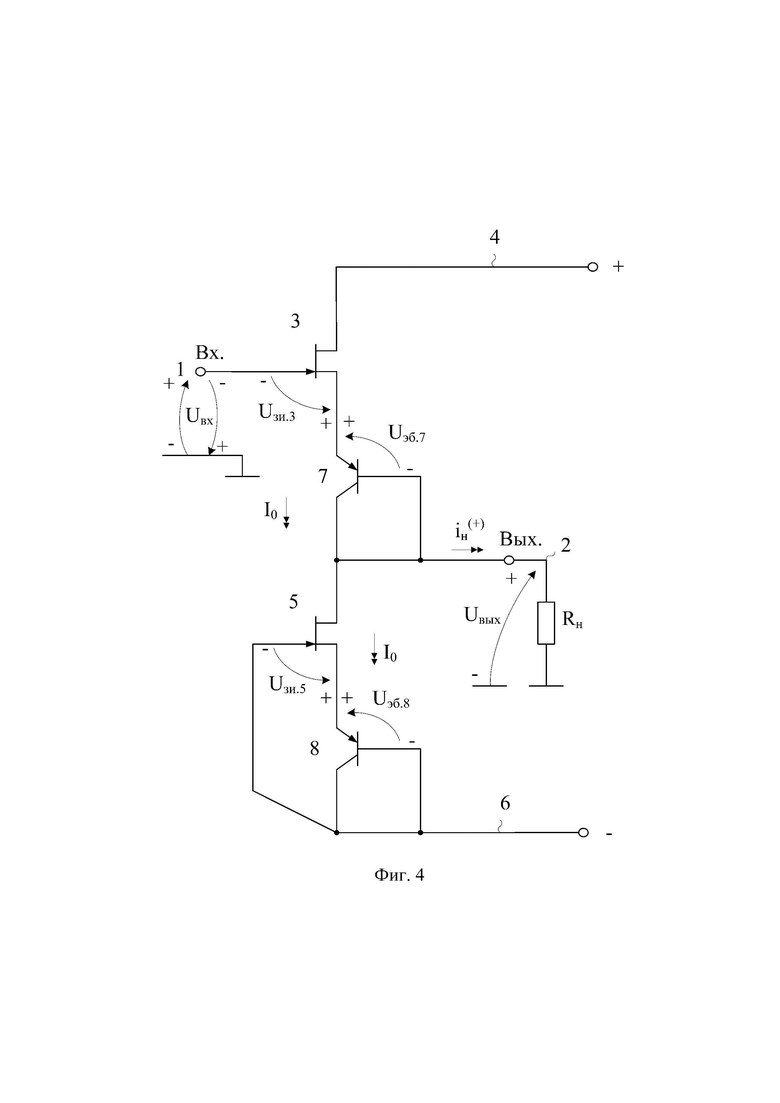

На чертеже фиг. 4 показан истоковый повторитель напряжения в соответствии с п. 4 формулы изобретения для случая, когда в качестве прямосмещенных p-n-переходов 7 и 8 используются биполярные p-n-p-транзисторы, а входной 3 и выходной 5 полевые транзисторы с управляющим p-n-переходом имеют n-канал.

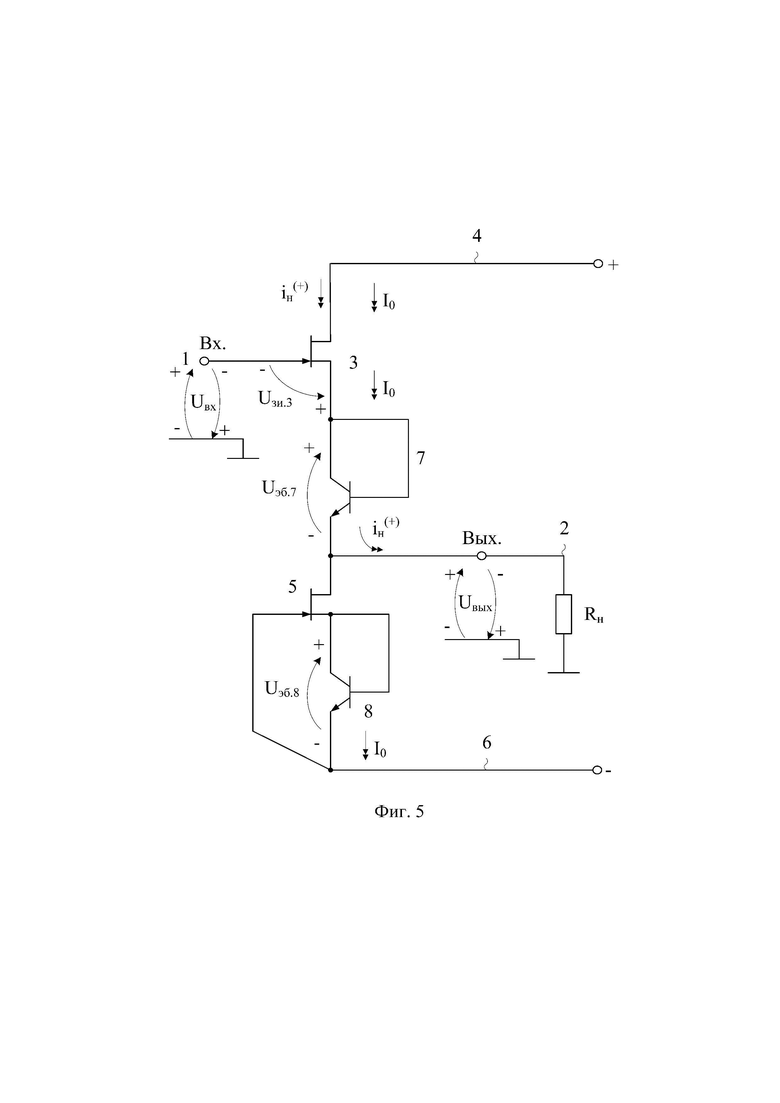

На чертеже фиг. 5 представлен истоковый повторитель напряжения в соответствии с п. 4 формулы изобретения для случая, когда в качестве прямосмещенных p-n-переходов 7 и 8 используются биполярные n-p-n-транзисторы, а входной 3 и выходной 5 полевые транзисторы с управляющим p-n-переходом имеют n-канал.

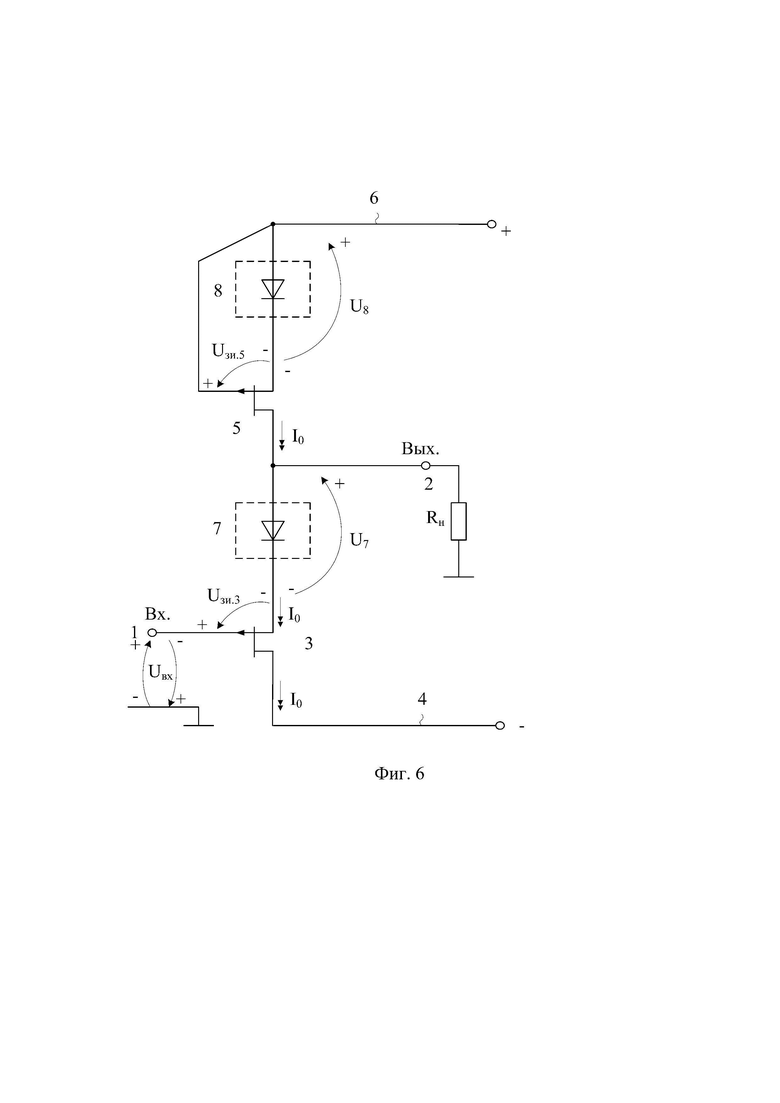

На чертеже фиг. 6 приведен истоковый повторитель напряжения в соответствии с п. 5 формулы изобретения для случая, когда в качестве полевых транзисторов 3 и 5 используются JFET полевые транзисторы p-каналом.

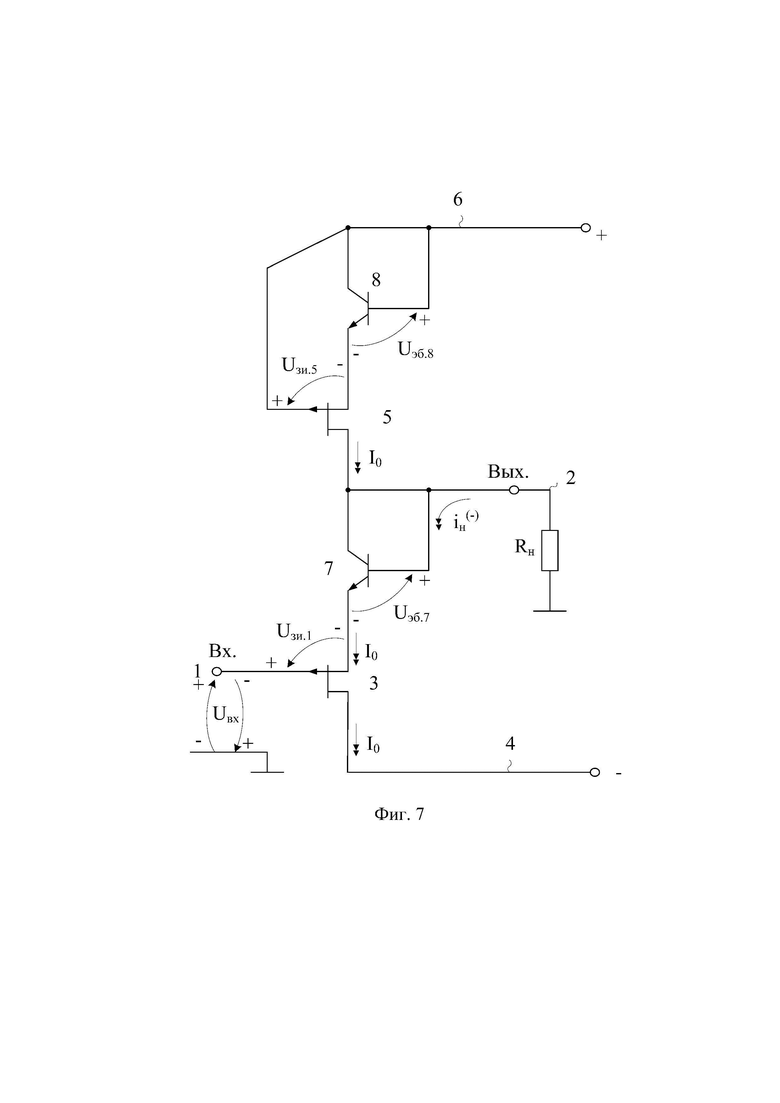

На чертеже фиг. 7 показан истоковый повторитель напряжения в соответствии с п. 5 формулы изобретения для случая, когда в качестве полевых транзисторов 3 и 5 используются JFET полевые транзисторы p-каналом, а прямосмещенные p-n-переходы 7 и 8 реализованы на n-p-n биполярных транзисторах.

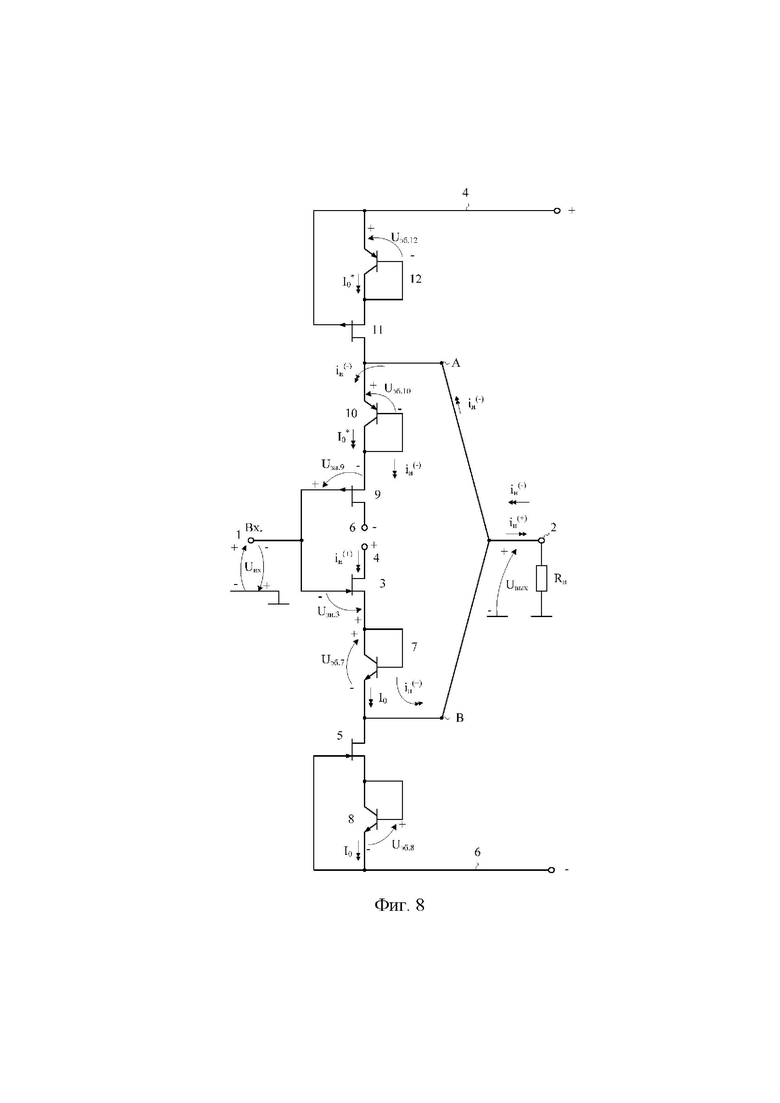

На чертеже фиг. 8 представлен двухтактный истоковый повторитель напряжения на JFET комплементарных входных транзисторах (3 и 9, а также 5 и 11) в соответствии с п. 6 формулы изобретения.

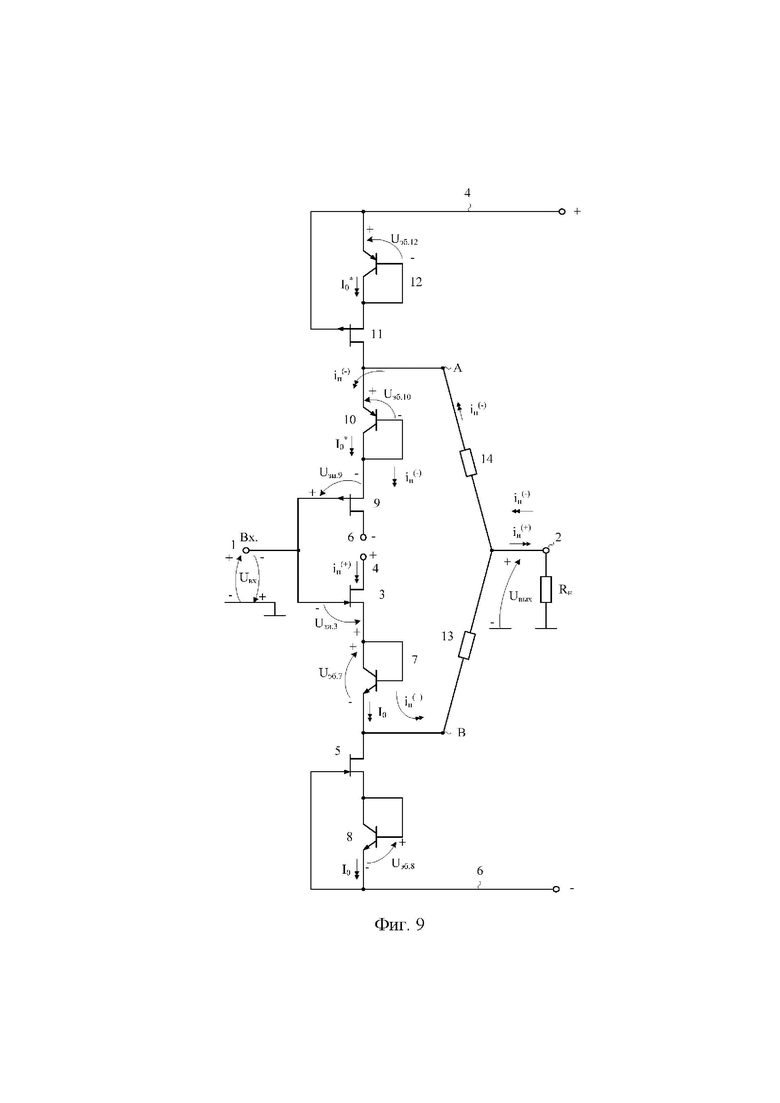

На чертеже фиг. 9 приведен двухтактный истоковый повторитель напряжения на JFET комплементарных входных транзисторах (3 и 9, а также 5 и 11) в соответствии с п. 7 формулы изобретения.

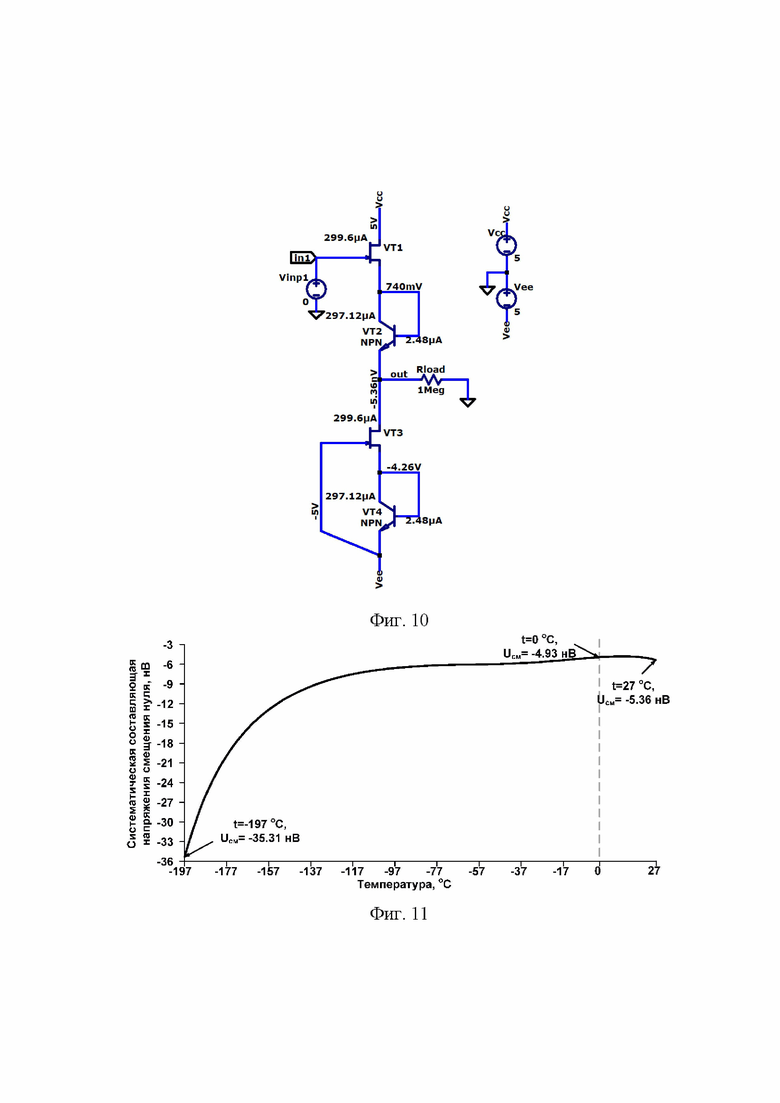

На чертеже фиг. 10 показана схема для моделирования JFet-n-p-n истокового повторителя напряжения, соответствующего фиг. 5, в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload=1 МОм.

На чертеже фиг. 11 представлена зависимость систематической составляющей напряжения смещения нуля JFet-n-p-n истокового повторителя напряжения фиг. 10 от температуры при +Vcc=-Vee=5 В, Rload=1 МОм.

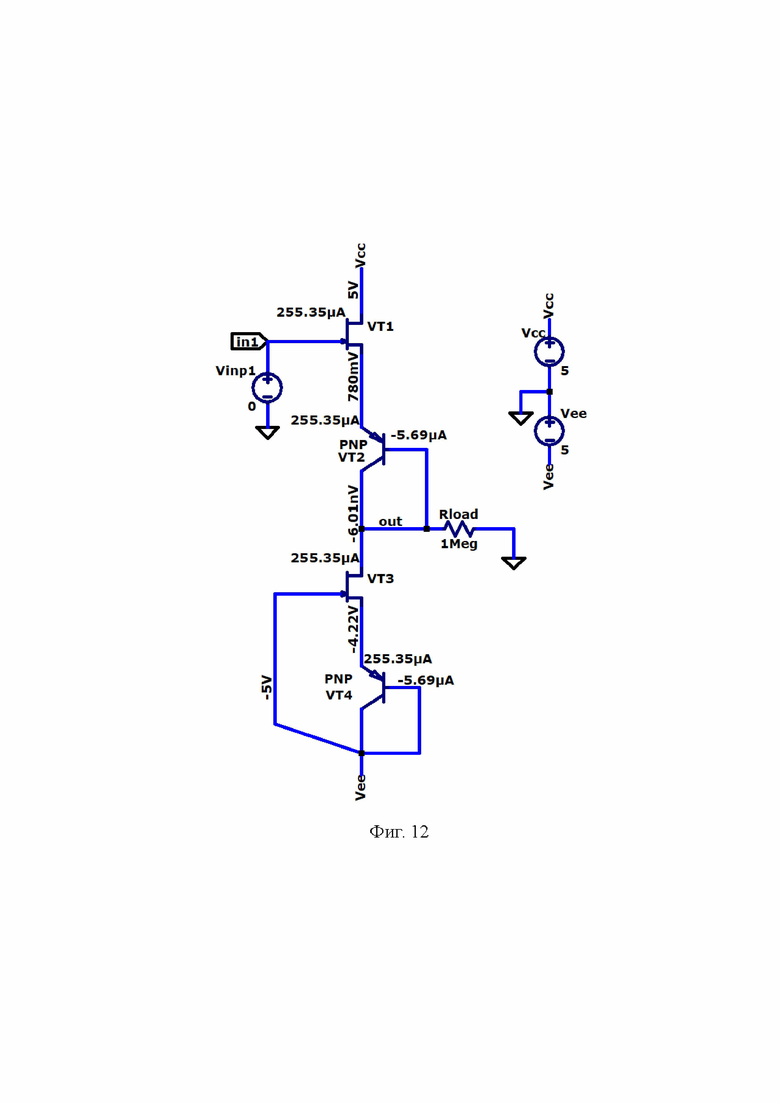

На чертеже фиг. 12 приведена схема для моделирования Si JFet-p-n-p истокового повторителя напряжения, соответствующего фиг. 4, в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload=1 МОм.

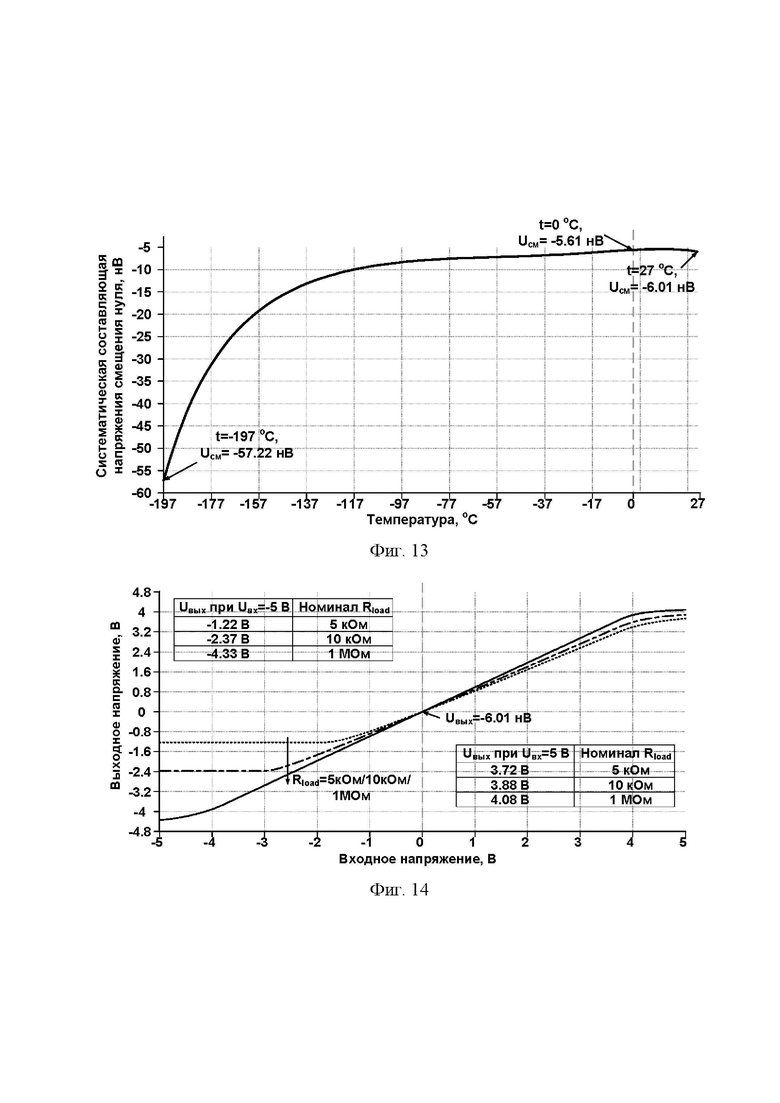

На чертеже фиг. 13 показана зависимость систематической составляющей напряжения смещения нуля Si JFet-p-n-p истокового повторителя напряжения фиг. 12 от температуры при +Vcc=-Vee=5 В, Rload=1 МОм.

На чертеже фиг. 14 представлена амплитудная характеристика кремниевого JFet-p-n-p истокового повторителя напряжения фиг. 12 в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload= 5 кОм/ 10 кОм/1 МОм.

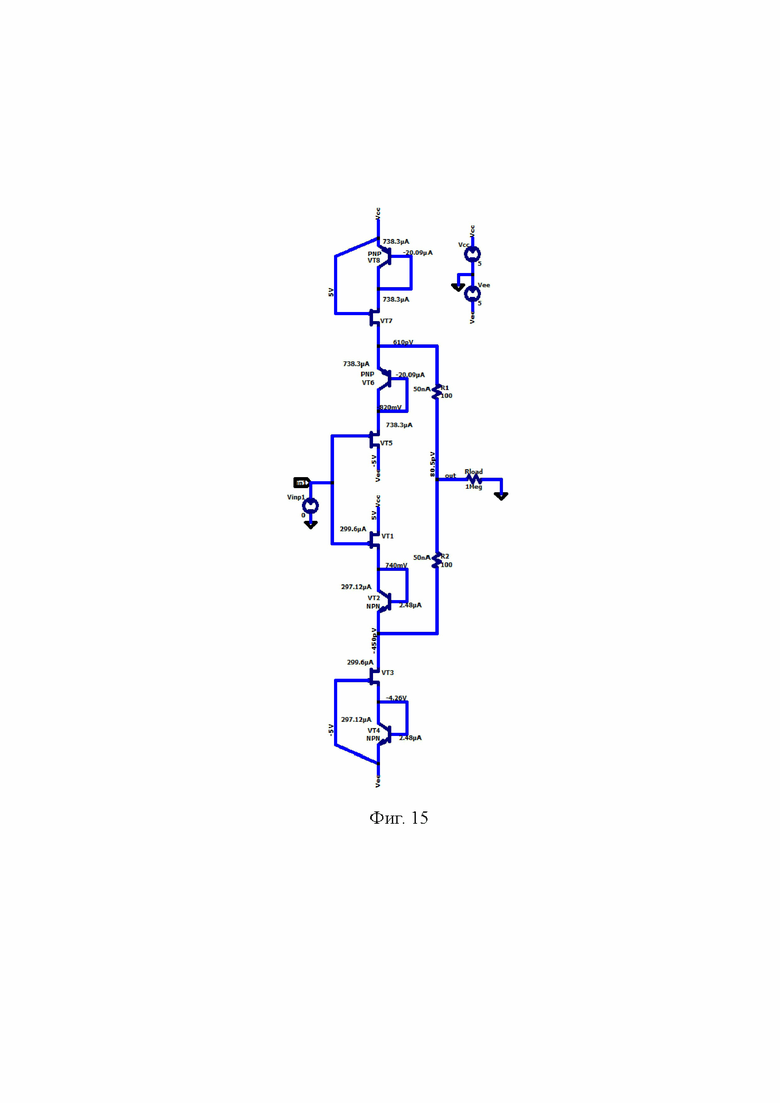

На чертеже фиг. 15 приведена схема для моделирования Si повторителя напряжения, соответствующего фиг. 9, в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload=1 МОм, R1=R2=100 Ом.

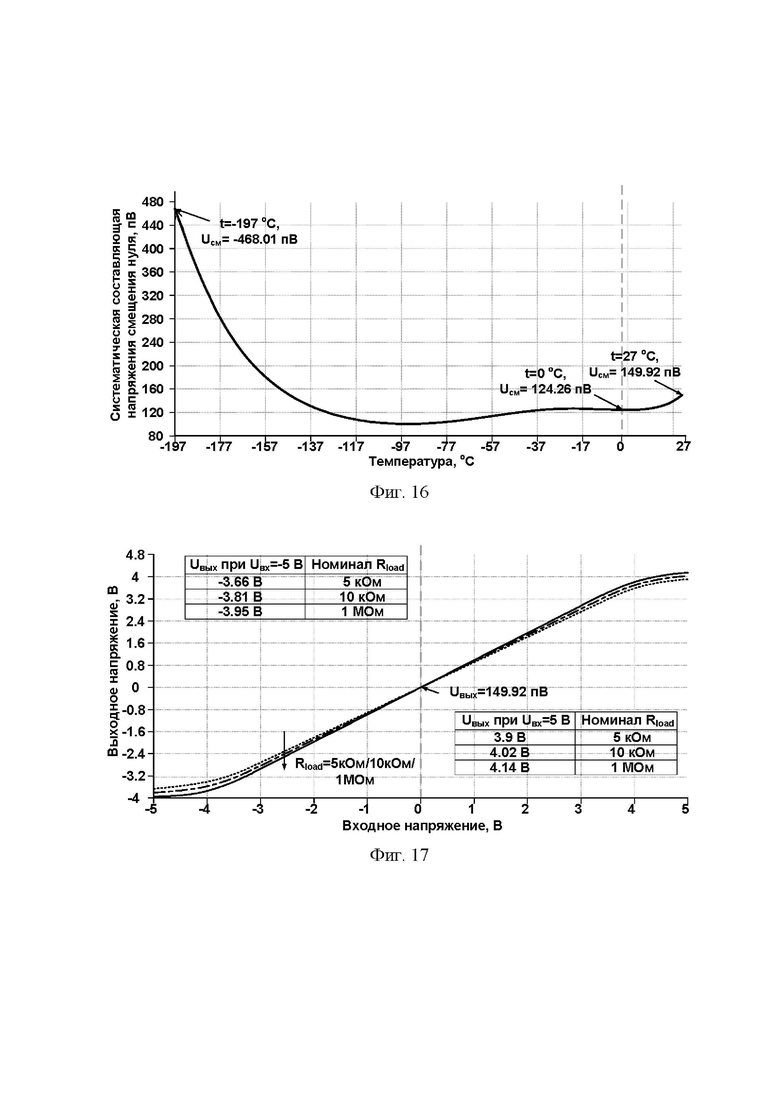

На чертеже фиг. 16 показана зависимость систематической составляющей напряжения смещения нуля кремниевого повторителя напряжения фиг. 15 от температуры при +Vcc=-Vee=5 В, Rload=1 МОм.

На чертеже фиг. 17 представлена амплитудная характеристика кремниевого повторителя напряжения фиг. 15 в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload= 5 кОм/ 10 кОм/1 МОм.

Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля фиг. 2 содержит вход 1 и выход 2 устройства, входной полевой транзистор 3, сток которого соединен с первой 4 шиной источника питания, затвор подключен ко входу 1 устройства, а исток связан с выходом 2 устройства, выходной полевой транзистор 5, исток которого связан со второй 6 шиной источника питания, а сток подключен к выходу устройства 2. Исток входного полевого транзистора 3 связан с выходом устройства 2 через первый 7 прямосмещенный p-n-переход, а исток выходного полевого транзистора 5 связан со второй 6 шиной источника питания через второй 8 прямосмещенный p-n-переход, причем затвор выходного полевого транзистора 5 соединен со второй 6 шиной источника питания.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, в качестве входного 3 и выходного 5 полевых транзисторов используются КМОП полевые транзисторы с индуцированным каналом.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, в качестве входного 3 и выходного 5 полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом.

На чертежах фиг. 4 и фиг. 5, в соответствии с п. 4 формулы изобретения, входной 3 и выходной 5 полевые транзисторы имеют n-канал.

На чертежах фиг. 6 и фиг. 7, в соответствии с п. 5 формулы изобретения, входной 3 и выходной 5 полевые транзисторы имеют p-канал.

На чертеже фиг. 8, в соответствии с п. 6 формулы изобретения, ко входу устройства 1 подключен затвор дополнительного входного полевого транзистора 9 с p-каналом, сток которого соединен со второй 6 шиной источника питания, а исток соединен через третий 10 прямосмещенный p-n-переход со стоком дополнительного выходного полевого транзистора 11 с p-каналом, причем исток дополнительного выходного полевого транзистора 11 с p-каналом связан с первой 4 шиной источника питания через четвертый 12 прямосмещенный p-n-переход, кроме этого сток дополнительного выходного полевого транзистора 11 с p-каналом связан с выходом устройства 2.

На чертеже фиг. 9, в соответствии с п. 7 формулы изобретения, сток выходного полевого транзистора 5 с n-каналом связан с выходом устройства 2 через первый 13 дополнительный резистор, а сток дополнительного выходного полевого транзистора 11 с p-каналом связан с выходом устройства 2 через второй 14 дополнительный резистор.

Рассмотрим работу ИПН на чертеже фиг. 3.

На основании второго закона Кирхгофа для схемы фиг. 3 (фиг. 2) можно составить следующее уравнение для выходного напряжения ИПН

где Uзи.3 – напряжение затвор-исток входного полевого транзистора 3 при токе стока, равно I0;

U7 – напряжение на первом 7 прямосмещенном p-n-переходе.

Ток I0 через первый 7 прямосмещенный p-n-переход определяется током через второй 8 прямосмещенный p-n-переход, который идентичен первому 7 прямосмещенному p-n-переходу. Поэтому

Uэ = U8 = Uзи.5 = Uзи.3.

Таким образом, при отсутствии входного сигнала систематическая составляющая напряжения смещения нуля ИПН фиг. 3

Для схемы фиг. 4, в которой первый 7 и второй 8 прямосмещенные p-n-переходы выполнены на p-n-p-транзисторах, также справедливо уравнение (2).

Если входной полевой транзистор 3 имеет p-канал (фиг. 6, фиг. 7), то и в этом случае выполняется условие (2).

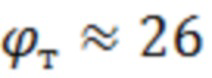

Выходное сопротивление предлагаемого ИПН на чертеже фиг. 3 определяется формулой

где S1 – крутизна стоко-затворной характеристики входного полевого транзистора 3;

мВ – температурный потенциал;

мВ – температурный потенциал;

I0 – статический ток истока входного полевого транзистора 3.

Двухтактная структура ИПН, работающая в режиме класса АВ, реализуется в соответствии с чертежами фиг. 8 и фиг. 9.

Компьютерное моделирование ИПН фиг. 10 и фиг. 12 показывает, что Uсм рассматриваемых ИПН измеряется микровольтами. При этом амплитудная характеристика ИПН, представленная на чертеже фиг. 4, соответствует работе схемы в режиме класса АВ.

Исследования двухтактного ИПН на чертеже фиг. 15, представленные на чертежах фиг. 16 и фиг. 17, показывают, что данное схемотехническое решение имеет симметричную амплитудную характеристику (фиг. 17). При этом максимальные выходные токи в схеме ИПН на чертеже фиг. 15 могут быть увеличены за счет параллельного включения нескольких входных полевых транзисторов или изменения ширины их каналов.

Таким образом, выше показано, что в заявляемой схеме истокового повторителя создаются условия для существенного уменьшения систематической составляющей напряжения смещения нуля, что обусловлено ее балансной структурой и эффектами взаимной компенсации.

Выполненный выше анализ, а также результаты компьютерного моделирования показывают, что в заявляемой схеме истокового повторителя решена одна из проблем современной аналоговой микросхемотехники – минимизация напряжения смещения нуля.

Таким образом, заявляемое устройство в сравнении с прототипом имеет существенные преимущества по уровню систематической составляющей напряжения смещения нуля.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5351012, 1994 г. (в схеме fig. 6 – полевой транзистор 14 и источник опорного тока 26).

2. Патент US 7764123, 2010 г. (в схеме fig. 3 – полевой транзистор N1 и источник опорного тока CS2).

3. Патент US 5973534, 1999 г. (в схеме fig. 1b – полевой транзистор 120 и источник опорного тока на транзисторах 122 и 124).

4. Патент US 6215357, 2001 г. (в схеме fig. 3 – полевой транзистор М5, источник опорного тока на транзисторе М4).

5. Патент RU 2536672, 2014 г. (в схемах fig. 3 и fig. 4 – входной биполярный транзистор, токовое зеркало 8 и выходной транзистор 1).

6. Заявка на патент US 2005/0275453, 2005 г. (в схеме fig. 1 – полевой транзистор MN1, источник опорного тока 14).

7. Патент US 6573784, 2003 г. (в схеме fig. 4 – полевой транзистор 414, источник опорного тока 452).

8. RU 2530263 C1, 2014 г.

9. Авт. свидетельство SU 1 059 665, 1981 г. (в схеме фиг. 1 – входной полевой транзистор 1, источник опорного тока 3).

10. Заявка на патент US 2004/0227573, 2004 г. (в схеме fig. 4 – полевой транзистор 2, источник опорного тока 4).

11. Патент US 4806877, 1989 г. (в схеме fig. 3 – полевой транзистор TR0, источник опорного тока J0).

12. Патент EP 0 648 010, 1994 г. (в схеме fig. 4 – полевой транзистор T1, источник опорного тока 32).

13. Заявка на патент US 2010/0013562, 2010 г. (в схеме fig. 1 – полевой транзистор 150, источник опорного тока 185).

14. Патент US 7847590, 2010 г. (в схеме fig. 5 – полевой транзистор 523, источник опорного тока 521).

15. Патент US 7.898.339, fig.4, 2011 г.

16. Патент US 6.727.729 fig.5B, 2004 г.

17. Патент US 7.733.182 fig.1, 2010 г.

18. Патент US 6.043.690 fig.1, fig.2, 2000 г.

19. Патент US 3.678.402 fig.2, fig.7, 1972 г.

20. Патент US 5.469.085 fig.2, 1995 г.

21. Патент US 4.492.932 fig.4a, 1985 г.

22. Патент US 4.092.701, 1978 г.

23. Патент US 4.698.526 fig.2, 1987 г.

24. Патент US 6.469.562 fig.A, fig.2A, 2002 г.

25. Патент US 6.154.580, fig.4, 2000 г.

26. Патент US 7.304.540, fig.1, fig.2, 2007 г.

27. Патент US 7.944.303, fig.1, 2011 г.

28. Патент US 8.148.962, fig.2, 2012 г.

29. Патент US 5.045.808, 1991 г.

30. Патент US 4.101.788, fig.2, 1978 г.

31. Патент US 3.436.672, fig.1, 1969 г.

32. Патент US 4.168.471, fig.1, 1979 г.

33. Патент US 5.365.199, fig.2, 1994 г.

34. Патент US 5.666.070, 1997 г.

35. Эннс В. И., Кобзев Ю. М. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика / Под редакцией канд. Техн. Наук В. И. Эннса. – М.: Горячая линия-Телеком. – 2005. – 454 с.: ил. (рис. 3.54а, стр. 183).

36. Singh R., Mehra R. Design A Darlington Amplifier with Improved Gain and Slew Rate //International Journal of Electronics and Communication Technology. – 2017. – Т. 8. – №. 4. – С. 13-16. (Fig. 3, Fig. 4).

37. D. Danyuk, «JFET Follower Amplifier Cancels Distortion» URL: https://www.radiolocman.com/shem/schematics.html?di=606611 (в схеме fig. 1 - полевой транзистор Q1, источник опорного тока на биполярным транзисторе Q2).

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОКОВЫЙ ПОВТОРИТЕЛЬ СИГНАЛА С МАЛЫМ УРОВНЕМ СИСТЕМАТИЧЕСКОЙ СОСТАВЛЯЮЩЕЙ НАПРЯЖЕНИЯ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784373C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| НЕИНВЕРТИРУЮЩИЙ ВЫХОДНОЙ КАСКАД АРСЕНИД-ГАЛЛИЕВОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2784049C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ n-КАНАЛЬНЫХ ПОЛЕВЫХ И p-n-p БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2784376C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

Изобретение относится к области радиотехники. Технический результат: уменьшение систематической составляющей напряжения смещения нуля истокового повторителя с единиц вольт до уровня единиц микровольт. Для этого предложен истоковый повторитель, который содержит вход (1) и выход (2) устройства, входной полевой транзистор (3), сток которого соединен с первой (4) шиной источника питания, затвор подключен ко входу (1) устройства, а исток связан с выходом (2) устройства, выходной полевой транзистор (5), исток которого связан со второй (6) шиной источника питания, а сток подключен к выходу устройства (2). Исток входного полевого транзистора (3) связан с выходом устройства (2) через первый (7) прямосмещенный p-n-переход, а исток выходного полевого транзистора (5) связан со второй (6) шиной источника питания через второй (8) прямосмещенный p-n-переход, причем затвор выходного полевого транзистора (5) соединен со второй (6) шиной источника питания. 6 з.п. ф-лы, 17 ил.

1. Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля, содержащий вход (1) и выход (2) устройства, входной полевой транзистор (3), сток которого соединен с первой (4) шиной источника питания, затвор подключен ко входу (1) устройства, а исток связан с выходом (2) устройства, выходной полевой транзистор (5), исток которого связан со второй (6) шиной источника питания, а сток подключен к выходу устройства (2), отличающийся тем, что исток входного полевого транзистора (3) связан с выходом устройства (2) через первый (7) прямосмещенный p-n-переход, а исток выходного полевого транзистора (5) связан со второй (6) шиной источника питания через второй (8) прямосмещенный p-n-переход, причем затвор выходного полевого транзистора (5) соединен со второй (6) шиной источника питания.

2. Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля по п.1, отличающийся тем, что в качестве входного (3) и выходного (5) полевых транзисторов используются КМОП полевые транзисторы с индуцированным каналом.

3. Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля по п.1, отличающийся тем, что в качестве входного (3) и выходного (5) полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом.

4. Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля по п.3, отличающийся тем, что входной (3) и выходной (5) полевые транзисторы имеют n-канал.

5. Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля по п.3, отличающийся тем, что входной (3) и выходной (5) полевые транзисторы имеют p-канал.

6. Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля по п.4, отличающийся тем, что ко входу устройства (1) подключен затвор дополнительного входного полевого транзистора (9) с p-каналом, сток которого соединен со второй (6) шиной источника питания, а исток соединен через третий (10) прямосмещенный p-n-переход со стоком дополнительного выходного полевого транзистора (11) с p-каналом, причем исток дополнительного выходного полевого транзистора (11) с p-каналом связан с первой (4) шиной источника питания через четвертый (12) прямосмещенный p-n-переход, кроме этого сток дополнительного выходного полевого транзистора (11) с p-каналом связан с выходом устройства (2).

7. Истоковый повторитель напряжения с малым уровнем систематической составляющей напряжения смещения нуля по п.6, отличающийся тем, что сток выходного полевого транзистора (5) с n-каналом связан с выходом устройства (2) через первый (13) дополнительный резистор, а сток дополнительного выходного полевого транзистора (11) с p-каналом связан с выходом устройства (2) через второй (14) дополнительный резистор.

| US 7304540 B2, 04.12.2007 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2530263C1 |

| US 6924674 B2, 02.08.2005 | |||

| US 4430586 A1, 07.02.1984. | |||

Авторы

Даты

2022-11-23—Публикация

2022-07-17—Подача